# **Engineering Specification**

| DADT MAME                                   |      |         |         |                  |         |         |        |         |                   | DADTA   | ПМрет   | 2    |      |         |      |            |                 |           |         |

|---------------------------------------------|------|---------|---------|------------------|---------|---------|--------|---------|-------------------|---------|---------|------|------|---------|------|------------|-----------------|-----------|---------|

| PART NAME PART NUMBER                       |      |         |         |                  |         | EC 2    | riem : | 1D255   | 7 A A             |         |         |      |      |         |      |            |                 |           |         |

| EMC Design Guide for Printed Circuit Boards |      |         |         | ES-3U5T-1B257-AA |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

| LET                                         | A    | A       | A       | A                | A       | A       | A      | A       | A                 | A       | A       | A 12 | A    | A       | A    | A          | A               | A         | A       |

| FR                                          | 1    | 2       | 3       | 4                | 5       | 6       | 7      | 8       | 9                 | 10      | 11      | 12   | 13   | 14      | 15   | 16         | 17              | 18        | 19      |

| LET                                         | A 20 | A       | A       | A                | A       | A 25    | A 26   | A 27    | A                 | A 20    | A 20    | A    | A    | A       | A    | A 2.5      | A 26            | A         | A 20    |

| FR                                          | 20   | 21      | 22      | 23               | 24      | 25      | 26     | 27      | 28                | 29      | 30      | 31   | 32   | 33      | 34   | 35         | 36              | 37        | 38      |

| LET                                         | A 39 | A<br>40 | 41      | 42               | A 43    | A<br>44 | A 45   | A<br>46 | A 47              | A<br>48 | A<br>49 | 50   | 51   | A 52    | 53   | 54         | 55              | A 56      | 57      |

| FR                                          |      |         |         |                  |         |         |        |         | 47                |         |         |      |      |         |      |            |                 |           |         |

| LET                                         | 58   | A 59    | A<br>60 | A 61             | A 62    | A 63    | A 64   | A<br>65 | A 66              | A 67    | A 68    | A 69 | A 70 | A<br>71 | A 72 | 73         | A 74            | 75        | A<br>76 |

| FR                                          |      |         | 00      | 01               | 02      | 0.3     | 04     | 03      | 00                | 0/      | 08      | 09   | /0   | / 1     | 12   | /3         | /4              | /3        | /0      |

| LET                                         | 77   | A 78    |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

| FR                                          | //   |         | ED      |                  |         |         | D      | EMICIO  | NIC               |         |         |      | DD   | CV      |      | RF         | <br> <br> FEREN | CE.       |         |

|                                             |      | LET     | FR      | Relea            | agad:   | EC 1    |        | EVISIO  | 57-AA             |         |         |      | DR   | CK      |      |            | . LILLI         | CL        |         |

|                                             |      |         |         |                  | l Rele  |         | 0051.  | -1DZ,   | ) / <b>-</b> A.P. | 1       |         |      |      |         | PF   | REPARE     | D/APPF          | OVED E    | BY      |

| 200210                                      | 001  |         |         |                  | )-I-11  |         | 3-000  | )       |                   |         |         |      |      |         |      |            |                 | 2-319     |         |

| 200210                                      | 701  |         |         | TLU              | )-1-11· | 7707.   | 3-000  | ,       |                   |         |         |      |      |         |      | CKED B     |                 | ETAILE    |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         | CO   | NCURR      | ENCE//          | APPROV    | AL.     |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            | NATUI           |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         | De   | sign Eng   | gineering       | g Supervi | sor     |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      | T 1        | Herm            | ann       |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         | Des  | ign Engi   | neering         | Managen   | nent    |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      | C.         | De B            | iasi      |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            | acturing        |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      | Qua        | ality Cor       | ntrol     |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      | P          | urchasir        | ng        |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         | S    | Supplier ( | Quality A       | Assistanc | e       |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

|                                             |      |         |         |                  |         |         |        |         |                   |         |         |      |      |         |      |            |                 |           |         |

| ED 43.55                                    | 1    |         |         | <b>5</b> ^       |         | 1       |        | _       |                   | 1       |         |      |      |         |      |            |                 |           |         |

| FRAME                                       | 1    | (       | OF      | 78               |         |         |        | Α       |                   |         |         |      |      |         |      |            |                 |           |         |

PD May 1988 3947a1e

Initial Release Date: OCTOBER 01 2002

## TABLE OF CONTENTS

| PART I:         | PREFACE                                                          | 8        |

|-----------------|------------------------------------------------------------------|----------|

| 1. INTRO        | ODUCTION                                                         | 8        |

| PART II:        | GENERAL EMC                                                      | <u>9</u> |

|                 | OVERVIEW                                                         |          |

| 2.1. T          | he Elements                                                      | <u>9</u> |

| 2.2. T          | he Environment                                                   | 10       |

| 2.3. R          | legulations and Standards                                        | 11       |

| 2.4. E          | lements of EMI                                                   | 12       |

| <b>PART III</b> | : DESIGN APPROACH                                                | 14       |

| 3. OVER         | CVIEW                                                            | 14       |

| 3.1. D          | Design Approach for Immunity (Susceptibility)                    | 14       |

| 3.1.1.          |                                                                  |          |

| 3.1.2.          | Design Approach for ESD                                          | 14       |

| 3.2. D          | Design Approach for Controlling Radiated and Conducted Emissions | 14       |

|                 | Fround System                                                    |          |

| 3.4. V          | Vavelength and Frequency                                         | 19       |

| 3.5. F          | requency Domain of Digital Signals                               | 22       |

| 3.6. R          | adiated Emissions Predictions                                    | 24       |

| 3.7. C          | Crosstalk                                                        | 28       |

| 3.7.1.          | Common Impedance Coupling                                        | 29       |

| 3.7.2.          | Capacitive and inductive coupling                                | 30       |

| 3.7.3.          | 1 6                                                              |          |

| 3.7.4.          | Inductive coupling                                               |          |

|                 | wisted Pair                                                      |          |

|                 | hielding                                                         |          |

|                 | Resistance                                                       |          |

|                 | nductance                                                        |          |

| PART IV         | : IC RE MEASUREMENT PROCEDURE                                    | 46       |

| 4. SCOP         | E                                                                | 46       |

| 4.1. A          | Applicable Documents                                             | 46       |

| 4.2. E          | MC Test Recommendations                                          | 47       |

|                 | est Procedure Applicability                                      |          |

|                 | C Emissions Reference Levels                                     |          |

| 4.4.1.          | Level 1                                                          | 49       |

| 4.4.2.          | Level 2                                                          |          |

| 4.4.3.          |                                                                  |          |

| 4.4.4.          | Level 4                                                          |          |

| 4.4.5.          | Level NR                                                         |          |

|                 | Oata Submission                                                  |          |

| 4.6. R          | adiated and Conducted Immunity                                   |          |

| PART V:         | EMC DESIGN GUIDELINES FOR PCB                                    | 51       |

| 5. GENE         |                                                                  |          |

|                 | Soard Structure/Ground Systems                                   |          |

| 5.2. P          | ower Systems                                                     | 57       |

|                 |                                                                  |          |

| 5.3. Digital Circuits                                                         | 61 |

|-------------------------------------------------------------------------------|----|

| 5.4. Analog Circuits                                                          | 64 |

| 5.5. Communication Protocols                                                  | 65 |

| 5.6. Shielding                                                                | 65 |

| 5.7. Miscellaneous                                                            | 67 |

| PART VI: REQUIREMENTS                                                         | 69 |

| 6. MANAGEMENT OF CHANGE FOR EMC                                               | 69 |

| 6.1. Radiated Immunity:                                                       | 69 |

| 6.1.1. For safety critical systems (containing one or more Class C functions) | 69 |

| 6.1.2 For non-safety critical systems                                         | 70 |

| 6.2. Conducted immunity:                                                      |    |

| 6.3. Electrostatic Discharge                                                  | 70 |

| 6.4. Conducted Emissions:                                                     | 71 |

| 6.4.1 CE420 Frequency domain                                                  | 71 |

| 6.4.2 CE410 Time Domain                                                       | 71 |

| PART VII: CHECKOFF LIST                                                       | 72 |

| 7. CHECKOFF LIST – EMC DESIGN GUIDE FOR PCB(S)                                |    |

### TABLE OF FIGURES

| Figure 2–1. Elements of EMI                                         | 12 |

|---------------------------------------------------------------------|----|

| Figure 3–1. Ground Grid                                             |    |

| Figure 3–2. Inductance of Grounds                                   | 16 |

| Figure 3–3. Single-Point Ground                                     | 18 |

| Figure 3–4. Multi-Point Ground                                      | 18 |

| Figure 3–5. Hybrid Ground                                           | 18 |

| Figure 3–6. Wavelength of an Electrical Signal                      | 19 |

| Figure 3–7. Elements of Digital Signal                              | 22 |

| Figure 3–8. Digital Signal Spectrum                                 | 22 |

| Figure 3–9. Setup for Measuring CM Currents                         | 27 |

| Figure 3–10. Elements of Common Impedance                           |    |

| Figure 3–11. Inductive and Capacitive Coupling Between Two Circuits | 30 |

| Figure 3–12. Capacitive Coupling                                    |    |

| Figure 3–13. Inductive Coupling                                     | 34 |

| Figure 3–14. Mutual Inductance Between Two Wires                    | 35 |

| Figure 3–15. Magnetic Field Coupling into Circuit                   | 36 |

| Figure 3–16. Magnetic Field Coupling into Twisted Wire Pair         | 36 |

| Figure 3–17. Effectiveness of Shielding.                            | 37 |

| Figure 3–18. Inductance in Parallel Wires                           | 42 |

| Figure 3–19. Inductance in Wires over Ground Plane                  | 43 |

| Figure 3–20. Inductance of Ground Plane vs. Wire Inductance         |    |

| Figure 4–1. IC Radiated Emissions Acceptance Levels                 | 48 |

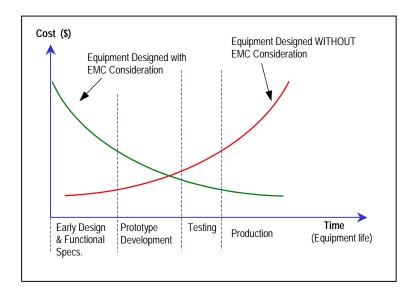

| Figure 5–1. Relative Costs of EMC vs. NO EMC Design Strategy        | 51 |

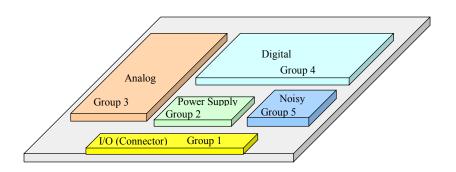

| Figure 5–2. Arrangement of Functional Groups on PCB                 | 52 |

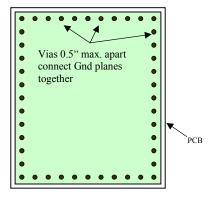

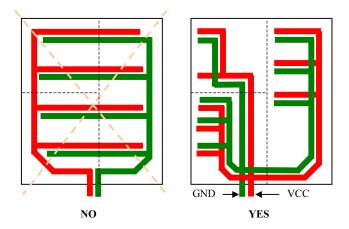

| Figure 5–3. Maximizing Ground on PCB                                | 52 |

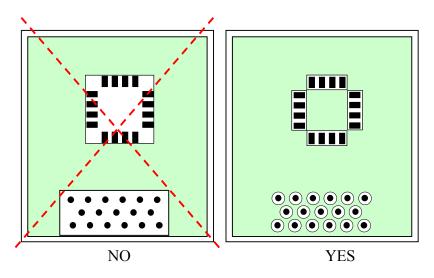

| Figure 5–4. Ground Grid Technique                                   | 53 |

| Figure 5–5. Creating 'Faraday's Cage'                               |    |

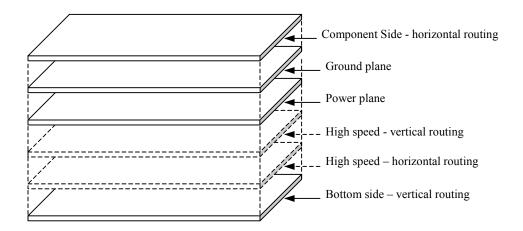

| Figure 5–6. Layer Stack-up                                          | 54 |

| Figure 5–7. IC Ground                                               |    |

| Figure 5–8. Eliminating Floating Ground.                            | 55 |

| Figure 5–9. Establishing Ground Plane Boundary                      | 56 |

| Figure 5–10. Power System's Star Point                              | 57 |

| Figure 5–11. Power and Ground Routing                               | 58 |

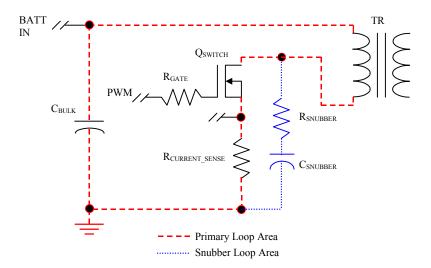

| Figure 5–12. Primary Loop Area                                      |    |

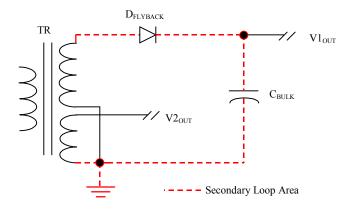

| Figure 5–13. Secondary Loop Area                                    |    |

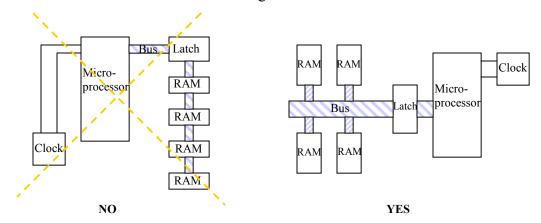

| Figure 5–14. Minimizing Digital Bus Length                          | 61 |

| Figure 5–15. Resistance and Inductance as Functions of Frequency    | 61 |

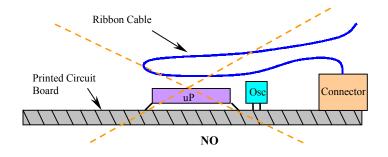

| Figure 5–16. Crystal/Oscillator placement                           | 62 |

| Figure 5–17. Transistor Circuit Routing                             | 64 |

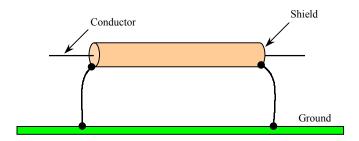

| Figure 5–18. Shielding of Low-Frequency Signals                     |    |

| Figure 5–19. Shielding of High-Frequency Signals                    | 66 |

| Figure 5–20. Packaging Considerations Affecting RE and CE           | 67 |

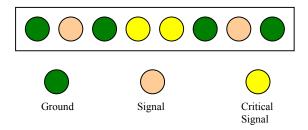

| Figure 5–21. Use of Interspersed Grounds                            | 68 |

## TABLE OF TABLES

| Table 2–1. FCC and Ford RE Limits                     | 12 |

|-------------------------------------------------------|----|

| Table 3–1. Frequency and Impedance                    | 17 |

| Table 3–2. Wavelength as Function of Frequency        | 20 |

| Table 3–3. Frequency Allocation and Usage Designation | 21 |

| Table 3–4. Sample RE Data                             | 26 |

| Table 3–5. Ford RE Limit vs. Sample Data              | 28 |

| Table 3–6. Mutual Capacitance in Two Wires            | 32 |

| Table 3–7. Relative Permeability of Common Metals     | 39 |

| Table 3–8. Resistance in Wires                        | 40 |

| Table 3–9. Resistance in Grounding Straps             | 41 |

| Table 3–10. Inductive Reactance vs. Frequency         | 42 |

| Table 3–11. Impedance in Solid Copper Wires           | 43 |

| Table 3–12. Self-Inductance in Wires                  | 45 |

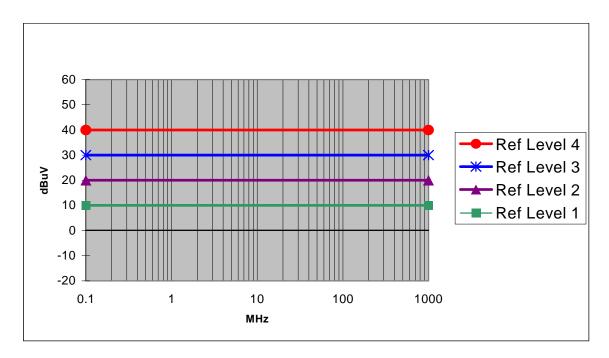

| Table 4–1. Rating Levels for IC's                     | 49 |

| Table 6–1. Analysis of EMC Testing                    |    |

|                                                       |    |

## TABLE OF EQUATIONS

| Equation 3–1.  | Wavelength                               | . 19 |

|----------------|------------------------------------------|------|

| Equation 3–2.  | Duty Cycle                               | . 23 |

| Equation 3–3.  | Bandwidth                                | . 23 |

| Equation 3–4.  | Current in Square Waves                  | . 24 |

| Equation 3–5.  | Far-Field Radiated Emissions             | . 24 |

| Equation 3–6.  | Radiated Emissions from a loop           | . 25 |

| Equation 3–7.  | Far Field strength                       | . 25 |

| Equation 3–8.  | Common Mode current                      | . 27 |

| Equation 3–9.  | E-field strength due to CM current       | . 27 |

| Equation 3–10. | CM current.                              | . 28 |

| Equation 3–11. | Mutual Capacitance in wires              | . 31 |

| Equation 3–12. | Mutual Capacitance                       | . 32 |

| Equation 3–13. | Voltage Noise due to capacitive coupling | . 33 |

| Equation 3–14. | Mutual Inductance                        | . 34 |

| Equation 3–15. | Noise voltage due to inductive coupling  | . 35 |

| Equation 3–16. | Noise voltage due to inductive coupling  | . 35 |

| Equation 3–17. | Inductive Coupling in twisted-wire pair  | . 36 |

| Equation 3–18. | Shielding effectiveness                  | . 38 |

| Equation 3–19. | Absorption loss                          | . 38 |

| Equation 3–20. | Resistance in Copper                     | . 40 |

| Equation 3–21. | Inductive Reactance                      | . 41 |

| Equation 3–22. | Inductance in rectangular conductor      | . 41 |

| Equation 3–23. | Inductance in parallel wires             | . 42 |

| Equation 3–24. | Self-Inductance                          | . 44 |

| Equation 3–25. | Inductance in air-core inductors         | . 45 |

| Equation 3–26. | Inductance in toroids                    | . 45 |

#### ACRONYMS AND ABREVIATIONS

AC**Alternating Current** AWG American Wire Gauge BCI **Bulk Cable Injection**

BWBandwidth

CE **Conducted Emissions** CI **Conducted Immunity** CM Common Mode

**CMOS** Complementary Metal-Oxide Semiconductor

**CPU** Central Processing Unit CS Conducted Susceptibility

dB decibel

DC Direct Current DM Differential Mode EC **European Community** Electrical/Electronic E/E

**EMC** Electromagnetic Compatibility

Electromagnetic Effect **EME** Electromagnetic Interference **EMI**

**EPDS Electrical Power Distribution System**

Electronic Subsystem Component (Device Under Test) ESC

**ESD** Electro Static Discharge

European Union EU

**Federal Communication Commission FCC**

FET Field Effect Transistor **FMC** Ford Motor Company

**HSIC** High Speed Integrated Circuit

IC **Integrated Circuit**

International Electrotechnical Commission **IEC**

I/O Input/Output

**International Standards Organization** ISO

Large State Integration LSI **MCU** Micro-Controller Unit Metal-Oxide Varister MOV

NB Narrowband

PCB Printed Circuit Board **PWB** Printed Wiring Board PWM Pulse Width Modulation RE Radiated Emissions RF Radio Frequency RI Radiated Immunity RS Radiated Susceptibility

Society of Automotive Engineers SAE Transverse Electromagnetic (Cell) **TEM**

### **PART I: PREFACE**

#### 1. INTRODUCTION

Due to the tremendous increase in the use of electronic devices, ensuring Electromagnetic Compatibility (EMC) of a full system in its early design phase is becoming one of the major technical issues, especially for automotive manufacturers. Safe and reliable operation must be guaranteed and legal requirements have to be satisfied. From both car-makers and suppliers sides, the electromagnetic problems occur either when integrating electronic devices in their operating environment (cross-coupling, interference) or when dealing with the related EMC regulations (simulation of radiating phenomena due to Common-Mode currents induced on attached cables). As digital devices become smaller and perform at greater speeds, their emissions increase, making a thorough understanding of Electromagnetic Interference (EMI) essential for everyone in electrical engineering and design today.

This document contains design guidelines to aid in achieving EMC (Electromagnetic Compatibility) in automotive electrical/electronic components and systems. None of the material presented herein is new. On the contrary, it is based on well-established EMC measures and techniques, and on specific automotive EMC experience accumulated over the years within Ford Motor Company. The "EMC design guide for PCB" simply attempts to collect that wisdom together.

It should be pointed out that Parts 1 through 6 of this document are meant to be strictly informative. For example, the various design techniques presented in Section 5 are derived from a set of fundamental principles, and although the techniques aid each other in achieving electromagnetic compatibility, they don't guarantee it. Suppliers are ultimately responsible for assuring full Ford EMC compliance of their products.

Completion of Part 7 is mandatory.

The reader is encouraged to forward any comments, questions or suggestions regarding this document to the following e-mail address:

mailto:contact@fordemc.com

### **PART II: GENERAL EMC**

### 2. EMC OVERVIEW

The application of electronic components and devices is increasing in all area of consumer products as well as within the industrial production environment. This provides an electromagnetic environment with an increasing overall noise floor due to digital control applications in virtually any niche of daily life and an ever increasing demand on mobile telecommunications facilities.

The noise margin – observations in the early 90's have revealed an increase of approximately 3 dB per year – poses an increasing threat onto the immunity margins of the electronic components. In contrast to the aggression, the immunity margin is falling due to the drastic increase in the complexity of the components, calling for a reduction in power consumption in order to control thermal effects for instance. The attempt of controlling costs also leads towards a trend of replacing solid metal housings with plastics or composites, which decrease shielding capabilities.

In summary, the trend in Electronics' applications, a raise of a harsh electromagnetic ambient has to be noticed with a loss of safety margins, making applications more susceptible to electromagnetic interference and calling for regulations to keep the problems arising under control

#### 2.1. The Elements

Electromagnetic radiation due to the operation of electrical or electronic devices may be grouped into two types:

- Intentional Emissions

- Unintentional Emissions

Examples of the first type are television and radio broadcasting systems, communication and radar systems, and transmitters for navigational purposes. However, even when performing properly such equipment may also generate undesired electromagnetic emissions of the second type. This might interfere with the system itself or the overall emissions might affect other sensitive equipment nearby. In order to control these kind of effects frequency management is necessary in the first place due to the fact that a certain part of the emission profile contains valuable information and is intended to be there.

Electronic components provide a frequency band and due to non-linearities in active devices unintentional harmonics may be created, and modulations might occur. In general, sources of coherent electromagnetic emission at a given frequency or within a specified frequency band are intentional transmitters, but both coherent as well as non-coherent emission bear the potential for electromagnetic interference problems. Electromagnetic emissions may thus be divided into:

- Radiation due to radio transmitters and similar nearby electrical or electronic equipment

- Transient environment caused by electrical switching operations, electrostatic discharge and lightning

#### 2.2. The Environment

There are two fundamental classes of transfer types:

- Analogue

- Digital

The difference is not only due to the information coding but with regard to EMC the main difference is due to the quality and vulnerability.

Analogue circuitry reacts immediately on perturbations but the effects remain within relatively small limits, they might cause a rectification and possibly a drifting of the operation point. Typically, analogue circuitry recovers from the perturbation by turning back towards the regular operation. The operational safety margin corresponds to the signal to noise ratio.

In contrast to the above, digital circuits provide a 'large' safety margin because of the switching thresholds for the different states. Hence a digital application appears more robust than an analogue one. However, the move towards low voltage logic, 3V and even less, will reduce these margins. Another difference lies in the quality of failure which might be quite unpredictable for digital application – a bit might switch and cause a system to malfunction in the case of switching to a defined state or to hang because of turning into an undefined state.

Most problems associated with digital circuits are due to the high bandwidth inherited from the high-speed clocks and edge rates. Rise times in the realm of a few nanoseconds are equivalent with bandwidths well above 300 MHz range and the increase of the clock rates will drive this into the microwave range. In other words, higher bandwidths increase both emissions and the susceptibility of the circuitry.

This issue is fundamental to the functioning of the designed circuitry and comprises mainly the aspects of internal or intra-system EMC and Signal Integrity. Intra-system EMI includes problems due to mixed technologies, e.g. analogue and digital, or electromechanical and digital. In the former case, the noise created by the digital circuitry due to the impulsive nature of the power demands might cause some jamming of the analogue circuits. In the latter case, the noise due to motors and switching relays typically causes jamming of the digital circuits. In the case of high speed digital application the digital circuitry might also cause some malfunctions due to crosstalk between such high speed applications and reflections on the interconnects. A particular characteristic of analogue components is that they typically operate at low frequencies and low levels and in addition show very high input impedances.

### 2.3. Regulations and Standards

E/E devices on Ford products must comply with a variety of requirements mandated by:

- Federal Communications Commission (FCC) regulations

- Ford EMC specifications

- European Community (EC) EMC Directive

Within the United States, the FCC is responsible for radio spectrum allocations and assignments outside the federal government sector. FCC 15J is the FCC document that controls the interference potential of electronic computing devices. A computing device is defined as any electronic device or system that uses digital techniques. This encompasses any device that intentionally generates and utilizes frequencies in excess of 10 kHz. The FCC regulates transmitters and receivers under a different rule.

Vehicle radios and remote controlled transceivers must comply with FCC regulations. Most other E/E modules designed exclusively for a vehicle use, have Section 1 exemption from FCC regulations. However, Ford has a policy of voluntary compliance for all modules.

The FCC regulates the amount of radiated EMI from an E/E device. Table 2–1 compares the maximum radiated electric fields allowed by Ford and the FCC. The table shows the electric field strength in  $dB\mu V/m$  and  $\mu V/m$ . FCC Class B limits are for consumer-type computing devices.

Ford EMC requirement limits are derived from a variety of SAE, International Standards Organization (ISO), and EC standards. The latest version of the primary Ford component level EMC specification is available on line at <a href="https://www.fordemc.com">www.fordemc.com</a>.

By inspection of Table 2–1, it is evident that the Ford limits are much more stringent than those of FCC; especially when one considers that FCC limits are measured 3 meters away from the radiating device while Ford measurements are taken at 1 meter. The Ford limits are more restrictive for two primary reasons:

- Radiating devices on the vehicle are closer to radio transceivers on board the vehicle

- A vehicle contains many radiating devices

Table 2-1. FCC and Ford RE Limits

| Ford RE limits (ES-XW7T-1A278-AB) |            |         |  |  |  |  |

|-----------------------------------|------------|---------|--|--|--|--|

|                                   | (1 meter)  |         |  |  |  |  |

| Frequency (MHz)                   | μV/m       | dBμV/m  |  |  |  |  |

| 0.15 - 25                         | 31.6       | 30      |  |  |  |  |

| 25 - 200                          | 3.2        | 10      |  |  |  |  |

| 200 – 1000                        | 3.2 - 15.8 | 10 - 24 |  |  |  |  |

| FCC Class B RE limits             |            |         |  |  |  |  |

|                                   | (3 meters) |         |  |  |  |  |

| 30 - 88                           | 100        | 40      |  |  |  |  |

| 88 – 216                          | 150        | 43.5    |  |  |  |  |

| 216 – 1000                        | 200        | 46      |  |  |  |  |

Outside the United States, the European Community (**EC**) has recently passed a uniform EMC directive. Any electronic product and vehicle manufactured in the United States or elsewhere must fulfill the EC regulations before they can be marketed in Europe. The main EC EMC Directive for automotive is 95/54/EC (and UN-ECE R10.02).

#### 2.4. Elements of EMI

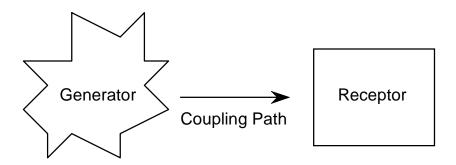

Figure 2–1 shows the elements of an EMI situation. A generator is an E/E device that produces EMI. A receptor is an E/E device that receives or couples in EMI. A coupling path allows EMI from the generator to produce an undesired response in the receptor.

Figure 2–1. Elements of EMI

There are 3 ways in which to minimize the EMI:

- Reduce the noise from the generator

- Alter the coupling path

- Improve the immunity of the receptor

Reducing the noise from the generator may include reducing the generator circuit area, using a slower rise and fall time of a switching signal, using slower digital logic, reducing the circuit current, re-orienting the generator circuit on PCB, filtering, and/or shielding.

Often the designer must contend with the generator noise. This leaves either reducing the coupling path or hardening the receptor. Minimizing the coupling path may include moving the receptor away from the generator, re-orienting the receptor and/or generator on PCB, or shielding the receptor or generator.

Increasing the immunity of the receptor may include reducing the receptor circuit area, re-orienting the receptor circuit on PCB, using less susceptible electronic components, changing the impedance of the circuit, filtering, and/or shielding.

### PART III: DESIGN APPROACH

### 3. OVERVIEW

Each unit of the overall system must be designed to meet the EMC Specified Limits. These EMC requirements can be divided into two primary categories: immunity (susceptibility) requirements and emission requirements.

### 3.1. Design Approach for Immunity (Susceptibility)

The different susceptibility requirements differ in threat energy and frequency content, although there is considerable overlap of these parameters among the test requirements. Of these requirements, the two susceptibility requirements that impact the design the most are the **Radiated Immunity** (**RI**) requirements, and the effects of **Electrostatic Discharge** (**ESD**) requirements.

### 3.1.1. Design Approach for Radiated Immunity

The Radiated Immunity threat is characterized by moderately high energy and very high frequency that can propagate in unexpected ways to circuit components, causing unexpected effects. The frequency range of radiated immunity can be found in the latest version of the component level spec at <a href="www.fordemc.com">www.fordemc.com</a>. Historic component level RI data shows that the band of frequencies most likely to cause radiated immunity-related problems for electronic controllers in an automotive environment is 10 MHz to ~ 900 MHz. The overall design approach for Radiated Immunity is to keep RI interference contamination out of the ESC (Electronic Subsystem Component) by removing it from signal and power lines entering the ESC (at ESC entry point).

### 3.1.2. Design Approach for ESD

The ESD threat is primarily characterized by short duration, high energy pulses that can damage I/O components or cause circuit upset. The frequency range of ESD is from DC to ~300 MHz (DC - 10MHz for lightning). The design approach for Radiated Immunity will also help prevent circuit upset caused by the high frequency components of ESD. However, ESD protection requires additional measures to prevent damage from the low frequency, high energy content of the induced ESD threats. Therefore, the overall design approach for ESD protection is to maintain high impedance, with respect to chassis ground, on signal and power lines to the ESC to minimize the effect of damaging ESD current and the corresponding energy from entering the ESC.

### 3.2. Design Approach for Controlling Radiated and Conducted Emissions

The purpose of emission requirements is to provide a level of assurance that the equipment will not produce electromagnetic emissions great enough to adversely affect the performance of other equipment in the vehicle (primarily communication, audio and electronic vehicle control systems). Fortunately, many of the design techniques used to

prevent Radiated Immunity and ESD interference energy from entering the ESC also prevent internally generated emissions from leaving the ESC. However, there are several additional design techniques used to minimize electromagnetic emissions from the ESC. The overall design approach for reducing emissions from the ESC is to prevent or minimize the generation of high frequency interference voltage and currents as close to the interference source as possible. The objective is to stop emissions at their source, before they can cross couple to other circuits and signal lines that cannot be easily filtered.

### 3.3. Ground System

A low inductance ground system is the most important element in designing a PCB for EMC. There are three types of ground structures on PCB:

- Minimal

- Ground Grid

- Ground Plane

The **minimal** ground structure connects the ground points on PCB with random, high inductance connections to other ground points. This is the least desirable method from an EMC standpoint.

Maximizing the ground area on a PCB minimizes the inductance of the ground system, which in turn minimizes radiated emissions. In addition, the maximized ground area provides shielding to improve radiated immunity of the PCB.

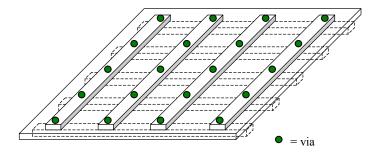

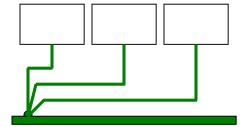

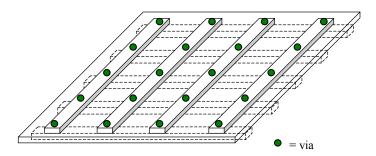

Figure 3–1 shows the ground grid structure. A **ground grid** provides many lower-inductance paths for current to return to its source.

Figure 3–1. Ground Grid

Ground grid is achieved by connecting vertical and horizontal lines on opposite sides of PCB with vias. A **via** is a plated through hole that interconnects two or more PCB layers. Via connections also allow a signal track to 'jump over' a ground grid trace. All two layer PCBs should use a ground grid. In addition, multi-layer PCBs should use ground grids even if they employ one or more ground planes.

A ground plane is the lowest impedance conductor that serves as a current return and a signal reference. *A ground plane is the ideal ground system*. It offers the lowest possible inductance for current to return to its source. A properly designed ground grid is the next best ground system.

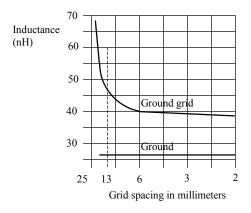

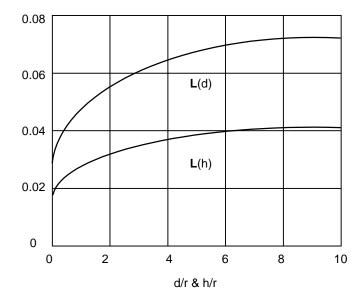

Figure 3–2 compares the inductance of a ground grid and ground plane. The graph displays the inductance in nanohenries (nH) versus grid spacing in millimeters. To effectively lower the inductance of a ground grid the grid spacing must be less than 0.5 inches (~13 mm). Figure 3–2 shows that when the grid spacing equals 0.5 inches, the ground grid inductance has significantly decreased. Reducing the grid spacing further lowers the inductance.

Figure 3–2. Inductance of Grounds

The inductance of a ground grid approaches but can never equal the inductance of a ground plane. They have equal inductances only when the grid spacing equals zero (when the ground grid becomes a ground plane).

Table 3–1 shows the impedance versus frequency for PCB tracks and ground planes. The ground plane is square and made of one-ounce copper (0.035 mm thick). The track is also 1 oz. copper with width of 1.0 mm and length 10.0 mm. These impedance calculations do not take into account the mutual inductance between a signal track and ground plane which would decrease the total impedance.

Table 3–1 indicates that the track has significantly more impedance than the ground plane due to a larger inductance. Ground inductance generates ground noise. This is the reason why ground planes generate less noise than a minimal ground system.

When high frequencies flow through the larger inductances of a minimal ground system they generate voltage drops within that system. Often this is the source of radiated emissions from a PCB. Ground noise voltages force EMI currents to flow out onto the wire harness that connects to the PCB. Moreover, the wires harness is usually much longer than the PCB, and thus it radiates more efficiently.

Table 3–1. Frequency and Impedance

| Frequency | Ground plane impedance | Track<br>impedance      |  |

|-----------|------------------------|-------------------------|--|

| 100 Hz    | 574 μΩ                 | $5.74~\mathrm{m}\Omega$ |  |

| 1 kHz     | 574 μΩ                 | 5.74 mΩ                 |  |

| 10kHz     | 574 μΩ                 | 5.76 mΩ                 |  |

| 20 kHz    | 574 μΩ                 | 5.81 mΩ                 |  |

| 50 kHz    | 574 μΩ                 | 6.14 mΩ                 |  |

| 100 kHz   | 574 μΩ                 | 7.21 mΩ                 |  |

| 500 kHz   | 576 μΩ                 | 22.5 mΩ                 |  |

| 1 MHz     | 582 μΩ                 | $44~\mathrm{m}\Omega$   |  |

| 2 MHz     | 604 μΩ                 | 87.5 mΩ                 |  |

| 5 MHz     | 736 μΩ                 | $218~\mathrm{m}\Omega$  |  |

| 10 MHz    | 1.04 mΩ                | $437~\mathrm{m}\Omega$  |  |

| 20 MHz    | 1.61 mΩ                | 874 mΩ                  |  |

| 50 MHz    | 2.62 mΩ                | 2.18 Ω                  |  |

| 100 MHz   | 3.69 mΩ                | 4.37 Ω                  |  |

| 200 MHz   | 5.22 mΩ                | 8.74 Ω                  |  |

| 500 MHz   | 8.26 mΩ                | 21.8 Ω                  |  |

| 1 GHz     | 11.6 mΩ                | 43.7 Ω                  |  |

Signal grounds usually fall into one of the three categories:

- Single-point ground

- Multi-point ground

- Hybrid ground

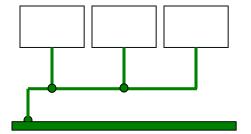

Single point grounds, (Figure 3–3), with regards to noise, are very undesirable because of the series connection of all the individual circuit grounds. At high-frequencies the inductances of the ground conductors increase the ground impedance. A single-point ground is preferable below 1 MHz. Between 1 and 10 MHz a single point-ground can usually be used, provided the length of the longest ground conductor is less than one-twentieth of a wave-length to prevent emissions and to maintain a low impedance.

Figure 3-3. Single-Point Ground

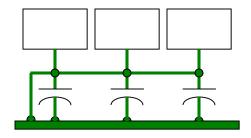

Multi-point grounds, (Figure 3–4), have very low ground impedance and should be used at high frequencies and in digital circuitry. The low impedance is due primarily to the lower inductance of the ground plane. The connection between each circuit and the ground plane should be kept as short as possible to minimize their impedance. Multi-point grounds should be avoided at low frequencies since ground currents from all circuits flow through a common ground impedance – the ground plane.

Figure 3-4. Multi-Point Ground

A hybrid ground, (Figure 3–5), is one in which the system grounding configuration appears differently at different frequencies – a single-point ground at low frequencies, and a multi-point ground at high frequencies. When different types of circuits (low-level analog, digital, noisy, etc.) are used in the same system or on the same PCB, then each must be grounded in a manner appropriate for that type of circuit. The different ground circuits should be tied together, usually at a single point.

Figure 3-5. Hybrid Ground

### 3.4. Wavelength and Frequency

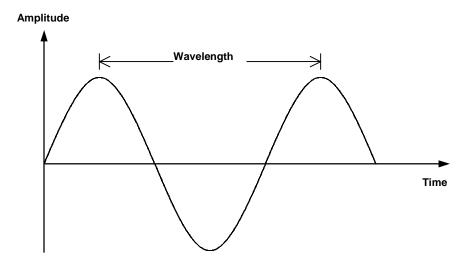

All electrical signals travel as waves with a finite velocity. Figure 3–6 shows the amplitude plot of a wave as a function of time. Its **wavelength** is the distance between any two equivalent points on the waveform.

Figure 3–6. Wavelength of an Electrical Signal

The propagation medium determines the wave's velocity. In space a wave travels at the speed of light c ( $c = 3 \times 10^8$  meters/second). However, the wave travels more slowly through wires or printed circuit board tracks (approx. 0.6 the speed of light).

Equation 3–1 relates wavelength ( $\lambda$ ) to frequency in free space or in air. Table 3–2 shows that the wavelength and frequency are inversely proportional. Consequently, as the frequency increases, the wavelength will decrease.

$$\lambda = \frac{300}{f \, (MHz)} \quad [\text{meters}]$$

### Equation 3–1. Wavelength

The atmosphere contains many electromagnetic fields generated by transmitters, which operate in a range from a few kilohertz to many gigahertz. Table 3–3 shows some of the frequency spectrum allocations in the United States (US), Europe (E), and Japan (J). All undesignated sources are in the United States.

Table 3–2. Wavelength as Function of Frequency

| Frequency | λ         |

|-----------|-----------|

| 10 Hz     | 30,000 km |

| 60 Hz     | 5,000 km  |

| 100 Hz    | 3,000 km  |

| 1 kHz     | 300 km    |

| 50 kHz    | 6 km      |

| 100 kHz   | 3 km      |

| 500 kHz   | 600 m     |

| 1 MHz     | 300 m     |

| 10 MHz    | 30 m      |

| 100 MHz   | 3 m       |

| 1 GHz     | 30 cm     |

| 10 GHz    | 3 cm      |

It is crucial that the E/E devices installed in a vehicle are immune to the fields produced by transmitters such as those listed in Table 3–3. In addition, the vehicle's E/E devices must not generate emissions that interfere with the intended receivers of these transmitters.

Table 3-3. Frequency Allocation and Usage Designation

| Source           | Frequency<br>(MHz) | Typical radiated power (kW) |

|------------------|--------------------|-----------------------------|

| AM (E)           | 0.15 - 0.285       | 320                         |

| AM (E & J)       | 0.525 - 1.605      | 600 & 500                   |

| AM (US)          | 0.53 - 1.71        | 50                          |

| Amateur          | 1.8 - 29.7         | 0.16 (mobile)               |

| Citizens band    | 26.9 – 27.4        | 0.004                       |

| Amateur          | 28 - 30            | 0.2 (mobile)                |

| Land mobile      | 29 – 54            | 0.1                         |

| Amateur          | 50 – 54            | 0.2 (mobile)                |

| TV low VHF       | 54 – 88            | 100                         |

| Land mobile (E)  | 65 – 85            | 0.1                         |

| FM (J)           | 76 – 90            | 44                          |

| FM (US & E)      | 88 – 108           | 105                         |

| Aircraft         | 108 – 136          | 1                           |

| Land mobile (E)  | 120 – 160          | 0.1                         |

| Land mobile      | 132 – 174          | 18 – 100                    |

| Land mobile (J)  | 142 – 170          |                             |

| Amateur          | 144 – 148          | 0.2 (mobile)                |

| TV high VHF      | 174 – 216          | 316                         |

| Land mobile      | 216 – 222          | 0.2                         |

| Amateur          | 222 – 225          | 0.1 (mobile)                |

| Land mobile (J)  | 335 – 384          |                             |

| Land mobile      | 406 – 512          | 0.1                         |

| Land mobile (J)  | 450 – 470          |                             |

| Amateur          | 430 – 450          | 0.1 (mobile)                |

| TV UHF           | 470 - 806          | 5000                        |

| Land mobile      | 806 – 947          | 0.035                       |

| Cellular (AMPS)  | 806 – 947          | 0.003                       |

| Amateur, LM, GPS | 1200 – 1600        |                             |

| Cellular (PCS)   | 1700 - 2000        | 0.003                       |

| Bluetooth        | 2300 - 2500        |                             |

### 3.5. Frequency Domain of Digital Signals

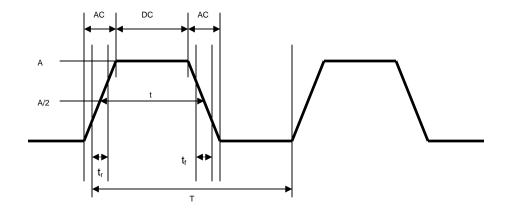

A typical square wave is shown in Figure 3–7.

Figure 3-7. Elements of Digital Signal

A square wave has an AC component during the transition times and a DC component during the steady state. The AC current contains all of the frequency components of the square wave. In addition to the fundamental frequency, a digital signal also contains **harmonic frequencies** which are integer multiples of the fundamental frequency. For example, a digital signal with a fundamental frequency of 10 MHz has harmonic frequency components at 20, 30, 40, ... MHz. Therefore, digital signal current flows at DC and at 10, 20, 30, 40, ... MHz.

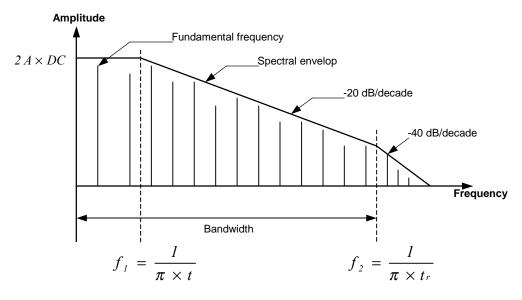

The signal spectrum is a plot of the fundamental and harmonic frequencies. Figure 3–8 shows the signal spectrum for a square wave in amplitude versus frequency graph.

Figure 3–8. Digital Signal Spectrum

The **spectrum envelope** is a mathematical amplitude limitation of the spectral components of a digital signal. The maximum amplitude of the spectrum envelope equals  $2A \times DC$ , where A is the peak amplitude of the square wave, and DC is a duty cycle (often denoted as  $\delta$ ), then:

$$\delta = \frac{t}{T}$$

### Equation 3–2. Duty Cycle

Where, t is the time that a square wave stays above one-half the maximum amplitude. The spectrum envelope falls off at 20 dB per decade at frequencies above  $f_1 = 1/\pi t$ .

The signal **rise time**  $(t_r)$  is the time that a digital signal takes to rise from 10% to 90% of its value (refer to Figure 3–7). Equation 3–1 states that the rise time determines the **bandwidth** (BW) of the signal. Use the signal **fall time**  $(t_f)$  if it is faster than the rise time, which it usually is. The spectrum envelope falls of at 40 dB per decade at frequencies above  $f_2 = 1/\pi t_r$ .

The magnitude (M) in dB at  $> f_i$  is computed as follows:

$$M(f_{1} < f < f_{2})_{dB} = M_{1} = 20 \log(2A\delta) - 20 \log(\frac{f}{f_{1}})$$

$$M(f > f_{2})_{dB} = M_{dB} = (f = f_{2}) - 40 \log(\frac{f}{f_{2}})$$

$$BW = \frac{1}{\pi \times t_{r}}$$

### Equation 3–3. Bandwidth

In Figure 3–8, the bandwidth contains 99% of the spectral energy of the signal.

The spectrum of the square wave in Figure 3–8 is also its Fourier series. Fourier theory states that a periodic signal can be expressed in terms of weighted sum of harmonically related sinusoids.

Equation 3–4 gives the amplitude for the fundamental and harmonic currents in the Fourier series of a square wave.

$$|I_n| = 2I_{max}\delta \frac{\sin(n\pi\delta)}{n\pi\delta} \times \frac{\sin(n\pi\frac{t_r}{T})}{n\pi(\frac{t_r}{T})}$$

[Amperes]

### Equation 3–4. Current in Square Waves

Where,  $1 \le n \le \infty$ ,  $I_{max}$  is the maximum current.

It is assumed that the rise and the fall times of a square wave are equal. A square wave with  $\delta = 0.5$  has only odd numbered harmonic with the first current harmonic,  $I_1 = 0.641I_{max}$

#### 3.6. Radiated Emissions Predictions

For intentional transmitters (e.g. broadcast towers), the electromagnetic field next to a transmitting antenna is very complex. This field is called the **near field**. However, the field becomes an uniform plane wave some distance from the antenna. This field is called the **far field**. The near to far field transition (equation below) occurs at about one-sixth of a wavelength from the transmitting antenna.

Near to far field transition:

$$\approx \frac{\lambda}{2\pi}$$

[meters]

This next equation, Equation 3–5, shows how to calculate the far-field radiated emissions from any RF transmitter:

$$E = \frac{\sqrt{30 \times P_t}}{r} \quad \text{[Volts/meter]}$$

### Equation 3–5. Far-Field Radiated Emissions

For example, the far field for a FM transmitter at 100 MHz occurs at about one-half meter. The transmitter electric field strength 100 meters (r) away from the transmitter ( $P_t$ =250 kW) equals 27.4 volts per meter.

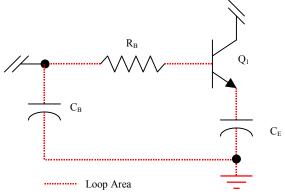

For unintentional noise sources, E/E designers should consider circuit loops.

Equation 3–6 gives the maximum radiated emission in  $dB\mu V$  per meter from a small loop. **Differential mode (DM)** current,  $I_n$ , is the normal signal or power current that flows in a loop.

$$E_{DM} = 20 \log_{10} \left( 2.63 \times 10^{-8} \frac{A \times f_n^2 \times I_n}{r} \right) \text{ [dB}\mu\text{V/m]}$$

### Equation 3-6. Radiated Emissions from a loop

Where, A is the area of a small loop

$f_n$  is the spectral signal frequency  $I_n$  is the spectral signal current

r is the distance from the small loop to the measurement antenna or the distance between a radiating generator loop and a receptor circuit.

Equation 3–7 predicts the maximum electric field in the far field from a small loop. It is accurate when the loop perimeter is less than one-quarter wavelength, and approximate for larger loops. In the near field multiply Equation 3–6 by Equation 3–7.

$$\vec{E}_{far\_field} = \sqrt{1 + \left(\frac{\lambda}{2\pi \times r}\right)^2}$$

### Equation 3-7. Far Field strength

Table 3–4 shows the radiated emissions at 1 meter from a PCB circuit with the following values:

Area =  $5.0 \times 10^{-4} \text{ meter}^2 (5 \text{ cm} \times 1 \text{ cm})$

Fundamental frequency = 10 MHz

$I_{\text{max}} = 10 \text{ mA}$

Rise time = fall time = 5 ns (typical high-speed CMOS)

Table 3–4. Sample RE Data

| Frequency (MHz) | Current  | Electric field (µV/m) | Electric field (dBµV/m) |

|-----------------|----------|-----------------------|-------------------------|

| 10              | 6.34 mA  | 40.7                  | 32.2                    |

| 30              | 2.04 mA  | 45.5                  | 33.2                    |

| 50              | 1.15 mA  | 52.1                  | 34.3                    |

| 70              | 0.737 mA | 47.5                  | 33.5                    |

| 90              | 0.494 mA | 52.6                  | 34.4                    |

| 110             | 0.331 mA | 52.7                  | 34.4                    |

| 130             | 0.214 mA | 47.6                  | 33.5                    |

| 150             | 0.127 mA | 37.6                  | 31.5                    |

| 170             | 63.7 μΑ  | 24.2                  | 27.7                    |

| 190             | 17.6 μΑ  | 8.4                   | 18.4                    |

Recall from Table 2–1 in Section 2.3 that the Ford RE limit from 1.8 MHz to 200 MHz is  $10 \text{ dB}\mu\text{V}$  per meter. Table 3–4 shows this PCB circuit would fail the RE limit set by ES-XW7T-1A278-AB spec at all of the spectral frequencies.

The predominant contribution to radiated emissions is due to the so-called **Common-Mode (CM)** current flowing in cables attached to an electronic device, and acting as efficient antennas in the frequency range which is considered (up to 2.5 GHz). The CM current is simply the net current in the cable. Ideally, this net current should vanish, because each current that enters the electronic device through the cable, also leaves it through the cable. Due to **parasitic effects**, this balance is disturbed and a CM current results. This CM current determines the amount of radiation because in the balanced case, the radiated field of each of the different wires in the cable almost cancel each other. Since only the net current in the cable is important, the cable may be considered as one single wire carrying this CM current. In automotive electronic devices several hundred different signals contribute to the overall CM current on attached cables. In order to estimate the contribution of the different nets, the basic CM current generation principle has to be understood and two basic mechanisms, i.e. current-driven and voltage-driven current excitation, need to be considered.

The **current-driven** mechanism is due to the partial inductance of the return currents in the ground plane, which produces a voltage drop across the ground plane, and injects the CM current into the attached cable.

The second mechanism is **voltage-driven**, because the signal voltage directly drives the CM current through the parasitic antenna capacitance.

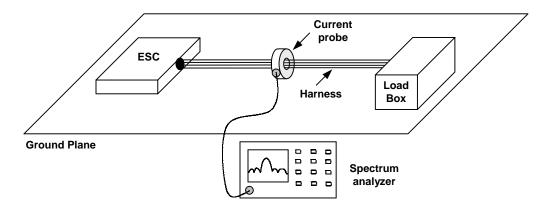

Figure 3–9 shows the setup for measuring CM currents from an electronic device. The cable (wire harness) connects the electronic device to a load box that contains all of the input circuitry and loads the device drives. A two-meter (2 m) harness is the standard length used for measuring radiated emissions from an electronic device at Ford. The electronic device, harness, and load box are placed over a ground plane.

Figure 3–9. Setup for Measuring CM Currents

The RF current probe measures the net current that exits on the harness. Equation 3–8 gives the CM current calculation as:

$$I_{CM} = \frac{V_{SA}}{Z_{*}}$$

[Amperes]

### Equation 3–8. Common Mode current

Where,  $V_{SA}$  is the voltage that the spectrum analyzer measures  $Z_t$  is the probe transfer impedance in ohms

Equation 3–9 gives the electric field in  $dB\mu V$  per meter for a short wire (relative to wavelength) in free space due to the spectral amplitude of current  $I_n$ . Use this equation to estimate the electric field emissions due to CM current.

$$E_{CM} = 20 \log_{10} \left( 1.26 \frac{I_n L f_n}{r} \right) \quad [dB\mu V/m]$$

### Equation 3–9. E-field strength due to CM current

Where,  $I_n$  is the spectral signal current

L is the length of the cable

$f_n$  is the spectral signal frequency

*r* is the distance from the wire to a measuring antenna or the distance between a radiating generator wire and a receptor circuit.

Solving Equation 3–9 for the current gives Equation 3–10:

$$I_n = \frac{0.4 \times E}{f_n} \quad [\mu \text{Amperes}]$$

### Equation 3-10. CM current

Where, E is in  $\mu V/m$  $f_n$  is in MHz

This equation includes the factors from ES-XW7T-1A278-AB specification, where the wire is two (2) meters long and the antenna distance from the wire harness is one (1) meter. It takes much less CM current than DM to result in the same Radiated Emissions.

Table 3–5 shows the maximum CM current that can flow on a single wire to just meet the Ford limit for radiated emissions. To find and measure the maximum CM current move the current probe along the harness length while monitoring the current with a spectrum analyzer.

Table 3–5. Ford RE Limit vs. Sample Data

| Frequency | Ford RE limit   |             | I     |

|-----------|-----------------|-------------|-------|

| (MHz)     | $(dB\mu V/m)^*$ | $(\mu V/m)$ | (µA)  |

| 10        | 30              | 31.6        | 1.3   |

| 30        | 10              | 3.16        | 0.04  |

| 100       | 10              | 3.16        | 0.013 |

| 200       | 10              | 3.16        | 0.006 |

Note: Data obtained using Fischer F33-1 current probe.

### 3.7. Crosstalk

Vehicles contain many conductors such as wires, vehicle sheet metal, PCB tracks, and PCB ground planes. Wires can become a dominant factor since they may couple electromagnetic energy to other wires in the same bundle, and hence into an electronic device (module). **Crosstalk** is the coupling of signals between conductors. Crosstalk can occur through the following mechanisms:

- Common impedance coupling

- Capacitive coupling

- Inductive coupling

<sup>\*</sup> Limits per ES-XW7T-1A278-AB specification

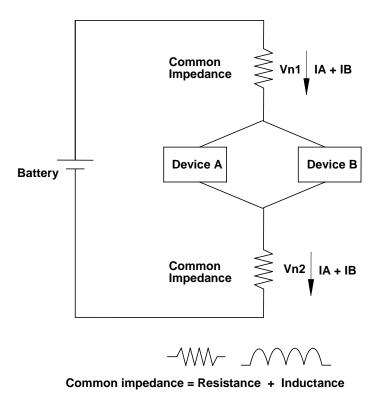

### 3.7.1. Common Impedance Coupling

Common Impedance Coupling exists when two or more circuits share a common conductor to source or sink current. The common impedance is a form of communication between the two circuits. Current passing through the common impedance develops a voltage, which appears directly in the receptor circuit. This shared impedance can occur in the automotive battery feed and ground distributions and shared signal voltage feed and signal returns. Common impedance coupling can cause many problems in PCBs and integrated circuits.

Figure 3–10 shows a common impedance in the positive and negative sides of a battery distribution circuit for two devices, A and B. Current flowing from circuit A raises the ground potential under circuit A and circuit B. Likewise, current flowing from circuit B has the same effect on circuit A. The voltage drop caused by current flow from either circuit changes the ground potential of the other (receptor) circuit. This is a form of communication between devices A and B, which may cause a problem, depending on the sensitivity of the other circuit. The same mechanism of common impedance occurs on the positive side of the battery.

Figure 3–10. Elements of Common Impedance

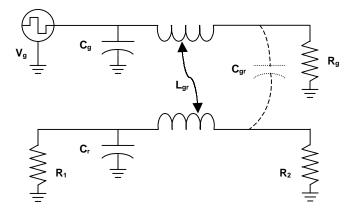

### 3.7.2. Capacitive and inductive coupling

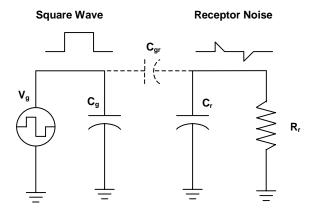

Figure 3–11 shows capacitive and inductive coupling between two circuits.

Figure 3–11. Inductive and Capacitive Coupling Between Two Circuits

Where,  $V_g$  is generator voltage

$C_g$  is the generator capacitance

$\mathbf{R}_{\mathbf{g}}$  is the generator circuit load

$\mathbf{R_1}$  and  $\mathbf{R_2}$  are terminating resistances of the receptor circuit

$C_r$  is the capacitance of the receptor circuit

$C_{gr}$  is the mutual capacitance from the generator to the receptor circuit

$L_{gr}$  is the mutual inductance from the generator to the receptor circuit

### 3.7.3. Capacitive coupling

A signal voltage creates an electric field from wires and PCB traces. Capacitive coupling results from the interaction of a time-varying electric field between a generator and receptor circuit. Figure 3–11 illustrates that capacitive coupling results from a mutual capacitance  $C_{gr}$ . The mutual capacitance provides a path for EMI current to flow from the generator circuit to the receptor circuit.

Figure 3–12 shows the equivalent circuit for the capacitive coupling shown in Figure 3–11.  $R_r$  is the parallel equivalent circuit for  $R_1$  and  $R_2$ . Whenever the generator signal changes, it induces a noise voltage in the receptor circuit. By inspecting Figure 3–12 one can see that capacitive coupling is essentially a differentiator circuit. The presence of  $C_{gr}$  differentiates the square wave to produce the receptor noise voltage.

Figure 3–12. Capacitive Coupling

The amount of noise voltage that the generator circuit induces into the receptor circuit depends on the generator frequency and  $C_{gr}$ , which is largely a function of:

- Parallel length of the two circuits, and

- Separation between the two circuits

Equation 3–11 gives the mutual capacitance in picofarads per inch between two long conductors:

$$\frac{C}{l} = \frac{0.7\varepsilon_{r(eff)}}{ln\left[\frac{d}{r} + \sqrt{l - \left(\frac{2r}{d}\right)^2}\right]} \quad [pF/in]$$

### Equation 3–11. Mutual Capacitance in wires

Where, d is the distance between the center lines of the wires r is the wire radius  $\varepsilon_r$  is the permittivity of the wire insulation material.

The **effective permittivity**,  $\varepsilon_{r(eff)}$  depends on the separation distance. It varies from  $1 < \varepsilon_{r(eff)} < 3.2$

Equation 3–12 gives the capacitance in picofarads per inch between two wires over a ground plane.

$$\frac{C}{l} = \frac{0.7\varepsilon_{r(eff)} \ln\left[1 + \left(\frac{2h}{d}\right)^2\right]}{\left[\ln\left(\frac{2h}{r}\right)\right]^2} \quad \text{[pF/in], for } \frac{2h}{r} >> 1$$

Equation 3–12. Mutual Capacitance

Where, d is the distance between the center lines of the wires

*r* is the wire radius

**h** is the distance between the center lines of the wires and the ground plane (hight)

Table 3–6 shows how mutual capacitance varies between two 18 gauge wires (radius = 0.024 inch) with and without a ground plane -- the ground plane returns the currents of both wires. The ground plane reduces the mutual capacitance between the wires by increasing the self-capacitance – the capacitance to its ground reference – on each wire. Butting wires show an increase in capacitance due to the dielectric constant of the wire insulation (PTFE with an  $E_r$  equal to 2.1).

Table 3-6. Mutual Capacitance in Two Wires

| Separation Distance (inches) | No ground plane (pF) | Ground plane<br>h = 02 in<br>(pF) |

|------------------------------|----------------------|-----------------------------------|

| Wires butting                | 18.77                | 6.28                              |

| 0.1                          | 6.16                 | 3.01                              |

| 0.2                          | 3.99                 | 1.71                              |

| 0.5                          | 2.77                 | 0.53                              |

| 1.0                          | 2.25                 | 0.16                              |

Equation 3-13 gives the noise voltage,  $V_n$  due to capacitive coupling.  $R_f$  is the parallel equivalence of  $R_1$  and  $R_2$ , which equals  $2\pi \times f$ , where f is the frequency or frequencies of  $V_{\varrho}$ .

$$V_n = j\omega \times R_r C_{gr} V$$

whenever  $R_r \ll \frac{1}{j\omega (C_{gr} + C_r)}$

and

$$V_n = \left(\frac{C_{gr}}{C_{gr} + C_r}\right) V_g \quad \text{whenever} \quad R_r >> \frac{1}{j\omega(C_{gr} + C_r)}$$

Equation 3–13. Voltage Noise due to capacitive coupling

To reduce capacitive coupling:

- Decrease the generator frequency

- Decrease the parallel length between the circuits

- Increase the separation between the circuits

- Orient the receptor circuit to the generator circuit at 90°

- Increase  $C_r$

- Decrease  $R_r$

- Shield the generator and/or the receptor circuit

- Place conductors over a ground plane

### 3.7.4. Inductive coupling

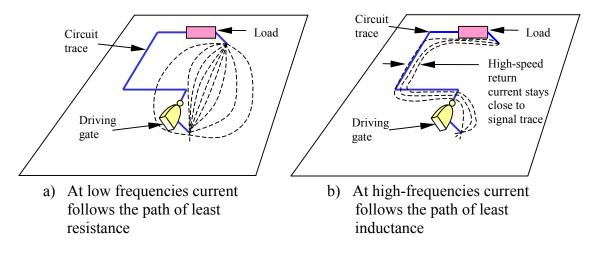

Inductive coupling results from the interaction of a time-varying magnetic field between a generator and receptor circuit. Inductive coupling can occur at low or high frequencies. Crosstalk from inductive coupling is more prevalent when highlevel and fast-rising currents transients are conducted in a low-impedance circuits.

Signal current creates a magnetic field that surrounds the conductor. Figure 3–11 illustrates that conductive coupling results from a mutual inductance  $L_{gr}$ . The mutual inductance provides a path for magnetic flux to couple from the generator circuit to the receptor circuit.

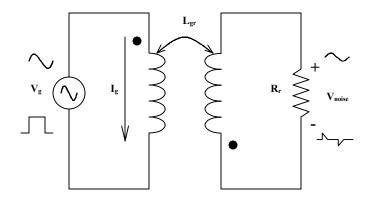

Figure 3–13 shows that inductive coupling is essentially a simple magnetic transformer. The generator circuit is the primary and the receptor circuit is the secondary of the transformer. The figure also illustrates that when  $V_g$  is a sine wave then  $V_{noise}$  is a sine wave as well but with a reduced amplitude. When  $V_g$  is a square wave then  $V_{noise}$  shows noise spikes when the square wave changes.

Figure 3–13. Inductive Coupling

The amount of noise voltage that the generator circuit induces into the receptor circuit depends on the generator frequency and  $L_{gr}$ , which is a function of:

- Receptor and generator area

- Parallel length of the two circuits

- Separation between the two circuits

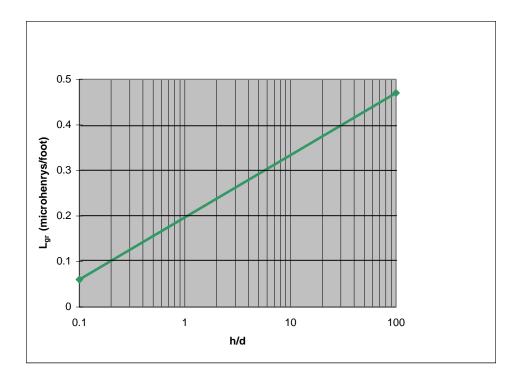

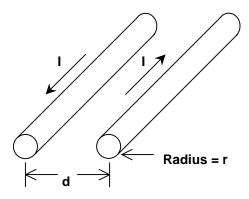

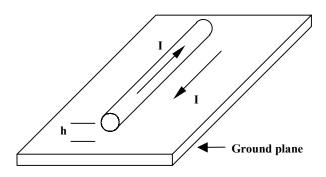

Equation 3–14 gives the mutual inductance in microhenries per inch between two long circular conductors over a ground plane. The ground plane returns the currents of both circuits.

$$\frac{L_{gr}}{l} = 0.00254 \ln \left[ 1 + \left( \frac{2h}{d} \right)^2 \right] \quad [\mu \text{H/in}]$$

### Equation 3–14. Mutual Inductance

Where, **h** is the distance between the conductor centers and the ground plane **d** is the distance between the center lines of the conductors

Figure 3–14 shows mutual inductance in microhenries per foot between two wires over a ground plane, versus the ratio of wire height to wire separation. The figure illustrates that mutual inductance increases as the areas of the generator and receptor circuits, increase.

Figure 3-14. Mutual Inductance Between Two Wires

Equation 3–15 gives induced noise voltage from inductive coupling:

$$N_{noise} = L_{gr} \times \frac{di_g}{dt}$$

Equation 3–15. Noise voltage due to inductive coupling

Where,  $\frac{di_g}{dt}$  is the rate of change of the generator current

Therefore, fast changing generator currents will induce larger noise voltages in receptor circuits.

Equation 3–16 also gives the noise voltage due to inductive coupling:

$$V_n = j\omega \times BA\cos\Theta$$

### Equation 3–16. Noise voltage due to inductive coupling

Where,  $\mathbf{B}$  is the magnetic flux density (weber/cm<sup>2</sup>)

A is the receptor circuit area (cm<sup>2</sup>)

$\boldsymbol{\Theta}$  is the angle between the generator and receptor circuit

### 3.8. Twisted Pair

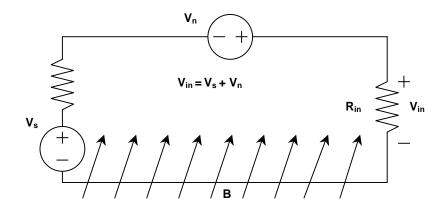

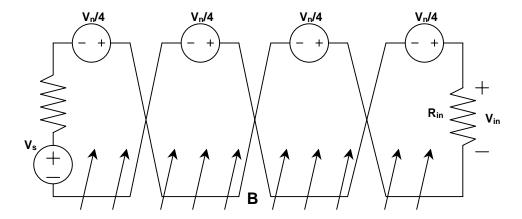

A twisted pair of wires reduces inductive coupling by canceling induced magnetic field voltages. Figure 3–15 shows magnetic field (**B**) coupling into a circuit.  $V_s$  represents an input signal to an electronic device on a vehicle.  $R_{in}$  represents the input impedance of the module. The figure shows that the device input voltage,  $V_{in}$ , is the sum of  $V_s$  and the noise voltage  $V_n$ , which the magnetic field induces.

Figure 3–15. Magnetic Field Coupling into Circuit

Figure 3–16. Magnetic Field Coupling into Twisted Wire Pair

Figure 3–16 shows the circuit in Figure 3–15 that uses a twisted pair. The twisting produces four equal loop areas with equal noise voltages. By summing all the voltages around the circuit the noise voltages cancel due to the twisting. This is why twisted pairs work best to reduce inductive coupling into a receptor circuit.

$$V_{in} = -\frac{V_n}{4} - \frac{V_n}{4} + V_s + \frac{V_n}{4} + \frac{V_n}{4} = V_s$$

Equation 3–17. Inductive Coupling in twisted-wire pair

To reduce inductive coupling:

- Reduce the receptor circuit area

- Increase the separation between the generator and receptor circuit

- Reduce the parallel length between the generator and receptor circuit

- Twist the receptor wires if the receptor current returns back through a wire

- Orient the receptor circuit to the generator circuit at 90°

- Twist the generator wires if the generator current returns back through a wire

- Reduce the operating frequency of the generator circuit

- Reduce the rate of change of the generator current

- Reduce the generator circuit area

- Shield the receptor circuit with a shield grounded at both ends

- Use a shield of magnetic material

- Place the conductors over a ground plane. The ground plane must return the conductor currents

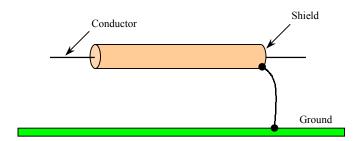

### 3.9. Shielding

EMI control must originate in the initial design of an E/E device. Some E/E devices require shielding to keep radiated energy away from module circuitry, or to keep EM energy from radiating from the module circuitry. Using a shield as a post-design fix to provide additional EMI protection adds cost and development time.

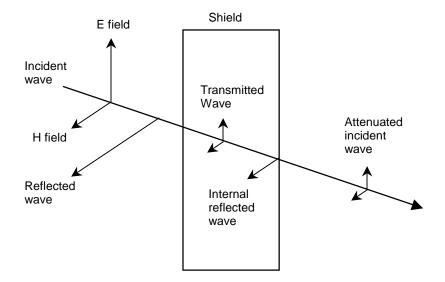

Shielding places a conductive partition between two regions in space. Shielding reflects and absorbs radiated EM energy, as shown in Figure 3–17. The noise source side of the shield reflects most of the incident energy, and the remaining energy enters the shield. As the field propagates through the shield, it absorbs some of the energy. When the field encounters the other surface of the shield some of it reflects back into the shield. The remaining electromagnetic energy enters the protected region.

Figure 3–17. Effectiveness of Shielding

A shield presents two losses to electromagnetic energy:

- The **reflection loss (R)** is the air-to-shield and shield-to-air loss. Shield reflection varies with the type of field.

- The **absorption loss (A)** is the energy lost due to absorption as the field propagates through the shield. Shield absorption does not vary with the type of field. However, absorption loss varies with the type of shielding material.

Equation 3–18 shows that the **shielding effectiveness (SE)** is the sum of the reflection and absorption losses. The decibel is the unit of SE:

$$SE = R + A$$

[dB]

### Equation 3–18. Shielding effectiveness

A SE of 40 dB indicates that the shield reflects and absorbs 99.99% of electromagnetic energy. Therefore, only 0.01% of EM energy penetrates the shielding system.

Magnetic material has a relative permeability  $(\mu_r)$  greater than 1. Where  $\mu_r$  is the ratio of the material's magnetic field conduction ability to air ( $\mu_r$  varies with frequency). At ratios greater than 1, the magnetic field would rather conduct through the magnetic material than through the air. Table 3–7 shows the relative permeability of some common materials. The table also gives the relative conductivity of the material. The relative **conductivity**  $(\delta_r)$  of the material is the ability to conduct current relative to copper. It is the inverse of **resistivity**  $(\rho)$ .

#### Absorption loss (A)

$$A = 3.34t (f \times \mu_r \times \delta_r)^{\frac{1}{2}} \quad [dB]$$

### Equation 3–19. Absorption loss

t is the thickness in inches Where,

Shield absorption does not vary with the type of field. However, absorption loss varies with the type of shield material.

#### Reflection loss (R)

A shield can protect against the following:

- Electromagnetic (EM) field

- Electric (E) field

- Magnetic (H) field

Electromagnetic, electric, and magnetic fields require different shield design. An electromagnetic filed has both, an electric and magnetic fields oriented 90 degrees to each other. These fields travel together as the electromagnetic wave propagates through space. The electromagnetic field is usually referred to as a far field plane wave.

Any metallic shield will reflect electromagnetic and electric fields. Here, shielding is a function of:

- Frequency

- Shield thickness

- Shield's relative conductivity

- Shield's relative permeability

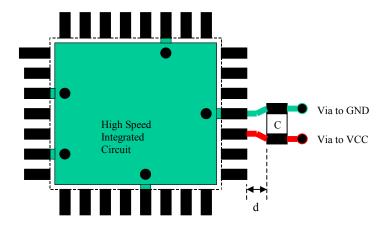

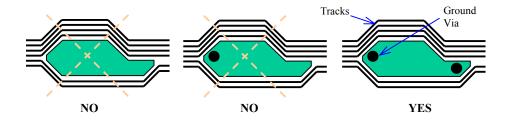

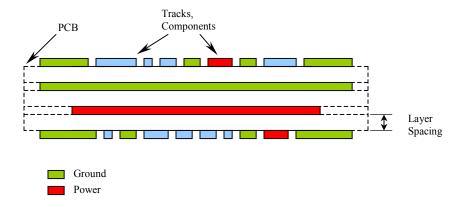

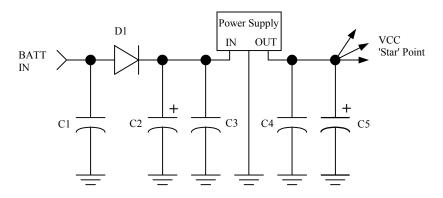

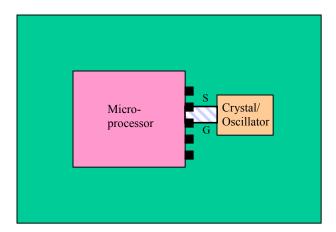

- Any openings (apertures) in the shield