## **Engr354: Digital Logic Circuits**

**Chapter 2: Introduction to Logic Circuits**

**Dr. Curtis Nelson**

### **Chapter 2 Objectives**

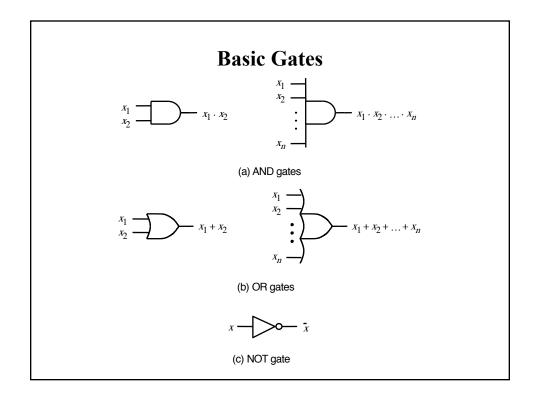

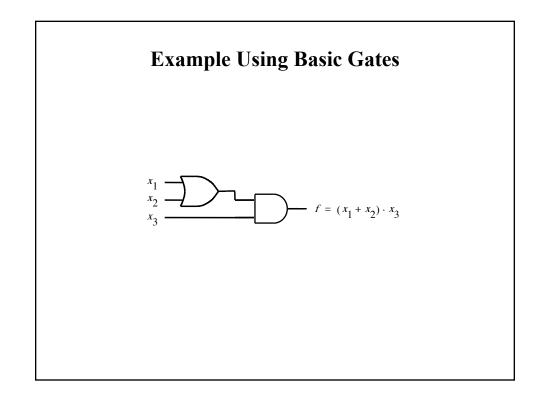

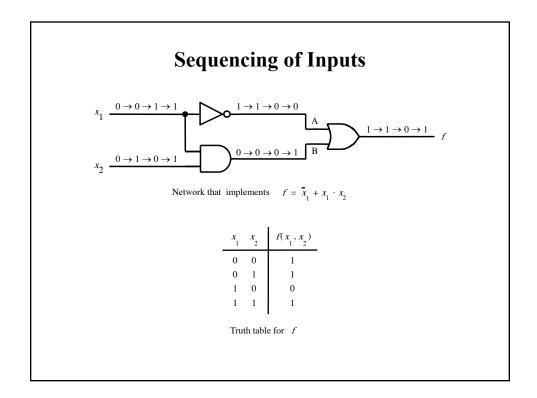

- Define and illustrate basic logic functions and circuits;

- Present Boolean algebra for dealing with logic functions;

- Illustrate logic gates and synthesis of simple circuits;

- Review CAD tools and the VHDL hardware description language.

|                                                                          | Truth Tables |       |                 |             |    |  |  |  |  |  |

|--------------------------------------------------------------------------|--------------|-------|-----------------|-------------|----|--|--|--|--|--|

| <ul><li>All combinat</li><li>Outputs on th</li><li>2-input AND</li></ul> | ne rig       | ht;   |                 | ŕ           | W. |  |  |  |  |  |

|                                                                          | $x_1$        | $x_2$ | $x_1 \cdot x_2$ | $x_1 + x_2$ |    |  |  |  |  |  |

|                                                                          | 0            | 0     | 0               | 0           |    |  |  |  |  |  |

|                                                                          | 0            | 1     | 0               | 1           |    |  |  |  |  |  |

|                                                                          | 1            | 0     | 0               | 1           |    |  |  |  |  |  |

|                                                                          | 1            | 1     | 1               | 1           |    |  |  |  |  |  |

|                                                                          |              |       | AND             | OR          |    |  |  |  |  |  |

### **Axioms of Boolean Algebra**

1.

$$0 \cdot 0 = 0$$

$1 + 1 = 1$ 2.  $1 \cdot 1 = 1$  $0 + 0 = 0$ 3.  $0 \cdot 1 = 1 \cdot 0 = 0$  $1 + 0 = 0 + 1 = 1$ 4. if  $x = 0$  then  $\overline{x} = 1$ if  $x = 1$  then  $\overline{x} = 0$

1

| Synthesis                                |       |       |               |                                |  |  |  |  |  |

|------------------------------------------|-------|-------|---------------|--------------------------------|--|--|--|--|--|

| • Synthesis is the p specification, i.e. |       |       | -             | cuit from a c, VHDL code, etc. |  |  |  |  |  |

| -                                        | $x_1$ | $x_2$ | $f(x_1, x_2)$ |                                |  |  |  |  |  |

| -                                        | 1     | ~-Z   | J (~1· ~2/    |                                |  |  |  |  |  |

|                                          | 0     | 0     | 1             |                                |  |  |  |  |  |

|                                          | 0     | 1     | 1             |                                |  |  |  |  |  |

|                                          | 1     | 0     | 0             |                                |  |  |  |  |  |

|                                          | 1     | 1     | 1             |                                |  |  |  |  |  |

|                                          |       |       | I             |                                |  |  |  |  |  |

|                                          |       |       |               |                                |  |  |  |  |  |

|                                          |       |       |               |                                |  |  |  |  |  |

|                                          |       |       |               |                                |  |  |  |  |  |

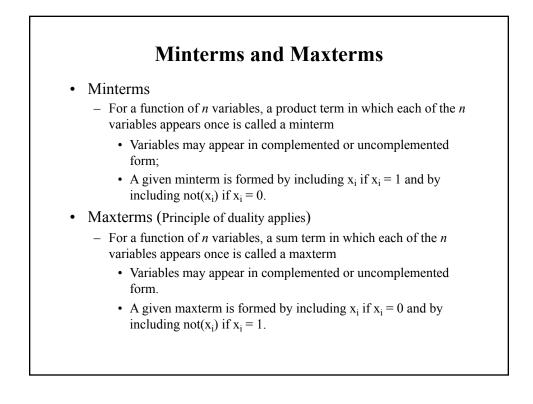

|               | <u> </u> |       |       | 1                                                    |                                                          |

|---------------|----------|-------|-------|------------------------------------------------------|----------------------------------------------------------|

| Row<br>number | $x_1$    | $x_2$ | $x_3$ | Minterm                                              | Maxterm                                                  |

| 0             | 0        | 0     | 0     | $m_0 = \overline{x}_1 \overline{x}_2 \overline{x}_3$ | $M_0 = x_1 + x_2 + x_3$                                  |

| 1             | 0        | 0     | 1     | $m_1 = \overline{x}_1 \overline{x}_2 x_3$            | $M_1 = x_1 + x_2 + \overline{x}_3$                       |

| 2             | 0        | 1     | 0     | $m_2 = \overline{x}_1 x_2 \overline{x}_3$            | $M_2 = x_1 + \overline{x}_2 + x_3$                       |

| 3             |          | 1     | 1     | $m_3 = \overline{x}_1 x_2 x_3$                       | $M_3 = x_1 + \overline{x}_2 + \overline{x}_3$            |

| 4             | 1        |       |       | $m_4 = x_1 \overline{x}_2 \overline{x}_3$            | $M_4 = \overline{x}_1 + x_2 + x_3$                       |

| 5             | 1        |       | 1     | $m_5 = x_1 \overline{x}_2 x_3$                       | $M_5 = \overline{x}_1 + x_2 + \overline{x}_3$            |

| 6             |          | 1     | 0     | $m_6 = x_1 x_2 \overline{x}_3$                       | $M_6 = \overline{x}_1 + \overline{x}_2 + x_3$            |

| 7             | 1        | 1     | 1     | $m_7 = x_1 x_2 x_3$                                  | $M_7 = \overline{x}_1 + \overline{x}_2 + \overline{x}_3$ |

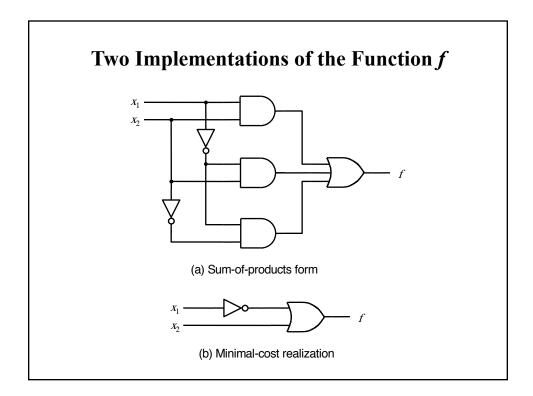

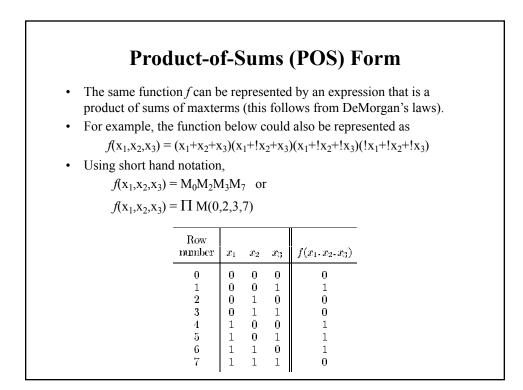

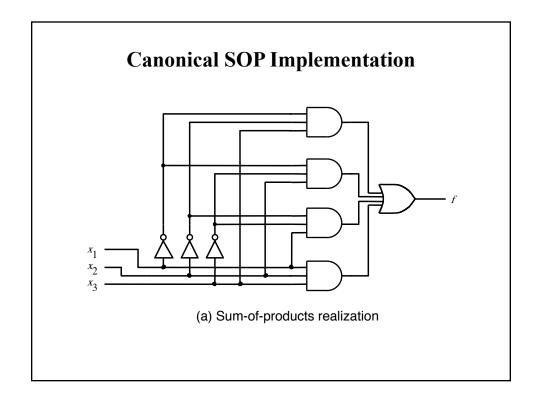

### **Sum-of-Products (SOP) Form**

- A function *f* can be represented by an expression that is a sum of minterms.

- For example, the function below could be represented as

- $f(\mathbf{x}_1, \mathbf{x}_2, \mathbf{x}_3) = \mathbf{x}_1 \mathbf{x}_2 \mathbf{x}_3 + \mathbf{x}_1 \mathbf{x}_2 \mathbf{x}_3 + \mathbf{x}_1 \mathbf{x}_2 \mathbf{x}_3 + \mathbf{x}_1 \mathbf{x}_2 \mathbf{x}_3$

- Using short hand notation

•

$$f(x_1, x_2, x_3) = m_1 + m_4 + m_5 + m_6$$

or

$$f(x_1, x_2, x_3) = \Sigma m(1, 4, 5, 6)$$

| Row<br>number | $x_1$ | $x_2$ | $x_0$ | $f(x_1, x_2, x_3)$ |

|---------------|-------|-------|-------|--------------------|

| 0             | 0     | 0     | 0     | 0                  |

| 1             | 0     | 0     | 1     | 1                  |

| <b>2</b>      | 0     | 1     | 0     | 0                  |

| 3             | 0     | 1     | 1     | 0                  |

| 4             | 1     | 0     | 0     | 1                  |

| 5             | 1     | 0     | 1     | 1                  |

| 6             | 1     | 1     | 0     | 1                  |

| 7             | 1     | 1     | 1     | 0                  |

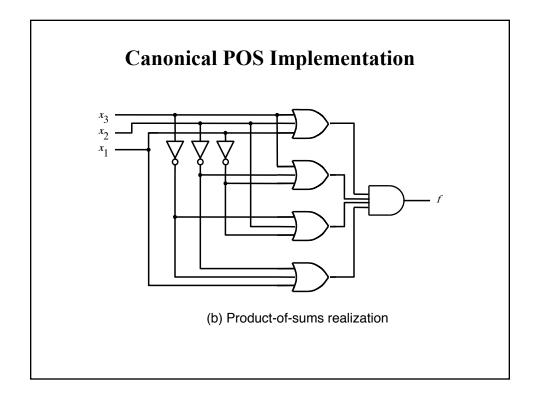

### Canonical

• A logic expression is said to be canonical if each term contains all variables, either complemented or uncomplemented.

### 2-Variable Example • Synthesize the following function using four different, but equivalent, expressions Minterm form; • Maxterm form; • Canonical form; ٠ • Minimum form. $f(x_1, x_2)$ $x_1$ $x_2$ $\mathbf{0}$ $\mathbf{0}$ 1 1 1 00 01 1 1 1

| <ul> <li>Synthesize the following function using four different, but equivalent, expressions</li> <li>Minterm form;</li> </ul> |  |

|--------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                |  |

| • Maxterm form;<br>• Canonical form; $x_1  x_2  x_3  f$                                                                        |  |

| • Minimum form. 0 0 0                                                                                                          |  |

|                                                                                                                                |  |

| 0 1 0 1                                                                                                                        |  |

| 0 1 1 0                                                                                                                        |  |

| 1 0 0 1                                                                                                                        |  |

|                                                                                                                                |  |

|                                                                                                                                |  |

|                                                                                                                                |  |

| <u></u>                                                                                                                        |  |

### Textbook Problem 2.28 Brown 3<sup>rd</sup> Ed.

- Design the simplest circuit that has three inputs, a, b, and c, which produces an output value of 1 whenever two or more of the input variables have the value of 1; otherwise, the output has to be 0.

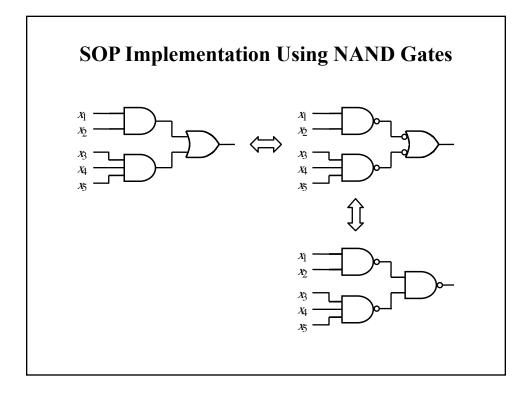

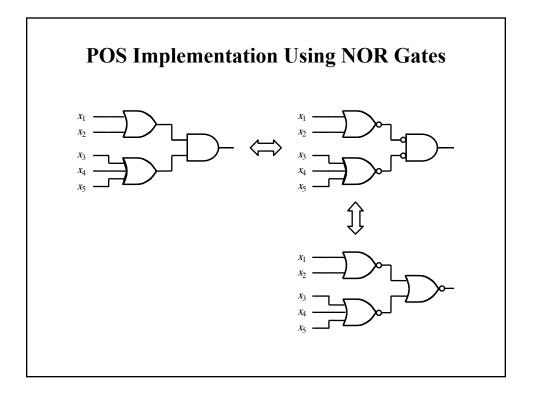

- Implement the circuit three different ways

- With minimum *and/or* logic;

- With *nand* logic gates only;

- With *nor* logic gates only.

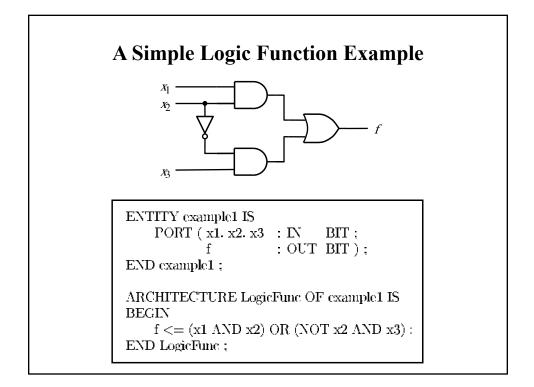

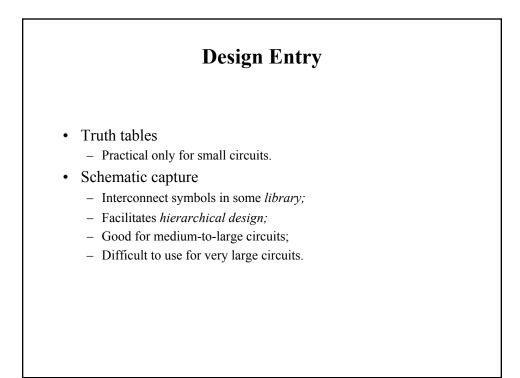

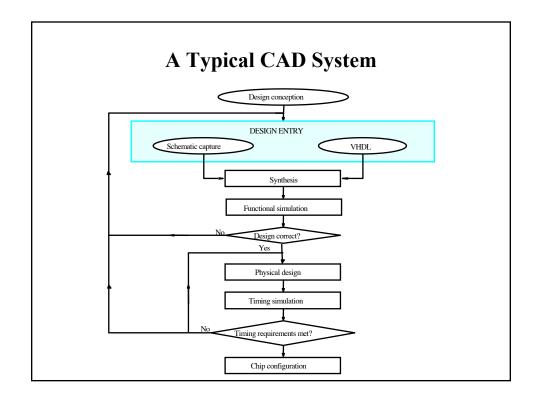

# Design Entry - Continued Hardware description languages (HDL's) Similar to a programming language; VHDL and Verilog HDL are IEEE standards; Provide design *portability*; Allow for sharing and design reuse; Support hierarchical design; Can be combined with schematics.

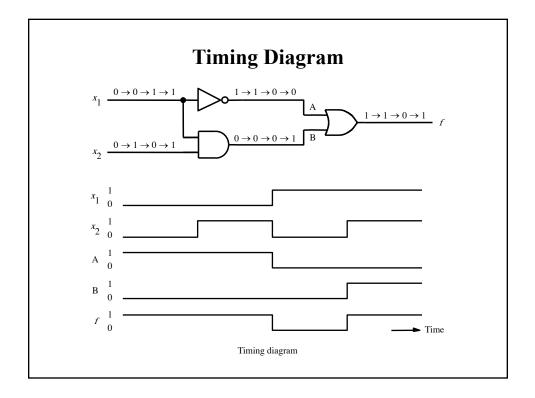

## Simulation A *functional simulator* is used to determine if a designed circuit operates correctly from a logic perspective. Circuit verification User provides input values to the circuit;

- Simulator determines the circuit response;

- User checks responses against desired outputs.

- A *timing simulator* is used to check correctness by incorporating the *electrical* characteristics of a logic design in addition to the *logical* performance. This simulation requires

- Technology mapping;

- Layout synthesis.

### VHDL

- VHDL Very high speed integrated circuit hardware description language;

- Original IEEE standard adopted in 1987;

- Revised standard in 1993;

- Originally used for documentation and simulation;

- Now, it is also used for synthesis;

- Very complex language, but only a subset is needed to design a wide range of circuits.

### **Representing Digital Signals in VHDL**

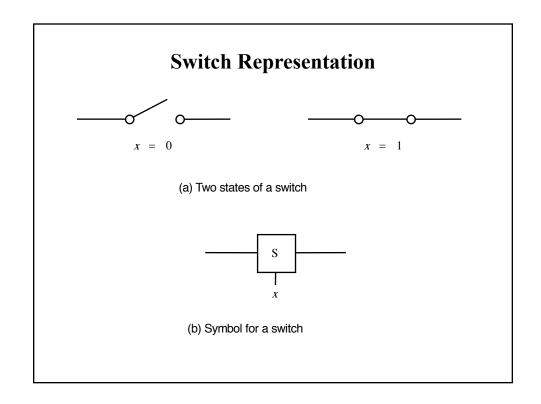

- Each logic signal in a circuit is a data object in VHDL code;

- Data objects in VHDL are assigned *types;*

- A simple type is BIT which is used for objects that can take only 2 values: 0 or 1.