## ECE124 Digital Circuits and Systems

## Prof. C. Gebotys

# **Final Exams Review**

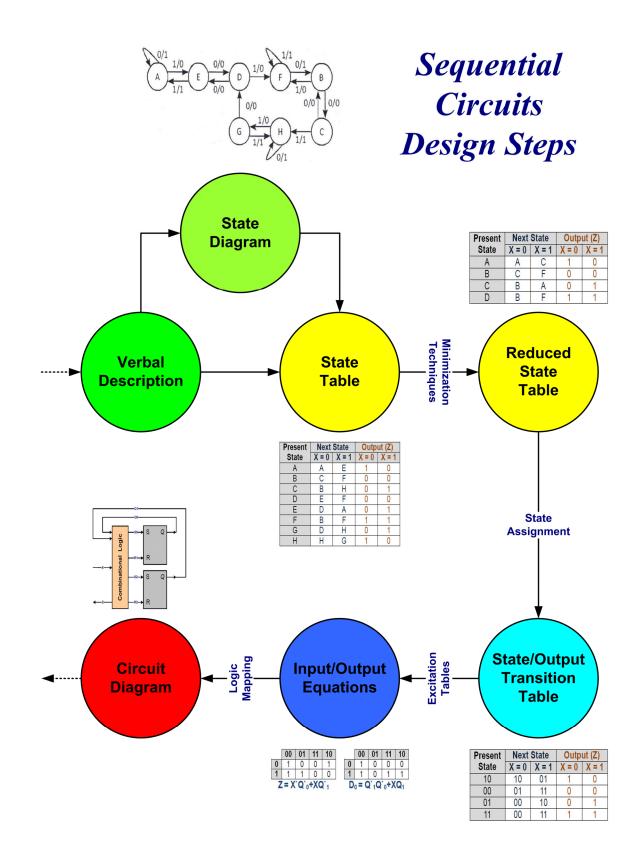

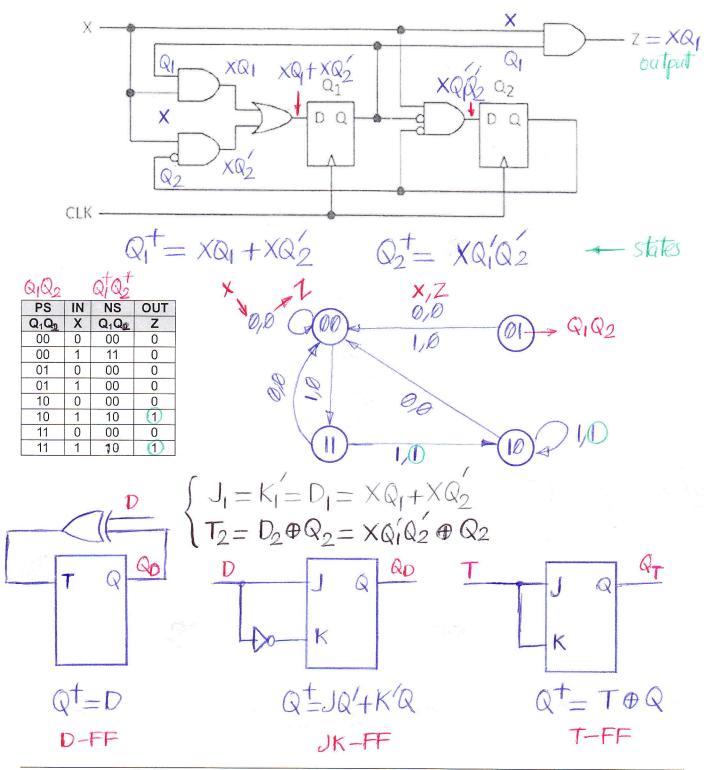

[Q1] For the following clocked sequential circuit with one input (X) and one output (Z):

- 1. Drive a state table and draw a state diagram for the circuit.

- Redesign this circuit by replacing the Q<sub>1</sub> flip-flop (i.e. the D flip-flop holding Q<sub>1</sub> state) with a JK flipflop, and the Q<sub>2</sub> flip-flop with a T flip-flop. Only show the excitation equations (or state equations) for J<sub>1</sub>, K<sub>1</sub>, and T<sub>2</sub>.

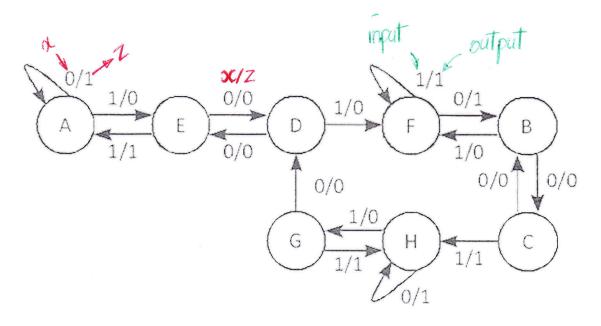

[Q2] Draw the state diagram for the table below that describes a finite-state machine which has one input x and one output z.

| Present | Next  | State | Outp  | ut (z) |

|---------|-------|-------|-------|--------|

| State   | x = 0 | x = 1 | x = 0 | x = 1  |

| A       | Α     | Е     | 1     | 0      |

| В       | С     | F     | 0     | 0      |

| С       | В     | Н     | 0     | 1      |

| D       | Е     | F     | 0     | 0      |

| E       | D     | Α     | 0     | 1      |

| F       | В     | F     | 1     | 1      |

| G       | D     | Н     | 0     | 1      |

| Н       | Н     | G     | 1     | 0      |

[Q3] Consider the following state diagram for a synchronous circuit with one input X and one output Z. Analyze this state diagram and draw its circuit implementation using JK flip-flop (state Q0) and T flip-flop (state Q1) and MUX-4x1 for Z.

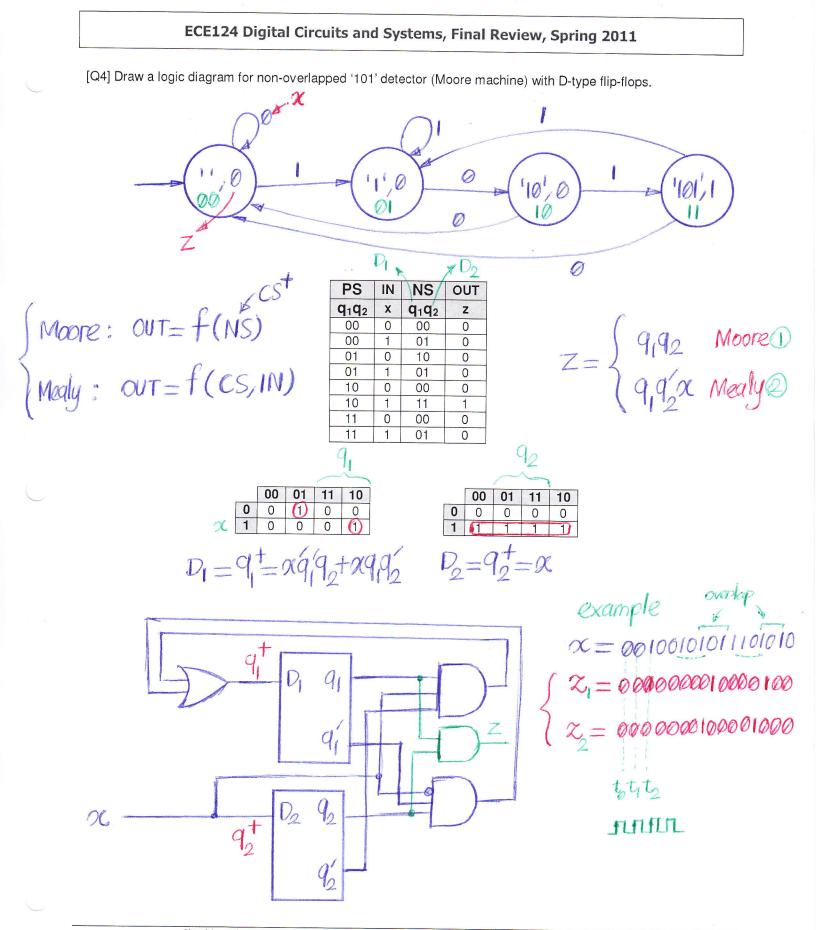

[Q4] Draw a circuit diagram for non-overlapped '101' detector with "D" flip-flops as a Mealy and Moore machine.

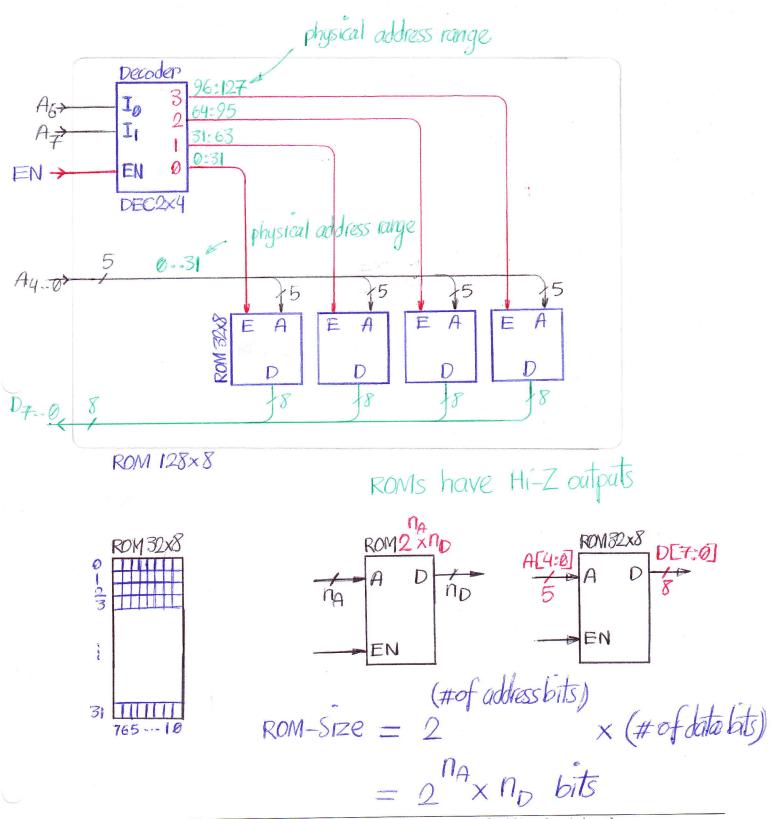

[Q5] Given a 32x8 ROM chip with an enable input, show the block level required connections to construct a 128x8 ROM with above ROM chips and a decoder. How many data and address lines these ROMs have?

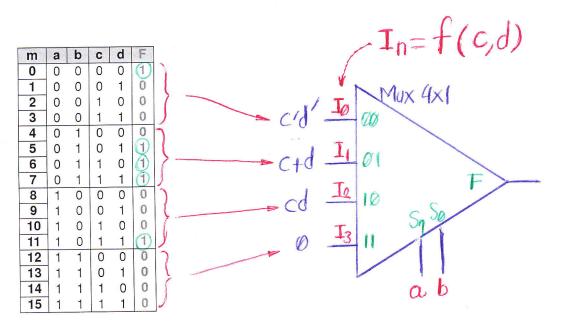

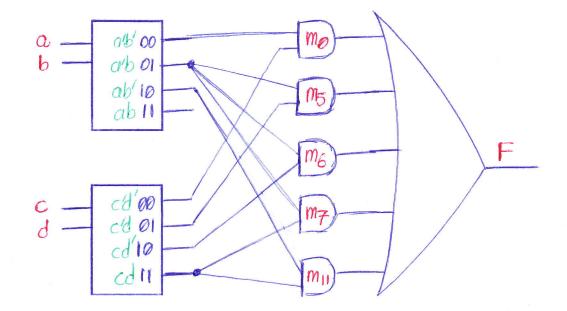

[Q6] Implement the circuit defined by equation  $F(a,b,c,d) = \sum (0,5,6,7,11)$  using:

- 1. 4-to-1 multiplexers and logic gates.

- 2. 2-to-4 decoders with non-inverted outputs and logic gates.

[Q7] Use a 3-bit binary counter with active-high load (L) and Increment (I) control inputs (load has higher priority than increment) and implement a circuit (draw) to generate and repeat the following sequence at the output of the counter. Initial counter value is "000".

$\cdots \rightarrow 000 \rightarrow 001 \rightarrow 010 \rightarrow 101 \rightarrow 110 \rightarrow 111 \rightarrow 000 \rightarrow \cdots$

[Q8] Design a digital circuit that takes two 4-bit numbers A and B as input and generates output Z as follows:

- If A and B are odd numbers then Z=A-B

- If A and B are even numbers then Z=B-A

- If A is an even number and B is an odd number then Z=A+B

- If A is an odd number and B is an even number then Z=A-B-1

Assume that you have access to as many as you need of AND, OR, INV, XOR gates and only one FULL-ADDER, DECODER and MULTIPLEXER of any size.

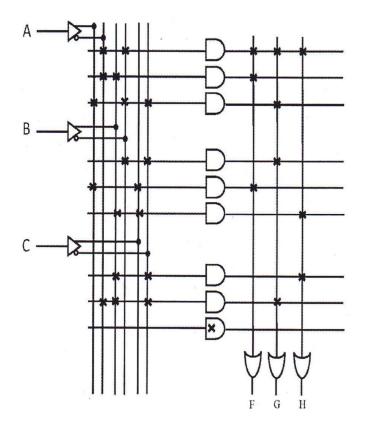

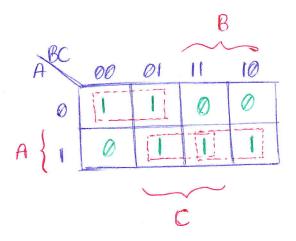

[Q9] For the following Programmable Logic Array (PLA), find the function expressions for all outputs and draw the Karnaugh-Map for function "F".

[Q10] What are three different ways of representing a signed number? Assume 7 bit numbers and represent (-15) in each of them, then find (B-A) and (A-C) for A = 1101010, B = 0110101 and C = 0010101 in all forms.

[Q11] Find:

- a) The 7's complement of base-8 number "45201"

- b) Multiplication of base-12 numbers "541" and "3"

- c) Base-10 unsigned number "214.45" to its base-2 representation

- d) Base-6 number "513" to its base-10 and then base-5 representations

- e) Hexadecimal number "AF6" to its base-2 and base-8 representations

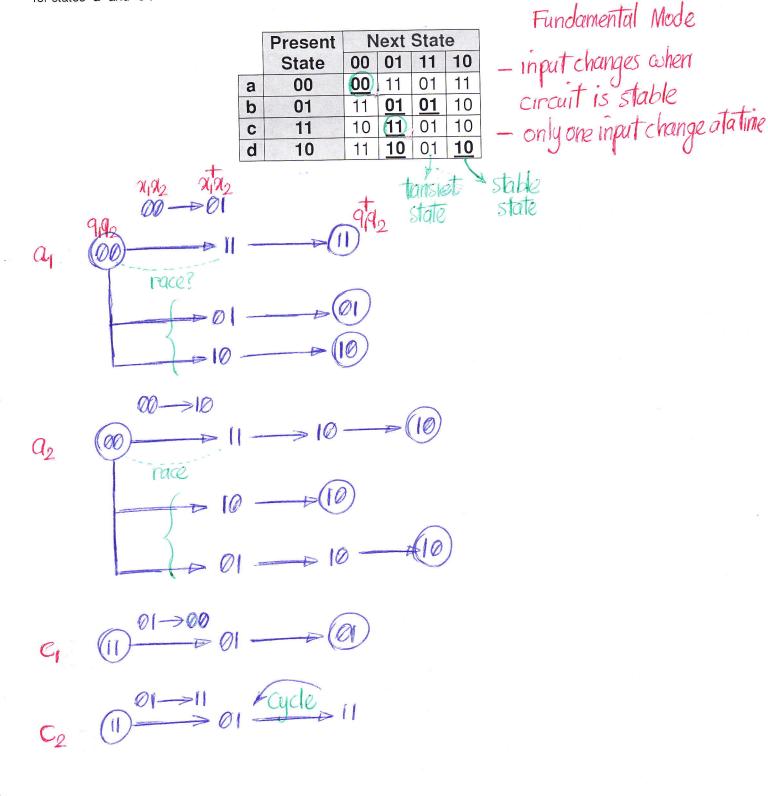

[Q12] For the following asynchronous sequential state table, find all possible critical/non-critical races and cycles for states "a" and "c".

|   | Present | Next State |           |           |           |  |

|---|---------|------------|-----------|-----------|-----------|--|

|   | State   | 00         | 01        | 11        | 10        |  |

| а | 00      | 00         | 11        | 01        | 11        |  |

| b | 01      | 11         | <u>01</u> | <u>01</u> | 10        |  |

| С | 11      | 10         | <u>11</u> | 01        | 10        |  |

| d | 10      | 11         | <u>10</u> | 01        | <u>10</u> |  |

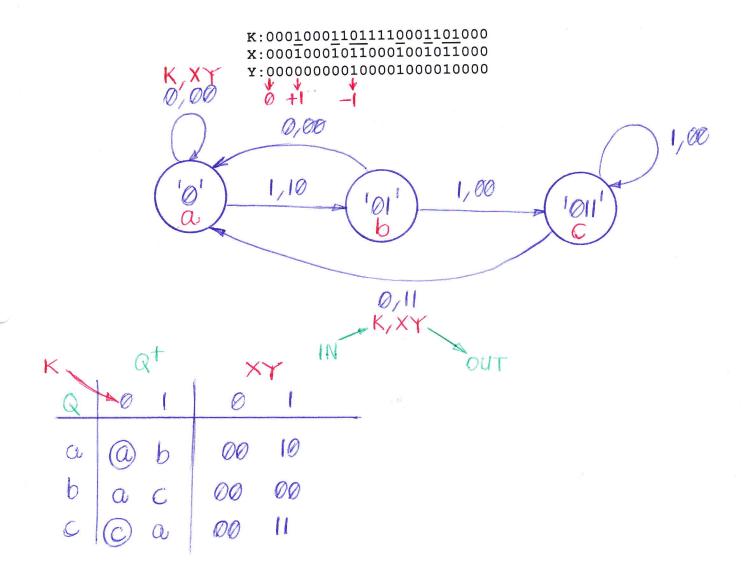

[Q13] A crypto module which transforms a secret key bit stream, K, into two other bit streams, X and Y has to be designed. This module must be designed as an asynchronous sequential Mealy state machine. It works as follows: if the secret key bit stream contains '011', then it's replaced with '10(-1)'. This transformation reduces the number of '1' bits in the key (which has significant impact on subsequent processing times in elliptic curve algorithms). However since we cannot represent 0, 1 and -1 with a one bit output, we use two output signals, X and Y. Whenever a m-bit sequence of 1's is detected (where m>1), X is set to 1 for the first K='1' in the sequence and when a K='0' is detected after the m<sup>th</sup> '1' bit both X and Y are set to '1'. Construct a sequential state table for this module.

####

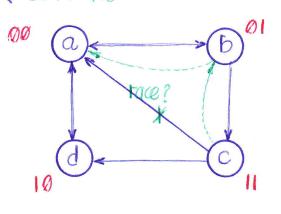

[Q14] For below sequential state table, perform a race-free state assignment and complete the entire state table:

| Present | 1        | Next State |    |          |    | Output |    |    |  |

|---------|----------|------------|----|----------|----|--------|----|----|--|

| State   | 00       | 01         | 11 | 10       | 00 | 01     | 11 | 10 |  |

| а       | <u>a</u> | <u>a</u>   | b  | d        | 0  | 1      | -  | -  |  |

| b       | а        | b          | b  | С        | -  | 0      | 1  | -  |  |

| С       | а        | -          | d  | <u>C</u> | -  | -      | -  | 0  |  |

| d       | а        | а          | d  | d        | -  | -      | 1  | 0  |  |

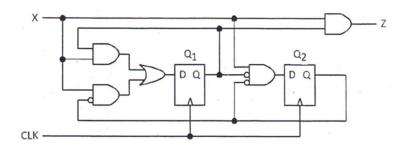

[Q1] For the following clocked sequential circuit with one input (X) and one output (Z):

- 1. Drive a state table and draw a state diagram for the circuit.

- 2. Redesign this circuit by replacing the  $\overline{Q}_1$  flip-flop (i.e. the D flip-flop holding  $Q_1$  state) with a JK flipflop, and the  $Q_2$  flip-flop with a T flip-flop. Only show the excitation equations (or state equations) for  $J_1$ ,  $K_1$ , and  $T_2$ .

[Q2] Draw the state diagram for the table below that describes a finite-state machine which has one input x and one output z.

| Present | Next  | State | Output (z) |       |  |

|---------|-------|-------|------------|-------|--|

| State   | x = 0 | x = 1 | x = 0      | x = 1 |  |

| Α       | А     | E     | 1          | 0     |  |

| В       | С     | F     | 0          | 0     |  |

| С       | В     | Н     | 0          | 1     |  |

| D       | E     | F     | 0          | 0     |  |

| E       | D     | A     | 0          | 1     |  |

| F       | В     | F     | 1          | 1     |  |

| G       | D     | Н     | 0          | 1     |  |

| Н       | Н     | G     | 1          | 0     |  |

Mealy Diagram z = f(cs, x)

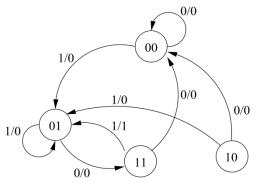

[Q3] Consider the following state diagram for a circuit with one input X and one output Z. Analyze this state diagram and draw its circuit implementation using JK flip-flop (state Q0) and T flip-flop (state Q1) and MUX-4x1 for Z.

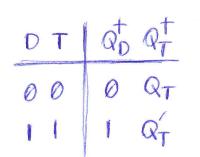

D&T FF characteristic tables

| PS                         | IN | NS                         | OUT | JK | -FF            | T-FF                  |

|----------------------------|----|----------------------------|-----|----|----------------|-----------------------|

| $\mathbf{q}_1\mathbf{q}_0$ | X  | $\mathbf{q}_1\mathbf{q}_0$ | Z   | Jo | K <sub>0</sub> | <b>T</b> <sub>1</sub> |

| 00                         | 0  | 00                         | 0   | 0  | Х              | 0                     |

| 00                         | 1  | 01                         | 0   | 1  | Х              | 0                     |

| 01                         | 0  | 11                         | 0   | Х  | 0              | 1                     |

| 01                         | 1  | 01                         | 0   | Х  | 0              | 0                     |

| 10                         | 0  | 00                         | 0   | 0  | Х              | 1                     |

| 10                         | 1  | 01                         | 0   | 1  | Х              | 1                     |

| 11                         | 0  | 00                         | 0   | Х  | 1              | 1                     |

| 11                         | 1  | 01                         | 1   | Х  | 0              | 1                     |

00

0 0 (1

1 0

01 11

0

Z

T1 = 91-490

10

| JK       | SR | QJK         | QSR               |  |  |

|----------|----|-------------|-------------------|--|--|

| 00       | 00 | <b>Q</b> jK | RSR               |  |  |

| 01       | 01 | 0           | 0                 |  |  |

| 10       | 10 | (           | I                 |  |  |

|          | 11 | Q'IK        | name and the same |  |  |

| JK&SR FF |    |             |                   |  |  |

characteristic tables

|   | 00 | 01 | 11 | 10 |

|---|----|----|----|----|

| 0 | 0  | Х  | Х  | 0  |

| 1 | 11 | Х  | Х  | 1  |

ØQ

J0 = X

00 01 11 10 0 Х 0 1 X 1 Х 0 Х 0 9,X K0 =

| Flip-Flops        |  |

|-------------------|--|

| excitation tables |  |

| ( | Rat | JK       | SR | D | T  |  |

|---|-----|----------|----|---|----|--|

|   | 00  | ØX       | ØX | 0 | Ø  |  |

|   | 01  | 1X       | 10 | I | 1  |  |

|   |     | XI<br>X0 | ×0 | 0 | 10 |  |

|      | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  | 0  | 0  |

| 1    | 0  | 0  | 1  | 0  |

| F(x) | 0  | 0  | X  | 0  |

[Q5] Given a 32x8 ROM chip with an enable input, show the block level required connections to construct a 128x8 ROM with ROM chips and a decoder. How many data and address lines these ROMs have?

[Q6] Implement the circuit defined by equation  $F(a,b,c,d) = \sum (0,5,6,7,11)$  using:

- 1. 4-to-1 multiplexers and logic gates.

- 2. 2-to-4 decoders with non-inverted outputs and logic gates.

$F(a_1b_1c_1d) = a'b'c'd' + a'bc'd + a'bcd' + a'bcd + ab'cd$  $mp m_5 m_6 m_7 m_1$

| [Q7] Use a 3-bit binary counter with active-hi<br>than increment) and implement a circuit (draw<br>counter. Initial counter value is "000". | gh load (L) and Increment (I) control inputs (load has higher priority<br>) to generate and repeat the following sequence at the output of the |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| $\cdots \rightarrow 000 \rightarrow 001$                                                                                                    | $\rightarrow 010 \rightarrow 101 \rightarrow 110 \rightarrow 111 \rightarrow 000 \rightarrow \cdots$                                           |

| 929,96                                                                                                                                      | characteristic 00 Q+1<br>table 01 Q+1                                                                                                          |

| PS-NS Counter Control I                                                                                                                     | ait IX P                                                                                                                                       |

| 92919 92910 L I P2P1                                                                                                                        | 6 Counter                                                                                                                                      |

| 000 000 0 I XXX                                                                                                                             | I-DI La                                                                                                                                        |

| 001 010 0 1 XXX                                                                                                                             |                                                                                                                                                |

| 010101   X 101                                                                                                                              | $P_2 Q_2 \rightarrow D_0 - D_1$                                                                                                                |

| 101 110 0 1 xxx                                                                                                                             |                                                                                                                                                |

| 110 III 0 1 XXX                                                                                                                             | 1 - Po Qo                                                                                                                                      |

| 111000 0 1 ×××                                                                                                                              |                                                                                                                                                |

| unused { 011 xxx x x x xxx<br>states { 100 xxx x x x xxx                                                                                    |                                                                                                                                                |

| 9990 00 01 11<br>0 0 0 X                                                                                                                    | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                          |

| 1 X Ø Ø                                                                                                                                     |                                                                                                                                                |

| $L = 9_2^{\prime} 9_2^{\prime}$                                                                                                             | I = 1                                                                                                                                          |

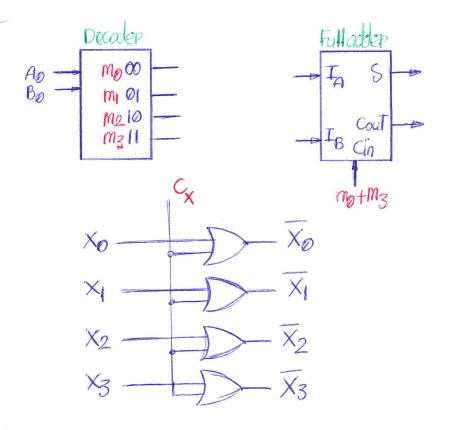

[Q8] Design a digital circuit that takes two 4-bit numbers A and B as input and generates output Z as follows:

- If A and B are odd numbers then Z=A-B

- If A and B are even numbers then Z=B-A

- If A is an even number and B is an odd number then Z=A+B

- If A is an odd number and B is an even number then Z=A-B-1

Assume that you have access to as many as you need of AND, OR, INV, XOR gates and FULL-ADDER, DECODER and MULTIPLEXER of any size.

|          | odd<br>even<br>AøBø | function<br>Z | Full addep inputs<br>IA TB Gin      | Control,<br>Commands                                                                                            |

|----------|---------------------|---------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| m1<br>M2 | 01<br>10            | A+B<br>A-B-1  | ~A B I<br>A B O<br>A ~B O<br>A ~B ( | $G_{n} = m_{0} + m_{3}$ $C_{A} = m_{0}$ $C_{B} = m_{2} + m_{3}$ $G_{B} = m_{2} + m_{3}$ $G_{B} = m_{2} + m_{3}$ |

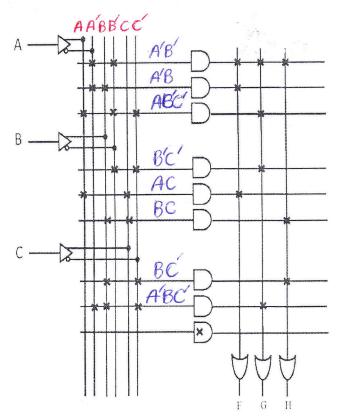

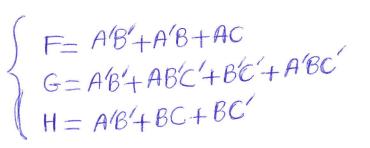

[Q9] For the following Programmable Logic Array (PLA), find the function expressions for all outputs and draw the Karnaugh-Maps for function "F".

| in each of th |                         | -15            | 2              |  |

|---------------|-------------------------|----------------|----------------|--|

|               | Signed & Maginitude     | 10011          | 1              |  |

|               | Signed & 1's Complement |                | XOQ            |  |

|               | Signed & 2's complement | 110001         |                |  |

|               | Magnitude               | 1's Camplement | 2's Camplement |  |

| B+            | 0110101                 | 0110101        | 0110101        |  |

| - A           | 0101010                 | 0010101        | 0010110        |  |

|               | Sign DOILIL             | 1001010        | 1001011        |  |

|               |                         | overflow       | overflow       |  |

| At            | 101010                  | 10010          | 1101010        |  |

| — C           | 1010101                 | 101010         | 1101011        |  |

|               | () @11110 add, 1        | (1010100       | 1010101        |  |

| Car           | F and araino            | 1 A            | discard        |  |

|               | ry sign Carry           | 10101 101      | endcarry       |  |

[Q10] What are three different ways of representing a signed number? Assume 7 bit numbers and represent (-15) in each of them, then find (B-A) and (A-C) for A = 1101010, B = 0110101 and C = 0010101 in all forms.

#### [Q11] Find:

- a) The 7's complement of base-8 number "45201"

- b) Multiplication of base-12 numbers "541" and "3"

- c) Base-10 unsigned number "214.45" to its base-2 representation

- d) Base-6 number "513" to its base-10 and then base-5 representations

- e) Hexadecimal number "AF6" to its base-2 and base-8 representations

54 b)  $\alpha$ 45201 32576 1403 4.45 (msb) (sb)  $d)(513)_{6} = 3x6 + 1x6 + 5x6$ X2 189 XI x2 (msb)  $=(1224)_{5}$ (msb) e) AF6=101011110110  $(214.45)_{10} = (11010110.011100)$  $(5366)_{8}$

[Q12] For the following asynchronous sequential state table, find all possible critical/non-critical races and cycles for states "a" and "c".

[Q13] A crypto module which transforms a secret key bit stream, K, into two other bit streams, X and Y has to be designed. This module must be designed as a synchronous sequential Mealy state machine. It works as follows: if the secret key bit stream contains '011', then it's replaced with '10(-1)'. This transformation reduces the number of '1' bits in the key (which has significant impact on subsequent processing times in elliptic curve algorithms). However since we cannot represent 0, 1 and -1 with a one bit output, we use two output signals, X and Y. Whenever a m-bit sequence of 1's is detected (where m>1), X is set to 1 for the first K='1' in the sequence and when a K='0' is detected after the m<sup>th</sup> '1' bit both X and Y are set to '1'. Construct a flow table for this module.

[Q14] For below Mealy flow table, perform a race-free state assignment and complete the entire state table:

| Present | Next State |            |     | Output |     |    |     |     |

|---------|------------|------------|-----|--------|-----|----|-----|-----|

| State   | 00         | 01         | 11  | 10     | 00  | 01 | 11  | 10  |

| а       | a          | (a)2       | b   | d      | 0   | 1  | ł   | Ø   |

| b       | a          | <b>b</b> 3 | 64  | С      | Ø   | 0  | 1   | 011 |

| С       | ba         | -          | d   | C5     | Ø   | 1  | 0/1 | 0   |

| d       | a          | а          | (d) | d,     | - 0 |    | 1   | 0   |

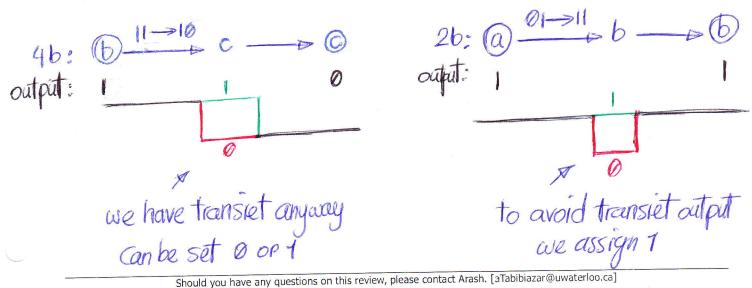

avoid transiet output { 1: to prevent static-1 hazard pulse 0/1: no hazard

race free

{race condition for  $\bigcirc \rightarrow @$  transition !? break the edge to transit  $c \rightarrow b \rightarrow a$