# FLIP-FLOP JK

(Tugas Sistem Digital)

Oleh

Riza Amelia (0917041048)

**Zaitun** (0917041017)

JURUSAN FISIKA

FAKULTAS MATEMATIKA DAN ILMU PENGETAHUAN ALAM

UNIVERSITAS LAMPUNG

BANDAR LAMPUNG

2013

#### FLIP-FLOP JK

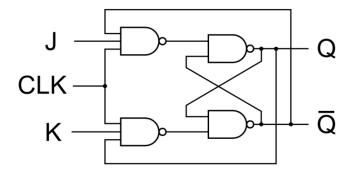

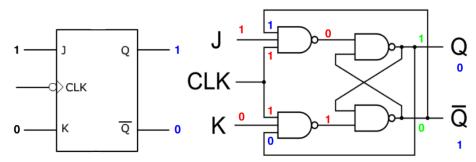

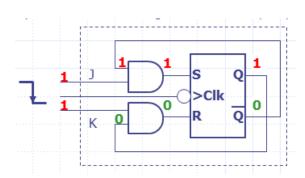

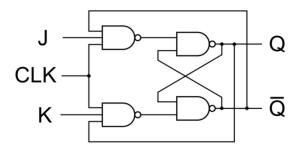

Flip-flop JK mempunyai masukan J dan K. flip-flop ini dipicu oleh suatu pinggiran pulsa clock positif atau negatif.Flip-flop JK merupakan rangkaian dasar untuk menyusun sebuah pencacah. Flip flop JK dibangun dari rangkaian dasar flip-flop-SR dengan menambahkan dua gerbang AND pada masukan R dan S serta dilengkapi dengan rangkaian diferensiator pembentuk denyut pulsa clock seperti yang ditunjukkan pada gambar berikut:

Rangkaian Flip-Flop JK

Pada flip-flop JK ini, masukan J dan K disebut masukan pengendali karena kedua masukan ini yang menentukan keadaan yang harus dipilih oleh flip-flop pada saat pulsa clock tiba (dapat pinggiran positif atau negatif, tergantung kepada jenis flip-flopnya). flip-flop ini berbeda dengan flip-flop-D karena pada flip-flop-JK masukan clock adalah masukan yang dicacah, dan masukan J serta K adalah masukan yang mengendalikan flip-flop tersebut.

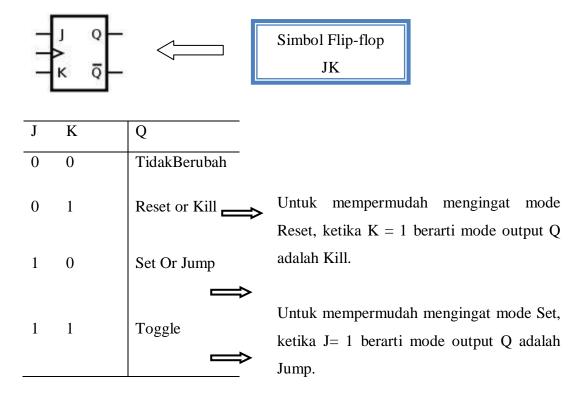

J-K flip-flop atau Jump-Kill Flip-flop merupakan penyempurna flip-flop dasar RS, yang mana. flip-flop ini mengatasi kelemahan flip-flop RS yang tidak mengizinkan pemberian masukan R=S=1, dengan meng-AND-kan masukan dari luar dengan keluaran seperti yang dilakukan oleh flip-flop T. Penyempurnaan

yang dilakukan flip flop JK ini yaitu mengganti mode keluaran (Q) dari mode ambigu menjadi toggle atau beralih. Pada flip-flop JK, input merupakan satusatunya masukan sedangkan keluarannya tetap dua. Jika keadaan keluaran flip-flop 0, maka setelah adanya sinyal pemicu keadaan berikutnya menjadi 1, dan bila keadaan keluarannya 1 maka setelah ada pemicu keadaannya akan menjadi 0. Berikut ini adalah Gambar simbol dan tabel kebenaran dari Flip-flop J-K

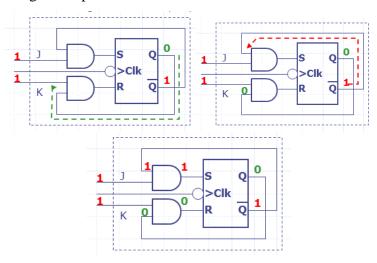

J = 1dan K = 1 dinamakan mode Toggle.Jika Q dimulai dari 0, maka setelah mode toggle menjadi high.

Jika Q dimulai dari 1, maka setelah mode toggle menjadi low.

\_

Prinsip kerja dari flip-flop JK adalah sebagai berikut :

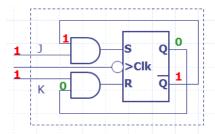

1. Pada saat J=0 dan K=0 atau keduanya berlogika low, gerbang AND tidak memberikan tanggapan sehingga keluaran Q tetap bertahan pada keadaan terakhirnya

2. Pada saat J=0 atau berlogika low dan K=1 atau berlogika high, maka flipflop akan direset hingga diperoleh keluaran Q=0 (kecuali jika flipflop memang sudah dalam keadaan reset atau Q memang sudah pada keadaan rendah).

3. Pada saat J=1 dan K=0 atauketika J berlogika high dan K berlogika low, maka masukan ini akan mengeset flip-flop hingga diperoleh keluaran Q=1 (kecuali jika flip-flop memang sudah dalam keadaan set atauQ sudah dalam keadaan tinggi).

4. Pada saat J dak K kedua-duanya tinggi, maka flip-flop berada dalam keadaan toggle, artinya keluaran Q akan berpindah pada keadaan lawan jika pinggiran pulsa clocknya tiba. Berikut ini merupakan bentuk diagram konstruksi dari JK Flip-Flop dan bagaimana mode toggle bekerja.

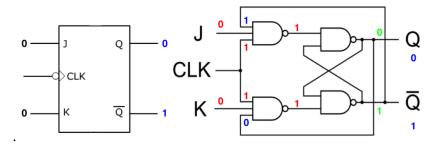

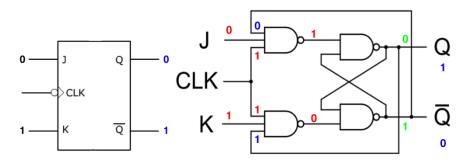

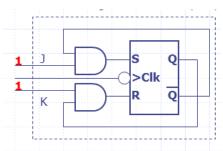

Diagram konstruksi Flip-Flip JK

Kita memberi masukan J=1 dan K=1, kita asumsikan bahwa keadaan awal Q=0, sehingga menghasilkan output Q=0 dan $\bar{Q}=1$ .

Tinjau kembali logika pada gerbang AND. Pada gerbang AND pertama akan menghasilkan logika output 1, sedangkan pada gerbang AND kedua akan menghasilkan logika output 0.

Dalam flip-flop JK, terdapat flip-flop SR yang siap mengatur output berlogika 1 jika clock atau detak diberikan. Pada proses tersebut dapat kita lihat logika output Q berubah menjadi 1.

### **Contoh Soal**

- 1. Sebutkan Gerbang penyusun Flip-Flop JK!

- 2. Gambarkan rangkaian Flip-Flop JK

- 3. Tuliskan tabel kebenaran dari Flip-Flop JK!

- 4. Mengapa masukan J K disebut masukan pengendali?

- 5. Apakah yang dimaksud dengan keadaan Toggle pada Flip-Flop JK?

### Jawaban

Flip flop JK dibangun dari rangkaian dasar flip-flop-SR dengan menambahkan dua gerbang AND pada masukan R dan S serta dilengkapi dengan rangkaian diferensiator pembentuk denyut pulsa clock

2.

Rangkaian Flip-Flop JK

# 3. Tabel Kebenaran Flip-Flop JK

| MODE<br>OPERASI | MASUKAN |   |   | KELUARAN              |    |

|-----------------|---------|---|---|-----------------------|----|

|                 | CK      | J | K | Q                     | Q' |

| TETAP           | 1       | 0 | 0 | TIDAK BERUBAH         |    |

| RESET           | 1       | 0 | 1 | 0                     | 1  |

| SET             | 1       | 1 | 0 | 1                     | 0  |

| TOGGLE          | 1       | 1 | 1 | KEADAAN<br>BERLAWANAN |    |

- 4. J dan K disebut masukan pengendali karena kedua masukan ini yang menentukan keadaan yang harus dipilih oleh flip-flop pada saat pulsa clock tiba

- 5. Keadaan toggle, artinya keluaran Q akan berpindah pada keadaan berlawanan jika pinggiran pulsa clocknya tiba