# **FPGA Generic Library Guide**

## Summary

This guide contains the naming conventions, detailed description and truth table of all components in the FPGA Generic Library.

## Introduction

FPGA Generic library covers a wide range of commonly used digital components to aid the process of building your system-on-FPGA. This library guide describes the components available in the FPGA Generic integrated library.

Components in this library maintain the policy of FPGA Vendor Independency. This means that you can easily port your design across different platform/architecture FPGA.

The description, functional table and additional information together

with their symbolic representation are presented to help you select the correct function to suite your design needs.

## **Selection Guidelines**

The Generic Library components are named following the convention described in <u>Naming</u> <u>Conventions</u> section of this guide.

In the <u>Functional Classes</u> section of this guide each component is listed under their functional category with a short description of their logic behavior.

The <u>Design Components</u> section of this guide lists the components in alphanumeric order with following information on each component:

- Functional Description

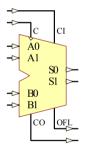

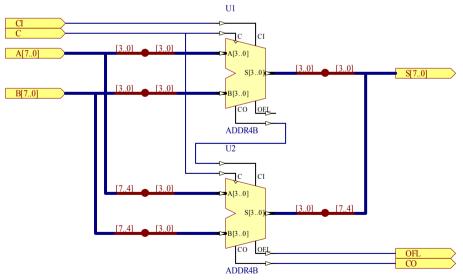

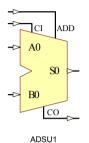

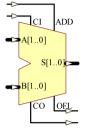

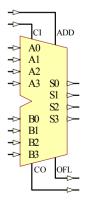

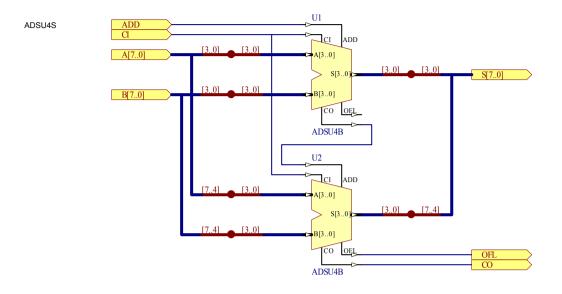

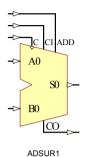

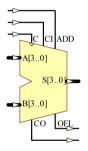

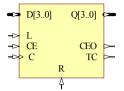

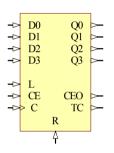

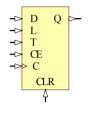

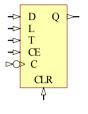

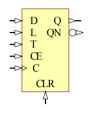

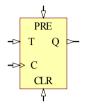

- Schematic Symbol

- Truth Table or equation

- Additional notes (if any)

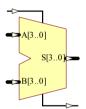

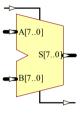

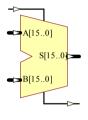

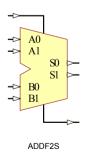

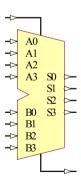

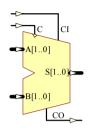

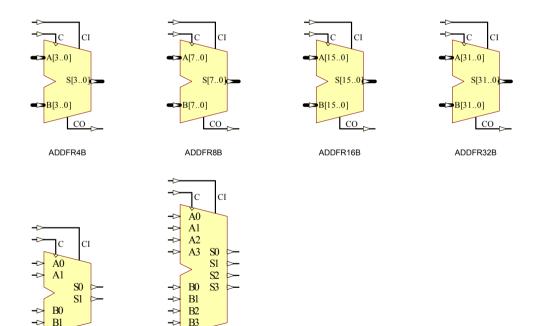

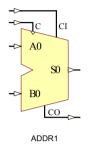

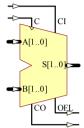

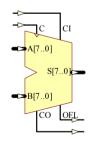

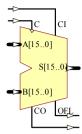

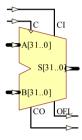

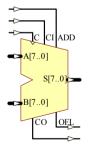

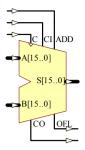

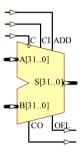

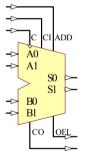

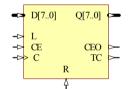

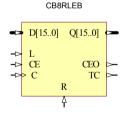

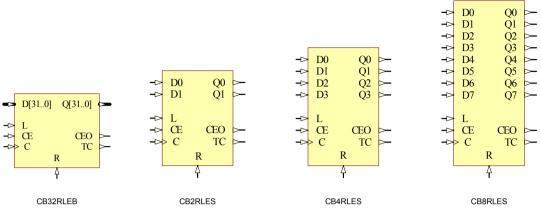

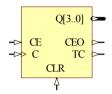

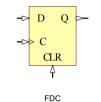

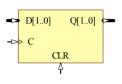

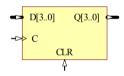

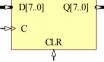

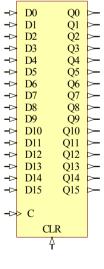

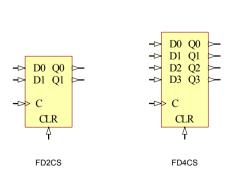

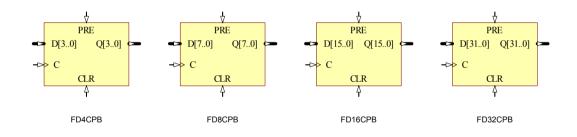

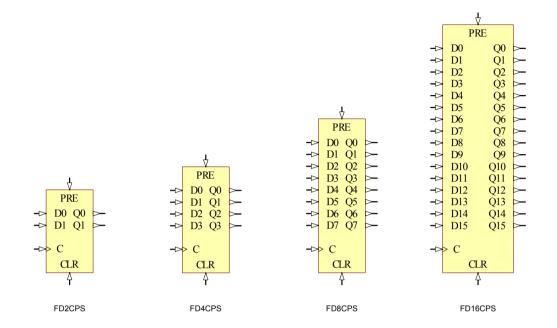

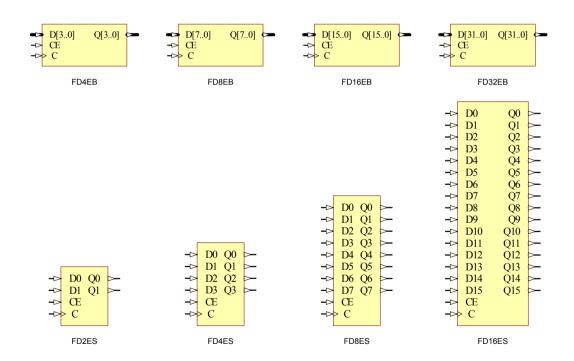

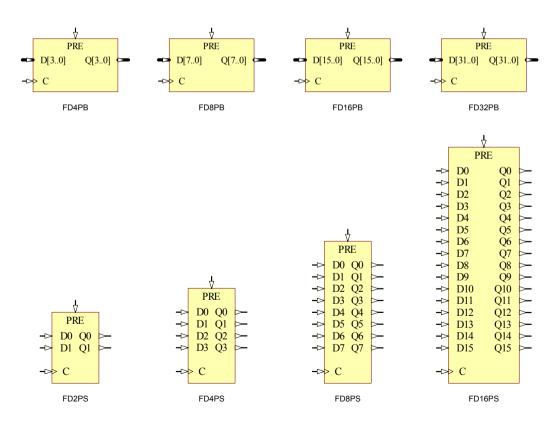

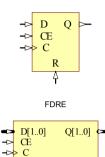

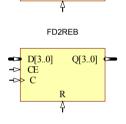

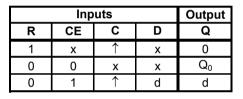

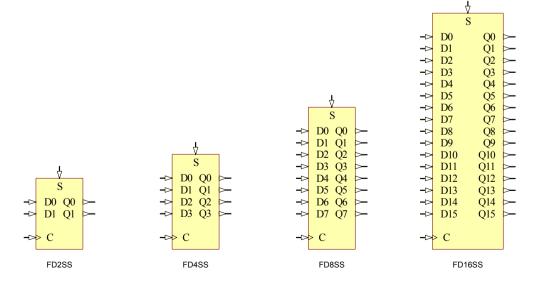

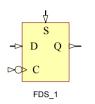

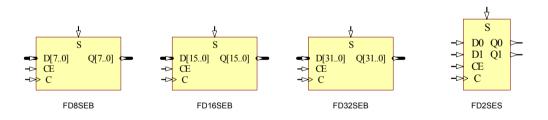

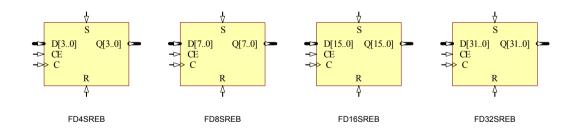

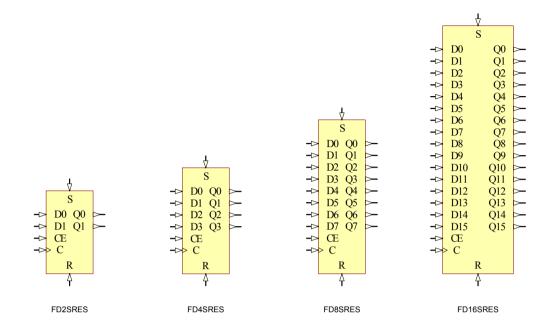

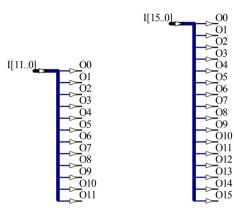

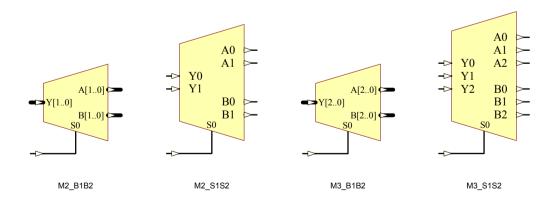

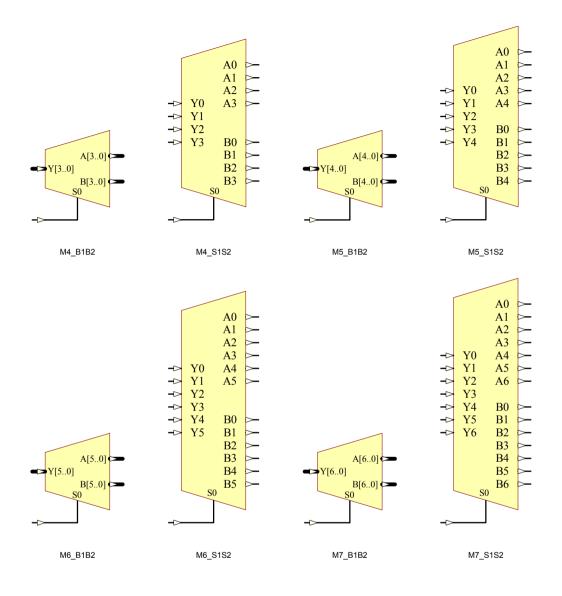

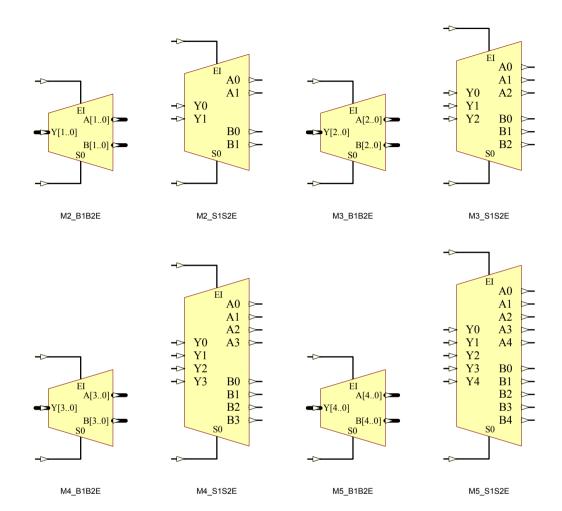

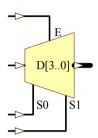

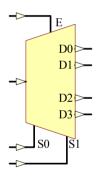

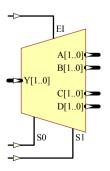

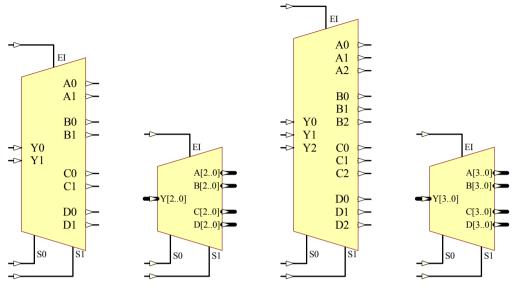

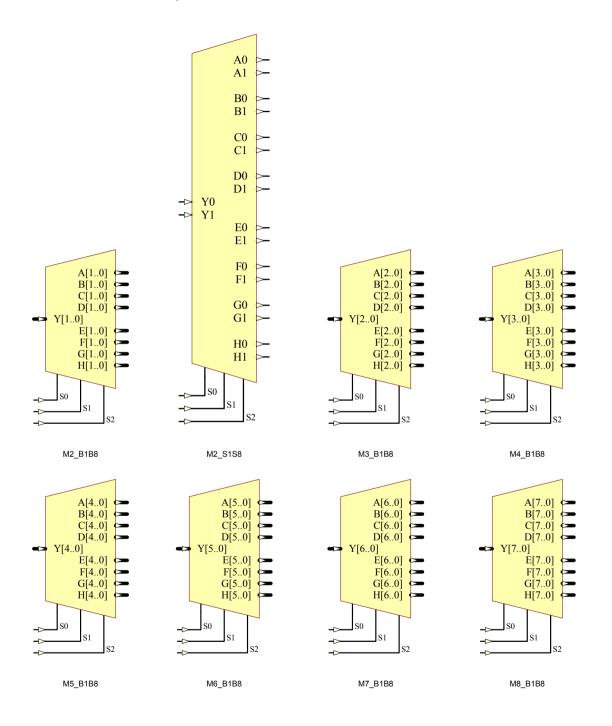

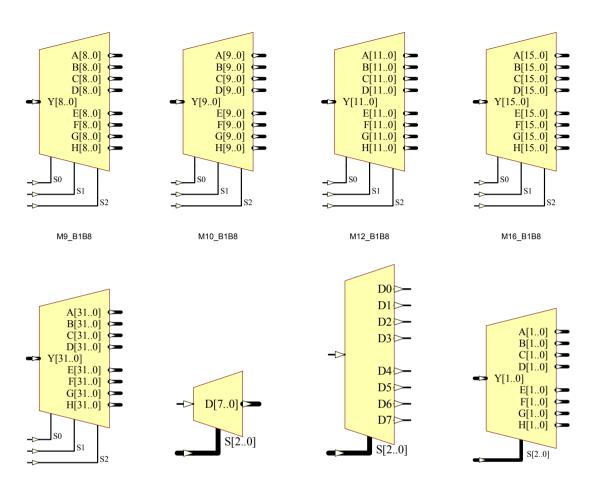

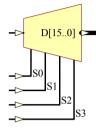

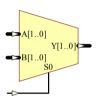

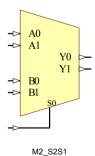

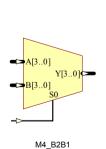

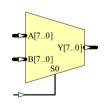

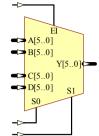

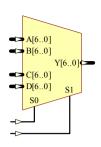

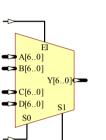

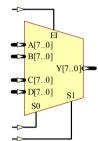

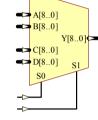

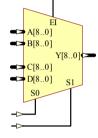

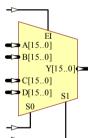

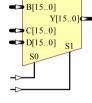

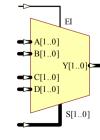

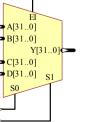

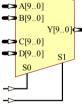

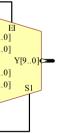

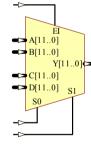

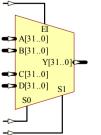

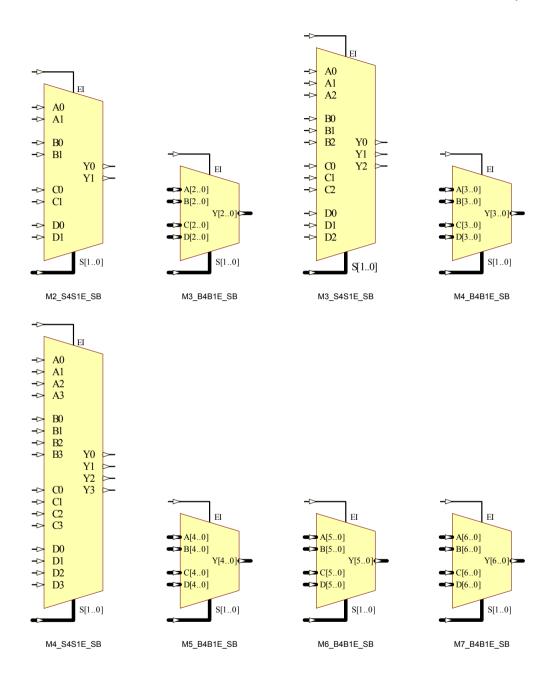

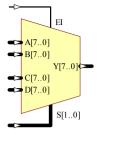

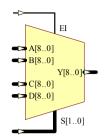

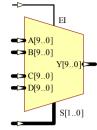

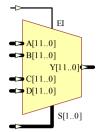

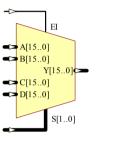

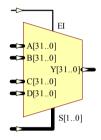

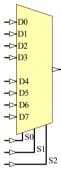

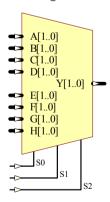

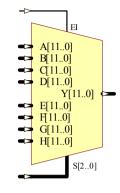

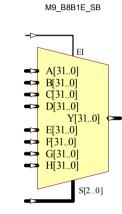

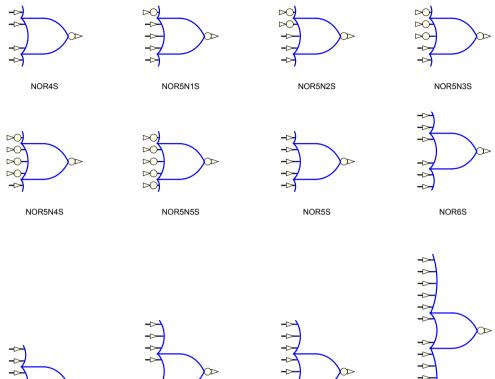

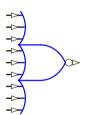

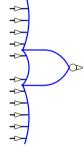

### **Schematic Symbols**

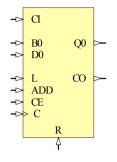

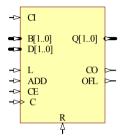

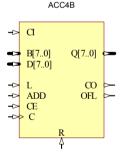

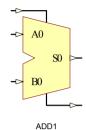

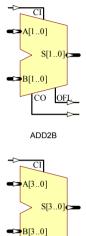

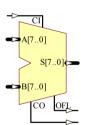

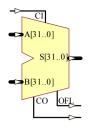

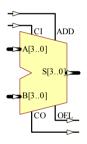

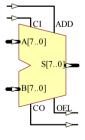

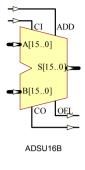

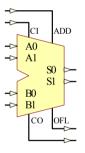

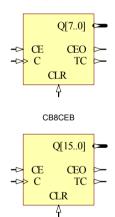

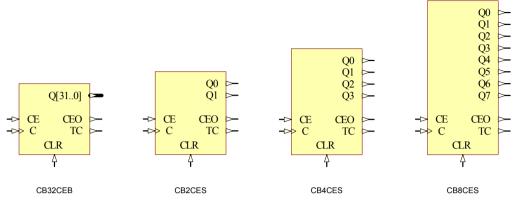

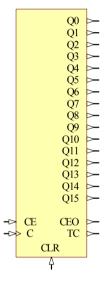

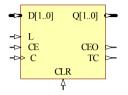

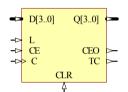

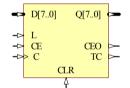

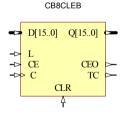

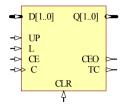

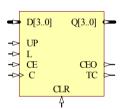

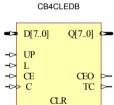

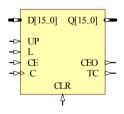

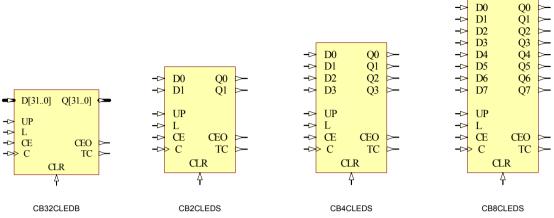

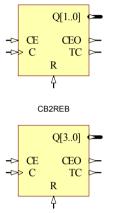

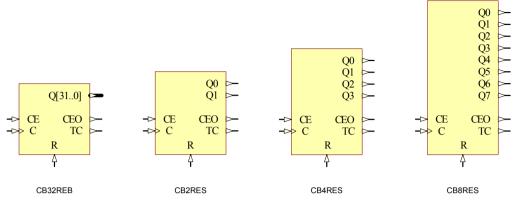

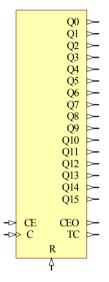

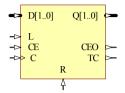

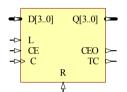

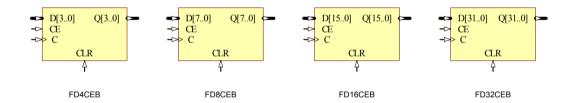

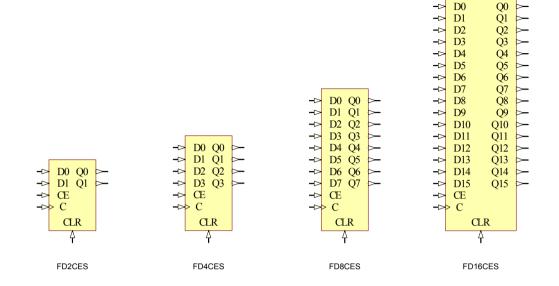

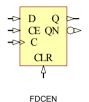

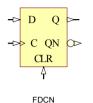

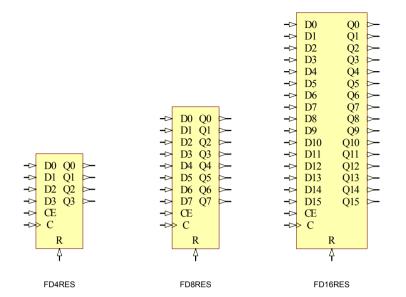

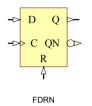

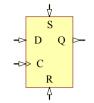

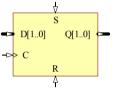

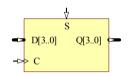

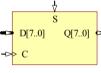

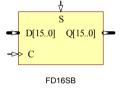

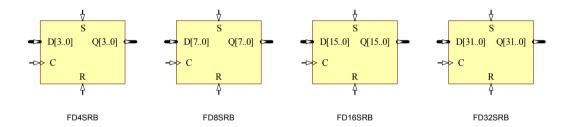

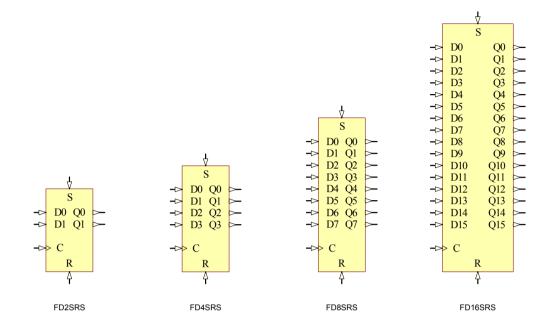

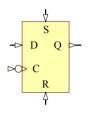

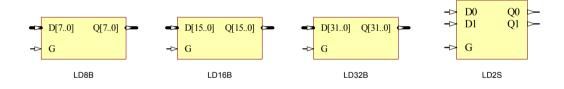

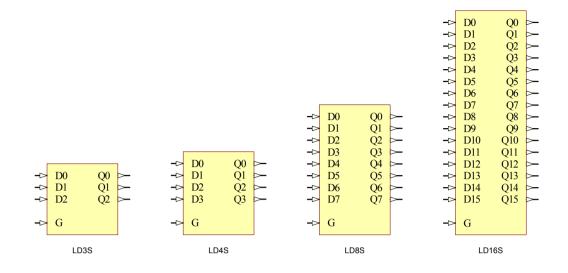

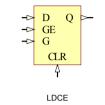

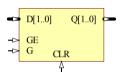

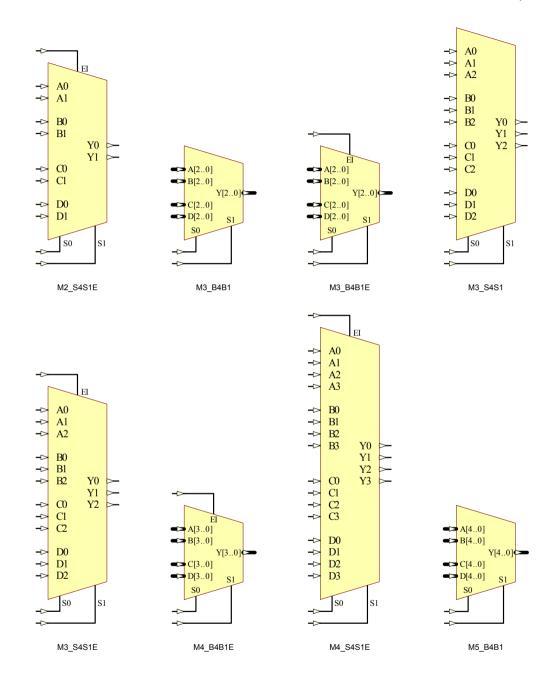

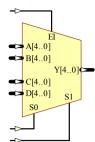

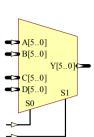

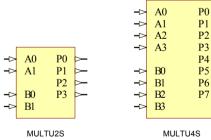

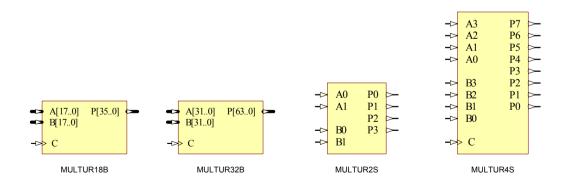

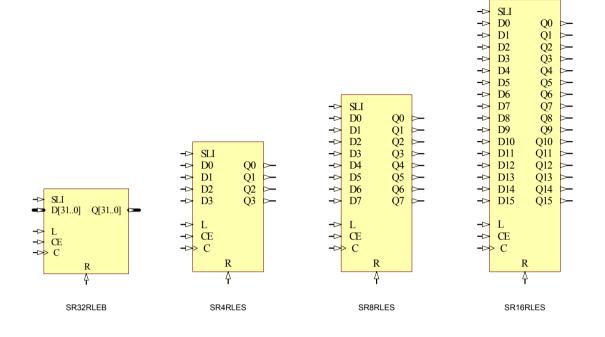

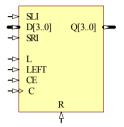

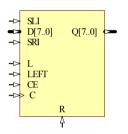

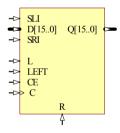

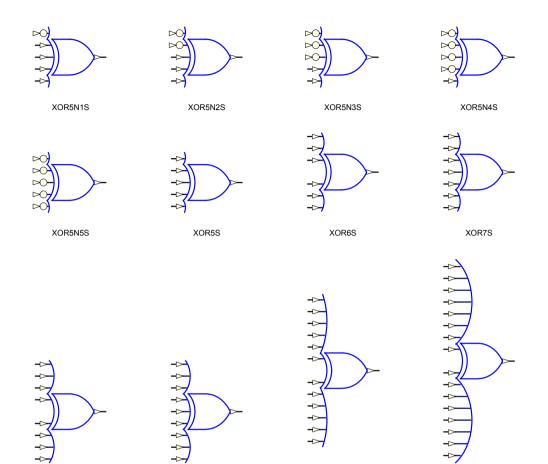

Schematic symbol representation of logic components are shown as they exist in the integrated library. In case where components have large bit size, smaller versions are used to represent their symbolic form.

# **Naming Conventions**

This section contains the naming conventions used to name the components found in the FPGA Generic integrated library. The naming conventions are available for the following functional classes:

- Arithmetic Function

- Buffer

- Bus Joiner

- Clock Divider

- <u>Clock Manager</u>

- <u>Comparator</u>

- <u>Counter</u>

- Decoder

- Encoder

- Flip-Flop

- <u>JTAG</u>

- Latch

- Logic Primitive

- Memory

- <u>Multiplexer</u>

- Numeric Connector

- Shift Register

- Shifter

- Wired Function

#### Literal Syntax

The naming convention syntax uses the following combinatorial typeface naming conventions.

| <object></object> | object is compulsory                       |

|-------------------|--------------------------------------------|

| [object]          | object is optional                         |

| object   {object} | object or combination of objects permitted |

| (object)          | object is literally omitted                |

### **Arithmetic Function**

The Arithmetic Function naming convention is defined as follows.

#### <Type>[Registered] [Bit-Size] [Version]

#### Туре

- ACC Accumulator, Loadable and Cascadable, with Signed and Unsigned Binary operations

- ADD Full Adder, with Signed and Unsigned Binary operations

- ADDF Full Adder, Unsigned

- ADSU Full Adder/Subtracter, with Signed and Unsigned Binary operations

- MULT Multiplier, Signed

- MULTU Multiplier, Unsigned

- PAR Odd/Even Parity Generators/Checker

#### Registered

R - Registered, ie. Synchronous function available for ADD, ADDF, ADSU, MULT, MULTU

#### Bit-Size

| 1, 2, 4, 8, 16, 32     | - for ACC, ADD, ADDF, ADSU |

|------------------------|----------------------------|

| 1, 2, 4, 8, 16, 18, 32 | - for MULT, MULTU          |

| 9                      | - for PAR                  |

- S Single pin version

- B Bus pin version

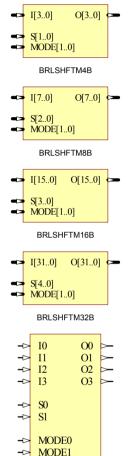

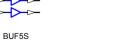

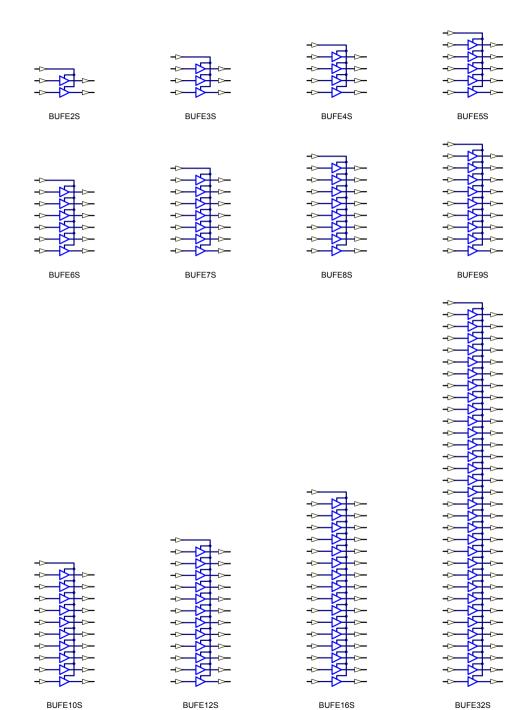

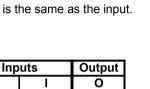

## **Buffer**

The Buffers naming convention is defined as follows.

#### <Type>[Bit-Size] [Version]

#### Туре

- BUF Normal Non-inverted Buffer

- BUFE 3-state Output Buffer with Active High Enable

- BUFT 3-state Output Buffer with Active Low Enable

- IOBUF Input/Output Buffer with common control T

- IOBUFC Input/Output Buffer with separated control Ts for each inputs

#### Bit-Size

(1), 2, 3, 4, 5, 6, 7, 8, 9, 10, 12, 16, 32

- S Single pin version

- B Bus pin version

## **Bus Joiner**

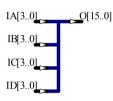

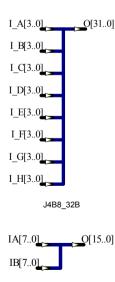

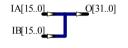

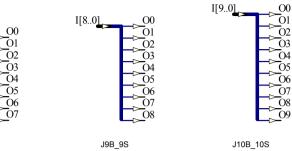

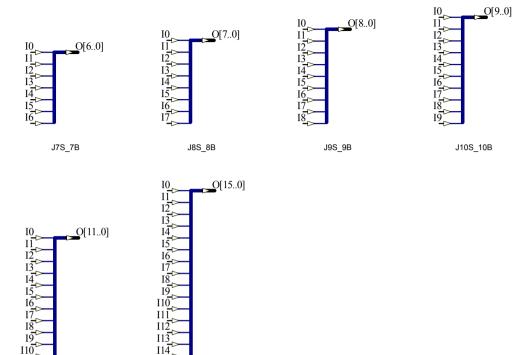

Two conventions are utilized to name the Bus Joiners. JB describes the *System Bus Joiner* and the following syntax describes the remaining Bus Joiners:

#### J<Bit><Port>[Bus-Num]\_<Bit><Port>[Bus-Num] [Pin-Type]

Bit

2, 3, 4, 5, 6, 7, 8, 9, 10, 12, 16, 32

Port

- S Single pin

- B Bus

#### Bus-Num

(1), 2, 4, 8

#### Pin-Type

X - INOUT

## **Clock Divider**

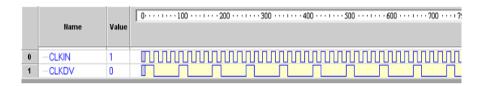

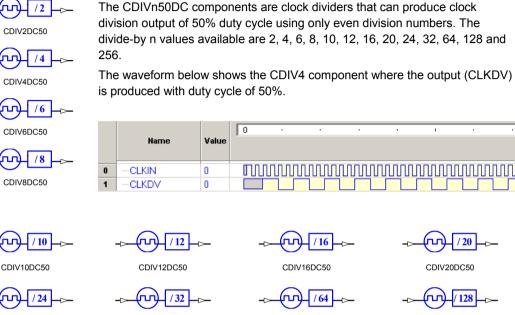

The Clock Divider naming convention is defined as follows.

#### CDIV[Num][Duty Cycle]

#### Num

$2,\,3,\,4,\,5,\,6,\,7,\,8,\,9,\,10,\,12,\,16,\,20,\,24,\,32,\,64,\,128,\,256$

Programmable versions have the following prefixes:

- N\_8 8-Bit Programmable

- N\_16 16-Bit Programmable

- N\_32 32-Bit Programmable

#### Duty Circle

DC50 - Duty Cycle of 50%

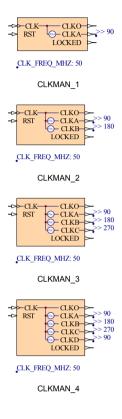

## **Clock Manager**

The Clock Manager namming convention is defined as follows.

CLKMAN\_<Num>

Num

number of operational output ports

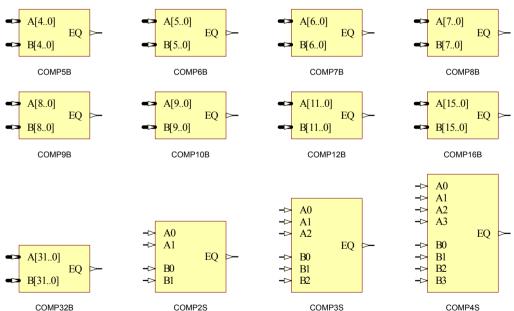

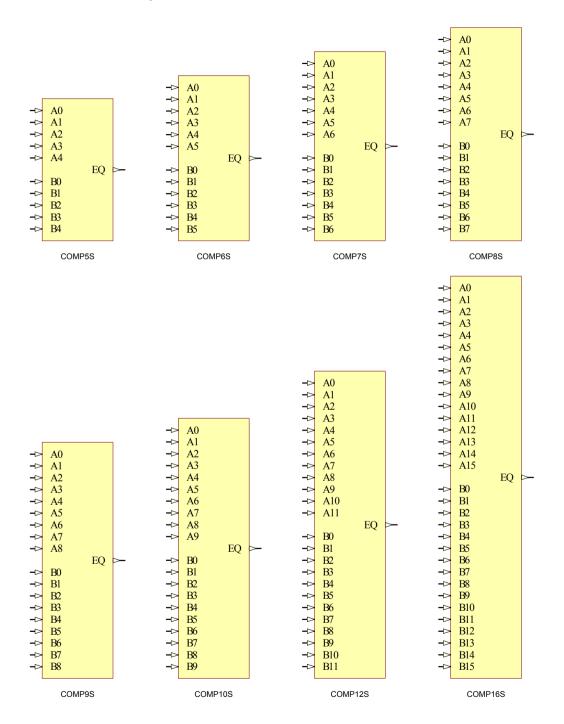

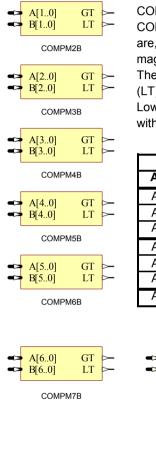

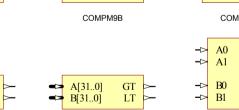

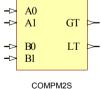

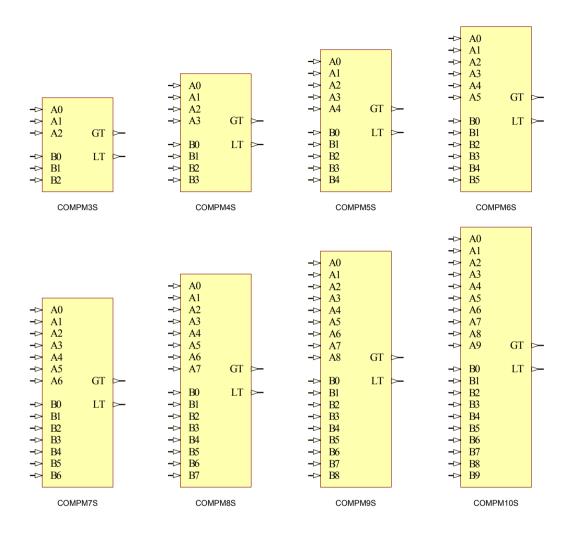

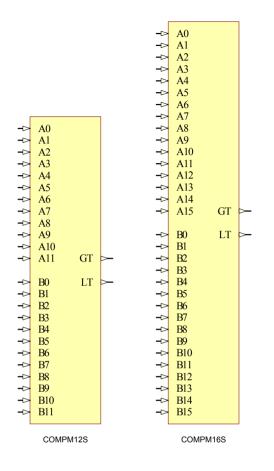

## Comparator

The Comparator naming convention is defined as follows.

#### <Type><Bit-Size>[Version]

#### Туре

COMP - Identity Comparator COMPM - Magnitude Comparator

#### Bit-Size

2, 3, 4, 5, 6, 7, 8, 9, 10, 12, 16, 32

- S Single pin version

- B Bus pin version

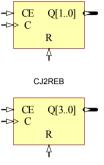

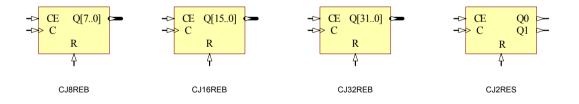

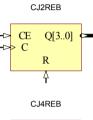

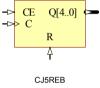

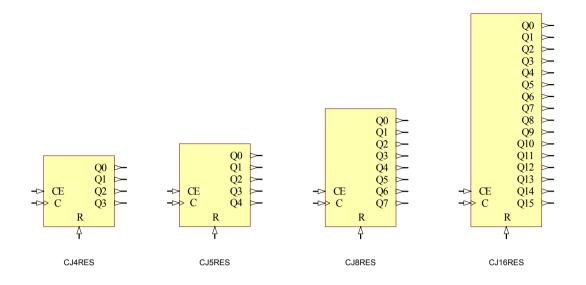

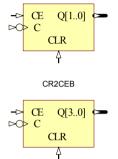

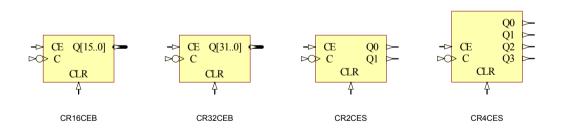

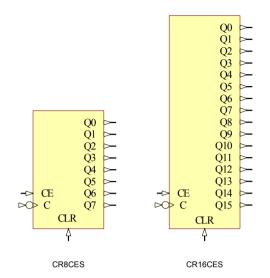

## Counter

The Counter naming convention is defined as follows.

#### C<Type><Bit-Size><Function|{Function}>[Direction] [Version]

#### Туре

| В | - Cascadable Binary Counter                     |

|---|-------------------------------------------------|

| D | - Cascadable Binary-Coded-Decimal (BCD) Counter |

| J | - Johnson Counter                               |

| R | - Negative-Edge Binary Ripple Counter           |

#### Bit-Size

| 2, 4, 8, 16, 32 | - for type B, R |

|-----------------|-----------------|

| 4               | - for type D    |

| 0 4 5 0 40 0    |                 |

2, 4, 5, 8, 16, 32 - for type J

#### Function

- C Asynchronous Clear

- R Synchronous Reset

- L Loadable (Synchronous Load)

- E Clock Enable

#### Direction

D - Bidirectional (Up/Down)

- S Single pin version

- B Bus pin version

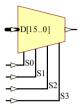

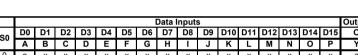

## Decoder

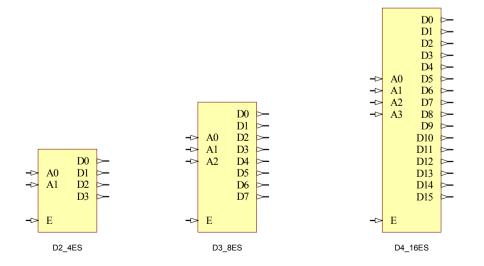

Various functional types of Decoders are available to accommodate design needs. The naming convention is defined as follows.

#### D<Type>[Function] [Version]

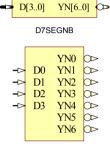

#### Туре

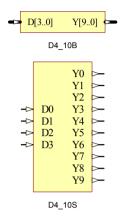

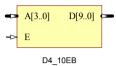

- 4\_10 Binary-Coded-Decimal (BCD) Decoder

- 7SEG 7-Segment-Display Decoder for Common-Cathode LED (Active High Output)

- 7SEGN 7-Segment-Display Decoder for Common-Anode LED (Active Low Output)

- *n\_m* Binary *n*-bit to *m*-bit Decoder, available in 2\_4, 3\_8, 4\_16, 5\_32

#### Function

E - With Enable. (for 4\_10, *n\_m* only)

- S Single pin version

- B Bus pin version

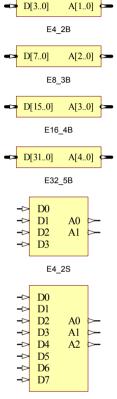

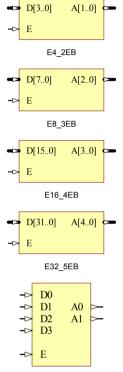

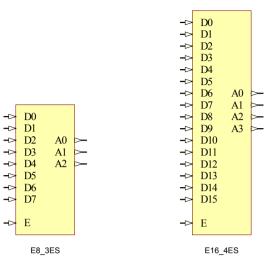

## Encoder

The Encoder naming convention is defined as follows.

#### E<Type>[Version]

#### Туре

- 10\_4 Binary-Coded-Decimal (BCD) Encoder

- *n\_m n*-bit to *m*-bit Priority Encoder, available in 4\_2, 8\_3, 10\_4, 16\_4, 32\_5

#### Function

E - With Enable

- S Single pin version

- B Bus pin version

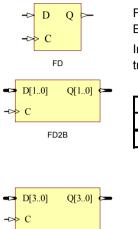

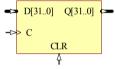

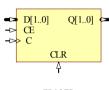

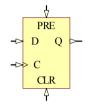

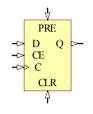

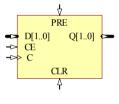

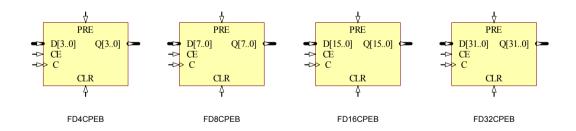

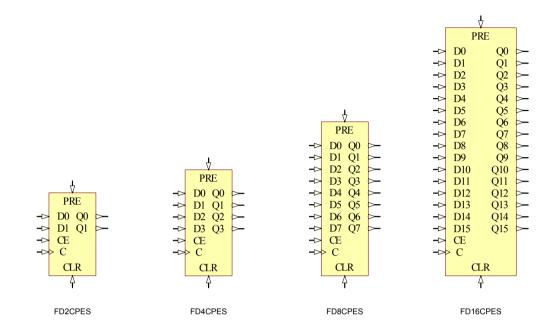

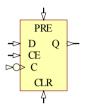

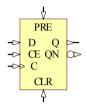

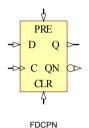

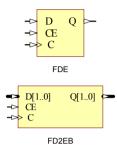

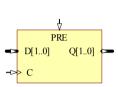

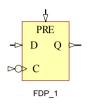

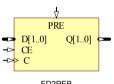

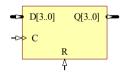

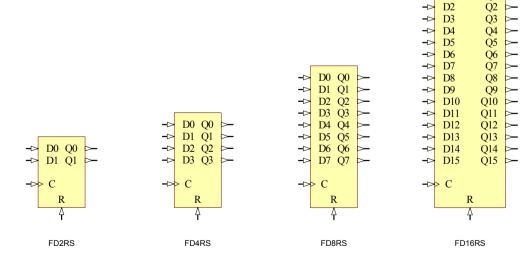

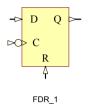

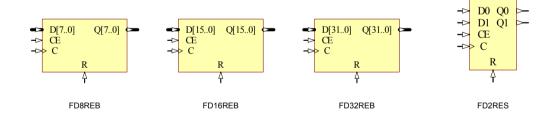

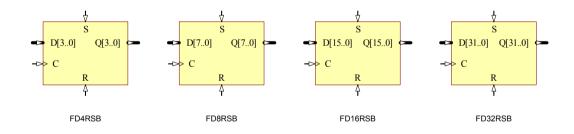

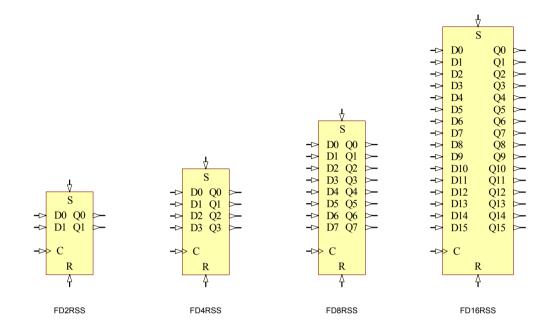

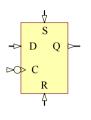

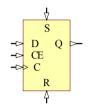

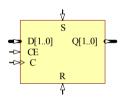

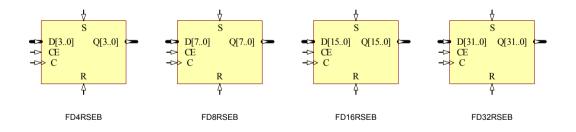

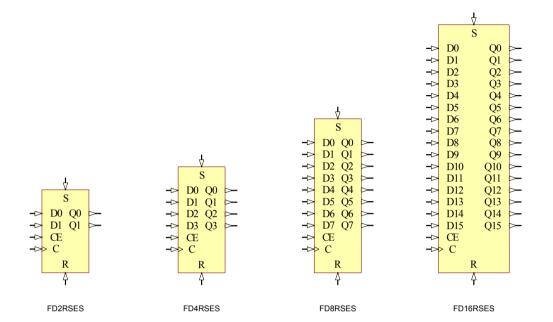

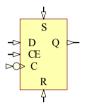

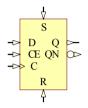

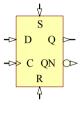

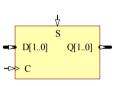

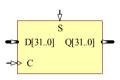

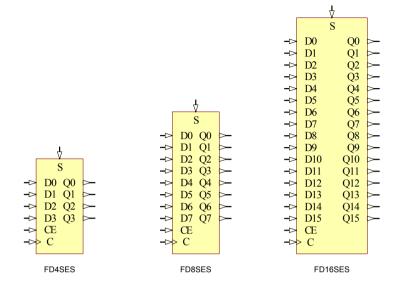

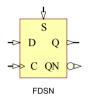

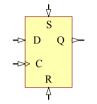

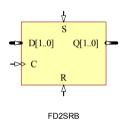

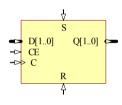

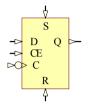

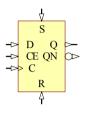

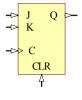

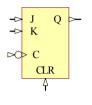

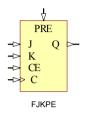

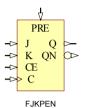

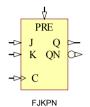

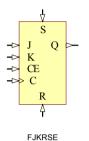

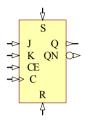

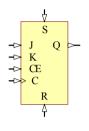

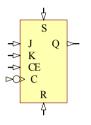

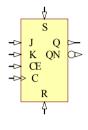

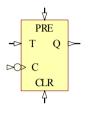

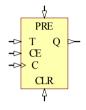

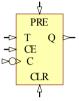

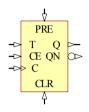

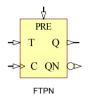

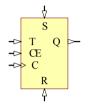

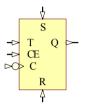

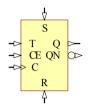

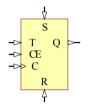

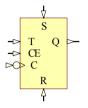

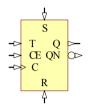

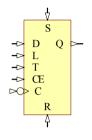

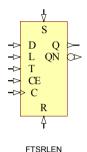

## Flip-Flop

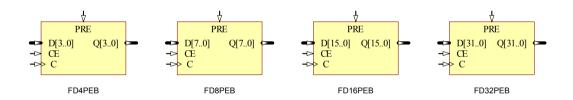

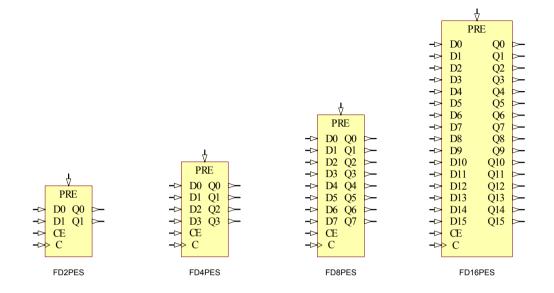

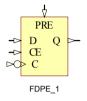

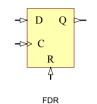

The Flip-Flop naming convention is defined as follows.

#### F<Type>[Bit-Size] [Function | {Function}] [State] [Version]

#### Туре

- D D Flip-Flop

- JK JK Flip-Flop

- T Toggle Flip-Flop

#### Bit-Size

- (1), 2, 4, 8, 16, 32- for type D

- (1) for other types

#### Function

- C Asynchronous Clear

- R Synchronous Reset (i.e. Synchronous Clear)

- P Asynchronous Preset

- S Synchronous Set (i.e. Synchronous Preset)

- E Clock Enable

#### State

- \_1 Negative Clock Edge Triggered

- N With Non-inverted and Inverted Outputs

- S Single pin version

- B Bus pin version

## **JTAG**

The JTAG naming convention is defined as follows.

#### <Type>

Туре

NEXUS\_JTAG\_PORT - Soft Nexus-Chain Connector

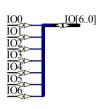

## Latch

The Latch naming convention is defined as follows.

#### LD[Bit-Size][Function|{Function}][State][Version]

#### Bit-Size

(1), 2, 3, 4, 8, 16, 32

#### Function

- C Clear

- P Preset

- E Gate Enable

#### State

\_1 - Inverted Gate

- S Single pin version

- B Bus pin version

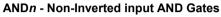

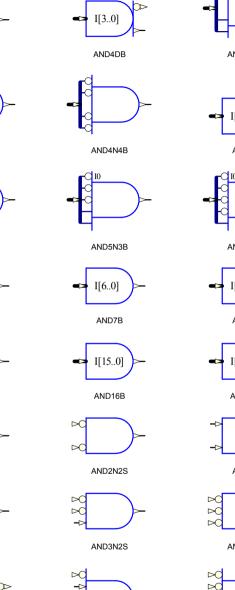

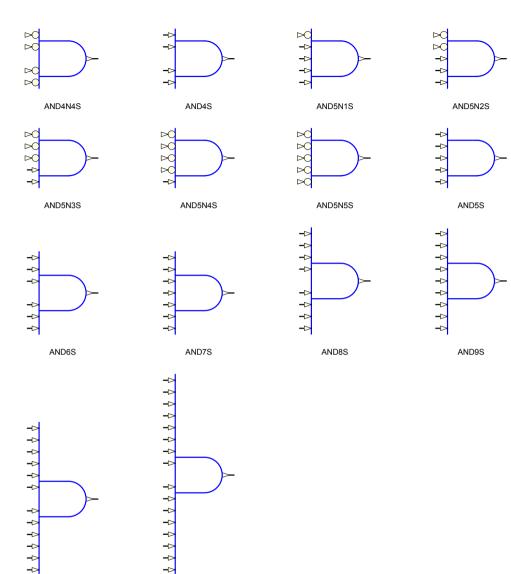

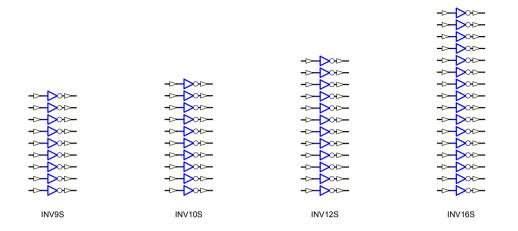

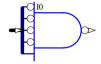

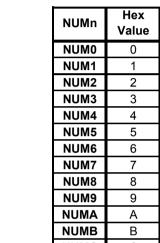

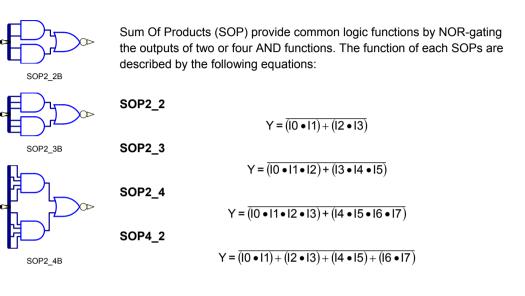

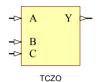

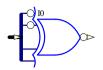

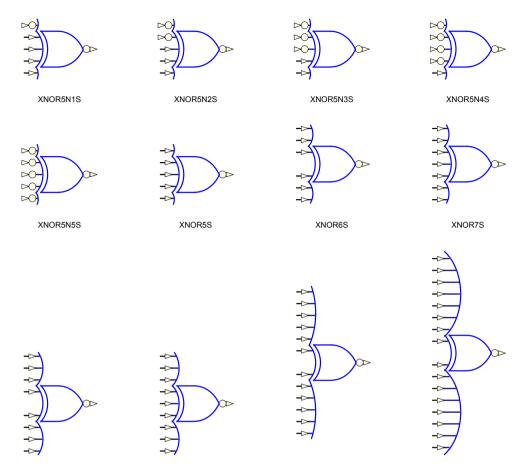

### **Logic Primitive**

The Logic Primitive naming convention is defined as follows.

<Type><Bit-Size>[Function] [Version]

#### Туре

- AND AND Gate

- NAND NAND Gate

- OR OR Gate

- NOR NOR Gate

- XNOR Exclusive-NOR Gate

- XOR Exclusive-OR Gate

- INV Inverter

- TCZO True/Complement, Zero/One Element

- SOP Sum of Products

#### Bit-Size

- 2, 3, 4, 5, 6, 7, 8, 9, 12, 16, 32 for AND, NAND, OR, NOR, XNOR, XOR

- (1), 2, 3, 4, 5, 6, 7, 8, 9, 10, 12, 16, 32 for INV

- *m\_n* Applicable to SOP only. Indicates *m* number of *n*-input AND gates in the Sum of Products combination, available in 2\_2, 2\_3, 2\_4, 4\_2

#### Function

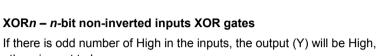

(Applicable to AND, NAND, OR, NOR, XNOR and XOR only)

Nm - m inverted inputs

(applicable to Bit-Size 2, 3, 4, 5, where *m* is less than or equal to Bit-Size)

D - Dual Output (applicable for AND and OR gates with a Bit-Size of 2, 3, 4)

- S Single pin version

- B Bus pin version

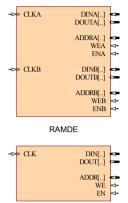

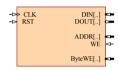

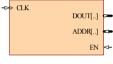

### Memory

The Memory component naming convention is defined as follows.

#### <Type><Port Type>[Function|{Function}]

#### Туре

- RAM Random Access Memory

- ROM Read Only Memory

#### Port Type

- S Single Port

- D Dual Port

#### Function

- E With Enable

- R With Reset

- B Byte Addressable

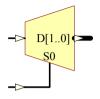

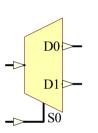

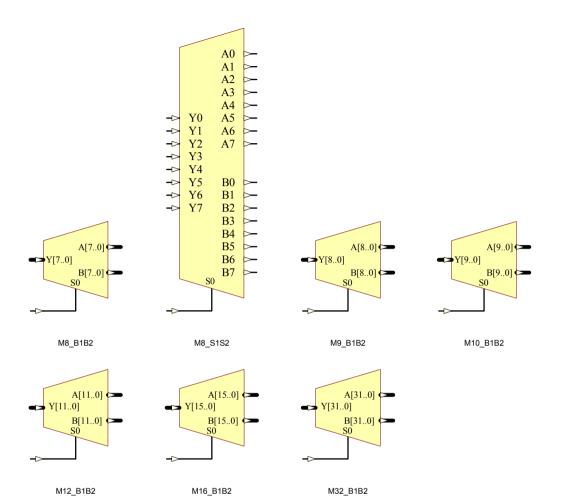

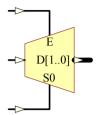

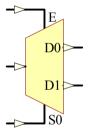

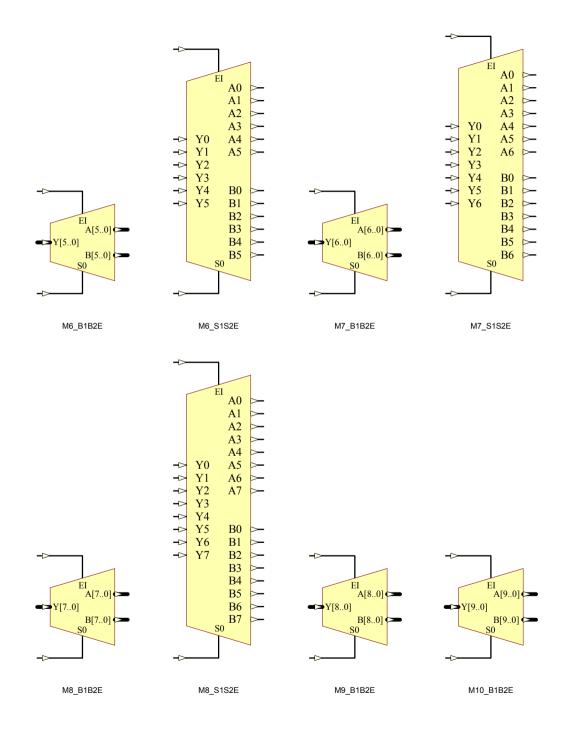

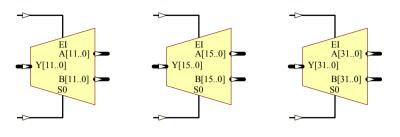

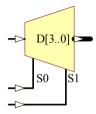

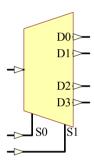

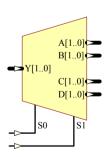

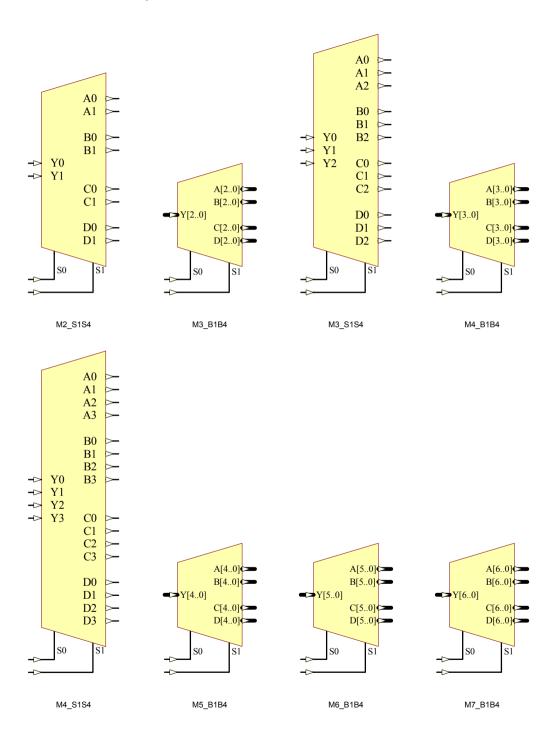

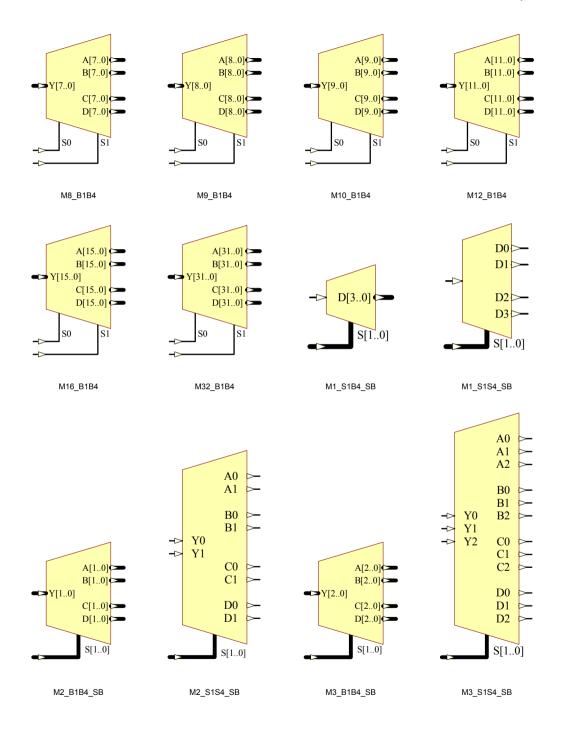

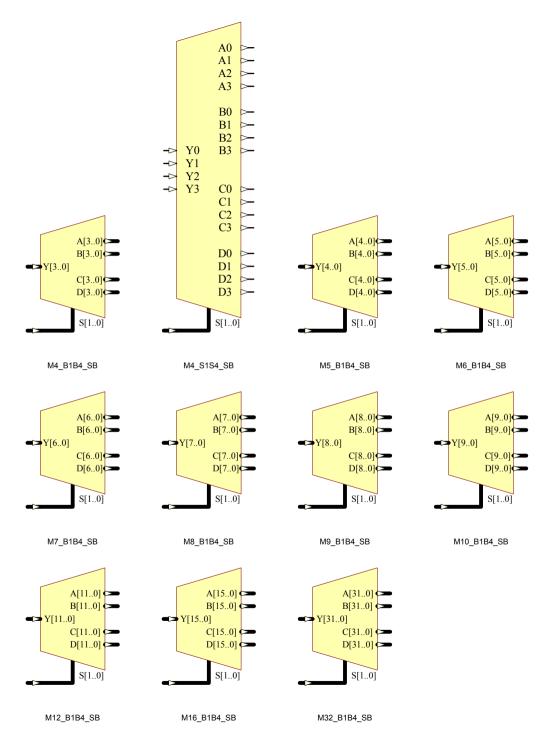

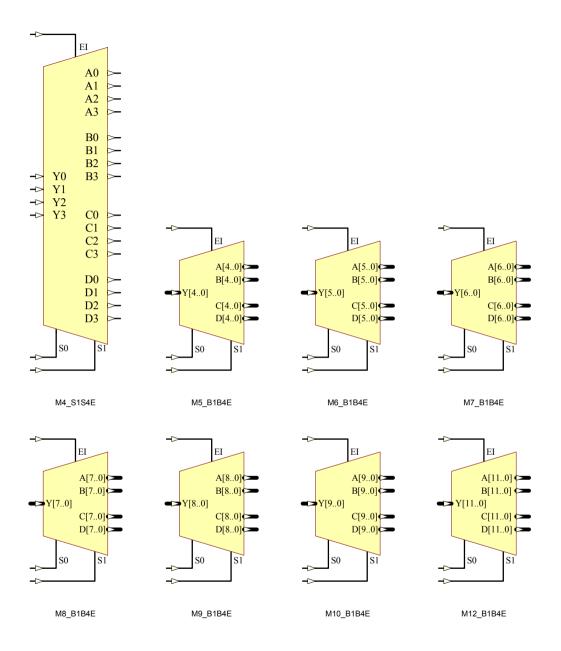

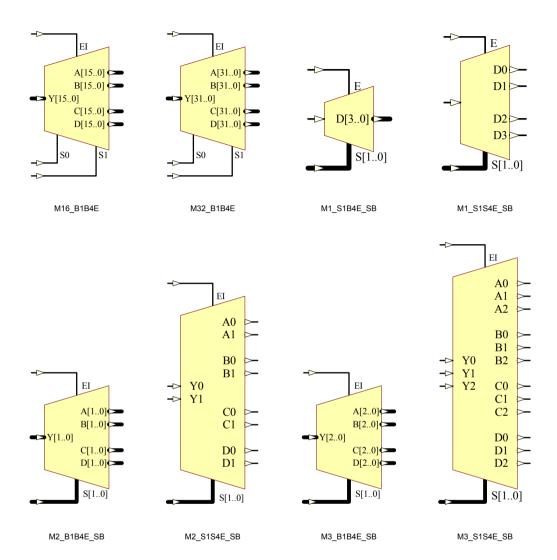

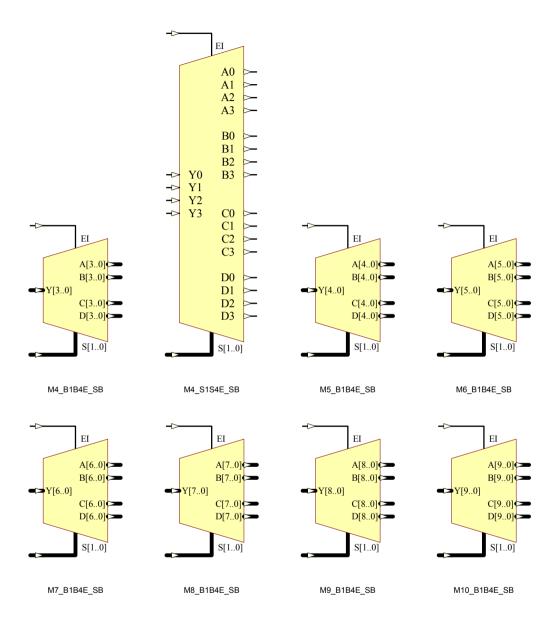

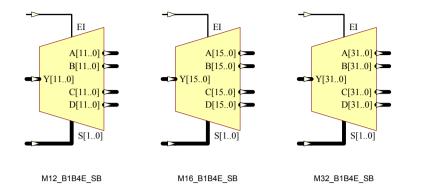

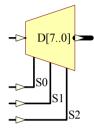

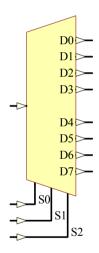

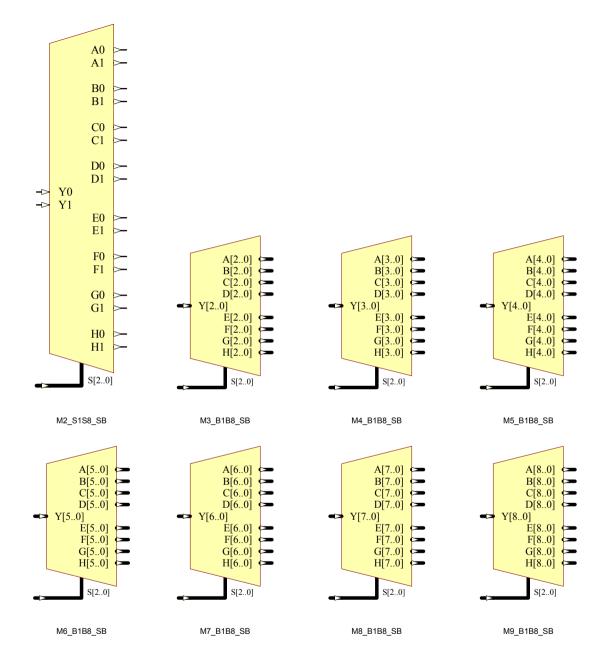

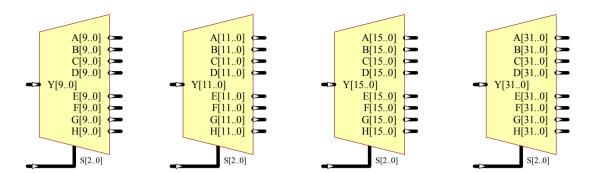

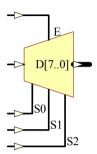

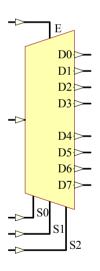

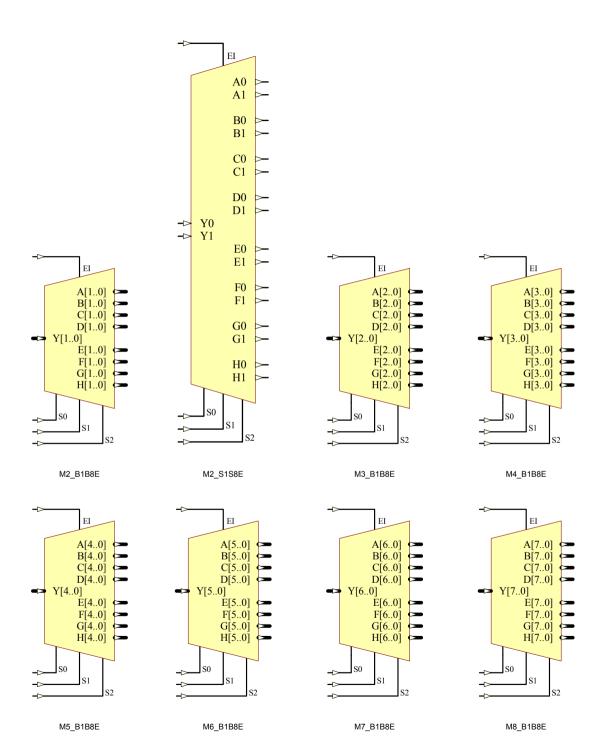

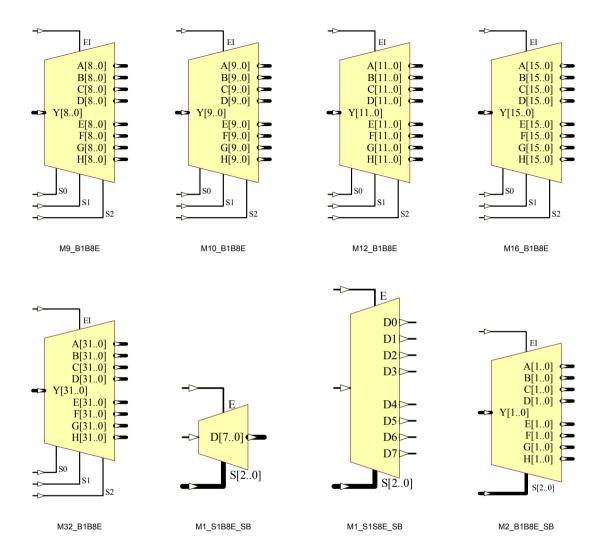

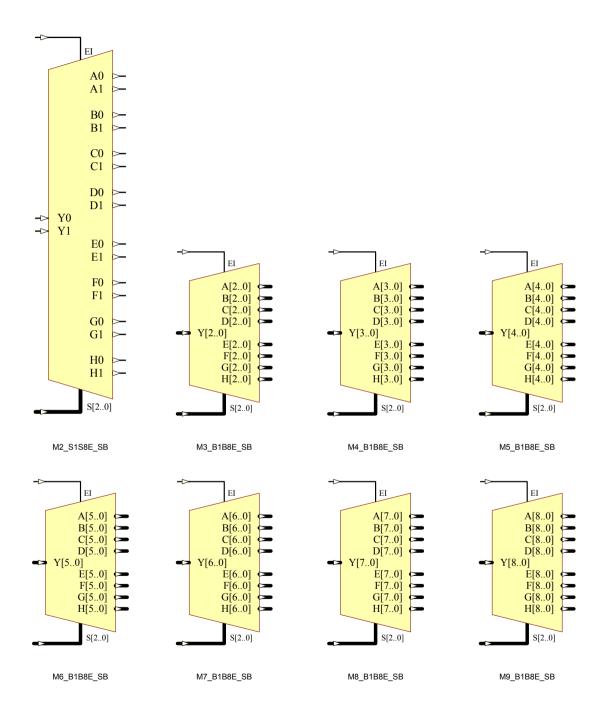

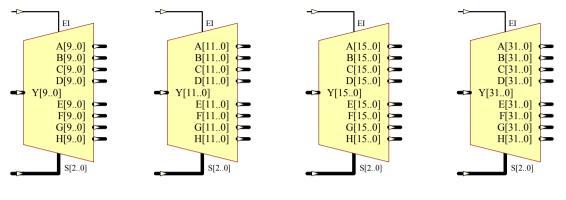

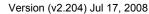

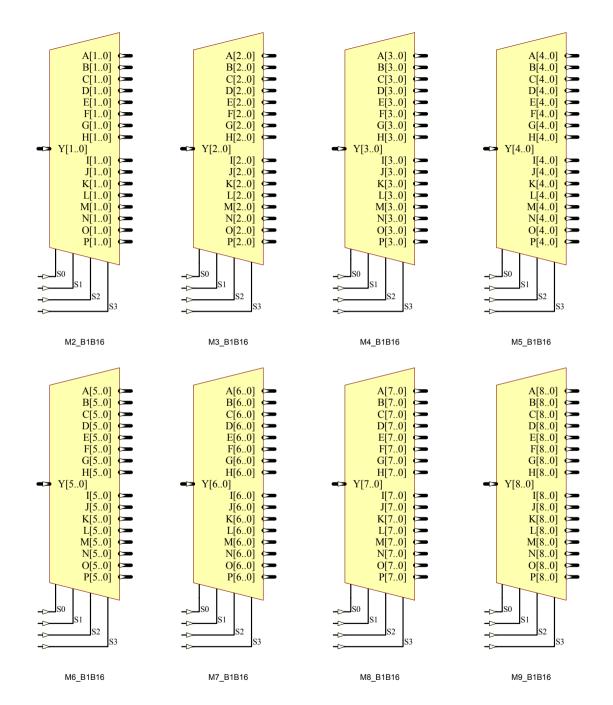

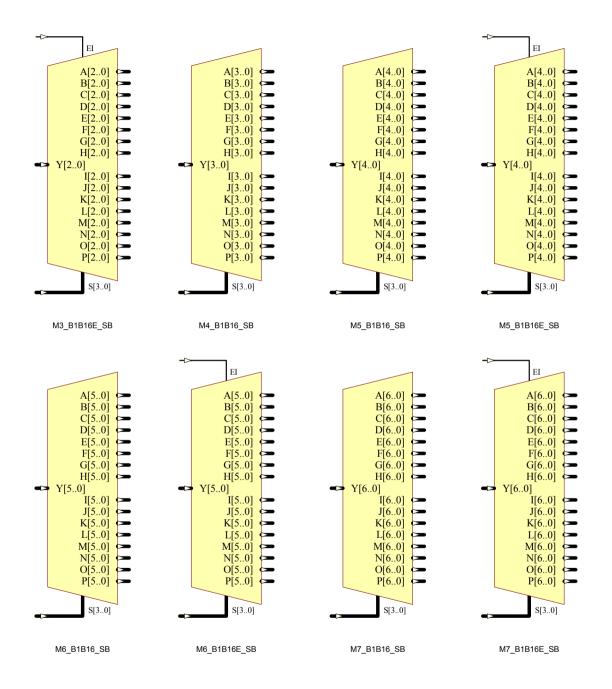

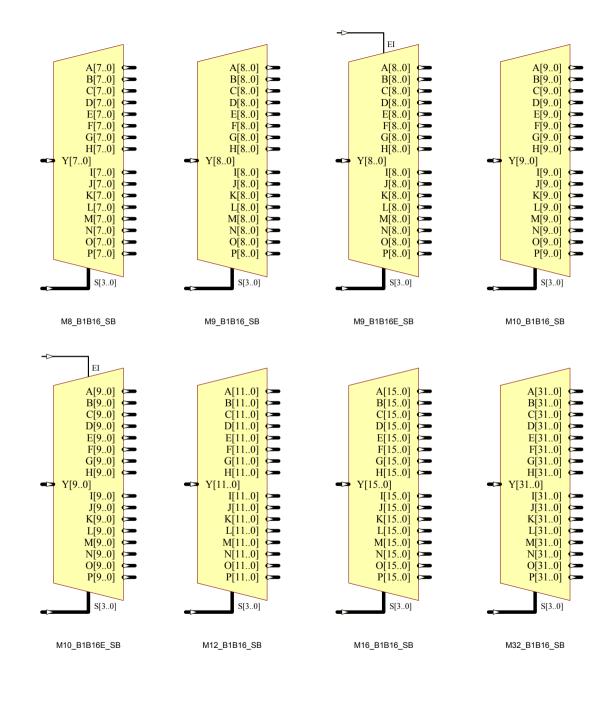

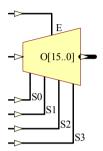

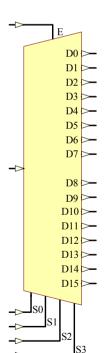

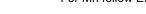

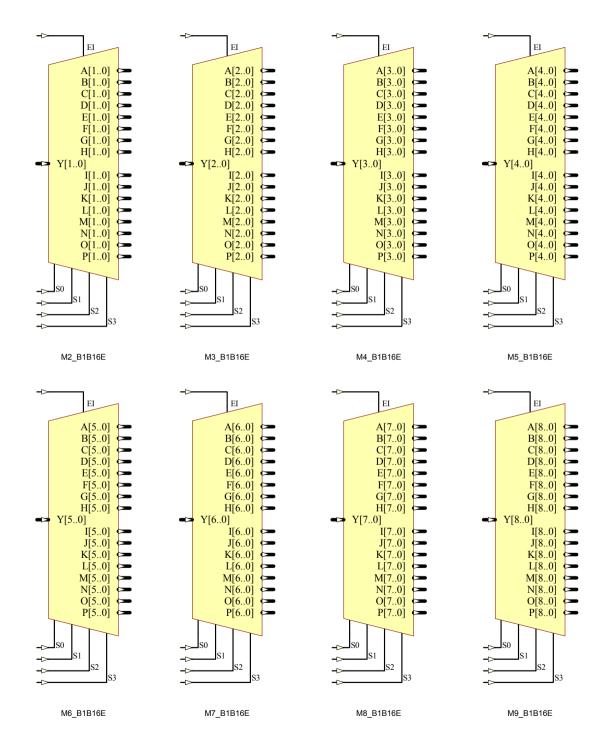

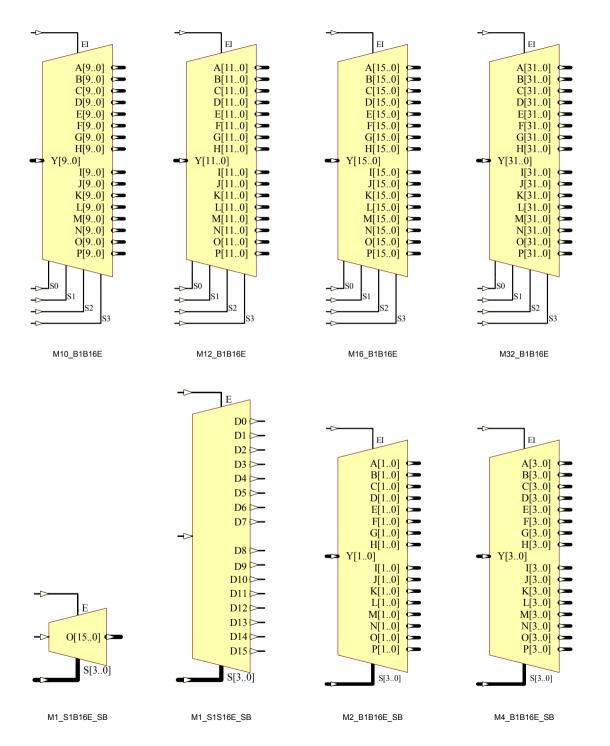

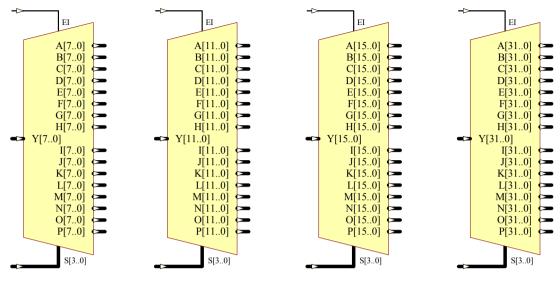

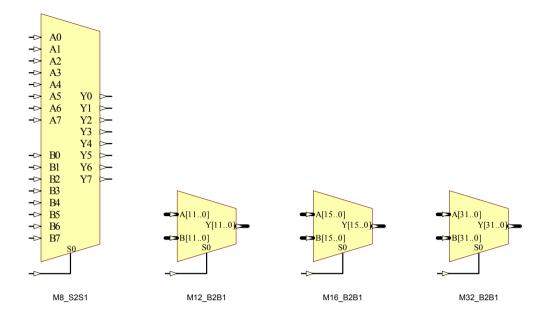

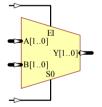

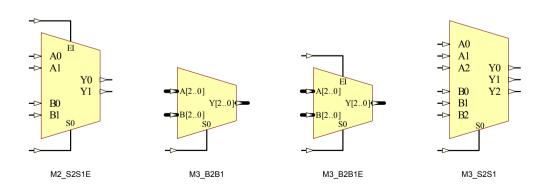

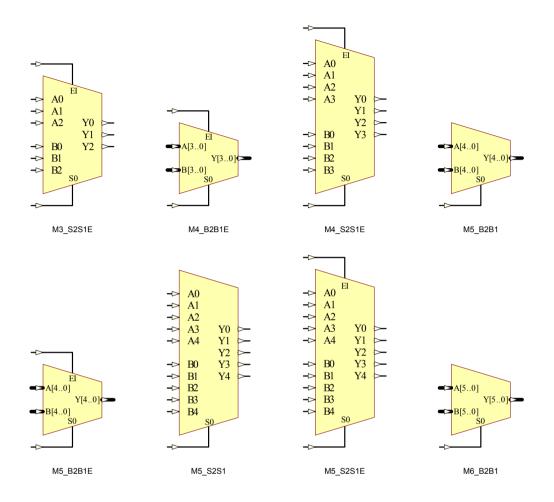

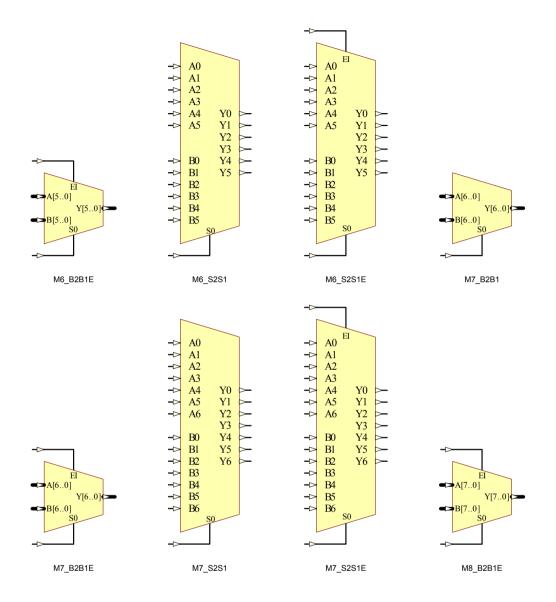

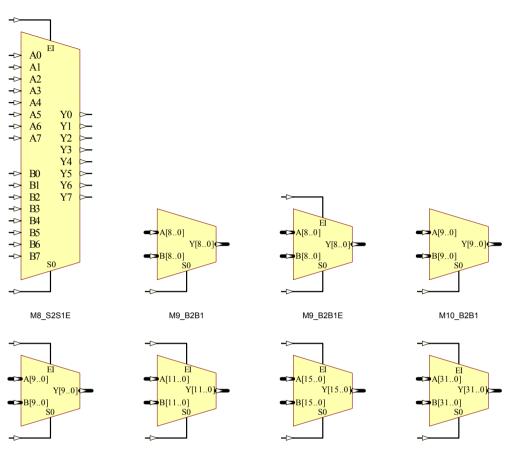

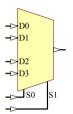

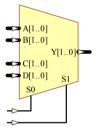

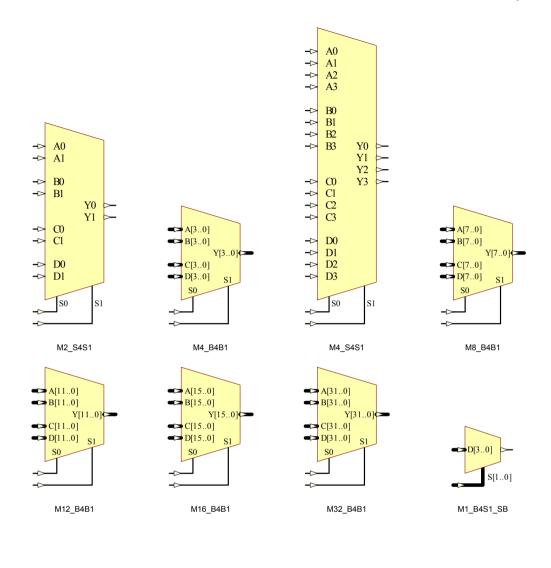

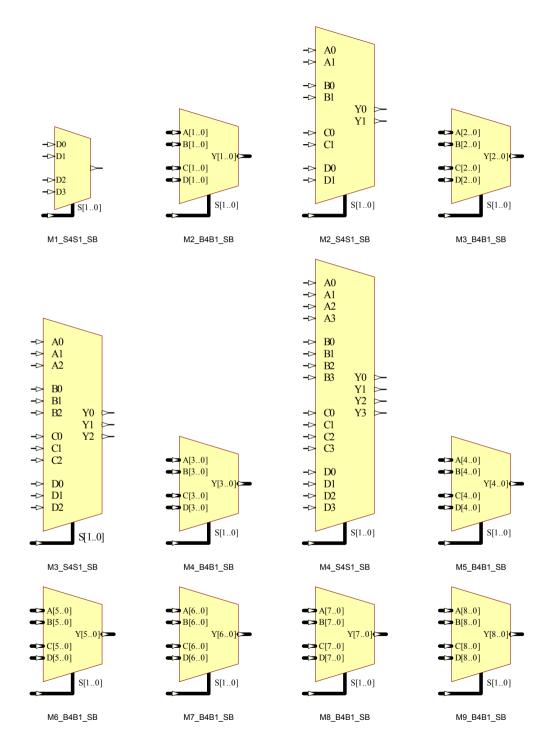

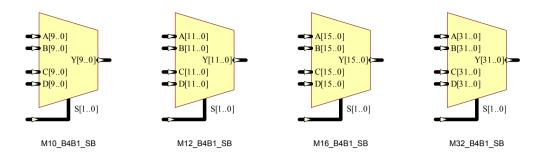

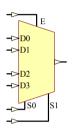

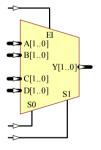

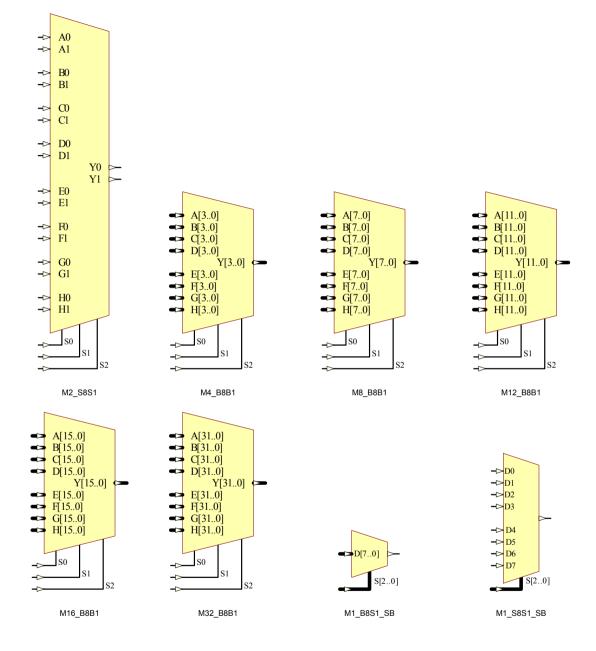

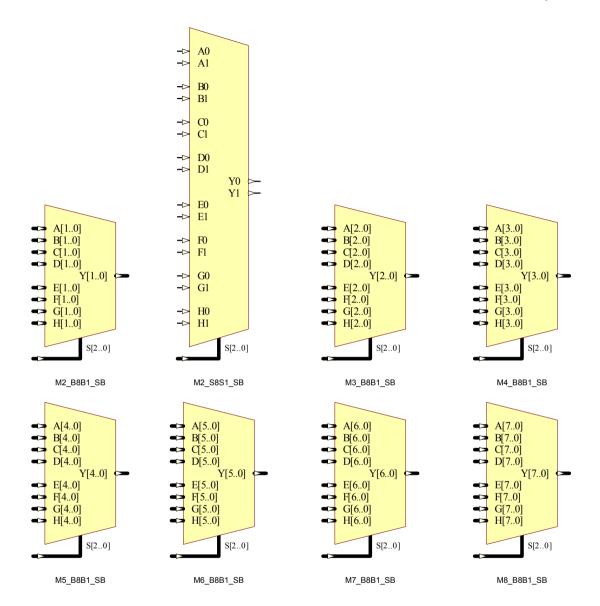

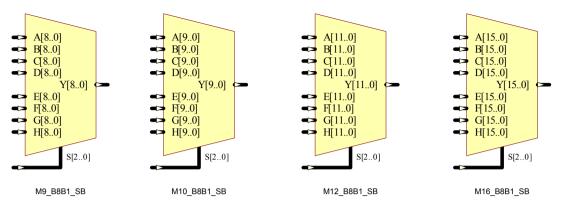

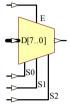

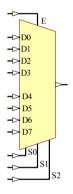

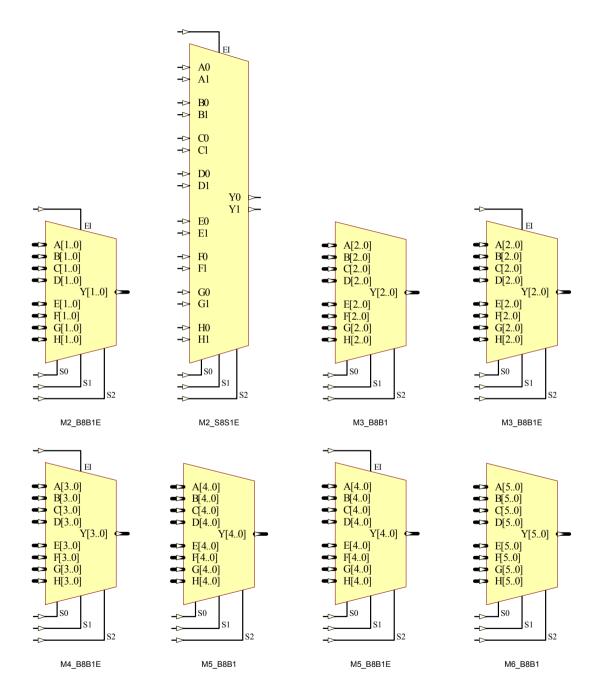

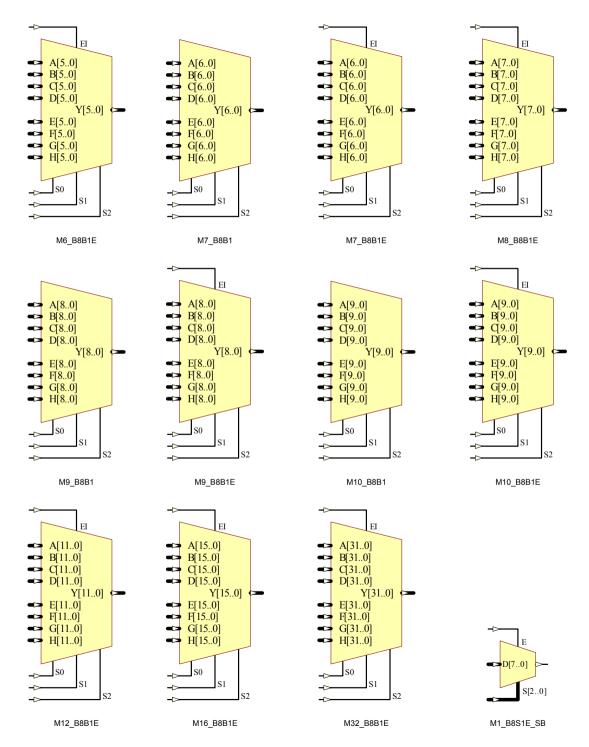

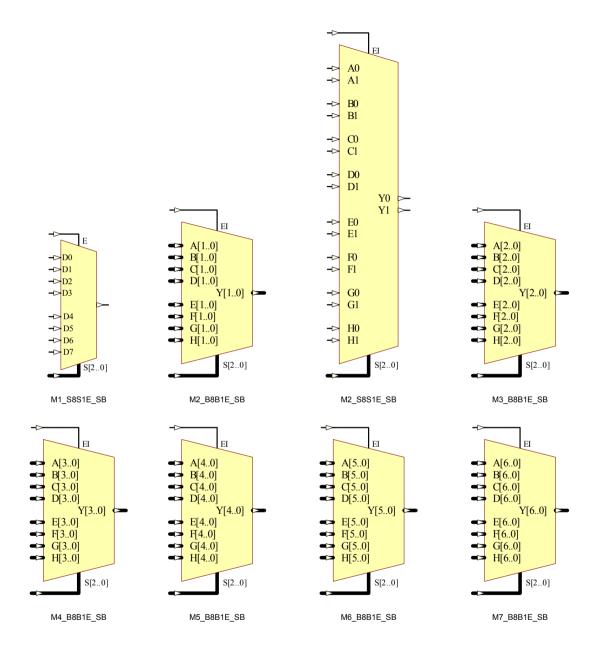

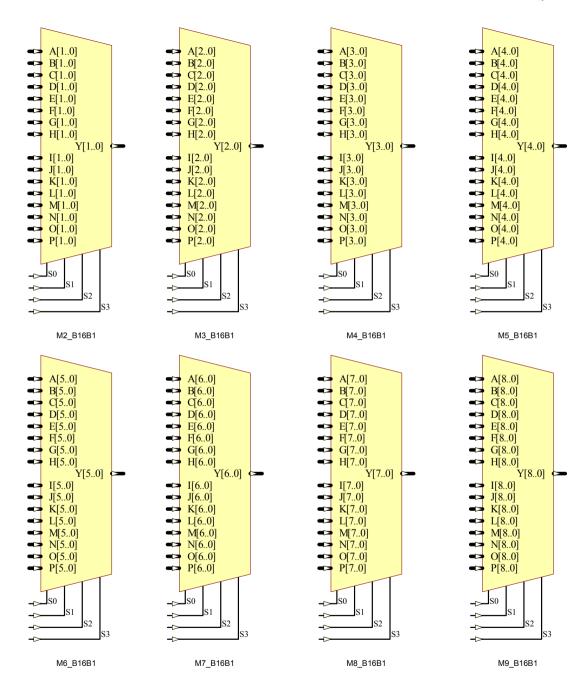

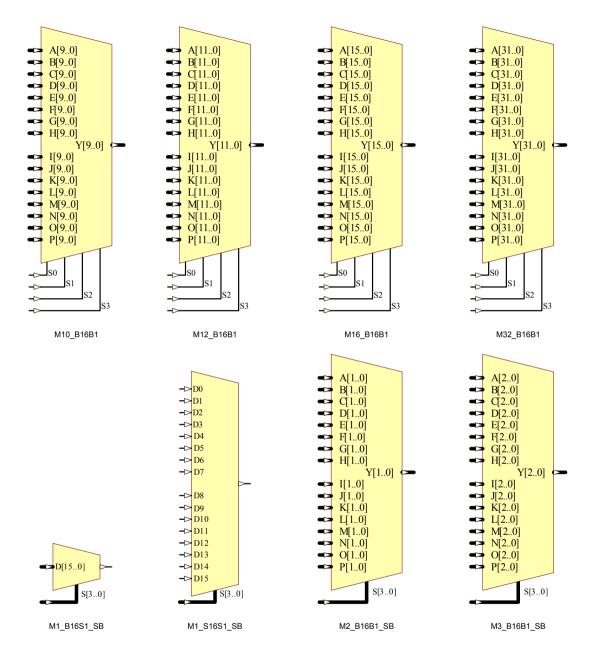

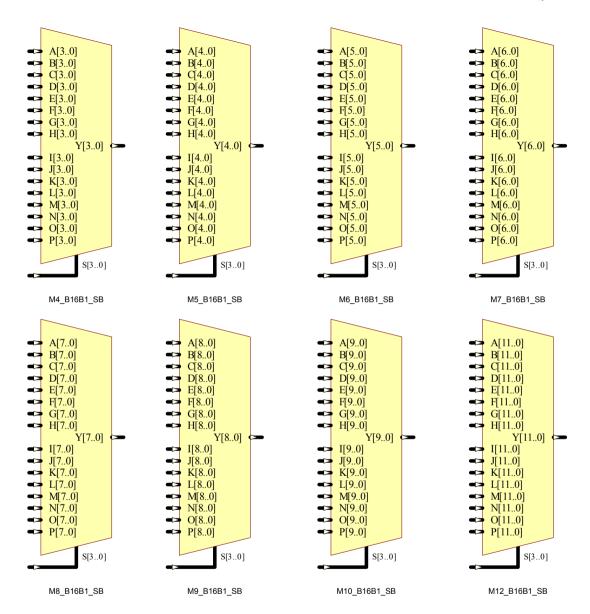

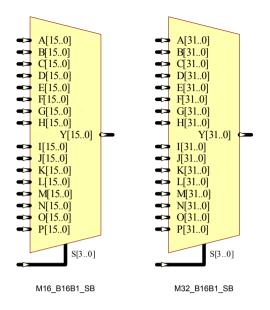

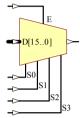

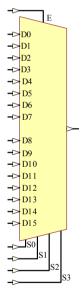

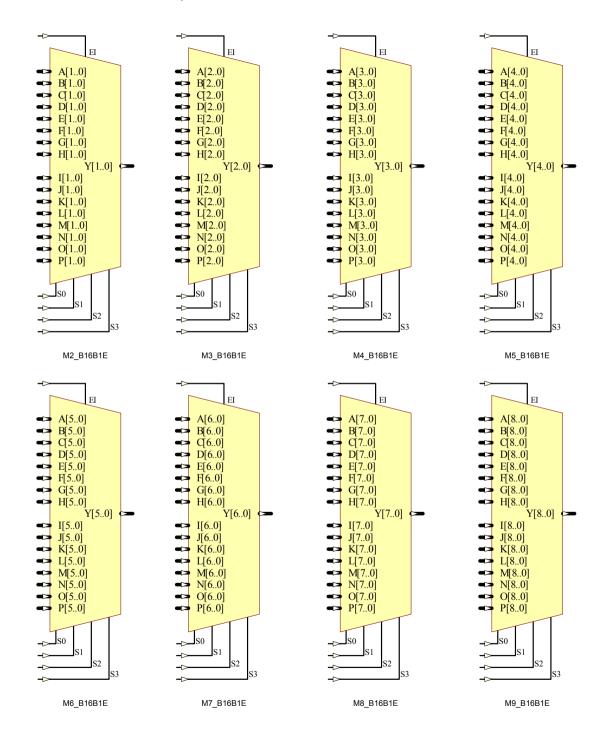

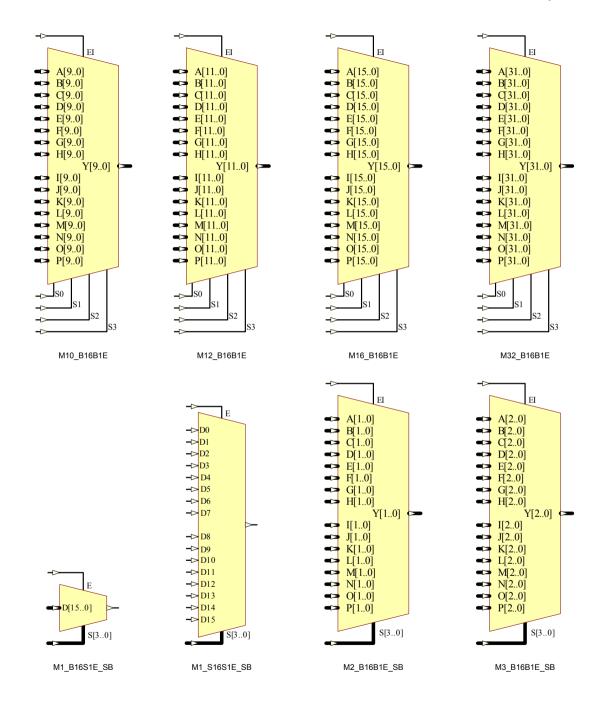

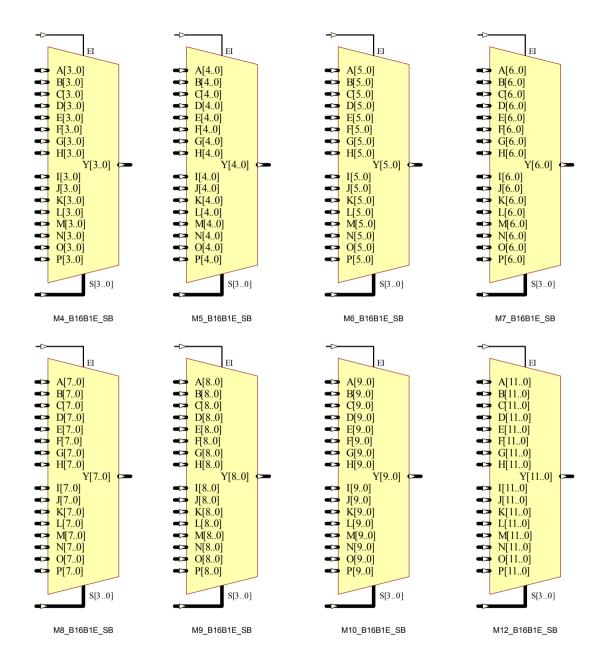

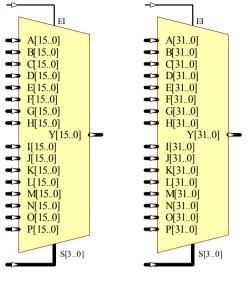

### **Multiplexer**

The Multiplexer naming convention is defined as follows.

#### M<Data Width>\_<Type>[Function][Select]

#### Data Width

1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 12, 16, 32

#### Туре

- BnB1 n-to-1 Multiplexer; n number of buses switch to 1 bus, bus size is defined by Data Width.

- SnS1 *n*-to-1 Multiplexer; *n* groups of single bit pins switch to 1 group, number of pins in a group is defined by Data Width.

- BnS1 n-to-1 Multiplexer; an n-bit bus switches to 1-bit single pin, apply for Data Width = 1.

- B1Bn 1-to-n DeMultiplexer; 1 bus switch to n number of busses, bus size is defined by Data Width.

- S1Sn 1-to-n DeMultiplexer; 1 group of single bit pins switch to n group, number of pins in a group is defined by Data Width.

- S1Bn 1-to-n DeMultiplexer; 1-bit single pin switches to an n-bit bus, apply for Data Width = 1.

\**n* is available in 2, 4, 8, 16

#### Function

E - With Enable

#### Select

\_SB - With Bus Version Select

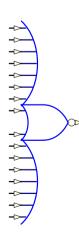

## **Numeric Connector**

These components are available for binary logic connections. The naming convention is as follows.

#### NUM<Hex Value>

Hex Value

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F

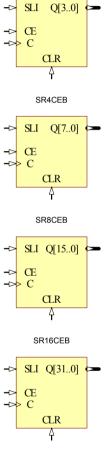

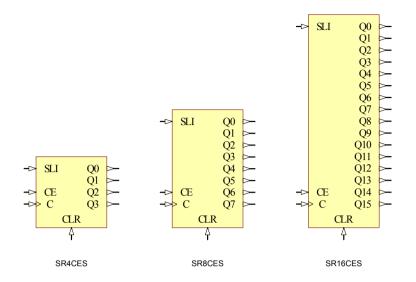

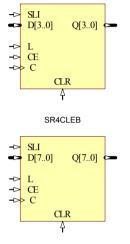

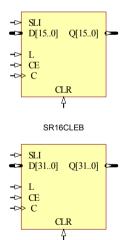

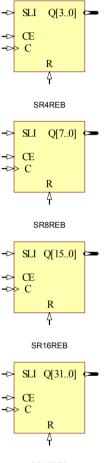

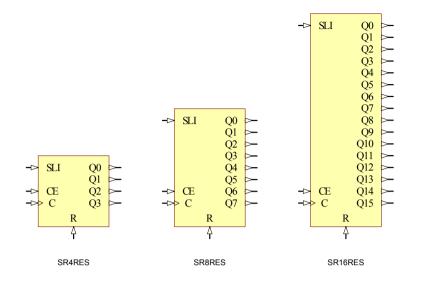

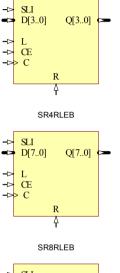

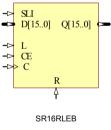

### **Shift Register**

The Shift Register naming convention is defined as follows.

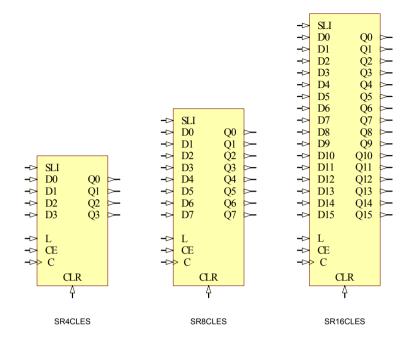

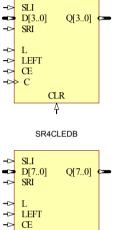

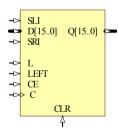

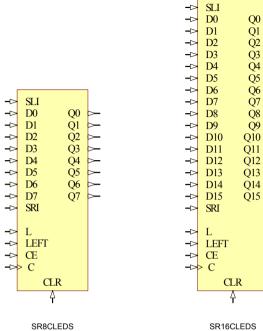

#### SR<Bit-Size><Function | {Function}>[Direction] [Version]

#### Bit-Size

4, 8, 16, 32

#### Function

- C Asynchronous Clear

- R Synchronous Reset (i.e. Synchronous Clear)

- L Loadable (Synchronous Load, ie. Parallel In)

- E Clock Enable

#### Direction

D - Bidirectional (with left or right shift option)

- S Single pin version

- B Bus pin version

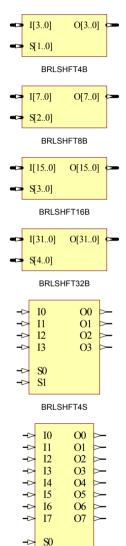

## Shifter

The Shifter naming convention is defined as follows.

#### BRLSHFT<Bit-Size><Function>[Version]

#### Bit-Size

4, 8, 16, 32

#### Function

M - Fill Mode and direction control

- S Single pin version

- B Bus pin version

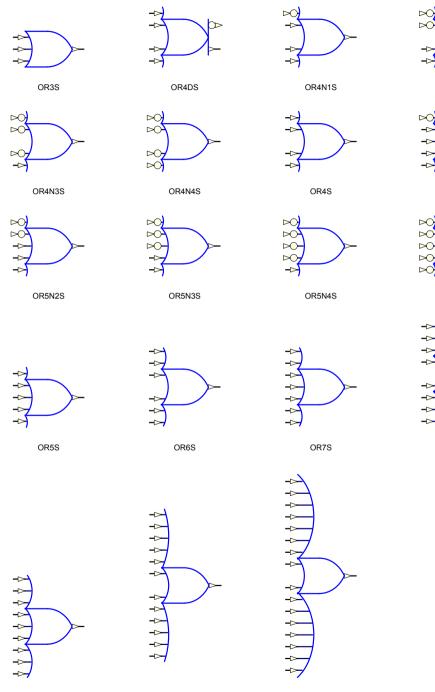

## **Wired Function**

The Wired Function naming convention is defined as follows.

#### <Type>[Bit-Size]<Version>

#### Туре

| PULLUP | <ul> <li>Pull-up Resistor</li> </ul> |

|--------|--------------------------------------|

PULLDOWN - Pull-down Resistor

#### Bit-Size

(1), 2, 4, 8, 12, 16, 32

- S Single pin version

- B Bus pin version

# **Functional Classes**

This section lists the name of all components along with a short description. Components are grouped according to functional class; the following classes are available:

- Arithmetic Function

- <u>Buffer</u>

- Bus Joiner

- Clock Divider

- <u>Clock Manager</u>

- <u>Comparator</u>

- <u>Counter</u>

- Decoder

- Encoder

- Flip-Flop

- <u>JTAG</u>

- Latch

- Logic Primitive

- <u>Memory</u>

- <u>Multiplexer</u>

- Numeric Connector

- Shift Register

- <u>Shifter</u>

- Wired Function

## **Arithmetic Function**

Various types of Arithmetic function are available as follows:

- ACC1

1-Bit Loadable Cascadable Accumulator with Synchronous Reset

- <u>ACC2B</u> 2-Bit Loadable Cascadable Accumulator with Synchronous Reset, Bus Version

- <u>ACC2S</u> 2-Bit Loadable Cascadable Accumulator with Synchronous Reset, Single Pin Version

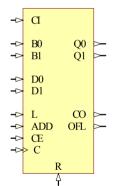

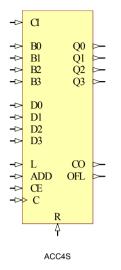

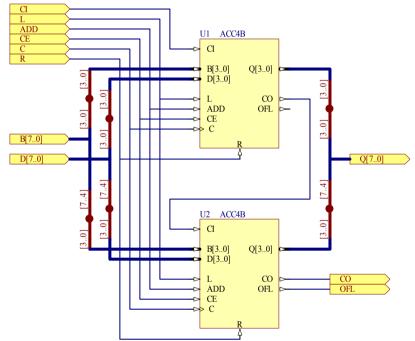

- ACC4B

4-Bit Loadable Cascadable Accumulator with Synchronous Reset, Bus

Version

- ACC4S

4-Bit Loadable Cascadable Accumulator with Synchronous Reset, Single

Pin Version

- ACC8B 8-Bit Loadable Cascadable Accumulator with Synchronous Reset, Bus Version

- ACC16B 16-Bit Loadable Cascadable Accumulator with Synchronous Reset, Bus Version

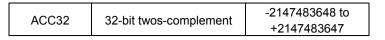

- ACC32B 32-Bit Loadable Cascadable Accumulator with Synchronous Reset, Bus Version

- ADD1 1-Bit Cascadable Full Adder

- ADD2B 2-Bit Cascadable Full Adder with Signed and Unsigned Operations, Bus Version

- ADD2S 2-Bit Cascadable Full Adder with Signed and Unsigned Operations, Single Pin Version

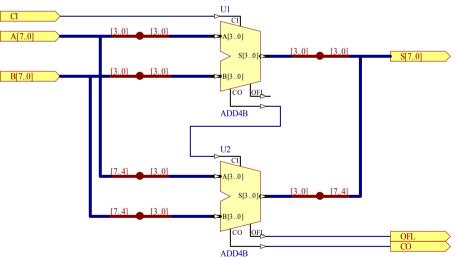

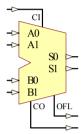

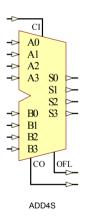

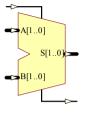

- ADD4B

4-Bit Cascadable Full Adder with Signed and Unsigned Operations, Bus

Version

- ADD4S 4-Bit Cascadable Full Adder with Signed and Unsigned Operations, Single Pin Version

- ADD8B 8-Bit Cascadable Full Adder with Signed and Unsigned Operations, Bus Version

- ADD16B 16-Bit Cascadable Full Adder with Signed and Unsigned Operations, Bus Version

- ADD32B 32-Bit Cascadable Full Adder with Signed and Unsigned Operations, Bus Version

- <u>ADDF2B</u> 2-Bit Cascadable Unsigned Binary Full Adder, Bus Version

- ADDF2S 2-Bit Cascadable Unsigned Binary Full Adder, Single Pin Version

- ADDF4B

4-Bit Cascadable Unsigned Binary Full Adder, Bus Version

- ADDF4S

4-Bit Cascadable Unsigned Binary Full Adder, Single Pin Version

- <u>ADDF8B</u> 8-Bit Cascadable Unsigned Binary Full Adder, Bus Version

- ADDF16B 16-Bit Cascadable Unsigned Binary Full Adder, Bus Version

- <u>ADDF32B</u> 32-Bit Cascadable Unsigned Binary Full Adder, Bus Version

- <u>ADDFR2B</u> 2-Bit Cascadable Unsigned Binary Registered Full Adder, Bus Version

- ADDFR2S 2-Bit Cascadable Unsigned Binary Registered Full Adder, Single Pin Version

- <u>ADDFR4B</u> 4-Bit Cascadable Unsigned Binary Registered Full Adder, Bus Version

- ADDFR4S

4-Bit Cascadable Unsigned Binary Registered Full Adder, Single Pin Version

- <u>ADDFR8B</u> 8-Bit Cascadable Unsigned Binary Registered Full Adder, Bus Version

- ADDFR16B 16-Bit Cascadable Unsigned Binary Registered Full Adder, Bus Version

- ADDFR32B 32-Bit Cascadable Unsigned Binary Registered Full Adder, Bus Version

- ADDR1 1-Bit Cascadable Registered Full Adder

- ADDR2B 2-Bit Cascadable Registered Full Adder with Signed and Unsigned Operations, Bus Version

- ADDR2S 2-Bit Cascadable Registered Full Adder with Signed and Unsigned Operations, Single Pin Version

- ADDR4B

4-Bit Cascadable Registered Full Adder with Signed and Unsigned

Operations, Bus Version

- ADDR4S

4-Bit Cascadable Registered Full Adder with Signed and Unsigned

Operations, Single Pin Version

- ADDR8B 8-Bit Cascadable Registered Full Adder with Signed and Unsigned

Operations, Bus Version

- ADDR16B 16-Bit Cascadable Registered Full Adder with Signed and Unsigned

Operations, Bus Version

- ADDR32B 32-Bit Cascadable Registered Full Adder with Signed and Unsigned

Operations, Bus Version

- ADSU1

1-Bit Cascadable Full Adder/Subtracter

- ADSU2B 2-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Bus Version

- ADSU2S 2-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Single Pin Version

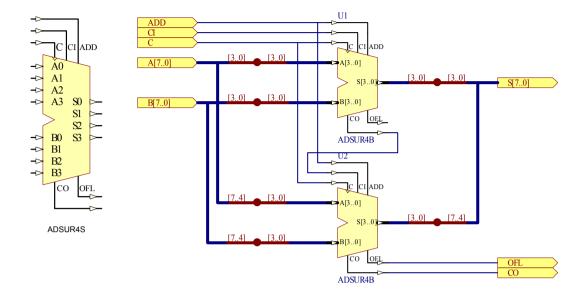

- ADSU4B

4-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Bus Version

- ADSU4S

4-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Single Pin Version

- ADSU8B 8-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Bus Version

- ADSU16B 16-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Bus Version

- ADSU32B 32-Bit Cascadable Full Adder/Subtracter with Signed and Unsigned

Operations, Bus Version

- ADSUR1 1-Bit Cascadable Registered Full Adder/Subtracter

- ADSUR2B 2-Bit Cascadable Registered Full Adder/Subtracter with Signed and Unsigned Operations, Bus Version

- ADSUR2S 2-Bit Cascadable Registered Full Adder/Subtracter with Signed and Unsigned Operations, Single Pin Version

- ADSUR4B

4-Bit Cascadable Registered Full Adder/Subtracter with Signed and

Unsigned Operations, Bus Version

- ADSUR4S

4-Bit Cascadable Registered Full Adder/Subtracter with Signed and

Unsigned Operations, Single Pin Version

- ADSUR8B 8-Bit Cascadable Registered Full Adder/Subtracter with Signed and Unsigned Operations, Bus Version

- ADSUR16B 16-Bit Cascadable Registered Full Adder/Subtracter with Signed and Unsigned Operations, Bus Version

- ADSUR32B 32-Bit Cascadable Registered Full Adder/Subtracter with Signed and Unsigned Operations, Bus Version

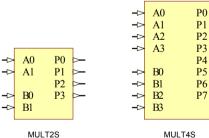

- <u>MULT2B</u> 2x2 Signed Multiplier, Bus Version

- <u>MULT2S</u> 2x2 Signed Multiplier, Single Pin Version

- <u>MULT4B</u> 4x4 Signed Multiplier, Bus Version

- <u>MULT4S</u>

4x4 Signed Multiplier, Single Pin Version

- <u>MULT8B</u> 8x8 Signed Multiplier, Bus Version

- <u>MULT16B</u> 16x16 Signed Multiplier, Bus Version

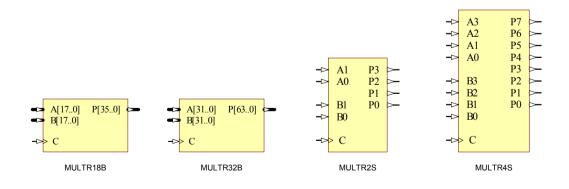

- <u>MULT18B</u> 18x18 Signed Multiplier, Bus Version

- <u>MULT32B</u> 32x32 Signed Multiplier, Bus Version

- MULTR2B 2x2 Signed Registered Multiplier, Bus Version

- <u>MULTR2S</u> 2x2 Signed Registered Multiplier, Single Pin Version

- MULTR4B 4x4 Signed Registered Multiplier, Bus Version

- <u>MULTR4S</u> 4x4 Signed Registered Multiplier, Single Pin Version

- <u>MULTR8B</u> 8x8 Signed Registered Multiplier, Bus Version

- <u>MULTR16B</u> 16x16 Signed Registered Multiplier, Bus Version

- MULTR18B 18x18 Signed Registered Multiplier, Bus Version

- <u>MULTR32B</u> 32x32 Signed Registered Multiplier, Bus Version

- <u>MULTU2B</u> 2x2 Unsigned Multiplier, Bus Version

- <u>MULTU2S</u> 2x2 Unsigned Multiplier, Single Pin Version

- <u>MULTU4B</u> 4x4 Unsigned Multiplier, Bus Version

- <u>MULTU4S</u> 4x4 Unsigned Multiplier, Single Pin Version

- MULTU8B 8x8 Unsigned Multiplier, Bus Version

.

- <u>MULTU16B</u> 16x16 Unsigned Multiplier, Bus Version

- <u>MULTU18B</u> 18x18 Unsigned Multiplier, Bus Version

- <u>MULTU32B</u> 32x32 Unsigned Multiplier, Bus Version

- <u>MULTUR2B</u> 2x2 Unsigned Registered Multiplier, Bus Version

- <u>MULTUR2S</u> 2x2 Unsigned Registered Multiplier, Single Pin Version

- <u>MULTUR4B</u> 4x4 Unsigned Registered Multiplier, Bus Version

- <u>MULTUR4S</u> 4x4 Unsigned Registered Multiplier, Single Pin Version

- MULTUR8B 8x8 Unsigned Registered Multiplier, Bus Version

- <u>MULTUR16B</u> 16x16 Unsigned Registered Multiplier, Bus Version

- MULTUR18B 18x18 Unsigned Registered Multiplier, Bus Version

- <u>MULTUR32B</u> 32x32 Unsigned Registered Multiplier, Bus Version

- PAR9B 9-Bit Odd/Even Parity Generators/Checker, Bus Version

- PAR9S 9-Bit Odd/Even Parity Generators/Checker, Single Pin Version

### **Buffer**

Multiple input and tri-state buffers are available as follows:

BUF 1-bit General Purpose (Non-inverting) Buffer • BUF2B 2-Bit General Purpose (Non-inverting) Buffer, Bus Version BUF2S 2-Bit General Purpose (Non-inverting) Buffer, Single Pin Version BUF3B 3-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF3S 3-Bit General Purpose (Non-inverting) Buffer, Single Pin Version BUF4B 4-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF4S 4-Bit General Purpose (Non-inverting) Buffer, Single Pin Version • BUF5B 5-Bit General Purpose (Non-inverting) Buffer, Bus Version • 5-Bit General Purpose (Non-inverting) Buffer, Single Pin Version BUF5S • BUF6B 6-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF6S 6-Bit General Purpose (Non-inverting) Buffer, Single Pin Version BUF7B 7-Bit General Purpose (Non-inverting) Buffer, Bus Version BUF7S 7-Bit General Purpose (Non-inverting) Buffer, Single Pin Version BUF8B 8-Bit General Purpose (Non-inverting) Buffer, Bus Version BUF8S 8-Bit General Purpose (Non-inverting) Buffer, Single Pin Version BUF9B 9-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF9S 9-Bit General Purpose (Non-inverting) Buffer, Single Pin Version • BUF10B 10-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF10S 10-Bit General Purpose (Non-inverting) Buffer, Single Pin Version • BUF12B 12-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF12S 12-Bit General Purpose (Non-inverting) Buffer, Single Pin Version • BUF16B 16-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF16S 16-Bit General Purpose (Non-inverting) Buffer, Single Pin Version • BUF32B 32-Bit General Purpose (Non-inverting) Buffer, Bus Version • BUF32S 32-Bit General Purpose (Non-inverting) Buffer, Single Pin Version • BUFE 1-bit 3-state Buffer with Active High Enable . BUFE2B 2-Bit 3-state Buffer with Active High Enable, Bus Version • BUFE2S 2-Bit 3-state Buffer with Active High Enable, Single Pin Version • BUFE3B 3-Bit 3-state Buffer with Active High Enable, Bus Version • BUFE3S 3-Bit 3-state Buffer with Active High Enable, Single Pin Version . 4-Bit 3-state Buffer with Active High Enable, Bus Version BUFE4B . BUFE4S 4-Bit 3-state Buffer with Active High Enable, Single Pin Version BUFE5B 5-Bit 3-state Buffer with Active High Enable, Bus Version

| • | BUFE5S         | 5-Bit 3-state Buffer with Active High Enable, Single Pin Version  |

|---|----------------|-------------------------------------------------------------------|

| ٠ | BUFE6B         | 6-Bit 3-state Buffer with Active High Enable, Bus Version         |

| • | BUFE6S         | 6-Bit 3-state Buffer with Active High Enable, Single Pin Version  |

| • | BUFE7B         | 7-Bit 3-state Buffer with Active High Enable, Bus Version         |

| • | BUFE7S         | 7-Bit 3-state Buffer with Active High Enable, Single Pin Version  |

| ٠ | BUFE8B         | 8-Bit 3-state Buffer with Active High Enable, Bus Version         |

| ٠ | BUFE8S         | 8-Bit 3-state Buffer with Active High Enable, Single Pin Version  |

| • | BUFE9B         | 9-Bit 3-state Buffer with Active High Enable, Bus Version         |

| • | BUFE9S         | 9-Bit 3-state Buffer with Active High Enable, Single Pin Version  |

| ٠ | BUFE10B        | 10-Bit 3-state Buffer with Active High Enable, Bus Version        |

| ٠ | BUFE10S        | 10-Bit 3-state Buffer with Active High Enable, Single Pin Version |

| • | BUFE12B        | 12-Bit 3-state Buffer with Active High Enable, Bus Version        |

| • | BUFE12S        | 12-Bit 3-state Buffer with Active High Enable, Single Pin Version |

| • | <u>BUFE16B</u> | 16-Bit 3-state Buffer with Active High Enable, Bus Version        |

| • | BUFE16S        | 16-Bit 3-state Buffer with Active High Enable, Single Pin Version |

| • | BUFE32B        | 32-Bit 3-state Buffer with Active High Enable, Bus Version        |

| • | BUFE32S        | 32-Bit 3-state Buffer with Active High Enable, Single Pin Version |

| • | <u>BUFT</u>    | 1-Bit 3-state Buffer with Active Low Enable                       |

| • | BUFT2B         | 2-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT2S         | 2-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | BUFT3B         | 3-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT3S         | 3-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | <u>BUFT4B</u>  | 4-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT4S         | 4-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | <u>BUFT5B</u>  | 5-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT5S         | 5-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | BUFT6B         | 6-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT6S         | 6-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | BUFT7B         | 7-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT7S         | 7-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | BUFT8B         | 8-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT8S         | 8-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | BUFT9B         | 9-Bit 3-state Buffer with Active Low Enable, Bus Version          |

| • | BUFT9S         | 9-Bit 3-state Buffer with Active Low Enable, Single Pin Version   |

| • | BUFT10B        | 10-Bit 3-state Buffer with Active Low Enable, Bus Version         |

| • | BUFT10S        | 10-Bit 3-state Buffer with Active Low Enable, Single Pin Version  |

|   |                |                                                                   |

- BUFT12B 12-Bit 3-state Buffer with Active Low Enable, Bus Version

- BUFT12S

12-Bit 3-state Buffer with Active Low Enable, Single Pin Version

- <u>BUFT16B</u> 16-Bit 3-state Buffer with Active Low Enable, Bus Version

- <u>BUFT16S</u> 16-Bit 3-state Buffer with Active Low Enable, Single Pin Version

- <u>BUFT32B</u> 32-Bit 3-state Buffer with Active Low Enable, Bus Version

- BUFT32S 32-Bit 3-state Buffer with Active Low Enable, Single Pin Version

- IOBUF Input/Output Buffer

- IOBUF2B 2-Bit Input/Output Buffer, Bus Version

- IOBUF2S 2-Bit Input/Output Buffer, Single Pin Version

- IOBUF3B 3-Bit Input/Output Buffer, Bus Version

- IOBUF4B 4-Bit Input/Output Buffer, Bus Version

- IOBUF4S

4-Bit Input/Output Buffer, Single Pin Version

- IOBUF5B 5-Bit Input/Output Buffer, Bus Version

- IOBUF6B 6-Bit Input/Output Buffer, Bus Version

- IOBUF7B 7-Bit Input/Output Buffer, Bus Version

- IOBUF8B 8-Bit Input/Output Buffer, Bus Version

- <u>IOBUF9B</u> 9-Bit Input/Output Buffer, Bus Version

- <u>IOBUF10B</u> 10-Bit Input/Output Buffer, Bus Version

- IOBUF12B 12-Bit Input/Output Buffer, Bus Version

- <u>IOBUF16B</u> 16-Bit Input/Output Buffer, Bus Version

- IOBUF32B 32-Bit Input/Output Buffer, Bus Version

- IOBUFC2B 2-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC2S 2-Bit Input/Output Buffer With Separated Control, Single Pin Version

- <u>IOBUFC3B</u> 3-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC4B 4-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC4S 4-Bit Input/Output Buffer With Separated Control, Single Pin Version

- IOBUFC5B 5-Bit Input/Output Buffer With Separated Control, Bus Version

- <u>IOBUFC6B</u> 6-Bit Input/Output Buffer With Separated Control, Bus Version

- <u>IOBUFC7B</u> 7-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC8B 8-Bit Input/Output Buffer With Separated Control, Bus Version

- <u>IOBUFC9B</u> 9-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC10B 10-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC12B 12-Bit Input/Output Buffer With Separated Control, Bus Version

- IOBUFC16B 16-Bit Input/Output Buffer With Separated Control, Bus Version

- <u>IOBUFC32B</u> 32-Bit Input/Output Buffer With Separated Control, Bus Version

•

•

•

•

•

.

.

.

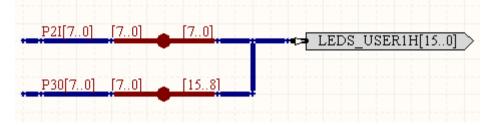

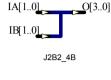

## **Bus Joiner**

Bus joiners are components that allow splitting or merging of buss slices to suite your needs. Various types are available as follows:

- J2B2 4B 2 x 2-Bit input bus to 1 x 4-bit output bus J3B 3S 3-Bit input bus to 3 Single pin outputs J3S 3B 3 Single pin inputs to single 3-Bit output bus • J3S 3BX 3 Single pin IO to single 3-Bit IO bus J4B2 8B 2 x 4-Bit input bus to 1 x 8-bit output bus • J4B4 16B 4 x 4-Bit input bus to 1 x 16-bit output bus • J4B8 32B 8 x 4-Bit input bus to 1 x 32-bit output bus . J4B 2B2 1 x 4-bit input bus to 2 x 2-Bit output bus • J4B 2B2X 1 x 4-bit IO bus to 2 x 2-Bit IO bus • J4B 4S 4-Bit input bus to 4 Single pin outputs • J4S 4B 4 Single pin inputs to single 4-Bit output bus . J4S 4BX 4 Single pin IO to single 4-Bit IO bus . J5B 5S 5-Bit input bus to 5 Single pin outputs • J5S 5B 5 Single pin inputs to single 5-Bit output bus . J5S 5BX 5 Single pin IO to single 5-Bit IO bus . J6B 6S 6-Bit input bus to 6 Single pin outputs • J6S 6B 6 Single pin inputs to single 6-Bit output bus • J6S 6BX 6 Single pin IO to single 6-Bit IO bus . J7B 7S 7-Bit input bus to 7 Single pin outputs . <u>J7S 7B</u> 7 Single pin inputs to single 7-Bit output bus . J7S 7BX 7 Single pin IO to single 7-Bit IO bus . J8B2 16B 2 x 8-Bit input bus to 1 x 16-bit output bus . J8B4 32B 4 x 8-Bit input bus to 1 x 32-bit output bus . J8B 4B2 1 x 8-bit input bus to 2 x 4-Bit output bus • J8B 4B2X 1 x 8-bit IO bus to 2 x 4-Bit IO bus . J8B 8S • 8-Bit input bus to 8 single pin outputs J8S 8B • 8 Single pin inputs to single 8-Bit output bus 8 Single pin IO to single 8-Bit IO bus <u>J8S 8BX</u> • **J9B 9S** 9-Bit input bus to 9 Single pin outputs J9S 9B 9 Single pin inputs to single 9-Bit output bus • J9S 9BX 9 Single pin IO to single 9-Bit IO bus

- <u>J10B\_10S</u> 10-Bit input bus to 10 Single pin outputs

- <u>J10S\_10B</u> 10 Single pin inputs to single 10-Bit output bus

- <u>J10S\_10BX</u> 10 Single pin IO to single 10-Bit IO bus

- <u>J12B\_12S</u> 12-Bit input bus to 12 single pin outputs

- <u>J12S\_12B</u>

12 Single pin inputs to single 12-Bit output bus

- <u>J12S\_12BX</u> 12 single-Bit IO to single 12-Bit IO bus

- <u>J16B2\_32B</u> 2 x 16-Bit input bus to 1 x 32-bit output bus

- <u>J16B\_4B4</u> 1 x 16-bit input bus to 4 x 4-Bit output bus

- <u>J16B\_4B4X</u> 1 x 16-bit IO bus to 4 x 4-Bit IO bus

- <u>J16B\_8B2</u> 1 x 16-bit input bus to 2 x 8-Bit output bus

- J16B\_8B2X 1 x 16-bit IO bus to 2 x 8-Bit IO bus

- <u>J16B\_16S</u> Single 16-Bit input bus to 16 single pin outputs

- <u>J16S 16B</u> 16 Single pin inputs to single 16-Bit output bus

- <u>J16S\_16BX</u>

16 Single pin IO to single 16-Bit IO bus

- J32B\_4B8 1 x 32-Bit input bus to 8 x 4-Bit output bus

- <u>J32B\_4B8X</u> 1 x 32-Bit IO bus to 8 x 4-Bit IO bus

- <u>J32B\_8B4</u> 1 x 32-Bit input bus to 4 x 8-Bit output bus

- <u>J32B\_8B4X</u> 1 x 32-Bit IO bus to 4 x 8-Bit IO bus

- <u>J32B\_16B2</u> 1 x 32-bit input bus to 2 x 16-Bit output bus

- <u>J32B\_16B2X</u> 1 x 32-bit IO bus to 2 x 16-Bit IO bus

- <u>JB</u>

٠

System BUS Joiner

## **Clock Divider**

General and programmable clock dividers are available as follows:

| • | CDIV2          | Clock Divider by 2                              |

|---|----------------|-------------------------------------------------|

| • | CDIV2DC50      | Clock Divider by 2 with 50% Duty Cycle Output   |

| • | CDIV3          | Clock Divider by 3                              |

| • | CDIV4          | Clock Divider by 4                              |

| • | CDIV4DC50      | Clock Divider by 4 with 50% Duty Cycle Output   |

| • | CDIV5          | Clock Divider by 5                              |

| • | CDIV6          | Clock Divider by 6                              |

| • | CDIV6DC50      | Clock Divider by 6 with 50% Duty Cycle Output   |

| • | CDIV7          | Clock Divider by 7                              |

| • | CDIV8          | Clock Divider by 8                              |

| • | CDIV8DC50      | Clock Divider by 8 with 50% Duty Cycle Output   |

| • | CDIV9          | Clock Divider by 9                              |

| • | <u>CDIV10</u>  | Clock Divider by 10                             |

| • | CDIV10DC50     | Clock Divider by 10 with 50% Duty Cycle Output  |

| • | <u>CDIV12</u>  | Clock Divider by 12                             |

| • | CDIV12DC50     | Clock Divider by 12 with 50% Duty Cycle Output  |

| • | CDIV16         | Clock Divider by 16                             |

| • | CDIV16DC50     | Clock Divider by 16 with 50% Duty Cycle Output  |

| • | CDIV20         | Clock Divider by 20                             |

| • | CDIV20DC50     | Clock Divider by 20 with 50% Duty Cycle Output  |

| • | CDIV24         | Clock Divider by 24                             |

| • | CDIV24DC50     | Clock Divider by 24 with 50% Duty Cycle Output  |

| • | CDIV32         | Clock Divider by 32                             |

| • | CDIV32DC50     | Clock Divider by 32 with 50% Duty Cycle Output  |

| • | CDIV64         | Clock Divider by 64                             |

| • | CDIV64DC50     | Clock Divider by 64 with 50% Duty Cycle Output  |

| • | <u>CDIV128</u> | Clock Divider by 128                            |

| • | CDIV128DC50    | Clock Divider by 128 with 50% Duty Cycle Output |

| • | <u>CDIV256</u> | Clock Divider by 256                            |

| • | CDIV256DC50    | Clock Divider by 256 with 50% Duty Cycle Output |

| • | CDIVN_8        | 8-Bit Programmable Clock Divider                |

| • | CDIVN_16       | 16-Bit Programmable Clock Divider               |

| • | CDIVN_32       | 32-Bit Programmable Clock Divider               |

## **Clock Manager**

Various clock manager components are available as follows:

- <u>CLKMAN\_1</u> Single Operational Output Clock Manager

- <u>CLKMAN\_2</u> Dual Operational Output Clock Manager

- <u>CLKMAN\_3</u> Multiple Operational Output Clock Manager

- <u>CLKMAN\_4</u> Multiple Operational Output Clock Manager

## Comparator

.

Magnitude, identity and address comparators are available as follows:

2-Bit Identity Comparator, Bus Version COMP2B COMP2S 2-Bit Identity Comparator, Single Pin Version COMP3B 3-Bit Identity Comparator, Bus Version COMP3S 3-Bit Identity Comparator, Single Pin Version COMP4B 4-Bit Identity Comparator, Bus Version • COMP4S 4-Bit Identity Comparator, Single Pin Version • COMP5B 5-Bit Identity Comparator, Bus Version • COMP5S 5-Bit Identity Comparator, Single Pin Version • COMP6B 6-Bit Identity Comparator, Bus Version • COMP6S 6-Bit Identity Comparator, Single Pin Version COMP7B 7-Bit Identity Comparator, Bus Version COMP7S 7-Bit Identity Comparator, Single Pin Version COMP8B 8-Bit Identity Comparator, Bus Version • COMP8S 8-Bit Identity Comparator, Single Pin Version COMP9B 9-Bit Identity Comparator, Bus Version COMP9S 9-Bit Identity Comparator, Single Pin Version COMP10B 10-Bit Identity Comparator, Bus Version • COMP10S 10-Bit Identity Comparator, Single Pin Version • COMP12B 12-Bit Identity Comparator, Bus Version • COMP12S 12-Bit Identity Comparator, Single Pin Version . COMP16B 16-Bit Identity Comparator, Bus Version . COMP16S 16-Bit Identity Comparator, Single Pin Version • COMP32B 32-Bit Identity Comparator, Bus Version • 2-Bit Magnitude Comparator, Bus Version COMPM2B . COMPM2S 2-Bit Magnitude Comparator, Single Pin Version . COMPM3B 3-Bit Magnitude Comparator, Bus Version . COMPM3S 3-Bit Magnitude Comparator, Single Pin Version . COMPM4B 4-Bit Magnitude Comparator, Bus Version . COMPM4S 4-Bit Magnitude Comparator, Single Pin Version . COMPM5B 5-Bit Magnitude Comparator, Bus Version . COMPM5S 5-Bit Magnitude Comparator, Single Pin Version . 6-Bit Magnitude Comparator, Bus Version COMPM6B . COMPM6S 6-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM7B</u> 7-Bit Magnitude Comparator, Bus Version

- <u>COMPM7S</u> 7-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM8B</u> 8-Bit Magnitude Comparator, Bus Version

- <u>COMPM8S</u> 8-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM9B</u> 9-Bit Magnitude Comparator, Bus Version

- <u>COMPM9S</u> 9-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM10B</u> 10-Bit Magnitude Comparator, Bus Version

- <u>COMPM10S</u> 10-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM12B</u> 12-Bit Magnitude Comparator, Bus Version

- <u>COMPM12S</u> 12-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM16B</u>

16-Bit Magnitude Comparator, Bus Version

- <u>COMPM16S</u>

16-Bit Magnitude Comparator, Single Pin Version

- <u>COMPM32B</u> 32-Bit Magnitude Comparator, Bus Version

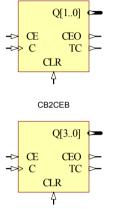

## Counter

Various function and types of counter are available as follows:

- <u>CB2CEB</u>

2-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB2CES</u>

2-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB2CLEB</u> 2-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB2CLEDB</u> 2-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB2CLEDS</u> 2-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB2CLES</u> 2-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB2REB</u> 2-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB2RES</u>

2-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB2RLEB</u> 2-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB2RLES</u> 2-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB4CEB</u>

4-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB4CES</u>

4-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB4CLEB</u>

4-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB4CLEDB</u>

4-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB4CLEDS</u>

4-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB4CLES</u>

4-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB4REB</u>

4-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB4RES</u>

4-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB4RLEB</u>

4-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB4RLES</u>

4-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB8CEB</u>

8-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB8CES</u>

8-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB8CLEB</u> 8-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB8CLEDB</u>

8-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB8CLEDS</u>

8-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB8CLES</u>

8-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB8REB</u>

8-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB8RES</u>

8-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB8RLEB</u> 8-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB8RLES</u>

8-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB16CEB</u>

16-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB16CES</u>

16-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB16CLEB</u>

16-Bit Loadable Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB16CLEDB</u>

16-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB16CLEDS</u>

16-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB16CLES</u>

16-Bit Loadable Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CB16REB</u>

16-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB16RES</u>

16-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB16RLEB</u>

16-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB16RLES</u>

16-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CB32CEB</u> 32-Bit Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB32CLEB</u> 32-Bit Loadable Cascadable Binary Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB32CLEDB</u> 32-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CB32REB</u> 32-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CB32RLEB</u> 32-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CD4CEB</u>

Cascadable BCD Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CD4CES</u>

Cascadable BCD Counter with Clock Enable and Asynchronous Clear, Single Pin Version

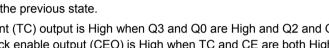

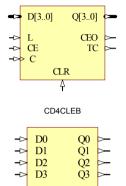

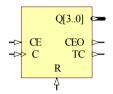

- <u>CD4CLEB</u>

Loadable Cascadable BCD Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CD4CLES</u>

Loadable Cascadable BCD Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CD4REB</u>

Cascadable BCD Counter with Clock Enable and Synchronous Reset, Bus

Version

- <u>CD4RES</u>

Cascadable BCD Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CD4RLEB</u>

Loadable Cascadable BCD Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CD4RLES</u>

Loadable Cascadable BCD Counter with Clock Enable and Synchronous Reset, Single Pin Version

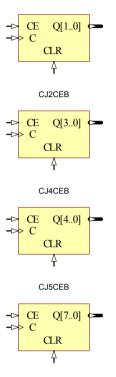

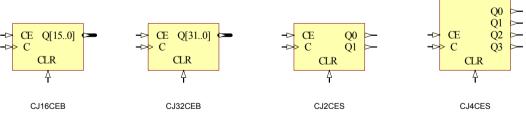

- <u>CJ2CEB</u> 2-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CJ2CES</u> 2-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CJ2REB</u> 2-Bit Johnson Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CJ2RES</u> 2-Bit Johnson Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CJ4CEB</u>

4-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CJ4CES</u>

4-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CJ4REB</u>

4-Bit Johnson Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CJ4RES</u>

4-Bit Johnson Counter with Clock Enable and Synchronous Reset, Single Pin Version

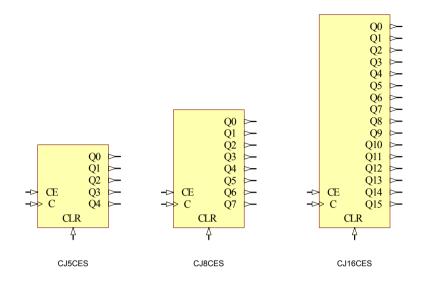

- <u>CJ5CEB</u>

5-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CJ5CES</u> 5-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CJ5REB</u> 5-Bit Johnson Counters with Clock Enable and Synchronous Reset, Bus Version

- <u>CJ5RES</u> 5-Bit Johnson Counters with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CJ8CEB</u>

8-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CJ8CES</u>

8-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CJ8REB</u> 8-Bit Johnson Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CJ8RES</u> 8-Bit Johnson Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CJ16CEB</u>

16-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CJ16CES</u>

16-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CJ16REB</u>

16-Bit Johnson Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CJ16RES</u>

16-Bit Johnson Counter with Clock Enable and Synchronous Reset, Single Pin Version

- <u>CJ32CEB</u> 32-Bit Johnson Counter with Clock Enable and Asynchronous Clear, Bus Version

- <u>CJ32REB</u> 32-Bit Johnson Counter with Clock Enable and Synchronous Reset, Bus Version

- <u>CR2CEB</u> 2-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CR2CES</u>

2-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CR4CEB</u>

4-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CR4CES</u>

4-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CR8CEB</u>

8-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CR8CES</u>

8-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CR16CEB</u>

16-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Bus Version

- <u>CR16CES</u>

16-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>CR32CEB</u> 32-Bit Negative-Edge Binary Ripple Counters with Clock Enable and Asynchronous Clear, Bus Version

# Decoder

Various type of decoders are available as follows:

- D2\_4B Binary 2- to 4-Bit Decoder, Bus Version

- D2\_4EB Binary 2- to 4-Bit Decoder with Enable, Bus Version

- D2\_4ES Binary 2- to 4-Bit Decoder with Enable, Single Pin Version

- D2\_4S Binary 2- to 4-Bit Decoder, Single Pin Version

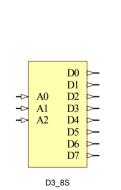

- D3\_8B Binary 3- to 8-Bit Decoder, Bus Version

- D3\_8EB Binary 3- to 8-Bit Decoder with Enable, Bus Version

- D3\_8ES

Binary 3- to 8-Bit Decoder with Enable, Single Pin Version

- D3\_8S Binary 3- to 8-Bit Decoder, Single Pin Version

- D4\_10B Binary-Coded-Decimal (BCD) Decoder, Bus Version

- D4\_10EB Binary-Coded-Decimal (BCD) Decoder with Enable, Bus Version

- <u>D4 10ES</u> Binary-Coded-Decimal (BCD) Decoder with Enable, Single Pin Version

- D4\_10S

Binary-Coded-Decimal (BCD) Decoder, Single Pin Version

- D4\_16B Binary 4- to 16-Bit Decoder, Bus Version

- <u>D4\_16EB</u> Binary 4- to 16-Bit Decoder with Enable, Bus Version

- <u>D4\_16ES</u> Binary 4- to 16-Bit Decoder with Enable, Single Pin Version

- D4\_16S Binary 4- to 16-Bit Decoder, Single Pin Version

- D5\_32B Binary 5- to 32-Bit Decoder, Bus Version

- D5\_32EB Binary 5- to 32-Bit Decoder with Enable, Bus Version

- D7SEGB 7-Segment-Display Decoder for Common-Cathode LED (Active High Output), Bus Version

- D7SEGNB 7-Segment-Display Decoder for Common-Anode LED (Active Low Output), Bus Version

- D7SEGNS

7-Segment-Display Decoder for Common-Anode LED (Active Low Output), Single Pin Version

- D7SEGS

7-Segment-Display Decoder for Common-Cathode LED (Active High Output), Single Pin Version

# Encoder

Various type of encoders are available as follows:

- <u>E4\_2B</u> 4- to 2-Bit Priority Encoder, Bus Version

- <u>E4\_2EB</u> 4- to 2-Bit Priority Encoder with Enable, Bus Version

- <u>E4\_2ES</u> 4- to 2-Bit Priority Encoder with Enable, Single Pin Version

- <u>E4\_2S</u>

4- to 2-Bit Priority Encoder, Single Pin Version

- E8\_3B

8- to 3-Bit Priority Encoder, Bus Version

- E8\_3EB 8- to 3-Bit Priority Encoder with Enable, Bus Version

- <u>E8\_3ES</u> 8- to 3-Bit Priority Encoder with Enable, Single Pin Version

- E8\_3S

8- to 3-Bit Priority Encoder, Single Pin Version

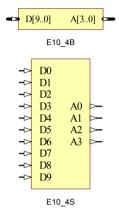

- <u>E10\_4B</u> Binary-Coded-Decimal (BCD) Encoder, Bus Version

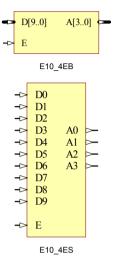

- <u>E10\_4EB</u> Binary-Coded-Decimal (BCD) Encoder with Enable, Bus Version

- <u>E10\_4ES</u> Binary-Coded-Decimal (BCD) Encoder with Enable, Single Pin Version

- <u>E10\_4S</u> Binary-Coded-Decimal (BCD) Encoder, Single Pin Version

- <u>E16\_4B</u> 16- to 4-Bit Priority Encoder, Bus Version

- <u>E16\_4EB</u> 16- to 4-Bit Priority Encoder with Enable, Bus Version

- <u>E16\_4ES</u> 16- to 4-Bit Priority Encoder with Enable, Single Pin Version

- E16\_4S

16- to 4-Bit Priority Encoder, Single Pin Version

- <u>E32\_5B</u> 32- to 5-Bit Priority Encoder, Bus Version

- E32\_5EB 32- to 5-Bit Priority Encoder with Enable, Bus Version

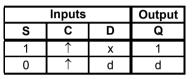

# Flip-Flop

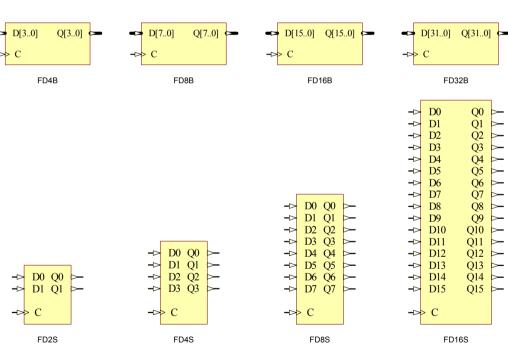

General and multi function flip-flops are available as follows:

- FD D-Type Flip-Flop

- ED2B

2-Bit D-Type Flip-Flop, Bus Version

- <u>FD2CB</u> 2-Bit D-Type Flip-Flop with Asynchronous Clear, Bus Version

- ED2CEB 2-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Bus Version

- ED2CES 2-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>FD2CPB</u> 2-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Bus Version

- ED2CPEB 2-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear. Bus Version

- ED2CPES 2-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Single Pin Version

- ED2CPS 2-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Single Pin Version

- ED2CS 2-Bit D-Type Flip-Flop with Asynchronous Clear, Single Pin Version

- ED2EB 2-Bit D Flip-Flop with Clock Enable, Bus Version

- <u>FD2ES</u> 2-Bit D Flip-Flop with Clock Enable, Single Pin Version

- FD2PB 2-Bit D-Type Flip-Flop with Asynchronous Preset, Bus Version

- ED2PEB 2-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Bus Version

- ED2PES 2-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Single Pin Version

- ED2PS 2-Bit D-Type Flip-Flop with Asynchronous Preset, Single Pin Version

- ED2RB 2-Bit D-Type Flip-Flop with Synchronous Reset, Bus Version

- ED2REB 2-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Bus Version

- ED2RES 2-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Single Pin Version

- ED2RS 2-Bit D-Type Flip-Flop with Synchronous Reset, Single Pin Version

- FD2RSB 2-Bit D-Type Flip-Flop with Synchronous Reset and Set, Bus Version

- ED2RSEB 2-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Bus Version

- ED2RSES 2-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Single Pin Version

- <u>FD2RSS</u> 2-Bit D-Type Flip-Flop with Synchronous Reset and Set, Single Pin Version

- <u>FD2S</u> 2-Bit D-Type Flip-Flop, Single Pin Version

- <u>FD2SB</u> 2-Bit D-Type Flip-Flop with Synchronous Set, Bus Version

- ED2SEB 2-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Bus Version

- ED2SES 2-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Single Pin Version

- <u>FD2SRB</u> 2-Bit D-Type Flip-Flop with Synchronous Set and Reset, Bus Version

- ED2SREB 2-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Bus Version

- ED2SRES 2-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Single Pin Version

- <u>FD2SRS</u> 2-Bit D-Type Flip-Flop with Synchronous Set and Reset, Single Pin Version

- ED2SS 2-Bit D-Type Flip-Flop with Synchronous Set, Single Pin Version

- <u>FD4B</u> 4-Bit D-Type Flip-Flop, Bus Version

- <u>FD4CB</u> 4-Bit D-Type Flip-Flop with Asynchronous Clear, Bus Version

- FD4CEB

4-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Bus

Version

- FD4CES

4-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>FD4CPB</u> 4-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Bus Version

- ED4CPEB 4-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Bus Version

- ED4CPES 4-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Single Pin Version

- FD4CPS

4-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Single Pin

Version

- <u>FD4CS</u> 4-Bit D-Type Flip-Flop with Asynchronous Clear, Single Pin Version

- <u>FD4EB</u> 4-Bit D Flip-Flop with Clock Enable, Bus Version

- ED4ES 4-Bit D Flip-Flop with Clock Enable, Single Pin Version

- ED4PB

4-Bit D-Type Flip-Flop with Asynchronous Preset, Bus Version

- FD4PEB

4-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Bus

Version

- FD4PES

4-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Single

Pin Version

- <u>FD4PS</u> 4-Bit D-Type Flip-Flop with Asynchronous Preset, Single Pin Version

- <u>FD4RB</u> 4-Bit D-Type Flip-Flop with Synchronous Reset, Bus Version

- FD4REB

4-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Bus

Version

- FD4RES

4-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Single

Pin Version

- <u>FD4RS</u> 4-Bit D-Type Flip-Flop with Synchronous Reset, Single Pin Version

- <u>FD4RSB</u> 4-Bit D-Type Flip-Flop with Synchronous Reset and Set, Bus Version

- FD4RSEB

4-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Bus Version

- ED4RSES

4-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Single Pin Version

- <u>FD4RSS</u> 4-Bit D-Type Flip-Flop with Synchronous Reset and Set, Single Pin Version

- FD4S

4-Bit D-Type Flip-Flop, Single Pin Version

- <u>FD4SB</u> 4-Bit D-Type Flip-Flop with Synchronous Set, Bus Version

- FD4SEB

4-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Bus

Version

- FD4SES

4-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Single Pin Version

- <u>FD4SRB</u> 4-Bit D-Type Flip-Flop with Synchronous Set and Reset, Bus Version

- ED4SREB

4-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Bus Version

- ED4SRES

4-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Single Pin Version

- ED4SRS

4-Bit D-Type Flip-Flop with Synchronous Set and Reset, Single Pin Version

- ED4SS

4-Bit D-Type Flip-Flop with Synchronous Set, Single Pin Version

- <u>FD8B</u> 8-Bit D-Type Flip-Flop, Bus Version

- <u>FD8CB</u> 8-Bit D-Type Flip-Flop with Asynchronous Clear, Bus Version

- ED8CEB

8-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Bus Version

- FD8CES

8-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Single Pin Version

- ED8CPB

8-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Bus Version

- ED8CPEB

8-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Bus Version

- ED8CPES

8-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Single Pin Version

- ED8CPS

8-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Single Pin Version

- <u>FD8CS</u> 8-Bit D-Type Flip-Flop with Asynchronous Clear, Single Pin Version

- ED8EB

8-Bit D Flip-Flop with Clock Enable, Bus Version

- ED8ES

8-Bit D Flip-Flop with Clock Enable, Single Pin Version

- ED8PB 8-Bit D-Type Flip-Flop with Asynchronous Preset, Bus Version

- ED8PEB 8-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Bus Version

- ED8PES

8-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Single Pin Version

- <u>FD8PS</u> 8-Bit D-Type Flip-Flop with Asynchronous Preset, Single Pin Version

- ED8RB

8-Bit D-Type Flip-Flop with Synchronous Reset, Bus Version

- FD8REB 8-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Bus Version

- FD8RES

8-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Single Pin Version

- ED8RS 8-Bit D-Type Flip-Flop with Synchronous Reset, Single Pin Version

- <u>FD8RSB</u> 8-Bit D-Type Flip-Flop with Synchronous Reset and Set, Bus Version

- FD8RSEB

8-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Bus Version

- ED8RSES

8-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Single Pin Version

- <u>FD8RSS</u> 8-Bit D-Type Flip-Flop with Synchronous Reset and Set, Single Pin Version

- <u>FD8S</u> 8-Bit D-Type Flip-Flop, Single Pin Version

- <u>FD8SB</u> 8-Bit D-Type Flip-Flop with Synchronous Set, Bus Version

- ED8SEB 8-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Bus Version

- FD8SES

8-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Single Pin Version

- <u>FD8SRB</u> 8-Bit D-Type Flip-Flop with Synchronous Set and Reset, Bus Version

- FD8SREB 8-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Bus Version

- ED8SRES

8-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Single Pin Version

- ED8SRS 8-Bit D-Type Flip-Flop with Synchronous Set and Reset, Single Pin Version

- ED8SS

8-Bit D-Type Flip-Flop with Synchronous Set, Single Pin Version

- <u>FD16B</u> 16-Bit D-Type Flip-Flop, Bus Version

- <u>FD16CB</u> 16-Bit D-Type Flip-Flop with Asynchronous Clear, Bus Version

- FD16CEB 16-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Bus Version

- FD16CES

16-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Single Pin Version

- <u>FD16CPB</u> 16-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Bus Version

- <u>FD16CPEB</u> 16-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Bus Version

- FD16CPES

16-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Single Pin Version

- FD16CPS

16-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Single Pin Version

- FD16CS 16-Bit D-Type Flip-Flop with Asynchronous Clear, Single Pin Version

- ED16EB

16-Bit D Flip-Flop with Clock Enable, Bus Version

- <u>FD16ES</u> 16-Bit D Flip-Flop with Clock Enable, Single Pin Version

- <u>FD16PB</u> 16-Bit D-Type Flip-Flop with Asynchronous Preset, Bus Version

- FD16PEB 16-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Bus Version

- FD16PES

16-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Single Pin Version

- <u>FD16PS</u> 16-Bit D-Type Flip-Flop with Asynchronous Preset, Single Pin Version

- FD16RB 16-Bit D-Type Flip-Flop with Synchronous Reset, Bus Version

- FD16REB

16-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Bus Version

- FD16RES

16-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Single Pin Version

- <u>FD16RS</u> 16-Bit D-Type Flip-Flop with Synchronous Reset, Single Pin Version

- <u>FD16RSB</u> 16-Bit D-Type Flip-Flop with Synchronous Reset and Set, Bus Version

- ED16RSEB

16-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Bus Version

- ED16RSES

16-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Single Pin Version

- ED16RSS

16-Bit D-Type Flip-Flop with Synchronous Reset and Set, Single Pin Version

- FD16S

16-Bit D-Type Flip-Flop, Single Pin Version

- <u>FD16SB</u> 16-Bit D-Type Flip-Flop with Synchronous Set, Bus Version

- ED16SEB

16-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Bus

Version

- ED16SES

16-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Single Pin Version

- <u>FD16SRB</u> 16-Bit D-Type Flip-Flop with Synchronous Set and Reset, Bus Version

- ED16SREB

16-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Bus Version

- ED16SRES

16-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Single Pin Version

- ED16SRS

16-Bit D-Type Flip-Flop with Synchronous Set and Reset, Single Pin Version

- ED16SS

16-Bit D-Type Flip-Flop with Synchronous Set, Single Pin Version

- ED32B 32-Bit D-Type Flip-Flop, Bus Version

- <u>FD32CB</u> 32-Bit D-Type Flip-Flop with Asynchronous Clear, Bus Version

- FD32CEB 32-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Clear, Bus Version

- <u>FD32CPB</u> 32-Bit D-Type Flip-Flop with Asynchronous Preset and Clear, Bus Version

- ED32CPEB 32-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear, Bus Version

- <u>FD32EB</u> 32-Bit D Flip-Flop with Clock Enable, Bus Version

- <u>FD32PB</u> 32-Bit D-Type Flip-Flop with Asynchronous Preset, Bus Version

- ED32PEB 32-Bit D-Type Flip-Flop with Clock Enable and Asynchronous Preset, Bus Version

- <u>FD32RB</u> 32-Bit D-Type Flip-Flop with Synchronous Reset, Bus Version

- FD32REB 32-Bit D-Type Flip-Flop with Clock Enable and Synchronous Reset, Bus Version

- <u>FD32RSB</u> 32-Bit D-Type Flip-Flop with Synchronous Reset and Set, Bus Version

- FD32RSEB 32-Bit D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable, Bus Version

- ED32SB 32-Bit D-Type Flip-Flop with Synchronous Set, Bus Version

- FD32SEB 32-Bit D-Type Flip-Flop with Clock Enable and Synchronous Set, Bus Version

- <u>FD32SRB</u> 32-Bit D-Type Flip-Flop with Synchronous Set and Reset, Bus Version

- ED32SREB 32-Bit D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable, Bus Version

- <u>FD\_1</u> D-Type Negative Edge Flip-Flop

- EDC D-Type Flip-Flop with Asynchronous Clear

- <u>FDC\_1</u> D-Type Negative Edge Flip-Flop with Asynchronous Clear

- EDCE D-Type Flip-Flop with Clock Enable and Asynchronous Clear

- FDCE\_1 D-Type Negative Edge Flip-Flop with Clock Enable, Asynchronous Clear and Dual output

- EDCEN D-Type Flip-Flop with Clock Enable, Asynchronous Clear and Inverted and Non-Inverted Outputs

- EDCN D-Type Flip-Flop with Asynchronous Clear and Inverted and Non-Inverted Outputs

- EDCP D-Type Flip-Flop with Asynchronous Preset and Clear

- <u>FDCP\_1</u> D-Type Negative Edge Flip-Flop with Asynchronous Preset and Clear

- EDCPE D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Clear

- FDCPE\_1 D-Type Negative Edge Flip-Flop with Clock Enable and Asynchronous

Preset and Clear

- EDCPEN

D-Type Flip-Flop with Clock Enable, Asynchronous Preset, Clear and Inverted and Non-Inverted Outputs

- EDCPN D-Type Flip-Flop with Asynchronous Preset, Clear and Inverted and Non-Inverted Outputs

- FDE D Flip-Flop with Clock Enable

- <u>FDE\_1</u> D Negative Edge Flip-Flop with Clock Enable

- EDEN D Flip-Flop with Clock Enable and Inverted and Non-Inverted Outputs

- EDN D-Type Flip-Flop with Inverted and Non-Inverted Outputs

- EDP D-Type Flip-Flop with Asynchronous Preset

- <u>FDP\_1</u> D-Type Negative Edge Flip-Flop with Asynchronous Preset

- EDPE D-Type Flip-Flop with Clock Enable and Asynchronous Preset

- <u>FDPE\_1</u> D-Type Flip-Flop with Clock Enable and Asynchronous Preset

- EDPEN D-Type Flip-Flop with Clock Enable and Asynchronous Preset and Inverted and Non-Inverted Outputs

- EDPN D-Type Flip-Flop with Asynchronous Preset and Inverted and Non-Inverted Outputs

- EDR D-Type Flip-Flop with Synchronous Reset

- EDR 1

D-Type Negative Edge Flip-Flop with Synchronous Reset

- EDRE D-Type Flip-Flop with Clock Enable and Synchronous Reset

- <u>FDRE\_1</u> D-Type Negative Edge Flip-Flop with Clock Enable and Synchronous Reset

- EDREN D-Type Flip-Flop with Clock Enable Synchronous Reset and Inverted and Non-Inverted Outputs

- EDRN D-Type Flip-Flop with Synchronous Reset and Inverted and Non-Inverted Outputs

- EDRS

D-Type Flip-Flop with Synchronous Reset and Set, Single Pin Version

- <u>FDRS\_1</u> D-Type Negative Edge Flip-Flop with Synchronous Reset and Set

- EDRSE D-Type Flip-Flop with Synchronous Reset and Set and Clock Enable

- FDRSE\_1 D-Type Negative Edge Flip-Flop with Synchronous Reset and Set and Clock Enable

- EDRSEN

D-Type Flip-Flop with Synchronous Reset and Set, Clock Enable and Inverted and Non-Inverted Outputs

- EDRSN D-Type Flip-Flop with Synchronous Reset, Set and Inverted and Non-Inverted Outputs

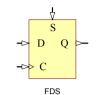

- <u>FDS</u> D-Type Flip-Flop with Synchronous Set, Single Pin Version

- <u>FDS\_1</u> D-Type Negative Edge Flip-Flop with Synchronous Set

- EDSE D-Type Flip-Flop with Clock Enable and Synchronous Set

- <u>FDSE\_1</u> D-Type Negative Edge Flip-Flop with Clock Enable and Synchronous Set

- EDSEN D-Type Flip-Flop with Clock Enable Synchronous Set and Inverted and Non-Inverted Outputs

- EDSN D-Type Flip-Flop with Synchronous Set and Inverted and Non-Inverted Outputs

- EDSR D-Type Flip-Flop with Synchronous Set and Reset

- <u>FDSR\_1</u> D-Type Negative Edge Flip-Flop with Synchronous Set and Reset

- EDSRE D-Type Flip-Flop with Synchronous Set and Reset and Clock Enable

- FDSRE\_1 D-Type Negative Edge Flip-Flop with Synchronous Set and Reset and Clock Enable

- EDSREN D-Type Flip-Flop with Synchronous Set, Reset, Clock Enable and Inverted and Non-Inverted Outputs

- EDSRN D-Type Flip-Flop with Synchronous Set, Reset and Inverted and Non-Inverted Outputs

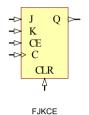

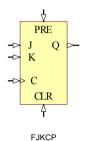

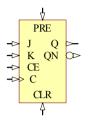

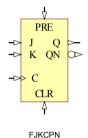

- EJKC J-K Flip-Flop with Asynchronous Clear

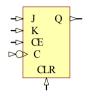

- <u>FJKC\_1</u> J-K Negative Edge Flip-Flop with Asynchronous Clear

- EJKCE J-K Flip-Flop with Clock Enable and Asynchronous Clear

- FJKCE\_1 J-K Negative Edge Flip-Flop with Clock Enable and Asynchronous Clear

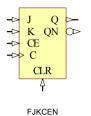

- FJKCEN J-K Flip-Flop with Clock Enable, Asynchronous Clear and Inverted and Non-Inverted Outputs

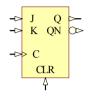

- FJKCN J-K Flip-Flop with Asynchronous Clear and Inverted and Non-Inverted

Outputs

- <u>FJKCP</u> J-K Flip-Flop with Asynchronous Clear and Preset

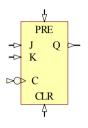

- <u>FJKCP\_1</u> J-K Negative Edge Flip-Flop with Asynchronous Clear and Preset

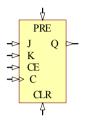

- <u>FJKCPE</u> J-K Flip-Flop with Asynchronous Clear and Preset and Clock Enable

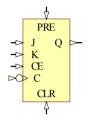

- <u>FJKCPE\_1</u> J-K Negative Edge Flip-Flop with Asynchronous Clear and Preset and Clock Enable

- FJKCPEN J-K Flip-Flop with Asynchronous Clear, Preset, Clock Enable and Inverted and Non-Inverted Outputs

- FJKCPN J-K Flip-Flop with Asynchronous Clear, Preset and Inverted and Non-Inverted Outputs

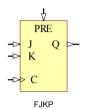

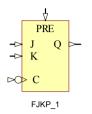

- <u>FJKP</u> J-K Flip-Flop with Asynchronous Preset

- <u>FJKP\_1</u> J-K Negative Edge Flip-Flop with Asynchronous Preset

- FJKPE J-K Flip-Flop with Clock Enable and Asynchronous Preset

- <u>FJKPE 1</u> J-K Negative Edge Flip-Flop with Clock Enable and Asynchronous Preset

- FJKPEN J-K Flip-Flop with Clock Enable, Asynchronous Preset and Inverted and Non-Inverted Outputs

- FJKPN J-K Flip-Flop with Asynchronous Preset and Inverted and Non-Inverted Outputs

- FJKRSE J-K Flip-Flop with Clock Enable and Synchronous Reset and Set

- FJKRSE\_1 J-K Negative Edge Flip-Flop with Clock Enable and Synchronous Reset and Set

- FJKRSEN J-K Flip-Flop with Clock Enable, Synchronous Reset and Set and Inverted and Non-Inverted Outputs

- FJKSRE J-K Flip-Flop with Clock Enable and Synchronous Set and Reset

- FJKSRE\_1 J-K Negative Edge Flip-Flop with Clock Enable and Synchronous Set and Reset

- FJKSREN J-K Flip-Flop with Clock Enable, Synchronous Set and Reset and Inverted and Non-Inverted Outputs

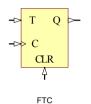

- <u>FTC</u>

Toggle Flip-Flop with Toggle Enable and Asynchronous Clear

- FTC 1

Negative Edge Toggle Flip-Flop with Toggle Enable and Asynchronous

Clear

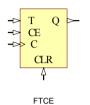

- Example 2 Flip-Flop with Toggle and Clock Enable and Asynchronous Clear

- FTCE\_1

Negative Edge Toggle Flip-Flop with Toggle and Clock Enable and

Asynchronous Clear

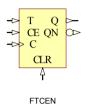

- FTCEN Toggle Flip-Flop with Toggle, Clock Enable, Asynchronous Clear and Inverted and Non-Inverted Outputs

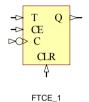

- <u>FTCLE</u>

Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Clear

- <u>FTCLE\_1</u>

Toggle/Loadable Negative Edge Flip-Flop with Toggle and Clock Enable and Asynchronous Clear

- <u>FTCLEN</u>

Toggle/Loadable Flip-Flop with Toggle, Clock Enable, Asynchronous Clear and Inverted and Non-Inverted Outputs

- <u>FTCN</u>

Toggle Flip-Flop with Toggle Enable, Asynchronous Clear and Inverted and Non-Inverted Outputs

- ETCP Toggle Flip-Flop with Toggle Enable and Asynchronous Clear and Preset

- FTCP\_1 Negative Edge Toggle Flip-Flop with Toggle Enable and Asynchronous

Clear and Preset

- ETCPE Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear and Preset

- FTCPE\_1 Negative Edge Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear and Preset

- <u>FTCPEN</u>

Toggle Flip-Flop with Toggle, Clock Enable, Asynchronous Clear and Preset and Inverted and Non-Inverted Outputs

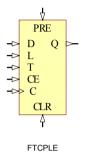

- <u>FTCPLE</u>

Loadable Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear and Preset

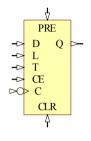

- <u>FTCPLE\_1</u>

Loadable Negative Edge Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear and Preset

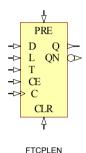

- <u>FTCPLEN</u>

Loadable Toggle Flip-Flop with Toggle, Clock Enable, Asynchronous Clear and Preset and Inverted and Non-Inverted Outputs

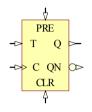

- FTCPN Toggle Flip-Flop with Toggle Enable, Asynchronous Clear, Preset and Inverted and Non-Inverted Outputs

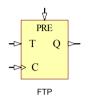

- ETP Toggle Flip-Flop with Toggle Enable and Asynchronous Preset

- FTP\_1

Negative Edge Toggle Flip-Flop with Toggle Enable and Asynchronous

Preset

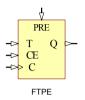

- ETPE Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Preset

- FTPE\_1 Negative Edge Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Preset

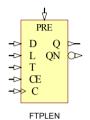

- FTPEN Toggle Flip-Flop with Toggle, Clock Enable, Asynchronous Preset and Inverted and Non-Inverted Outputs

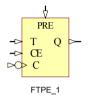

- FTPLE Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Preset

- <u>FTPLE 1</u>

Toggle/Loadable Negative Edge Flip-Flop with Toggle and Clock Enable and Asynchronous Preset

- FTPLEN Toggle/Loadable Flip-Flop with Toggle, Clock Enable, Asynchronous Preset and Inverted and Non-Inverted Outputs

- FTPN Toggle Flip-Flop with Toggle Enable, Asynchronous Preset and Inverted and Non-Inverted Outputs

- FTRSE Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Reset and Set

- FTRSE\_1 Negative Edge Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Reset and Set

- FTRSEN Toggle Flip-Flop with Toggle, Clock Enable, Synchronous Reset and Set and Inverted and Non-Inverted Outputs

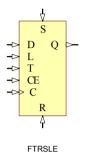

- FTRSLE Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Synchronous

Reset and Set

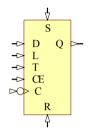

- <u>FTRSLE\_1</u> Toggle/Loadable Negative Edge Flip-Flop with Toggle and Clock Enable and Synchronous Reset and Set

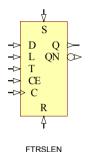

- FTRSLEN Toggle/Loadable Flip-Flop with Toggle, Clock Enable, Synchronous Reset and Set and Inverted and Non-Inverted Outputs

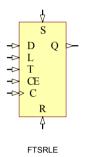

- FTSRE Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset

- FTSRE\_1 Negative Edge Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset

- FTSREN Toggle Flip-Flop with Toggle, Clock Enable, Synchronous Set and Reset

and Inverted and Non-Inverted Outputs

- FTSRLE Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset

- FTSRLE\_1

Toggle/Loadable Negative Edge Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset

- FTSRLEN Toggle/Loadable Flip-Flop with Toggle, Clock Enable, Synchronous Set and Reset and Inverted and Non-Inverted Outputs

# JTAG

<u>NEXUS JTAG PORT</u> Soft Nexus-Chain Connector

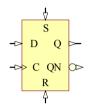

# Latch

Various latches are available as follows:

- LD Transparent Data Latch

- LD2B 2-Bit Transparent Data Latch, Bus Version

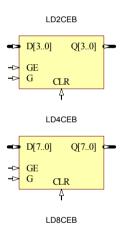

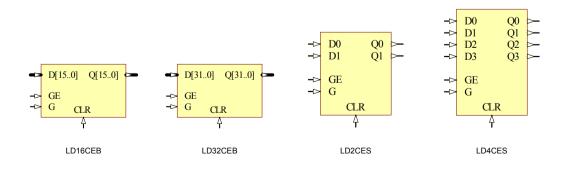

- LD2CEB 2-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Bus Version

- LD2CES 2-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Single Pin Version

- LD2S 2-Bit Transparent Data Latch, Single Pin Version

- LD3B 3-Bit Transparent Data Latch, Bus Version

- LD3S 3-Bit Transparent Data Latch, Single Pin Version

- LD4B

4-Bit Transparent Data Latch, Bus Version

- LD4CEB

4-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Bus Version

- LD4CES 4-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Single Pin Version

- LD4S 4-Bit Transparent Data Latch, Single Pin Version

- LD8B 8-Bit Transparent Data Latch, Bus Version

- LD8CEB 8-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Bus Version

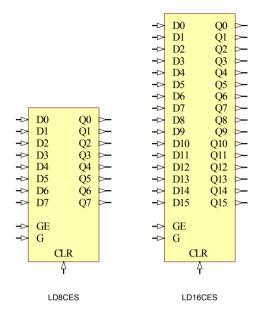

- LD8CES

8-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Single Pin Version

- LD8S 8-Bit Transparent Data Latch, Single Pin Version

- LD16B

16-Bit Transparent Data Latch, Bus Version

- LD16CEB 16-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Bus Version

- LD16CES 16-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Single Pin Version

- LD16S 16-Bit Transparent Data Latch, Single Pin Version

- LD32B 32-Bit Transparent Data Latch, Bus Version

- LD32CEB 32-Bit Transparent Data Latch with Asynchronous Clear and Gate Enable, Bus Version

- LD 1 Transparent Data Latch with Inverted Gate

- LDC Transparent Data Latch with Asynchronous Clear

- LDC 1

Transparent Data Latch with Asynchronous Clear and Inverted Gate

- LDCE Transparent Data Latch with Asynchronous Clear and Gate Enable

- LDCE\_1 Transparent Data Latch with Asynchronous Clear, Gate Enable, and Inverted Gate

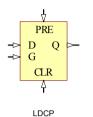

- LDCP Transparent Data Latch with Asynchronous Clear and Preset

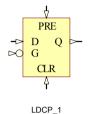

- LDCP\_1 Transparent Data Latch with Asynchronous Clear and Preset and Inverted Gate

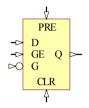

- LDCPE Transparent Data Latch with Asynchronous Clear and Preset and Gate Enable

- LDCPE\_1 Transparent Data Latch with Asynchronous Clear and Preset, Gate Enable, and Inverted Gate

- LDE Transparent Data Latch with Gate Enable

- LDE\_1 Transparent Data Latch with Gate Enable and Inverted Gate

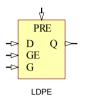

- LDP Transparent Data Latch with Asynchronous Preset

- LDP\_1 Transparent Data Latch with Asynchronous Preset and Inverted Gate

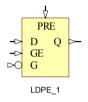

- LDPE Transparent Data Latch with Asynchronous Preset and Gate Enable

- LDPE\_1 Transparent Data Latch with Asynchronous Preset, Gate Enable, and Inverted Gate

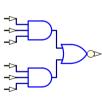

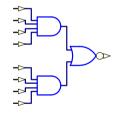

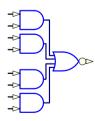

# **Logic Primitive**

Basic building block logic primitives are available under the following sub classes:

- AND Gates

- Inverters

- NAND Gates

- NOR Gates

- OR Gates

- Sum of Product

- <u>True/Complement</u>

- XNOR Gates

- XOR Gates

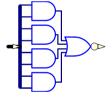

# **AND Gates**

Various inputs and dual output AND Gates are available as follows:

- <u>AND2B</u> 2-Input AND Gate, Bus Version

- AND2DB 2-Input AND/NAND Gate, Bus Version

- AND2DS 2-Input AND/NAND Gate, Single Pin Version

- AND2N1B 2-Input AND Gate with Active Low A Input, Bus Version

- AND2N1S 2-Input AND Gate with Active Low A Input, Single Pin Version

- AND2N2B 2-Input AND Gate with Active Low A and B Inputs, Bus Version

- AND2N2S 2-Input AND Gate with Active Low A and B Inputs, Single Pin Version

- AND2S 2-Input AND Gate, Single Pin Version

- AND3B 3-Input AND Gate, Bus Version

- AND3DB 3-Input AND/NAND Gate, Bus Version

- AND3DS 3-Input AND/NAND Gate, Single Pin Version

- AND3N1B 3-Input AND Gate with Active Low A Input, Bus Version

- AND3N1S 3-Input AND Gate with Active Low A Input, Single Pin Version

- AND3N2B 3-Input AND Gate with Active Low A and B Inputs, Bus Version

- AND3N2S 3-Input AND Gate with Active Low A and B Inputs, Single Pin Version

- AND3N3B 3-Input AND Gate with Active Low A, B and C Inputs, Bus Version