# PERFORMANCE BOTTLENECKS ON LARGE-SCALE SHARED-MEMORY MULTIPROCESSORS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Robert C. Kunz December 2004

© Copyright by Robert C. Kunz 2005 All Rights Reserved

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dr. John Hennessy<br>(Principal Advisor)                                                                                                                                  |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy. |

| Dr. Mark Horowitz                                                                                                                                                         |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy. |

| Dr. Christos Kozyrakis                                                                                                                                                    |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy. |

| Dr. Mark Heinrich                                                                                                                                                         |

| Approved for the University Committee on Graduate Studies:                                                                                                                |

### **Abstract**

While multiprocessors have existed for many years, most parallel architectures are difficult to program efficiently. The key challenge is how to simplify the programming model so that programmers can write portable highly efficient parallel programs with minimal effort. For example, cache-coherent shared-memory architectures trade the memory system complexity of the coherence protocol for a simpler programming model that does not require communication to be programmed explicitly.

Software developers, operating systems researchers, and hardware architects have worked in their respective areas to improve the parallel efficiency of general-purpose applications. A critical question remains unanswered: how do advancements in each of these areas behave collectively? Using the FLASH machine, a large-scale cc-NUMA multiprocessor, this dissertation explores the interaction between hardware and software design trade-offs and quantifies the performance gains of memory system enhancements.

Researchers working on multiprocessor memory systems have advocated easing the programming burden by adding enhancements to the memory system designed to reduce memory latency and coherence overhead. Of course, these enhancements also add complexity and affect the speed of basic memory operations. Analogous to the lessons learned during the RISC movement over 20 years ago, this dissertation demonstrates that at large processor counts, simpler memory system designs are faster than more complicated ones, primarily because the additional contention present in the memory system overwhelms minor reductions in latency that more complicated protocols provide. Thus, architects should focus on minimizing memory controller occupancy on large-scale multiprocessors rather than just latency.

Even setting aside contention, the coherence protocol is a smaller bottleneck than other system aspects including the operating system's scheduling policies and the application's

effective or ineffective use of the cache coherent memory system. Our results indicate that to achieve reasonable performance, programmers still need to tune their programs to a specific architecture; such tuning limits portability. While coherence protocols might be able to provide a reduction in remote communication, the mismatch between an application and the architecture are often more significant and prevent major performance improvements.

Our results indicate that large-scale multiprocessors continue to remain difficult to program because the memory system alone cannot eliminate the need for programmers to remain aware of implicit communication. The software libraries, compiler, and operating system must apply complex machine-specific optimizations to reduce second- and third-order performance bottlenecks. Therefore, the memory system should provide meaningful visibility and feedback to programming monitoring tools and compilers. Without such tools to assist programmers, the programming advantages of a coherent shared memory multiprocessor versus a message passing multiprocessor are likely to be small for larger processor counts.

## **Acknowledgments**

Do or do not. There is no try. -Yoda

Finishing the FLASH project has been the most challenging and yet rewarding experience of my professional life. Completing this dissertation would not have been possible without the efforts of many others who helped support me along the way.

First, I would like to thank John Hennessy, my principle advisor, for his guidance and mentoring over the last seven years. Working with him has been a dream of mine ever since my first computer architecture coarse over a decade ago. Despite his many commitments outside of the electrical engineering department, John has alway been there for me when I needed him. His efforts improved my research and writing tremendously.

I would also like to thank Mark Horowitz for serving as my secondary advisor. Through the years, he always looked out for his adopted students by setting the bar high. His feedback and encouragement improved my work tremendously. Mark Heinrich proved a valuable resource, even at a considerable physical distance from Stanford. I owe him a great debt for all of his time revising papers, discussing new directions, providing encouragement and some much needed humor. In addition, I thank Christos Kozyrakis for serving on my dissertation reading committee and Bernd Girod for chairing my oral defense committee.

My research would not have been possible without the foundation layed by the original FLASH team including Jeff Kuskin, David Ofelt, John Heinlein, Richard Simoni, Kourosh Gharachorloo, John Chapin, David Nakahira, Joel Baxter, Anoop Gupta, Mendel Rosenblum, and everyone else involved in the design and verification of the FLASH machine.

I would especially like to thank fellow members of John Hennessy's research group including David Ofelt, Joel Baxter, and Jeff Gibson for taking me under their wing and continuing to provide guidance even after they moved on to exciting new projects. I deeply respect their efforts and contributions to the FLASH project and my own work. Their

efforts taught me the skills to succeed.

In addition, I would also like to acknowledge the generous contributions of Kelly Shaw, Elizabeth Seamans and Ayodele Thomas during our weekly meetings over the last three years. Our research sessions helped refine my work and enabled us to exchange our ideas. Through their efforts, I learned about multiprocessors in other design spaces such as single-chip multiprocessors, network routers, and reconfigurable computers.

Mark Horowitz's research group provided a valuable resource as my research progressed as a forum for both testing ideas and remaining current in diverse research areas such as graphics and circuit design. Thank you to everyone in Mark's group including Bennett Wilburn, David Lee and my office mates, Francois Labonte and Jim Weaver.

Colleagues and friends are critical for success in the Ph.D. program. I especially would like to thank Dean Liu for his support and encouragement over the years. During our first years in the program, we were inseperable in classes and our friendship continues to this day. Robert Bosch gave countless hours of his time helping me as I learned the SimOS simulator. He proved to be not only a key resource but also a good friend.

In addition, Kinshuk Govil, and Ravi Soundararajan provided critical FLASH training and taught me humility through fantasy football leagues and Texas Hold'Em tournaments. Kinshuk taught me all that I know about operating systems and Ravi provided the initial remote access cache implementation.

I would also like to acknowledge SGI for providing the source code for the IRIX6.5 kern and libmp OpenMP library. Without their generous contribution to our project, none of this analysis would be possible. I would also like to thank the Department of Energy for their gracious research funding for our project under grand number DE-FG02-03ER25564.

My extended family stood by me through my graduate program and I thank them for their love and support over the years. I especially thank my grandparents, Fredda (now deceased), Warren, Bernice, and Louis, my parents, Ron and Fran, and my sisters, Amy and Katharine.

Finally, I would like to thank my lovely wife, Meredith, for supporting me over the years. Her patience and love have been a godsend. She ensured that I took my research seriously enough to finish but that I wouldn't take myself too seriously and miss the journey.

# **Contents**

| Al | Abstract        |          |                                                      |     |

|----|-----------------|----------|------------------------------------------------------|-----|

| A  | Acknowledgments |          |                                                      | vii |

| 1  | Intr            | oductio  | n                                                    | 1   |

|    | 1.1             | Resear   | rch Contributions                                    | 3   |

|    | 1.2             | Organ    | ization of the Dissertation                          | 4   |

| 2  | Evo             | lving to | wards cc-NUMA Multiprocessors                        | 7   |

|    | 2.1             | Progra   | nmming Model Design                                  | 8   |

|    | 2.2             | Evolut   | tion of Multiprocessor Architectures                 | 10  |

|    |                 | 2.2.1    | The Uniprocessor Programming Model                   | 10  |

|    |                 | 2.2.2    | Small-scale Symmetric Multiprocessors                | 11  |

|    |                 | 2.2.3    | Message-Passing Multiprocessor                       | 13  |

|    |                 | 2.2.4    | Simple NUMA Multiprocessors                          | 15  |

|    |                 | 2.2.5    | cc-NUMA Multiprocessors                              | 16  |

|    |                 | 2.2.6    | Summary                                              | 17  |

|    | 2.3             | Perfor   | mance Bottlenecks Present in cc-NUMA Multiprocessors | 18  |

|    |                 | 2.3.1    | Application-Centric Bottlenecks                      | 19  |

|    |                 | 2.3.2    | Architecture and Application-Created Bottlenecks     | 20  |

|    |                 | 2.3.3    | Machine Dependent Bottlenecks                        | 23  |

|    | 2.4             | The F    | LASH Multiprocessor                                  | 25  |

|    |                 | 2.4.1    | FLASH-specific Performance Bottlenecks               | 27  |

|    | 2.5             | Summ     | ary                                                  | 27  |

| 3 | Para | allel Be | nchmarks                                     | 29 |

|---|------|----------|----------------------------------------------|----|

|   | 3.1  | SPLA     | SH-2 Benchmark Suite                         | 30 |

|   | 3.2  | SpecC    | MP2001 Benchmark Suite                       | 33 |

|   |      | 3.2.1    | Parallel Programming using the OpenMP API    | 33 |

|   |      | 3.2.2    | High-Level SpecOMP2001 Characteristics       | 36 |

|   | 3.3  | Summ     | nary                                         | 41 |

| 4 | Ope  | rating S | System Performance and Bottlenecks           | 43 |

|   | 4.1  | Multip   | processor Scheduling Policies                | 44 |

|   |      | 4.1.1    | Time-Sharing Techniques                      | 45 |

|   |      | 4.1.2    | Space Scheduling Techniques                  | 46 |

|   | 4.2  | Unloa    | ded Overheads of Scheduling Policies         | 48 |

|   |      | 4.2.1    | Methodology                                  | 48 |

|   |      | 4.2.2    | Results                                      | 50 |

|   | 4.3  | Sched    | uling Overheads in a Multi-user Environment  | 53 |

|   |      | 4.3.1    | Methodology                                  | 54 |

|   |      | 4.3.2    | Results                                      | 54 |

|   | 4.4  | Summ     | nary                                         | 57 |

| 5 | Perf | ormano   | ce Trade-offs in Memory System Design        | 59 |

|   | 5.1  | Latence  | ey and Occupancy                             | 60 |

|   | 5.2  | Coher    | ence Protocols Design                        | 61 |

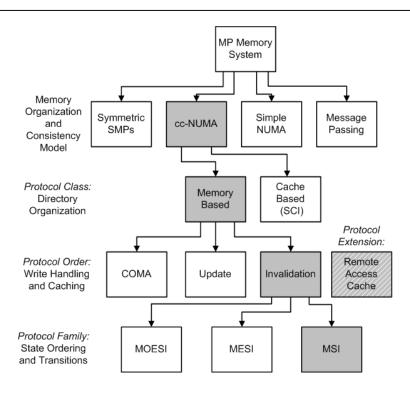

|   |      | 5.2.1    | The Architectural Layer                      | 61 |

|   |      | 5.2.2    | The Organizational Layer                     | 63 |

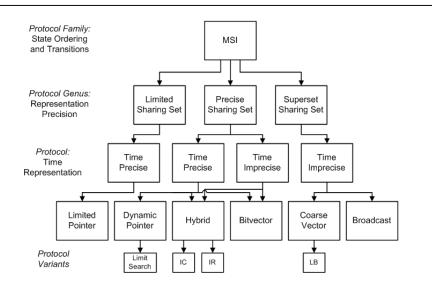

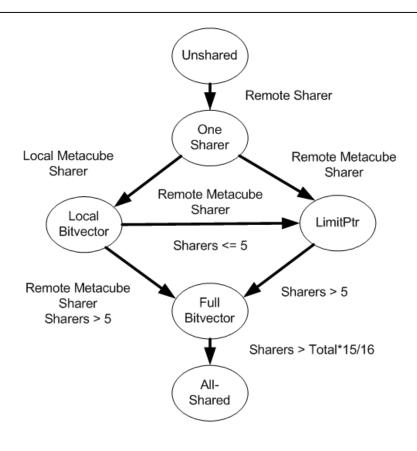

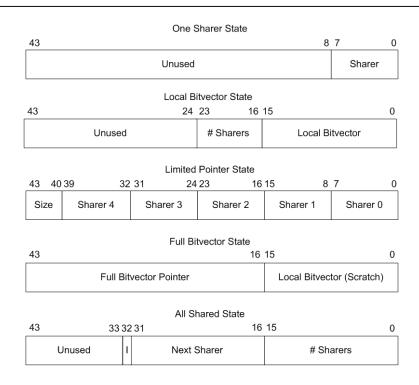

|   |      | 5.2.3    | Protocol Variants                            | 70 |

|   |      | 5.2.4    | Coherence Protocol Complexity                | 75 |

|   | 5.3  | Quant    | ifying Realistic Coherence Protocol Behavior | 76 |

|   |      | 5.3.1    | Point-to-Point Latency Analysis              | 77 |

|   |      | 5.3.2    | SpecOMP2001 Protocol Results                 | 81 |

|   |      | 5.3.3    | Protocol Extensions                          | 85 |

|   |      | 5.3.4    | The Occupancy Limit                          | 86 |

|   | 5.4  | The R    | emote Access Cache Protocol Extension        | 90 |

|   |      | 5.4.1    | Latency Characteristics of a RAC             | 90 |

|    |       | 5.4.2    | Occupancy Costs of a RAC                               | . 92  |

|----|-------|----------|--------------------------------------------------------|-------|

|    | 5.5   | Quanti   | fying Ideal Coherence Protocol Behavior                | . 95  |

|    |       | 5.5.1    | Methodology                                            | . 96  |

|    |       | 5.5.2    | Quantifying Latency Terms                              | . 98  |

|    |       | 5.5.3    | Performance of the Ideal Protocols                     | . 99  |

|    |       | 5.5.4    | Scaling Impact of the Ideal Protocols                  | . 100 |

|    |       | 5.5.5    | The Impact of Latency Hiding                           | . 103 |

|    | 5.6   | Summ     | ary                                                    | . 107 |

| 6  | Soft  | ware Bo  | ottlenecks and Optimizations                           | 109   |

|    | 6.1   | Increas  | sing Communication-to-Computation Ratio                | . 109 |

|    | 6.2   | Unnec    | essary Implicit Communication                          | . 112 |

|    |       | 6.2.1    | ART: Cache- and Page-Level False Sharing               | . 113 |

|    |       | 6.2.2    | APPLU: Poor Data Management                            | . 114 |

|    |       | 6.2.3    | APSI: Poor Data and Cache Management and False-Sharing | . 116 |

|    | 6.3   | Load I   | mbalance and Synchronization                           | . 118 |

|    |       | 6.3.1    | GAFORT: Lock Contention                                | . 118 |

|    | 6.4   | Summ     | ary                                                    | . 120 |

| 7  | Con   | clusions | S                                                      | 123   |

|    | 7.1   | Conclu   | asion                                                  | . 123 |

|    | 7.2   | Future   | Work                                                   | . 125 |

| A  | Inte  | rconnec  | ction Network Revisited                                | 127   |

| D: | hliog | ranhv    |                                                        | 133   |

# **List of Tables**

| 2.1 | Key Architecture Parameters for the FLASH machine              | 26  |

|-----|----------------------------------------------------------------|-----|

| 3.1 | SPLASH-2 Size and Time Characteristics                         | 31  |

| 3.2 | SpecOMP2001 Size and Time Characteristics                      | 37  |

| 5.1 | Coherence Protocol Complexity and Size                         | 75  |

| 5.2 | Protocol Read Latencies in Clock Cycles and Normalized to CV=2 | 78  |

| 5.3 | SpecOMP2001 Parallel Efficiency                                | 87  |

| 5.4 | SpecOMP2001 Total Occupied Cycles Normalized to CV=2           | 87  |

| A.1 | Routing Tables for 8-processor FLASH machine                   | 129 |

# **List of Figures**

| 1.1 | Published Papers between 1970 and 2004                                | 2  |

|-----|-----------------------------------------------------------------------|----|

| 2.1 | The programming design process                                        | 9  |

| 2.2 | Symmetric multiprocessor architecture                                 | 11 |

| 2.3 | Message-Passing Multiprocessors                                       | 13 |

| 2.4 | cc-NUMA Architecture                                                  | 16 |

| 2.5 | Complexity of functional and performance programming                  | 18 |

| 2.6 | General false sharing types                                           | 24 |

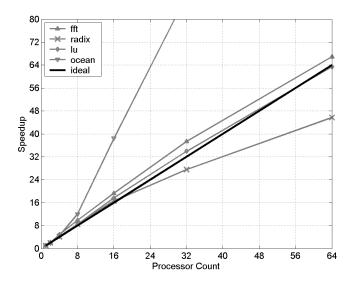

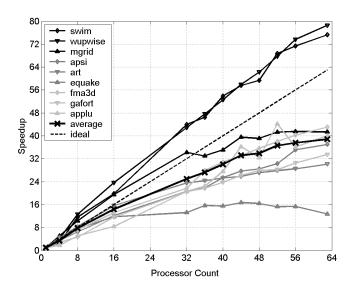

| 3.1 | Speedups for the SPLASH-2 benchmarks                                  | 32 |

| 3.2 | Simple loop example                                                   | 33 |

| 3.3 | Simple parallel loop using the OpenMP API                             | 34 |

| 3.4 | Simple parallel loop using ANL Macros                                 | 35 |

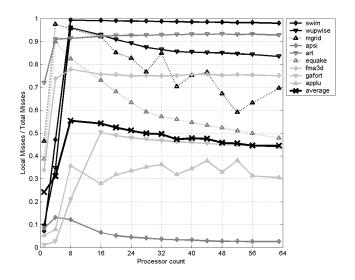

| 3.5 | Local cache misses over total cache misses from 1 to 63 processors    | 38 |

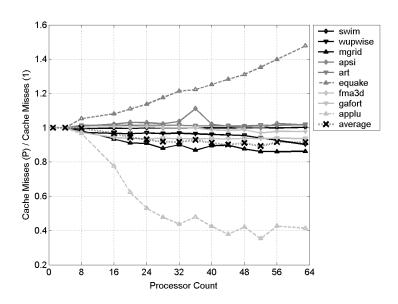

| 3.6 | Total L2 cache misses for the SpecOMP2001 benchmarks from 1 to 63     |    |

|     | processors                                                            | 39 |

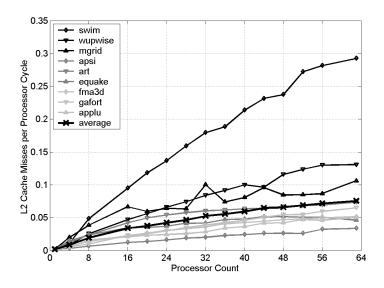

| 3.7 | L2 cache misses per R10k processor cycles                             | 41 |

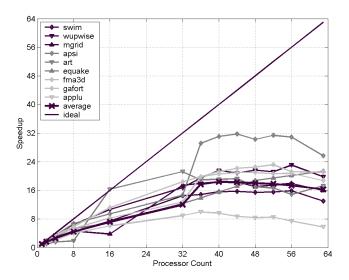

| 3.8 | Out-of-the-Box speedups of the SpecOMP2001 benchmarks                 | 42 |

| 4.1 | Pinning threads code example                                          | 49 |

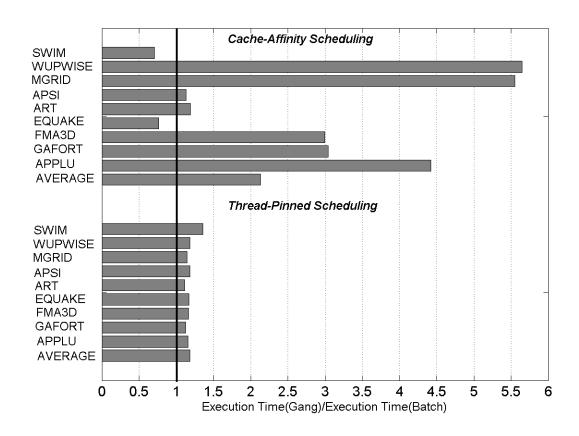

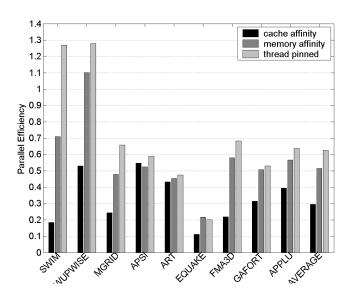

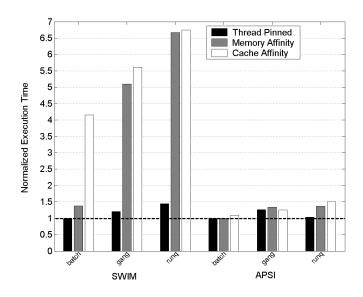

| 4.2 | Gang scheduling overheads at 63 processors                            | 50 |

| 4.3 | Parallel efficiencies for space scheduling policies at 63 processors  | 52 |

| 4.4 | OS multiprocessor scheduling policies at 63 processors                | 55 |

| 4.5 | SpecOMP2001 speedup with pinning enabled and gang scheduling disabled | 56 |

| 5.1 | Architectural Layer taxonomy                                          | 62 |

| 5.2  | The MSI coherence protocol family                                       |

|------|-------------------------------------------------------------------------|

| 5.3  | Sharing list state machine of sharing state list                        |

| 5.4  | Bit definitions of sharing state list                                   |

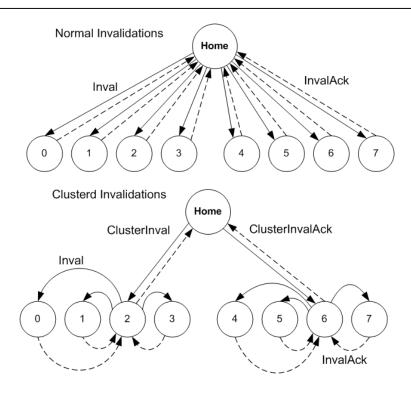

| 5.5  | Normal versus clustered invalidations                                   |

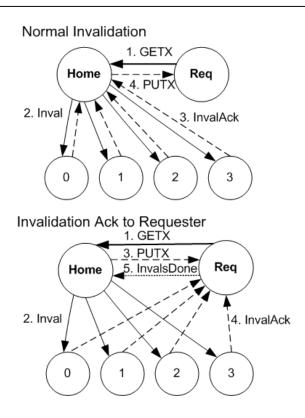

| 5.6  | Base versus requester invalidations acknowledgments                     |

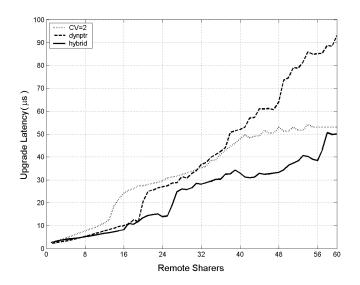

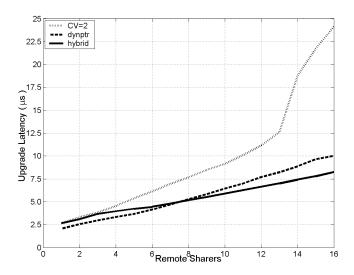

| 5.7  | Average upgrade latency versus total sharers                            |

| 5.8  | Average upgrade latency from 1 to 16 sharers                            |

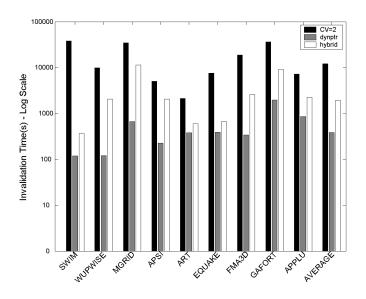

| 5.9  | Aggregate invalidation time at 63 processors                            |

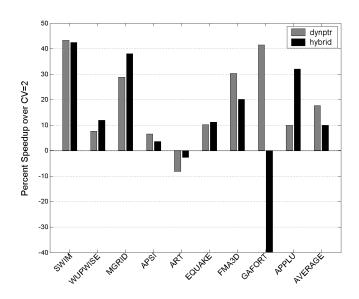

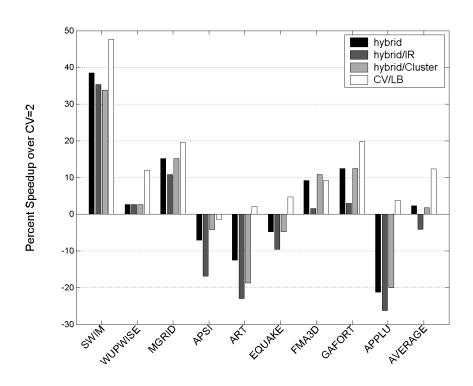

| 5.10 | Speedup relative to the CV=2 protocol at 8 processors 82                |

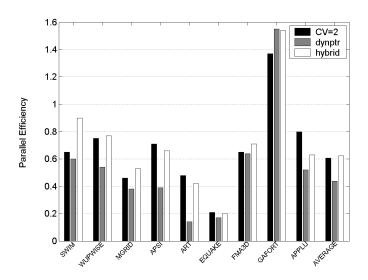

| 5.11 | Parallel efficiency at 63 processors                                    |

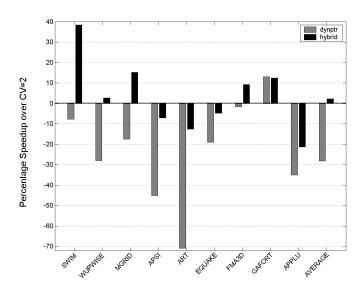

| 5.12 | Speedup relative to the CV=2 protocol at 63 processors 84               |

| 5.13 | Speedup relative to CV=2 at 63 processors                               |

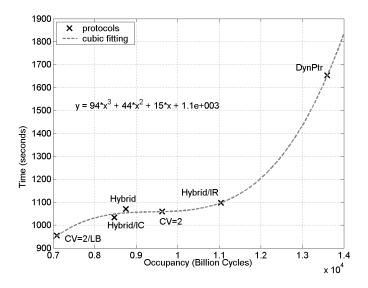

| 5.14 | Execution time versus occupancy at 63 processors                        |

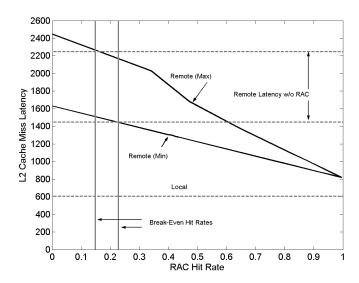

| 5.15 | Remote L2 cache miss latencies versus RAC hit rates 91                  |

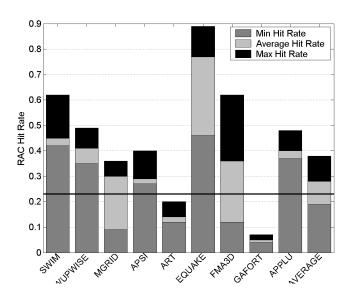

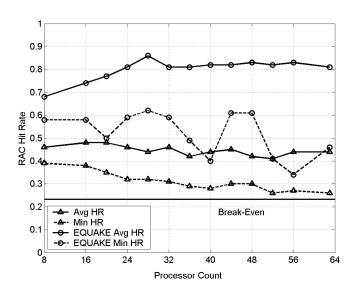

| 5.16 | SpecOMP2001 RAC hit rates                                               |

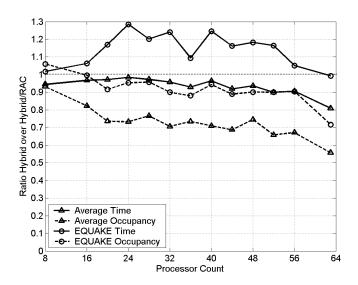

| 5.17 | Key parameter ratios of hybrid over hybrid/RAC=32MB protocols 93        |

| 5.18 | RAC hit rate versus processor count                                     |

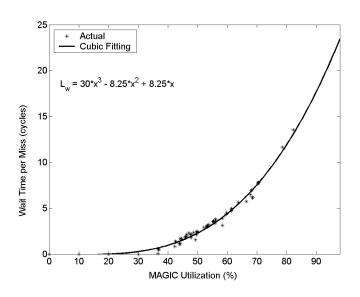

| 5.19 | Local wait time, $L_w$ versus MAGIC occupancy                           |

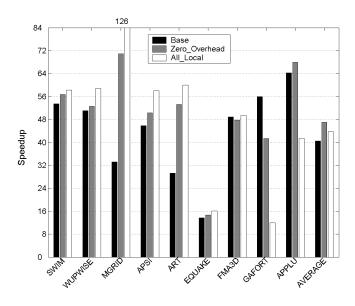

| 5.20 | Ideal speedups versus benchmark                                         |

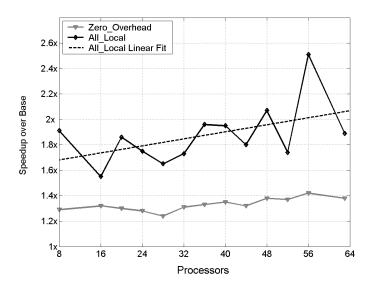

| 5.21 | Ideal Speedup versus Processor Count                                    |

| 5.22 | Ideal speedup at 63 processors                                          |

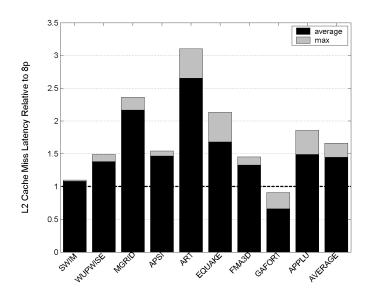

| 5.23 | Latency Ratio - 63 processors over 8 processors                         |

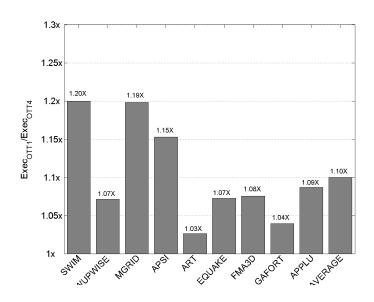

| 5.24 | Latency hiding from 1 to 4 outstanding transactions                     |

|      | Execution time versus processor count with 1-OTT                        |

| 5.26 | Ideal speedup versus processor count with 1-OTT                         |

| 6.1  | L2 cache misses relative to 8 processors at 63 proessors                |

| 6.2  | Pseudo-code for EQUAKE's sparse-matrix vector product procedure 111     |

| 6.3  | Optimized pseudo-code for optimized spares-matrix vector product proce- |

|      | dure                                                                    |

| 6.4  | Pseudo-code for ART's variable declarations                             |

| 6.5  | Optimized pseudo-code for ART's variable declarations                   |

| 6.6  | Pseudo-code for APPLU's scratch variable initialization and use         |

| 6.7  | Speedup curves for base and optimized APSI benchmarks                     |

|------|---------------------------------------------------------------------------|

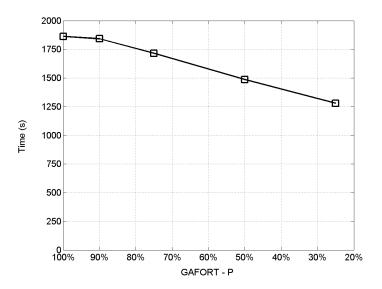

| 6.8  | GAFORT time versus probability $p$                                        |

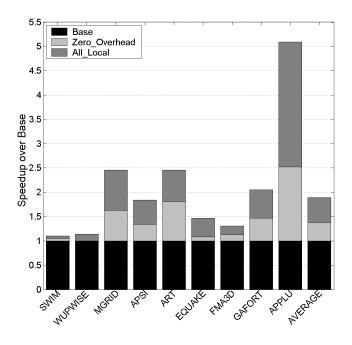

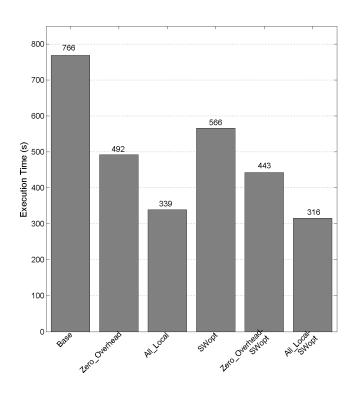

| 6.9  | SpecOMP2001 execution time for untuned and optimized benchmarks with      |

|      | base and ideal protocols                                                  |

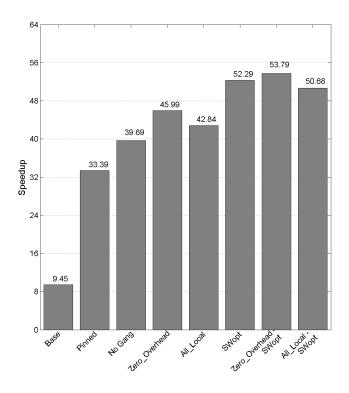

| 6.10 | SpecOMP2001 speedup for untuned and optimized benchmarks with base        |

|      | and ideal protocols                                                       |

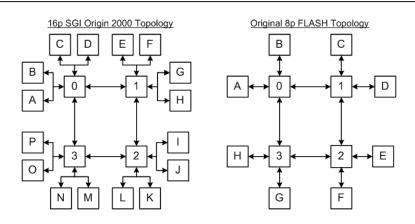

| A.1  | 16-Processor SGI Origin and original FLASH interconnection network topol- |

|      | ogy                                                                       |

| A.2  | 8-Processor FLASH interconnection network topology                        |

| A.3  | Internal connections in FLASH cluster router                              |

| A.4  | 16-Processor FLASH metacube                                               |

| A.5  | 64-Processor FLASH interconnection topology 132                           |

# Chapter 1

### Introduction

Parallel computing is a natural and old idea. The famous Illiac IV [9], developed in the late 1960s at the University of Illinois, is one of the earliest large parallel computers. This ambitious project ultimately took too long to design, cost too much to build and failed to deliver expected performance gains. In the intervening 40 years, large multiprocessors have continued to serve a specialized market for high-performance scientific or commercial applications for similar reasons.

In contrast, microprocessors have benefiting from dramatic advances in semiconductor technology and processor architecture, doubling in performance every one-and-a-half to two years. As a result, most people still use uniprocessor machines, based on the microprocessor. Pessimists have long predicted that Moore's Law will end sooner rather than later. Often, their dire predictions prove false because of the ingenuity of researchers and engineers who continue to develop novel fabrication techniques and processor architectures to improve microprocessor performance. In many ways, microprocessor performance growth has limited wider research and development of the general-purpose multiprocessor because there was no compelling performance reason to shift.

Lately, however, power constraints, longer on-chip wire delays, and limitations in instruction-level parallelism (ILP) are starting to limit microprocessor performance growth. Eventually fundamental physical communication limits and increasing power demands will limit our ability to improve microprocessor performance unless some fundamental paradigm shift occurs.

Parallel computing is one such paradigm shift. Once the microprocessor approaches

fundamental scaling limits, architects will leverage multiprocessors in an unprecedented way to continue performance trends. Already companies like Intel and AMD propose small-scale multiprocessor cores that leverage thread-level parallelism. Due to the programmer's heavy reliance on legacy software, the multiprocessor-programming model must remain as close to the uniprocessor-programming model as possible. In addition, programmers prefer efficient, yet *machine-independent*, program performance because the underlying multiprocessor architectures dramatically change as technology and machine sizes shift.

While small-scale cache-coherent multiprocessors are successful, many larger parallel machines abandon cache coherency. Somehow, the cache-coherent abstraction has failed to provide efficient, machine-independent performance with little programming effort at larger processor counts. The research and methodology presented in this dissertation seek to understand why programming large-scale multiprocessors remains difficult.

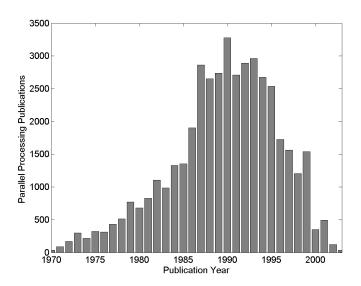

**Figure 1.1:** Multiprocessor and Distributed Computing Papers published between 1970 and 2004 [44]

The scarcity of useful large-scale shared-memory machines is not from a lack of effort by the architecture community. Figure 1.1 illustrates the rate of publications on multiprocessor and distributed computing papers from 1970 to today. Through the mid-1990s,

3

interest in parallel computing steadily increased because this area looked increasingly attractive. However, in the late 1990s, the community hit a research wall. Scarcer government funding, industry difficulties encountered in building and selling larger multiprocessor systems and a lack of new ideas from the architecture community contributed to the decline in parallel research.

Nor is the lack of these machines caused by the absence of parallelism in high-level applications. Parallelism frequently exists in these applications, but exposing this parallelism in software or extracting parallelism automatically in hardware proves challenging. The programmer, software interface, or parallel compiler fails to implement concise, machine-independent parallel algorithms. The hardware fails to provide a clear interface to the software or poorly extracts parallelism automatically.

### 1.1 Research Contributions

The primary contributions of this dissertation are:

- Measurements and analysis of performance and bottlenecks using a real large-scale

multiprocessor to measure and analyze performance. The FLASH system [35, 36]

was designed specifically to study design trade-offs present in large-scale multiprocessors. Using realistic multiprocessor provides a mechanism for studying a wider

range of application complexity and data set sizes than what is typically available via

simulation.

- Evaluation of operating system scheduling techniques to maximize system throughput when used in a high performance parallel processing context and a multi-user environment. This work illustrates that the traditional models of space-sharing and time-sharing fail to scale to larger processor counts, at least at a fine-grain level.

- Comprehensive analysis of complexity and performance trade-offs present in coherence protocol design for large-scale multiprocessors. This analysis consists of two parts: a practical study using coherence protocols implemented on the FLASH machine and a limit study using FLASH as an emulator to model ideal coherence protocols.

Evaluation of software bottlenecks in high-level applications. These optimizations

demonstrate that most of the performance bottlenecks present in high-level applications are well known problems with clear solutions in software—provided that the

programmer is aware of the presence and location of bottlenecks in their programs

and has significant understanding of the details of the architecture.

### 1.2 Organization of the Dissertation

To understand what types of problems limit the wider adoption of cache-coherency on large-scale multiprocessors, Chapter 2 explores scaling problems that led to the development of the shared-memory model and scaling problems encountered within high-level applications. The shared-memory model, developed in part to solve scaling issues encountered in earlier systems, and a variety of application-specific behaviors limit performance on these machines.

Naturally, we need to select a representative set of benchmarks that expose typical performance bottlenecks because often a trade-off exists between hardware and software solutions. Therefore, Chapter 3 discusses SpecOMP2001, a set of high-level applications that experience these application-specific effects, to provide a mechanism for exposing scaling problems. The next three chapters categorize why performance is lost at larger processor counts on the FLASH multiprocessor and explore potential solutions in hardware and software.

Unexpectedly, we encounter some bottlenecks related to the global scheduling of parallel programs and the virtualization of system resources provided by the operating system. Therefore, Chapter 4 investigates how the operating system influences—and in many cases degrades—performance at larger processor counts. Operating system-specific bottlenecks arise from multiprocessor scheduling policies that balance the needs of one parallel process against the throughput of the entire multiprocessor.

Perhaps we need only design a more efficient multiprocessor that exposes fewer pitfalls to the programmer. Chapter 5 explores how hardware architects have tried to do just this to reduce the challenge of efficient programming by increasing the memory system complexity. The FLASH multiprocessor was designed to provide an effective mechanism for analyzing efficient and scalable memory system design for building larger multiprocessors. We find through this chapter that practical limitations restrict our ability to solve performance bottlenecks in hardware on larger multiprocessor systems.

Therefore, Chapter 6 shifts focus to the high-level application's software to evaluate the effectiveness of applying machine-specific tuning that remove performance bottlenecks. Using hardware-assisted instrumentation, the chapter identifies performance bottlenecks and removes them. The critical bottleneck remains the programmer's ability to apply well known—but difficult to identify—optimizations.

The dissertation concludes in Chapter 7 with a discussion of the fundamental barriers to effectively programming larger cache-coherent shared-memory multiprocessors.

# Chapter 2

# **Evolving towards cc-NUMA Multiprocessors**

The cache-coherent non-uniform memory access (cc-NUMA) multiprocessor originally emerged as an attractive architecture because the programming model presented to the user remains similar to the uniprocessor-programming paradigm. Surprisingly, while small-scale systems show some of the intended benefits of shared-memory, larger systems do not. The cc-NUMA architecture evolved precisely to provide a scalable and efficient programming interface. Furthermore, the expected performance bottlenecks are well known, but not all arise directly through the choice of the cc-NUMA architecture.

The FLASH machine, proposed, built, and evaluated over a period of 10 years, provides a valuable test-bed for analyzing the performance of high-level applications on cc-NUMA multiprocessors. However, during the last decade, multiprocessor architectures have shifted away from cc-NUMA and towards clusters of symmetric multiprocessors (SMPs) or clusters of standalone PCs. Traditional large-scale multiprocessors like the SGI Origin 2000 [38] proved too difficult to efficiently program high-level applications to justify the multiprocessor's large cost.

This chapter fleshes this story out in more detail to understand why multiprocessors remain difficult to program. Understanding this problem remains critical, because future single-chip multiprocessors are likely to follow a similar evolutionary track towards multiprocessor. Today, the number of processors per chip is small, but future chips could approach the number of processors present in typical SMPs.

First, the chapter reestablishes the key advantages and design goals of the cc-NUMA architecture. Section 2.1 defines key characteristics of the multiprocessor programming model. Section 2.2 explores how the cc-NUMA architecture evolved from the uniprocessor and earlier multiprocessor architectures and describes how each step changed the programming model. Every multiprocessor architect makes design decisions to partition key performance responsibilities among the programmer, compiler and software tools, memory system architecture and network. During each step of the evolution, key responsibilities shift between the software and the hardware.

Section 2.3 presents a systemic description of performance bottlenecks encountered when writing programs for cc-NUMA machines. The programmer and compiler hold most of the optimization responsibilities for these machines. Therefore, this section provides a guide to most of the pitfalls programmers are likely to encounter when writing for high-performance.

The differentiating feature of the FLASH machine is the programmable memory controller called MAGIC. In most other machines, the memory controller is hard-wired. While the latency overheads for replacing a hard-wired memory controller with programmable one are small, there are some FLASH-specific performance bottlenecks that are discussed in Section 2.4.

### 2.1 Programming Model Design

Programmers use a *programming model* interface to write correct and efficient programs for a specific architecture. Initially, programmers develop correct programs, and then apply tuning to increase overall performance.

Choices in architecture design often create a trade-off between ease of programming and overall hardware performance. By shifting the burden of program optimization away from the hardware, the programmer or compiler writer must manage the additional complexity of the programming model. However, this shift may simplify the hardware design or yield greater overall performance. The rise of the RISC processor typifies this relationship: simplifying the hardware allows the processor to benefit from faster clock speeds and instruction pipelining. However, the complexity of writing efficient programs increases

because the assembly writer or compiler arranges instructions correctly to express a program's semantics and hide pipeline stalls.

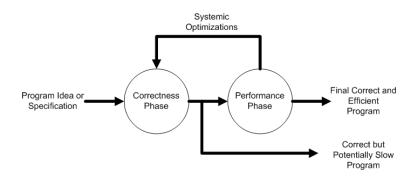

Figure 2.1: The programming design process

To simplify our understanding of writing programs, we divide the programming model into two design phases, illustrated in Figure 2.1. During the *correctness phase*, the programmer implements a new program idea, from a formal specification of a system, or an existing program written for another architecture using a programming language and the architecture's programming model. Once the programmer completes the correctness phase, the program precisely implements the original idea but potentially at suboptimal performance. Thereafter, the programmer enters the *performance phase* by applying optimizations that remove application-centric, architectural and application-created, and machine-dependent performance bottlenecks until the program achieves an acceptable level of performance. In the performance phase, the program's functionality does not change. The programmer may return to the correctness phase to remove high-level or systemic performance bottlenecks that require rewrites of major portions of the program.

The *memory consistency model* [20] portion of the programming model specifies the required relationship between load and store operations. Generally, programming under strong consistency is easier than under a weaker model because the programmer manages fewer memory ordering details. However, a strong consistency model requires the hardware to properly order memory operations.

The full complexity of performance phase depends on the final implementation details of the architecture. For example, a program running on a simple pipelined uniprocessor can leverage software pipelining to improve the performance of loops. However, correct program execution does not require software pipelining. The optimal sequence of machine instructions depends on the instruction delays and functional units in the final hardware implementation of the processor.

An critical performance factor discussed in later chapters is the proper organization of a program's instruction and data memory in a distributed memory system. Proper *memory placement* is critical because some memory layouts can lead to poor cache locality and long memory latencies. Assuming a single address space, the program will execute correctly, if slowly, independent of how efficiently a program uses the caches or where data is physically stored.

### 2.2 Evolution of Multiprocessor Architectures

This section describes the evolution from the simple uniprocessor to the large-scale cc-NUMA multiprocessor and the resulting changes in the programming model. These changes shift the responsibilities of the programmer, compiler, and architect and impact the complexity of expressing functionality and performing optimizations.

### 2.2.1 The Uniprocessor Programming Model

The uniprocessor programming model is simple and straightforward: instructions complete in sequence. The simple and logical flow of operations leads to the development of programming tools that allow higher-level statement execution. Therefore, we can write a high-level language (e.g. C, C++, FORTRAN, Perl, Python, etc.) and develop compilers or translators to understand the low-level programming model. Dividing the labor between the programmer and the compiler simplifies programming in the correctness phase. The programmer only encounters the programming model as seen through the high-level language.

While the underlying hardware might transparently reorder memory operations to hide latency, it must maintain the uniprocessor's *strict consistency* model: any read returns the value of the most recent write.

During the performance phase, the programmer need only understand a few architectural details. Often programmers optimize uniprocessor programs by simply activating aggressive compiler optimizations to implement techniques like loop unrolling or software

pipelining. Capturing simple spatial and temporal cache locality by properly organizing data frequently happens automatically. Assuming the OS does not place pages in a pathological way (i.e. poor page-coloring algorithm), a program benefits from caching regardless of where the OS places data in memory. Some programmers may use tools to perform simple optimizations that reduce memory conflicts and improve performance.

The fewer programming model details required by the programmer during the correctness and performance phases, the easier the programmer finds writing correct and efficient programs. Multiprocessor architectures hope to keep the programming model equivalent to the uniprocessor—where both the correctness and the performance phases require little architecture specific knowledge.

### 2.2.2 Small-scale Symmetric Multiprocessors

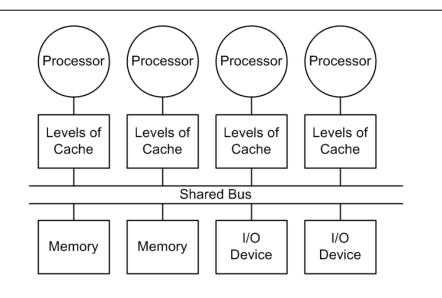

**Figure 2.2:** Symmetric multiprocessor architecture (SMP). Contention for the shared bus limits the effective size of this architecture

Uniprocessors naturally evolved into small-scale symmetric multiprocessors or *SMPs*. Additional processors and memories share information through a shared memory or a shared address space—in small-scale usually implemented with a coherent bus. Figure 2.2 illustrates a typical SMP configuration. The SMP, dubbed a *paracomputer* [53] in 1980,

predates more modern non-uniform memory access (*NUMA*) multiprocessors built during the early and mid-1990s. Modern SMPs include the Sun's Wildfire [14], Gemini Ultrasparc [31] and Niagara [34] processors.

The programmer has the additional responsibility of identifying parallel sections of the program and managing thread synchronization using a parallel program interface like ANL macros or OpenMP. This added interface increases the complexity of the correctness phase. Research projects such as the Stanford Hydra project [46] and parallel compilers such as Stanford's SUIF [4, 61] and SAPIENT, the University of Illinois at Urbana-Champaign's POLARIS [11] investigate ways of automatically discovering parallelism present in sequential programs. These tools simplify identifying and constructing parallel portions of the program but are not sophisticated enough to shield the programmer from understanding the parallel programming model.

To minimize the knowledge required by the programmer during the correctness phase, the hardware architect designs caches that snoop memory traffic broadcast across a shared bus to update their cache-line states. The *coherence protocol* specifies how to resolve data race conditions. This strategy keeps the correctness phase simple such that the programmer does not have to explicitly remove race conditions.

If multiple threads on each processor access the same memory location, memory operations broadcast on the shared bus provide *sequential consistency* [37]. Multiprocessor systems do not provide strict consistency because maintaining global timing proves too expensive. However, the sequential consistency model remains practically equivalent to the uniprocessor's strict consistency model. Thus, the programmer does not have to manage memory ordering during the correctness phase.

The performance phase is somewhat more complex than the uniprocessor's programming model. A program's memory accesses continue to benefit from temporal and spatial locality. An SMP's memory system provides a uniform memory access model (UMA); unloaded access time to each memory bank is identical. Therefore, the programmer does not have to manage memory placement beyond the effort required to tune uniprocessor programs. Communication among processes, however, leads to unavoidable cache misses, which are costly. The additional communication costs of shared cache misses are the key difference from the uniprocessor model.

Typically, SMPs use a broadcast model to communicate shared information between

processors. Every cache misses broadcasts across an interconnection network (typically a shared bus). In a system with few processors, network contention is usually negligible because the required bandwidth of the network to service cache misses is not high. However, as the number of processors increases both the length of the bus and the number of requests it must handle increase. Because the performance of a bus is inversely related to its length, eventually the required traffic exceeds the bus bandwidth, and some more complex interconnection network is needed.

#### 2.2.3 Message-Passing Multiprocessor

**Figure 2.3:** Message-passing multiprocessors scales well, but expressing communication proves difficult

To avoid contention present in broadcast models, architects turn to a distributed processor architecture where communication only occurs when explicitly requested by the processor. This architecture abandons cache coherence because broadcast operations are too expensive. The memory system no longer provides a shared address space between the processors. Each processor holds only a portion of the total system memory. If a processor needs to access remote data, it must send a message to the remote node. Hence, this architecture is called *message passing* because every node must explicitly communicate with another node using a message. Figure 2.3 illustrates a typical message passing architecture configuration.

Because each processor contains independent address spaces, message passing machines are often referred to as *multicomputers* or clusters. For these machines, the hardware effort shifts to creating a scalable, high-speed interconnection network. To minimize communication overheads, smaller messages are often aggregated into larger ones. The memory system provides low-overhead send and receive protocols and data buffers to support arbitrary message lengths. A message passing multiprocessor places a large burden on the programmer, because in the correctness phase any communication or data sharing must be explicitly programmed.

Once the program executes correctly, the programmer finds tracking where communication occurs easier in message passing than in an implied communication architecture (i.e. an SMP) because the inter-processor communication patterns are well documented in the code. Once understood, however, fixing bottlenecks often is more difficult. In the performance phase, the programmer must repartition data among processors to reduce communication latency and network contention and this may require restructuring of the code.

The scale of modern message-passing multiprocessors demonstrates that these machines can scale to large sizes. Many message-passing systems are built with thousands of nodes, notably the Earth Simulator [18, 47] with over 5000 nodes, currently third on the list of top 500 supercomputers in the world [59]. Universities and research laboratories routinely connect workstations using a fast network to build larger clusters. Other examples include ASC-Q in Los Alamos National Laboratory with 512 nodes and 16-processor SMPs [6] and Lawrence Livermore Laboratory's Thunder system connecting 4096 Intel Itanium 2 processors running Linux [58].

Consider the University of Texas's lonestar 1024-processor supercomputer. Each node in the multiprocessor is a 3.06GHz Intel Xeon processor connected together using a Dell-Cray network. This system is number 40 on the top 500 supercomputer list. They claim an overall performance of 6.34 Teraflops at peak performance, which is approximately the theoretical peak performance of 6.12 GFLOPS for each CPU multiplied by

1024. The actual performance of the LINPACK [17] benchmark, used to compare all of the top 500 supercomputers, only achieves 65% of the theoretical maximum, or 4.15 Teraflops. FLOPS only measures how quickly these computers process math operations. The programmer is lucky to get a similar parallel efficiency from this machine for any general-purpose application without applying significant programmer effort.

The contract between the software, the compiler, and the hardware has fundamentally changed. The hardware design ceases to be the major bottleneck to scaling. The main obstacle to efficient performance becomes the programming model.

### 2.2.4 Simple NUMA Multiprocessors

An alternative approach, the NUMA multiprocessor, arose roughly at the same time as the message passing multiprocessors. Initially these systems were built without cache-coherence, because cache-coherence traffic on the shared bus was the barrier to scaling SMPs to arbitrary sizes. In such simple NUMA architectures, any processor can address and thereby access any of the memory distributed throughout the system. Non-shared remote loads and stores complete by accessing memory across the interconnection network and benefit from caching. Shared accesses maintain coherence by synchronizing at the memory banks, but shared data is never cached.

The correctness phase on this architecture is equivalent to the small-scale bus-based systems. The user does not have explicitly express communication or handle communication race conditions in shared portions of the program. However, the programmer must correctly identify all of a program's shared data segments.

The complexity of the performance phase requires more effort than SMPs because the memory system is effectively partitioned between shared and non-shared data. Because shared data remains uncached, the programmer must minimize sharing in a process similar to message-passing architectures in which communication occurs explicitly. Otherwise, the application's memory accesses do not benefit from caching at all. Experiences with the Cray T3D and T3E machines and DASH [39], a cache-coherent NUMA multiprocessor, suggest that effectively programming shared memory machines requires caching shared memory [28, 54]

### 2.2.5 cc-NUMA Multiprocessors

The natural extension of the simple-NUMA architecture is to allow the caching of shared data. This approach, called cache-coherence NUMA or cc-NUMA, allows the caching of data regardless of its sharing patterns through the use of a directory that holds cache-line state in memory (or in the cache line itself) and a coherence protocol. This architecture retains the simple shared-memory model present in the smaller-scale symmetric multiprocessors. Examples of this architecture include the Stanford DASH and FLASH machines, the SGI Origin 2000 and Origin 3800, the Sun Fire 15K, and the HP Superdome.

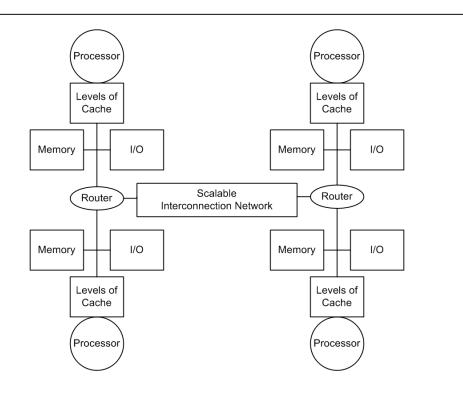

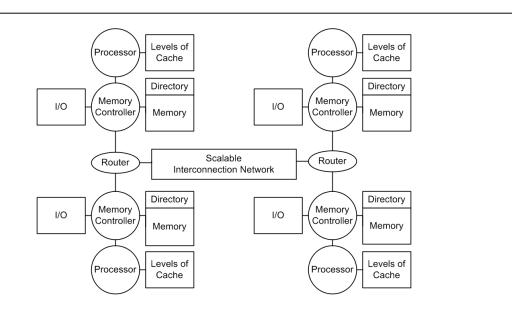

Figure 2.4: cc-NUMA Architecture. Design effort shifts to building a cache coherence protocol

Figure 2.4 illustrates a typical layout for a cc-NUMA machine. The memory controller arbitrates access to local memory between the local processor and remote requesters. The memory controller implements the coherence protocol to address communication races. Coherence operations are no longer broadcast across a shared bus, therefore cache interventions and invalidations—which on smaller systems would be handled by the caches snooping the bus and invalidating data automatically—are sent as coherence messages across the network.

The architect's responsibility is to design a memory controller that implements an efficient, scalable coherence protocol to service cache misses quickly. Most industrial multiprocessors have a hard-wired memory controller [38]. The FLASH multiprocessor uses an efficient custom-built protocol processor. Alternatives include the University of Wisconsin's Typhoon project [51], which replaced the memory controller with a commodity processor. The MIT Alewife [3] machine used a combination of custom logic and software traps to the processor.

Like the simple NUMA multiprocessor, the correctness phase of a cc-NUMA multiprocessor is similar to the SMP's correctness phase. Presumably in cc-NUMA architectures, the programmer manages fewer shared-memory details in the performance phase compared to simple NUMA. Shared and unshared data behave in identical ways and benefit from caching, therefore partitioning the memory space between shared and unshared is unnecessary. However, the true complexity of the cc-NUMA's performance phase remains unclear especially for larger processor counts. This dissertation explores exactly this question.

### 2.2.6 Summary

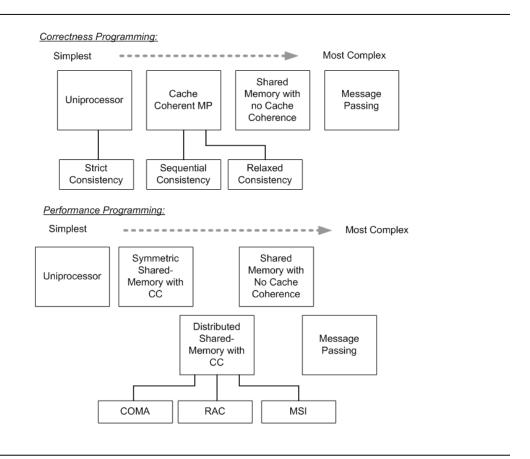

Figure 2.5 illustrates the relationship between multiprocessor architectures discussed in this section. The uniprocessor and message passing architectures form the ends of the functional and performance programming complexity spectrum. For some applications, architectures share similar performance complexities despite different programming models. While the programming models of simple NUMA and message passing differ dramatically, programmers must partition their data between shared and unshared portions for both. This effect is illustrated in the figure by overlapping boxes.

At large scale, can more aggressive coherence protocols that leverage remote caching deliver a simpler programming model? Alternatively, are architects forced to keep the memory system simpler for performance reasons? Understanding the trade-off between programming model and overall multiprocessor performance motivates the remainder of this dissertation.

Figure 2.5: Complexity of functional and performance programming

## 2.3 Performance Bottlenecks Present in cc-NUMA Multiprocessors

The answer to the questions posed at the end of the previous section depends on which performance bottlenecks the programmer encounters when writing applications for cc-NUMA architectures. This section details most of the common pitfalls encountered when writing applications for shared memory. Performance bottlenecks fall into three general categories. Section 2.3.1 discusses architecture-independent bottlenecks created by the programmer when writing the application. Some bottlenecks form because of interactions between the application and the architecture. Section 2.3.2 presents those bottlenecks. Finally, bottlenecks arising due to particular machine parameters are discussed in Section 2.3.3.

#### 2.3.1 Application-Centric Bottlenecks

Application-centric bottlenecks are bottlenecks the application would experience regardless of which architecture the application ran on, although, the precise impact of the bottleneck would vary from machine to machine due to processor speeds, memory sizes, and other machine-specific characteristics.

Removing or minimizing application-centric bottlenecks requires the programmer to apply high-level algorithm changes. Modern compilers apply peep-hole optimizations well, because the amount of information required is small. However, they are generally unable to make high-level algorithm changes because they lack enough global information to apply these complex parallel algorithm transformations.

Insufficient parallelism, Amdahl's Law for multiprocessors, is the most obvious example of this type of bottleneck. Most applications have some serial algorithm overhead or contain some code with too many dependencies to benefit from parallelism. By choosing and implementing a specific algorithm, the programmer implicitly limits the potential speedups present in the application. Clearly, data set size impacts the relative sizes of the serial and parallel sections of the application. Often increasing the data set size increases the size of the parallel section and thereby improves the available parallelism.

Improving the memory system's response time to memory requests reduces observed communication latency. Clearly communication affects speedup, but in the ideal the communication-to-computation ratio is programmer-determined because any parallel algorithm must communicate some information. The degree of ideal communication—the required minimum number of words to transmit between threads—determines the application-specific communication costs.

Less common application-centric bottlenecks arise from programming mistakes made in the parallel section that either cause excessive I/O traffic or OS system calls or traps. For example, on some operating systems each thread simultaneously calling malloc causes contention for kernel locks for virtual memory data.

#### 2.3.2 Architecture and Application-Created Bottlenecks

This section presents bottlenecks created by interactions between the architecture and the application. These bottlenecks exist, to an extent, on all multiprocessors. However, the relative impacts of these bottlenecks depend on the cost of operations in the implementation.

#### **Excessive Thread Synchronization**

A parallel program may include multiple parallel threads that must coordinate with one another in a prescribed manner. However, race conditions between threads often create unintended and incorrect behavior. Thread synchronization mechanisms eliminate race conditions between parallel sections or access to shared data.

Frequent global barriers cause a problem if the cost of the barrier is high or if the execution times for parallel sections vary widely across threads. Any parallel thread must wait for all threads to arrive at the barrier. Therefore, all threads experience the worst-case execution time of any threads to the barrier. Most applications require barriers due to the presence of race-conditions between parallel sections, called *parallel-section dependencies*. If all the barriers are necessary for correctness, the programmer can only decrease number of barriers by changing the application.

Using a high-level parallel-programming interface like OpenMP often introduces implied barriers between every parallel section. The programmer can ignore these parallel-section dependencies. An intelligent compiler might be smart enough to identify and remove unnecessary barriers by checking for parallel-section dependences. However, the compiler has difficulty doing this type of high-level analysis because often the parallel sections reside in different procedures or are complex code segments in their own right.

The memory system could potentially resolve barrier waits as well by allowing execution of threads to continue beyond barriers and faulting or restarting in a stricter mode if a parallel-section dependence violation occurs [49]. More commonly, the memory system implements some hardware-assisted barrier mechanism such as fetch-and-op [23].

Unnecessary locking can also degrade parallel performance. Contention for locks causes parallel threads to execute serially. As the thread count increases, more serialization between threads occurs because the likelihood of lock contention increases. The memory system impacts this bottleneck because slow lock acquisition and release mechanisms could make the bottleneck worse.

However, hardware overheads are often trivial compared to the size of unnecessarily long critical sections. Clearly, the programmer could resolve the situation in software by shortening the critical section. An intelligent compiler might identify the smallest possible critical section required, using the programmer's lock acquisition and release code as a guide. The memory system could use a fault model similar to the barrier technique, which would work normally but this solution would only solve the problem if lock contention occurred infrequently.

#### **Operating Systems Bottlenecks**

The operating system virtualizes the hardware to provide all processes with an identical view of system resources. Most bottlenecks created by the OS design involve how virtualization overheads are exposed to the user.

Any uniprocessor OS schedules and deschedules threads to allow many processes share one processor. On a multiprocessor, the thread scheduler considers more variables when making decisions. As machine sizes scale and the underlying architecture shifts, the scheduler takes longer to decide. On a symmetric shared-memory multiprocessor, the scheduler's decision is easy because the cost of thread migration is small. However, on a cc-NUMA architecture, the scheduler must be more careful because the proper thread placement depends not only on the available processing elements, but also the size and location of a thread's data.

There are also bottlenecks associated with multiprocessor scheduling policies that allow multiple parallel programs to share portions of the machine in space and time. These bottlenecks increase an application's exposure to thread scheduling overheads and context switches if the multiprocessor scheduling policies create unnecessary thread interrupts. Also, scheduling policies can disrupt an application's data locality if threads migrate far away from their data. *Negative thread migration* significantly degrades memory system performance.

#### **Communication-To-Computation Ratio Changes**

The bottlenecks presented in this section are well known to multiprocessor architects. As an application scales to higher processor counts, the communication patterns for an application can shift. The cost of this type of application-centric bottleneck is determined by the use

of an architecture—a good example is a distributed address space (architecture visible) that affects the communication.

As an application runs on larger processor counts, the size of available cache increases. This cache aggregation effect causes the number of cache misses to decrease. Therefore, the performance of the parallel application improves significantly. While this effect is not a true bottleneck, cache aggregation can hide other bottlenecks by artificially inflating the observer performance. Thus, cache aggregation hides the true performance of the memory system from the programmer.

Alternatively, extra communication degrades the overall performance of the application. This communication arises from the overheads required for a specific algorithm choice. Most parallel sections introduce some per-thread communication overheads to set up the parallel algorithm or initialize temporary data.

A higher communication-to-computation ratio creates an effect similar to insufficient parallelism. The algorithm fails to scale because extra communication causes the parallel sections to run longer. Each parallel thread is doing more work at larger processor counts than at smaller processor counts. In most cases, the programmer must eliminate this extra communication by changing the algorithm or increasing the problem size. The compiler and the architecture can only mitigate the cost of remote communication because each cannot remove necessary communication.

#### **Communication Hot Spots**

Communication hot spots arise in parallel programs when frequently accessed data falls on the same node. Node-level false sharing is a special case of more general communication hot spots discussed later in this section. A small subset of the program's data can lead to contention on a single node.

Perhaps the program appropriately distributes pages among the parallel threads. Additional bottlenecks arise by the OS placing data on the page-level granularity. The local processor accesses most of a page, but a remote processor exclusively uses an unused portion. The remote requester must transmit across the network to retrieve the data, but it is the only requester for that portion of the page.

As processor counts increase, each thread in the parallel program accesses a smaller portion of the total memory required by the algorithm. Therefore, remote misses increase with processor count. This effect behaves in an identical fashion as increasing communication-to-computation ratio, but differs in that it is caused by page placement decisions made by the OS.

#### 2.3.3 Machine Dependent Bottlenecks

Performance bottlenecks arise because of implementation choices made by the architects of a specific machine. In most cases, the programmer must be aware of these machine-specific problems when programming applications for performance. These coherence effects determine the difference between the ideal communication costs and the real observed memory latency. This section describes performance bottlenecks that are specific to the shared-memory model.

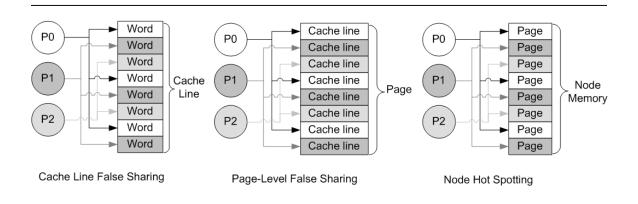

The memory system organizes memory into fixed-size hierarchical blocks to take advantage of temporal locality present in memory accesses and to reduce the complexity of memory management operations in software. Because data is aggregated into blocks, extra communication arises when multiple processors share resources in a block but do not actually unnecessarily exchange data. This *false-sharing* can occur at multiple levels in the memory hierarchy including the cache-line, a page, or even a node's memory.

Cache-line false sharing arises when multiple nodes exchange a cache line between them but access mutually disjoint sets of data words. Thus, this communication is unnecessary and expensive. This bottleneck is well known to architects and programmers alike. If cache line false sharing is systemic, an application will fail to scale well even at small processor counts. The number of nodes falsely sharing the cache line is bounded by the total words per cache line.

False sharing also occurs on a page or a node basis. Figure 2.6 illustrates three processors falsely sharing a cache line, a page, and node's memory. These bottlenecks share the same underlying property—processors falsely sharing a resource. However, each false-sharing bottleneck arises for different structural reasons in the program.

Page-level false sharing is less obvious to the programmer because the effect is often negligible on smaller machine sizes. The OS places data in memory on a page-level granularity. Page-level false sharing occurs when many nodes access the same page, but each

**Figure 2.6:** General false sharing types

node accesses disjoint sets of cache lines in the page. The total cache lines per page bound the number of nodes that could falsely share a page. The cost of page-level false sharing is bounded by the network latency to access the data on the page's home. However, at larger processor counts, contention arises as the accesses for the shared page contend with one another. This contention introduces queuing delay accessing the page's memory bank as processor counts scale.

Typically, page-level false sharing occurs on pages that hold thread-private data. The programmer solves the problem by separating unshared data into separate pages or segments. This process is similar to partitioning data between shared and unshared data in a simple NUMA machine. The potential requesters for a page scale with processor count. Therefore, on small-scale cc-NUMA machines, the programmer ignores this bottleneck because the potential requesters for a page remain small, contention is negligible, and applications benefit from the positive aspects of spatial locality.

Node-level false sharing occurs even if nodes access a disjoint set of pages on the same node. Contention occurs at larger processor counts where requests wait in the network buffer or the input request queues on the memory controller but access separate local memory banks. Frequently, this bottleneck arises from the master thread initializing and placing data before spawning parallel threads. This data placement causes all of the threads to access their data on the master node creating a large communication hot spot. This bottleneck arises from the programmer ignoring the distributed memory model and placing pages indiscriminately.

25

The compiler finds automatically removing false-sharing bottlenecks automatically difficult. The location of the bottlenecks in memory depends on the input set size, choice of parallel algorithm, and OS placement decisions. Either the programmer must find the bottlenecks and remove them by reorganizing data layout in software, or the memory system must adapt to migrate data closer to requesters. Two techniques discussed in Chapter 5, RAC and COMA, propose using remote request caching to mitigate these bottlenecks.

## 2.4 The FLASH Multiprocessor

Like any multiprocessor, the FLASH multiprocessor introduces machine-specific bottlenecks that impact performance. However, FLASH's architecture is unique in two important ways. First, the use of a flexible node controller provides a mechanism for identifying and quantifying performance bottlenecks. Second, the FLASH machine introduces machinedependent bottlenecks that are not present in a typical cc-NUMA multiprocessor.

As mentioned earlier, many shared-memory multiprocessor architects propose removing bottlenecks presented in the previous section in hardware. The side effects of their proposals are primarily memory system complexity required to implement more aggressive techniques. Most researchers use simulation to evaluate the impact of these more complex proposals. Assessing the true costs and advantages of these proposals proves difficult for high-level applications with large data sets and long execution time because there are many opportunities for simulation error [22] and because simulation times are very long. Analytical modeling is not much easier because low-level implementation details must be accurate to produce meaningful results [56]. Fortunately, the FLASH multiprocessor provides a mechanism for exploring these designs in more detail using the same underlying hardware.

This study uses the FLASH multiprocessor [36] designed, built and evaluated over the last decade. FLASH is a 64-processor cc-NUMA machine with a programmable memory controller called MAGIC that runs software code sequences (*protocol handlers*) to implement the cache coherence protocol. The operating system is a modified version of SGI's IRIX6.5, which uses first-touch page placement. FLASH is binary-compatible with SGI's Origin 2000 [38]. Each node has a 225MHz R10k processor with 224 MB of

| FLASH       | SGI Origin 2000                                           | SGI Origin 3800                                                                                                                             |

|-------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1997        | 1997                                                      | 2002                                                                                                                                        |

| 225MHz      | 195MHz                                                    | 400 MHz                                                                                                                                     |

| 256MB       | 256MB                                                     | 2GB                                                                                                                                         |

| 2MB         | 2MB                                                       | 8MB                                                                                                                                         |

| 128 bytes   | 128 bytes                                                 | 128 bytes                                                                                                                                   |

| 135 cycles  | 100 cycles                                                | 184 cycles                                                                                                                                  |

| Double Mesh | Bristled Hypercube                                        | Dual Fat-Tree                                                                                                                               |

|             | 1997<br>225MHz<br>256MB<br>2MB<br>128 bytes<br>135 cycles | 1997     1997       225MHz     195MHz       256MB     256MB       2MB     2MB       128 bytes     128 bytes       135 cycles     100 cycles |

**Table 2.1:** Key Architecture Parameters for FLASH versus the SGI Origin 2000 and 3800

addressable main memory (32 MB are reserved for protocol data and directory memory overhead).

Table 2.1 summarizes key architecture parameters for the FLASH machines and compares them to the SGI Origin 2000 and 3800 [27]. A local L2 cache read miss takes 100 processor cycles on the 195MHz SGI Origin with a 100MHz HUB memory controller and 135 processor cycles on 225MHz FLASH with a 75MHz MAGIC. Remote latencies differ slightly because our network topology differs from Origin's hyper-cube. Point-to-point remote latencies are at most four times longer than local latencies.

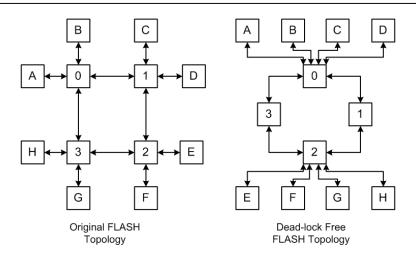

FLASH's network topology differs from the original proposal in [35]. These differences arose because the original network was not deadlock-free. Appendix A describes the required network topology changes in more detail.

FLASH's network is fast enough that network congestion can be ignored as a performance bottleneck. Each link provides a bandwidth of 800MB/s. In order to saturate the network, a processor needs a sustained rate of 6.55 million remote cache misses per second or one L2 remote cache miss every 152ns or 36 processor cycles. Even in the best case, it is impossible for the R10k processor to generate this request rate because even local L2 cache misses that are serviced locally take 600ns. The R10k processor allows four outstanding requests. One local miss could be generated every 150ns. After four outstanding remote misses, the processor would stall decreasing the network bandwidth requirements. Perhaps a single link multiplexing requests from multiple nodes and virtual channels would approach the bandwidth limit for a brief period of time, but in practice this network congestion only occurs because of some higher-level behavior caused by coherence protocol traffic or a communication hot spot.

2.5. SUMMARY 27

#### 2.4.1 FLASH-specific Performance Bottlenecks

FLASH's programmable memory controller provides us with information from a real machine that normally is available only via simulation or analytic analysis. The use of MAGIC for instrumentation has only a minor impact on overall memory latency [21].

The critical difference between MAGIC and a hard-wired memory controller is the use of embedded handlers executing on the protocol processor that implement the coherence protocols on FLASH. These handlers benefit from on-chip direct-mapped 16KB instruction cache and a 1MB direct-mapped off-chip data cache that reduce the protocol processor's memory access time. The flexible processor introduces two types of additional overheads: longer access times and caching behavior of the coherence protocol's handlers.

The data caching behavior of handlers does not significantly impact performance because both a hard-wired and an embedded processor implementation benefit equally from data caching. Each handler operates on a small amount data, typically the 64-bit address, the message header, and the directory entry. The stack is small, a few kilobytes is sufficient because most handlers have short call depths. The data cache does not have to be large to be effective because if frequent cache reuse occurs, as in false-sharing for example, other bottlenecks degrade performance. More likely, data cache reuse is infrequent because memory accesses are randomly distributed.

However, the performance of coherence protocols on MAGIC depends greatly on the number of instruction cache misses, which represent extra delay that is absent in a hard-wired solution. MAGIC can capture some concurrency present in a hard-wired solution of handlers. The 2-way VLIW processor pipelines instructions and additional hardware performs pre- and post-processing operations of a handler simultaneously. Nevertheless, protocol handlers must be kept short to avoid conflict misses. The direct-mapped 16KB instruction cache is too small to implement arbitrarily long handlers.

## 2.5 Summary

Future machines will encounter identical scaling trends as the traditional multiprocessor. Single-chip multiprocessors are in fact at the beginning using small clusters of symmetric multiprocessors to build larger systems. Eventually, single-chip cc-NUMA machines will encounter similar scaling issues. This chapter details how the cc-NUMA model developed

to make functional programming easy. An open issue remains understanding how difficult are cc-NUMA machines are to performance program. While the bottlenecks are understood, the remainder of the dissertation uses high-level applications written for shared-memory to evaluate which of these performance bottlenecks proves the largest stumbling block to efficient performance at larger processor counts.

# **Chapter 3**

# **Parallel Benchmarks**

To this point, we have not defined what we mean by a "high-level application". Ultimately, selecting a benchmark set influences the results and central conclusions. This chapter describes why we focus attention on the SpecOMP2001 [62] benchmark suite, rather than the SPLASH-2 [62] benchmarks traditionally used in FLASH research, to represent high-level applications in later chapters.

Most users of larger multiprocessors are not primarily computer scientists or experienced software programmers. Instead, they are physicists, chemists, engineers or biologists who develop scientific applications to model systems relevant to their primary field of interest. They may have only a vague understanding that inter-node communication must be managed—the shared-memory model hides the explicit details of inter-node communication to keep functional programming simple. Computer architects should not require that users have earned an advanced degree in parallel architecture to write high-performance programs.

The multiprocessor programmer lacks a capable agent to apply machine-specific optimizations for them automatically. On a uniprocessor, a programmer relies heavily on the compiler to apply appropriate processor-specific optimizations. Even programmers who have detailed knowledge of a uniprocessor's architecture rarely write more efficient code in assembly language. A novice uniprocessor programmer can cede performance programming to the compiler and achieve most of the potential performance of hand-tuned assembly. Parallel compilers have failed to succeed in an equivalent way at larger processor counts.

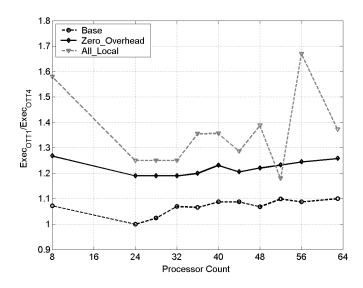

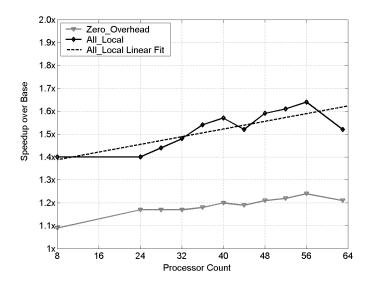

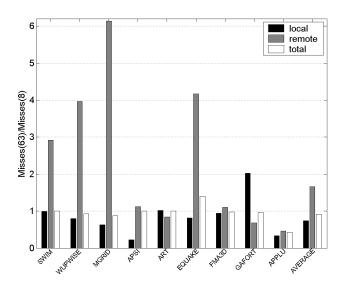

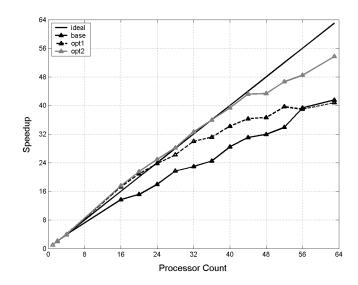

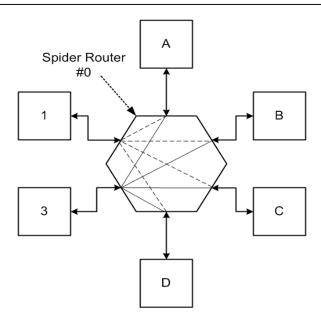

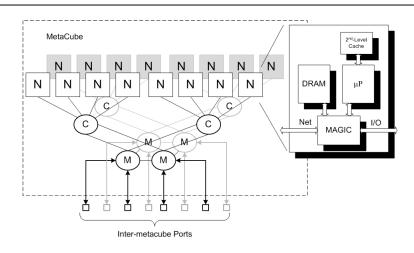

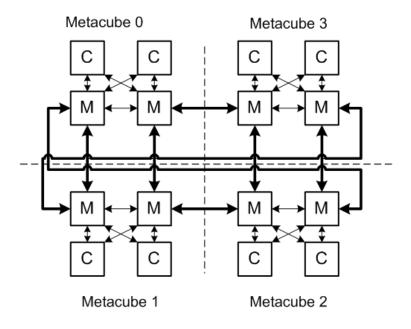

However, choosing a completely untuned benchmark suite is dangerous because a multiprocessor that is completely tolerant of programmer error would be impossible with these applications. No such machine would scale well. Thus we propose a middle ground in which the benchmarks have been optimized for the general architecture (e.g. shared-memory) without machine-specific optimizations. Some benchmarks will not be considered because they are either too optimized to the FLASH architecture or not optimized enough to the shared-memory model.