# HDL Coder Modeling Guidelines (R2015b)

# 0. Introduction

# 0.1 About this guide

This is a set of recommended guidelines for creating Simulink models, MATLAB function blocks, and Stateflow charts for use with HDL Coder. Because HDL Coder generates code that will target hardware, some amount of hardware architectural guidance must be provided as part of the design. There are additional guidelines for optimizing the speed and area of the design implemented in hardware. Where noted, the guidelines also reflect industry-standard HDL guidelines such as those from STARC.

# 0.1 Recommended HDL Coder design workflow

|                                    |    | •                                               |                                                                                                                                                                                                                                                                  |

|------------------------------------|----|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MATLAB /<br>Simulink               | 1. | Reference model<br>design                       | Design and verify the floating-point functional algorithm.                                                                                                                                                                                                       |

|                                    | 2. | Implementation<br>model creation                | Add hardware awareness, being mindful of clocking, data types, resource mapping. Use <u>HDL-supported blocks</u> . Typically Simulink is the top-level and primary entry point for this model, though MATLAB function blocks and Stateflow charts may be needed. |

| Fixed-Point<br>Designer            | 3. | Fixed-point conversion                          | Convert floating point data to fixed-point for hardware<br>implementation. Fixed-Point Designer utilizes simulation to<br>provide feedback and guidance on error tolerance and<br>min/max values.                                                                |

| HDL Coder                          | 4. | HDL generation<br>properties and<br>preferences | Set optimization preferences such as pipelining or resource sharing.                                                                                                                                                                                             |

|                                    | 5. | HDL generation<br>readiness check               | Checks the model for compliance and consistency with HDL code generation rules.                                                                                                                                                                                  |

|                                    | 6. | HDL generation                                  | Generates VHDL or Verilog.                                                                                                                                                                                                                                       |

| HDL Verifier +<br>EDA verification | 7. | HDL simulation and verification                 | Validate that the fully-timed bit-accurate HDL still meets functional requirements.                                                                                                                                                                              |

| EDA synthesis<br>and place & route | 8. | FPGA/ASIC implementation                        | Implement the generated HDL on the target hardware.                                                                                                                                                                                                              |

# 0.2 Target language

HDL Coder generates synthesizable VHDL or Verilog. VHDL is the default. The target language can be set a number of different ways, the most common being <u>Simulink Configuration Parameters > HDL Code Generation pane</u> or the <u>Simulink HDL Workflow Advisor</u> as follows:

#### 0.3 Definition of terms

Subsystems: <u>Atomic subsystem</u> <u>Variant subsystem</u> <u>Enabled Subsystem</u> <u>Triggered Subsystem</u> <u>Virtual subsystem</u>

Design concepts: <u>Base rate</u> <u>DUT</u> <u>Registers/Flip-Flops</u> <u>Global reset type</u> <u>Local reset</u>

Signals: Matrix signal Bus signal Vector signal Frame-based signal

Models: Model Variant Model referencing Validation model Generated Model Cosimulation model HDL model parameters HDL block properties HDL-supported blocks Configuration parameter

Implementation: <u>Floating-point to fixed-point conversion</u> <u>Floating-point mapping</u> <u>Sharing</u> <u>Streaming</u> <u>Pipelining</u> <u>DSP</u> <u>slice/block</u>

### 0.4 Guideline categories

The guidelines are categorized by level of compliance requirements:

|            | Mandatory                                                                              | Strongly Recommended                                                                                                              | Recommended                                                     | Informative                                        |

|------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|

| Definition | Not following this rule<br>will result in an error<br>and code cannot be<br>generated. | Code can be generated<br>but it will likely map<br>inefficiently to hardware<br>or may not match the<br>high-level functionality. | Improves quality,<br>readability, or ease of<br>implementation. | Guideline to provide<br>additional<br>information. |

| Impact     | Code generation or<br>logic synthesis cannot<br>be performed.                          | Poor quality of results                                                                                                           | May impact efficiency<br>or ease-of-use<br>downstream.          | None                                               |

# Index of HDL Coder Modeling Guidelines

| ID                                               | Title                                                                                                                            | Level                   | Hardware | STARC<br>ref |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|--------------|

| <u>1.</u>                                        | Architecture Design                                                                                                              | •                       | •        |              |

| <u>1.1</u>                                       | Basic settings                                                                                                                   |                         |          |              |

| <u>1.1.1</u>                                     | Appropriate use of Simulink, Stateflow, MATLAB Function,<br>BlackBox, Model Reference and HDL Cosimulation block                 | Informative             | All      |              |

| <u>1.1.2</u>                                     | Use the hdlsetup command to set model configuration parameters and HDL model properties                                          | Recommended             | All      |              |

| 1.1.3                                            | Avoid using double-byte characters                                                                                               | Mandatory               | All      |              |

| 1.1.4                                            | Consider resource sharing impact during model creation                                                                           | Recommended             | All      |              |

| <u>1.1.5</u>                                     | Document block name, block features, authors, etc., in subsystem block properties                                                | Recommended             | All      |              |

| <u>1.1.6</u>                                     | DIOCKS                                                                                                                           |                         | All      |              |

| 1.1.7                                            | Proper usage of commenting out blocks                                                                                            | Mandatory               | All      |              |

| Adjust sizes of constant and gain blocks so that |                                                                                                                                  | Recommended             | All      |              |

| 1.1.9                                            |                                                                                                                                  |                         | All      |              |

| <u>1.1.10</u>                                    | set_param                                                                                                                        |                         | All      |              |

| 1.2                                              | Subsystem and Model Hierarchy                                                                                                    | ·                       | •        | •            |

| <u>1.2.1</u>                                     | When the DUT is not at the top level of the model, set the DUT as a non-virtual subsystem                                        | Strongly<br>Recommended | All      |              |

| 1.2.2                                            | Type of subsystem and hierarchical design for a DUT                                                                              | Recommended             | All      |              |

| 1.2.3                                            | Do not connect constant blocks to ports directly crossing subsystem boundaries                                                   | Recommended             | ASIC     | 1.1.4.6      |

| <u>1.2.4</u>                                     | For testbenches that use blocks in continuous solver                                                                             |                         | All      |              |

| 1.2.5                                            | Generate re-usable HDL code from identical subsystems                                                                            | Recommended             | All      |              |

| 1.2.6                                            | Generate parameterized HDL code for gain and constant blocks                                                                     | Recommended             | All      |              |

| 1.2.7                                            | Insert handwritten code for a block into the generated code for the DUT                                                          | Mandatory               | All      |              |

| <u>1.2.8</u>                                     | Only use numerical values and string data types for mask<br>parameters for user-defined subsystems                               | Strongly<br>Recommended | All      |              |

| <u>1.3</u><br><u>1.3.1</u>                       | Signal types<br>Serialize 2D matrix signals into a 1D signal before it enters<br>an HDL subsystem, and vice versa for the output | Mandatory               | All      |              |

| 1.3.2                                            | Using a signal bus to improve readability                                                                                        | Recommended             | All      |              |

| 1.3.3                                            | Design considerations for vector signals                                                                                         | Strongly<br>Recommended | All      |              |

| <u>1.3.4</u>                                     | One-dimensional vectors created by Delay, Mux, and<br>Constant blocks generate HDL with ascending bit order                      | Informative             | All      | 2.1.6.1      |

| 1.3.5                                            | Manually write HDL control logic for bidirectional ports                                                                         | Mandatory               | All      |              |

| 1.4                                              | Clock and Reset                                                                                                                  | . ,                     | 1        | 1            |

| 1.4.1                                            | Creating a frequency-divided clock from the Simulink model's base sample rate                                                    | Informative             | All      |              |

| <u>1.4.2</u>                                     | Use master-clock division or a clock multiple for proper multi-rate modeling                                                     | Mandatory               | All      |              |

| <u>1.4.3</u>                                     | Use Dual Rate Dual Port RAM for non-integer multiple sample times in a multi-rate model                                          | Mandatory               | All      |              |

| <u>1.4.4</u>  | Use global reset type best suited for your target hardware                                                                               | Strongly<br>Recommended | FPGA<br>(Altera/Xilinx) |         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|---------|

| <u>2.</u>     | Block Settings                                                                                                                           |                         | •                       |         |

| 2.1           | Discontinuities                                                                                                                          |                         |                         |         |

| <u>2.2</u>    | Discrete                                                                                                                                 |                         |                         |         |

| <u>2.2.1</u>  | Appropriate use of various types of delay blocks as registers                                                                            | Recommended             | All                     | 1.3.1.3 |

| 2.2.2         | Map large delays to FPGA block RAM instead of registers to reduce area                                                                   | Recommended             | FPGA<br>(Altera/Xilinx) |         |

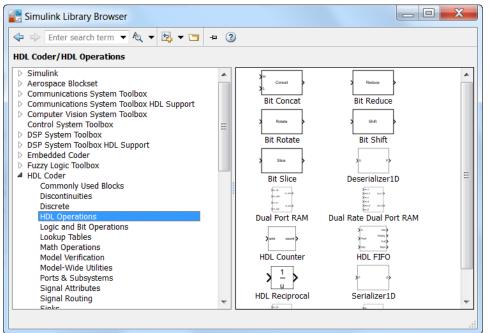

| 2.3           | HDL Operations                                                                                                                           |                         | ()                      |         |

| 2.3.1         | Use a Bit Concat block instead of a Mux block for bit concatenation in VHDL                                                              | Mandatory               | All                     | 2.1.6.1 |

| 2.3.2         | Design considerations for RAM Block access                                                                                               | Mandatory               | All                     |         |

| 2.3.3         | HDL FIFO block usage considerations                                                                                                      | Mandatory               | All                     |         |

| 2.3.4         | Parallel <> Serial conversion                                                                                                            | Informative             | All                     |         |

| 2.4           | Logic and bit operations                                                                                                                 |                         |                         |         |

| 2.4.1         | Logical vs. arithmetic bit shift operations                                                                                              | Informative             | All                     |         |

| 2.4.2         | Logical Operator, Bitwise Operator, and Bit Reduce for<br>logic operations                                                               | Informative             | All                     |         |

| <u>2.4.3</u>  | Use Boolean data type for the output of the Compare to<br>Constant/Zero and the Relational Operator blocks                               | Strongly<br>Recommended | All                     |         |

| 2.5           | Lookup tables                                                                                                                            |                         |                         |         |

| <u>2.5.1</u>  | Set the number of Lookup Table data entries to a power of 2 to avoid generation of a division operator (/)                               | Strongly<br>Recommended | All                     |         |

| <u>2.5.2</u>  | Generating FPGA block RAM from a Lookup Table block                                                                                      | Strongly<br>Recommended | FPGA<br>(Altera/Xilinx) |         |

| 2.6           | Math operations                                                                                                                          |                         |                         |         |

| <u>2.6.1</u>  | Input vector with Mux block to multi-input adder, multi-<br>input product, and multi-input Min/Max                                       | Strongly<br>Recommended | All                     |         |

| <u>2.6.2</u>  | Set ConstMultiplierOptimization to 'auto' for a Gain block                                                                               | Strongly<br>Recommended | All                     |         |

| <u>2.6.3</u>  | Use the Bit Shift block or the bitshift function for computations of the power of 2 (ASIC)                                               | Recommended             | ASIC                    |         |

| 2.6.4         | Use Gain block for computations of the power of 2 (FPGA)                                                                                 | Recommended             | FPGA<br>(Altera/Xilinx) |         |

| <u>2.6.5</u>  | Use a Gain block for constant multiplication and constant division                                                                       | Strongly<br>Recommended | All                     |         |

| <u>2.6.6</u>  | Efficient multiplier design for targeting Altera DSP block                                                                               | Recommended             | FPGA<br>(Altera)        |         |

| 2.6.7         | Efficient multiplier design for targeting Xilinx DSP48 slices                                                                            | Recommended             | FPGA (Xilinx)           |         |

| <u>2.6.8</u>  | Consider speed/area priority and DSP mapping when modeling complex multiplication                                                        | Recommended             | All                     |         |

| <u>2.6.9</u>  | Model the delay of blocks that will be auto-pipelined<br>(Divide, Sqrt, Trigonometric Function, Cascade<br>Add/Product, Viterbi Decoder) | Recommended             | All                     |         |

| <u>2.6.10</u> | Use Divide blocks in reciprocal mode with a RecipNewton<br>or RecipNewtonSingleRate architecture for more optimal<br>HDL                 | Strongly<br>Recommended | All                     |         |

| <u>2.6.11</u> | Consider the additional latency impact of different<br>implementation architectures for the Sqrt and<br>ReciprocalSqrt blocks            | Informative             | All                     |         |

|               | Tradeoffs for Sin/Cos calculation using Trigonometric                                                            |                         |               |          |

|---------------|------------------------------------------------------------------------------------------------------------------|-------------------------|---------------|----------|

| <u>2.6.12</u> | Function, Lookup Table, Sine/Cosine, and NCO HDL<br>Optimized block                                              | Informative             | All           |          |

|               | Use only conj, hermitian, or transpose in a Math Function                                                        |                         |               |          |

| <u>2.6.13</u> | block                                                                                                            | Mandatory               |               |          |

| <u>2.6.14</u> | HDL code generation compatible Math Operations for<br>complex number computation                                 | Informative             | All           |          |

| <u>2.7</u>    | Ports and subsystems                                                                                             |                         |               |          |

| <u>2.7.1</u>  | Block settings for Triggered Subsystems/Enabled<br>Subsystems                                                    | Mandatory               | All           |          |

| <u>2.7.2</u>  | Proper usage of a Unit Delay Enabled block versus an<br>enabled subsystem with a Delay block Informative         |                         | All           |          |

| <u>2.8</u>    | Signal attributes                                                                                                |                         |               | •        |

| <u>2.8.1</u>  | Rate conversion blocks and usage                                                                                 | Recommended             | All           |          |

| <u>2.9</u>    | Signal routing                                                                                                   |                         |               | •        |

| <u>2.9.1</u>  | Choosing the right block for extracting a portion of a vector signal                                             | Recommended             | All           |          |

| <u>2.9.2</u>  | Block parameter setting for the Multiport Switch Block Mandatory                                                 |                         | All           |          |

| <u>2.9.3</u>  | Add 1 to index signals when describing a selector circuit in a MATLAB Function block Recommended                 |                         | All           |          |

| <u>2.9.4</u>  | Use a MATLAB Function block to select indices when<br>extracting portions of a very large constant vector Recomm |                         | All           |          |

| <u>2.9.5</u>  | Writing to individual elements of a vector signal using the Assignment block                                     | Mandatory               | All           |          |

| 2.9.6         | Proper usage of Goto/From blocks                                                                                 | Mandatory               | All           |          |

| 2.9.7         | Ascending bit ordering for 1-D arrays may cause warnings from HDL rule checkers                                  | Informative             | All           | 2.1.6.1  |

| 2.10          | Source blocks                                                                                                    |                         |               |          |

| 2.10.1        | Do not use a sample time of inf for a Constant block                                                             | Mandatory               | All           |          |

| 2.11          | MATLAB Function blocks                                                                                           |                         |               |          |

| 2.11.1        | Proper usage of dsp.Delay as a register                                                                          | Recommended             | All           |          |

| <u>2.11.2</u> | Update persistent variables at the end of a MATLAB function                                                      | Strongly<br>Recommended | All           |          |

| <u>2.11.3</u> | Explicitly define data types for constants used in<br>expressions                                                | Mandatory               | All           |          |

| <u>2.11.4</u> | Use Delay blocks to break feedback loops in MATLAB Function blocks                                               | Mandatory               | All           |          |

| <u>2.11.5</u> | Do not use logical operators in conditional statements when initializing persistent variables                    | Recommended             | All           |          |

| <u>2.11.6</u> | Use X(:)=X+1; when input and output data types are the same in MATLAB code expressions                           | Recommended             | All           |          |

| <u>2.11.7</u> | Avoid unintended latch inference by performing arithmetic operations outside of if/else branches                 | Strongly<br>Recommended | All           | 2.2.1.1  |

| <u>2.11.8</u> | Avoid generating always @* Verilog code for Xilinx Virtex-<br>4 and 5                                            | Mandatory               | FPGA (Xilinx) |          |

| 2.11.9        | Using MATLAB code for [M, N] matrix operations                                                                   | Informative             | All           |          |

| 2.11.10       | Use a single for loop for element-by-element operations to reduce area                                           | Recommended             | All           |          |

| 2.12          | Stateflow                                                                                                        | I                       | I             | l        |

| <u>2.12.1</u> | Choosing Mealy vs Moore for Stateflow state machine type                                                         | Strongly<br>Recommended | All           | 2.11.1.1 |

|               |                                                                                                                  | Strongly                |               |          |

|                        | Do not upo phopluto timo for temporal la rical la ric (after                                 | 1                       |       |         |

|------------------------|----------------------------------------------------------------------------------------------|-------------------------|-------|---------|

| <u>2.12.3</u>          | Do not use absolute time for temporal logical logic (after, before and every)                | Mandatory               | All   |         |

| 2.12.4                 | Consider desired state order in generated HDL when                                           | Recommended             | All   |         |

|                        | naming states                                                                                |                         |       |         |

| <u>2.12.5</u>          | Using a chart output as an input via a feedback loop                                         | Recommended             | All   |         |

| <u>2.12.6</u>          | Insert an unconditional transition state to create an else statement in the generated HDL    | Strongly<br>Recommended | All   | 2.7.1.3 |

| <u>2.12.7</u>          | Avoid unintended latch inference by performing arithmetic operations outside of truth tables | Strongly<br>Recommended | All   | 2.2.1.1 |

| <u>2.12.8</u>          | Hardware considerations when designing an FSM                                                | Strongly<br>Recommended | All   |         |

| 2.13                   | DSP System Toolbox                                                                           | Reconniciació           |       |         |

|                        | Use the DSP System Toolbox Delay block if the number of                                      |                         |       |         |

| <u>2.13.1</u>          | samples to delay might be 0                                                                  | Recommended             | All   |         |

| 2.13.2                 | Changing the phase offset of a Downsample block                                              | Recommended             | All   |         |

| 2.13.3                 | Use the NCO HDL Optimized block for sine and cosine                                          | Recommended             | All   |         |

|                        | computation and signal generation                                                            |                         |       |         |

| <u>2.13.4</u>          | Block settings for FIR filter blocks                                                         | Informative             | All   |         |

| <u>2.13.5</u>          | IIR Filter blocks                                                                            | Informative             | All   |         |

| <u>2.14</u>            | Others                                                                                       |                         |       |         |

| <u>2.14.1</u>          | Use case restrictions when importing user-defined HDL code with an HDL Cosimulation block    | Mandatory               | All   |         |

| <u>2.14.2</u>          | Define clock and block name to match user-defined HDL                                        | Mandatory               | All   |         |

| 2                      | settings when using an HDL Cosimulation block Data type settings                             |                         |       |         |

| <u>3</u><br><u>3.1</u> | Basic data type settings                                                                     |                         |       |         |

| <u>3.1</u>             | Use fixed binary point scaling up to 128-bit for fixed-point                                 |                         |       | 1       |

| <u>3.1.1</u>           | operations                                                                                   | Mandatory               | All   |         |

| <u>3.1.2</u>           | Trading off rounding error vs processing expense                                             | Strongly<br>Recommended | All   |         |

| <u>3.1.3</u>           | Restrictions for data type override                                                          | Informative             | All   |         |

| 3.2                    | Simulink data type setting                                                                   |                         |       |         |

| <u>3.2.1</u>           | Use Boolean for logical data and use ufix1 for numerical data                                | Mandatory               | All   |         |

| 3.2.2                  | Define the data type of a Gain block explicitly                                              | Recommended             | All   |         |

| 3.2.3                  | Restrictions for using enumerated values                                                     | Mandatory               | All   |         |

| 3.3                    | Data type setting for MATLAB code                                                            | Mandatory               | 7 (11 |         |

| <u>3.3.1</u>           | Using a fi object in a MATLAB Function block                                                 | Strongly<br>Recommended | All   |         |

| 3.3.2                  | Use like or cast to inherit data types in MATLAB code                                        | Recommended             | All   |         |

| 3.3.3                  | Use True/False instead of Boolean data in MATLAB code                                        | Mandatory               | All   |         |

| 3.4                    | Data type setting for Stateflow charts                                                       |                         | 1     | 1       |

| <u>3.4.1</u>           | Use a fi object when the Stateflow action language is                                        | Mandatory               | All   |         |

|                        | MATLAB                                                                                       |                         |       |         |

| 4                      | Optimization of speed and area                                                               |                         |       |         |

| 4.1                    | Resource sharing                                                                             | Mandatarri              | All   |         |

| <u>4.1.1</u>           | Resource sharing requirements                                                                | Mandatory               | All   |         |

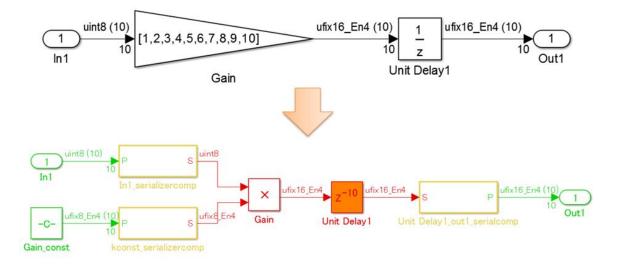

| <u>4.1.2</u>           | Use StreamingFactor for resource sharing of 1D vector signal processing                      | Informative             | All   |         |

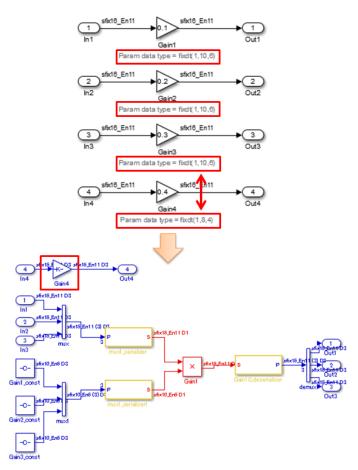

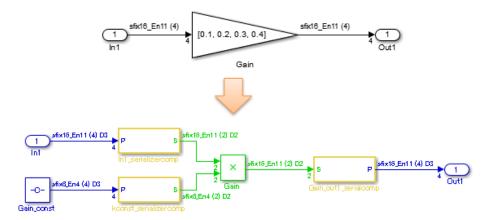

| <u>4.1.3</u>           | Resource sharing of Gain blocks                                                              | Recommended             | All   |         |

| 4.1.4                  | Resource sharing of Product blocks                                                           | Recommended             | All   |         |

| 4.1.5                  | Resource sharing of subsystems                                                               | Recommended             | All   |         |

| <u>4.2</u>   | Pipeline insertion                                                                                                                |  |     |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|--|-----|--|

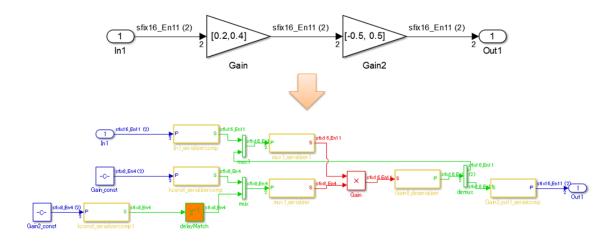

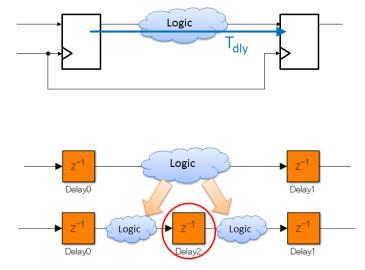

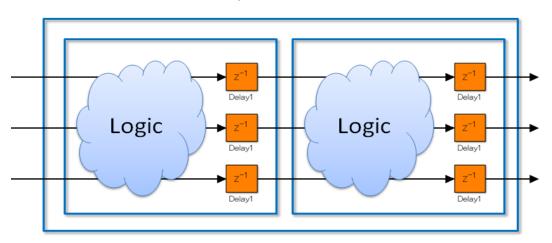

| <u>4.2.1</u> | Design considerations for pipelining and delay balancing Recommended All                                                          |  |     |  |

| 4.2.2        | Clock-rate pipelining Informative All                                                                                             |  |     |  |

| <u>4.2.3</u> | Recommended distributed pipelining settings Recommended All                                                                       |  | All |  |

| <u>4.2.4</u> | Apply distributed pipelining to adders, products, min/max,<br>and dot products with vector inputs         Informative         All |  |     |  |

| <u>5</u>     | Appendix                                                                                                                          |  |     |  |

| <u>5.1</u>   | Considerations in HDL code writing for ASIC/FPGA design                                                                           |  |     |  |

| <u>5.2</u>   | Synchronous circuit design overview and recommendations                                                                           |  |     |  |

| <u>5.3</u>   | Recommended use of registers at outputs of hierarchical structures                                                                |  |     |  |

| <u>5.4</u>   | Follow naming conventions                                                                                                         |  |     |  |

| <u>5.5</u>   | HDL-supported blocks                                                                                                              |  |     |  |

| <u>5.6</u>   | Compatibility check for HDL code generation                                                                                       |  |     |  |

| <u>5.7</u>   | Setting global clock and reset signals in for HDL code generation                                                                 |  |     |  |

| <u>5.8</u>   | Add comments for generating readable HDL code                                                                                     |  |     |  |

# 1. Architecture Design

# 1.1 Basic settings

# 1.1.1 Appropriate use of Simulink, Stateflow, MATLAB Function, BlackBox, Model Reference and HDL Cosimulation block

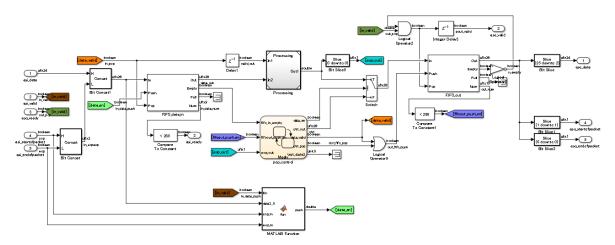

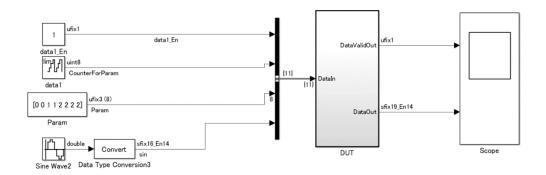

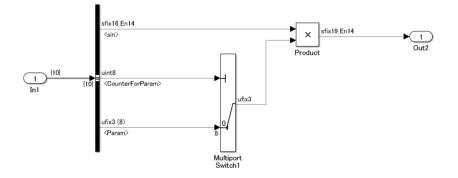

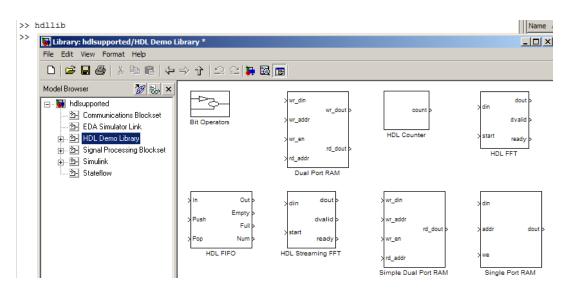

When creating a hardware implementation model, there are recommended applications for Simulink blocks, MATLAB function blocks and Stateflow charts. These can be mixed within a single subsystem to create a complete model as shown in the following figure:

The recommended application for each type of block is as follows:

- Simulink block: Arithmetic algorithm containing numerical processing or feedback loop.

- MATLAB Function block: Control logic, conditional branch (If/Else statement), simple state machine, and IP written with MATLAB code.

- Stateflow:

- State chart (Chart, State Transition Table block): Mode logic or state machine which control an output by logic of the past and the present

- Flow chart (Chart block): Multiple conditional branch (If/Else)

- Truth table (Truth Table block): Multiple conditional branch (If/Else)

The algorithm modeled by Stateflow uses logic as main elements, and when complicated operation is included, describe that the calculated result of Simulink block is changed in the logic of Stateflow. Because explicit pipeline processing cannot be described in Stateflow and change of the timing by pipelining insertion is unclear.

- BlackBox: For subsystems that don't need simulation, or that will use imported HDL code. This is an architecture property that can be applied to a <u>subsystem</u> or a <u>referenced model</u> (for example, an interface circuit for an A/D converter, an SDRAM controller, etc.) It is also possible to use the BlackBox property to <u>incorporate handwritten code into a cosimulation model</u>.

- Model reference: For re-using models as sub-blocks in other models. This is useful for partitioning a design to be worked on by multiple engineers in parallel. For more on HDL code generation from a referenced model, see the <u>documentation</u>.

Note that since a referenced model is treated the same as an Atomic subsystem, an <u>algebraic loop</u> may occur which will prevent HDL code generation. These can be fixed in the design, or possibly by setting the **Minimize algebraic loop occurrences** in the **Model Referencing** pane of Configuration Parameters.

HDL Cosimulation: For simulating HDL code for the DUT in Mentor<sup>®</sup> Questa<sup>®</sup> or ModelSim<sup>®</sup>, or Cadence<sup>®</sup> Incisive<sup>®</sup>, connected to the Simulink environment via <u>HDL Verifier</u>.

1.1.2 Use the hdLsetup command to set model configuration parameters and HDL model properties hdlsetup('modelname') sets the parameters of the model specified by modelname to common default values for HDL code generation.

Example: myhdlsetup.m

#### 1.1.3 Avoid using double-byte characters

Double-byte characters, which are used for Japanese and Chinese characters, are typically not supported by downstream logic synthesis and simulation tools. Therefore HDL code generation does not support them in model and block names.

It is also recommended to avoid using double-byte characters in comments as well, since comments are propagated into the generated code. It is good practice to use English for comments.

1.1.4 Consider resource sharing impact during model creation See 4.1 Resource Sharing.

#### 1.1.5 Document block name, block features, authors, etc., in subsystem block properties

To improve management of the generated HDL, it is good practice to document reference information in the subsystem block properties since these will be generated as comment headers in the HDL. For example:

| 🚹 Block Prope                                                                                                                                                                                                                                                                            | rties: Vector_FFT |           |        |      | ×     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|--------|------|-------|

| General                                                                                                                                                                                                                                                                                  | Block Annotation  | Callbacks |        |      |       |

| Usage                                                                                                                                                                                                                                                                                    |                   |           |        |      |       |

| Open Block: Click on the link to open the block.<br>Description: Text saved with the block in the model file.<br>Priority: Specifies the block's order of execution relative to other blocks in the same<br>model.<br>Tag: Text that appears in the block label that Simulink generates. |                   |           |        |      |       |

| Open Block:                                                                                                                                                                                                                                                                              | Vector_FFT        |           |        |      |       |

| Description                                                                                                                                                                                                                                                                              |                   |           |        |      |       |

| Function: V<br>This model<br>Revision 1.                                                                                                                                                                                                                                                 | shows             | ty to     |        |      |       |

| Priority:                                                                                                                                                                                                                                                                                |                   |           |        |      |       |

|                                                                                                                                                                                                                                                                                          |                   |           |        |      |       |

|                                                                                                                                                                                                                                                                                          |                   | OK        | Cancel | Help | Apply |

This generates code with a header that looks like this:

```

-- Simulink subsystem description for vector_fft_implementation_example/Vector_FFT:

--

-- Created by: John Simulink

-- Function: Vector FFT

-- This model shows...

-- Revision 1.0

-- Revision 1.1 added functionality to...

--

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY Vector FFT IS

```

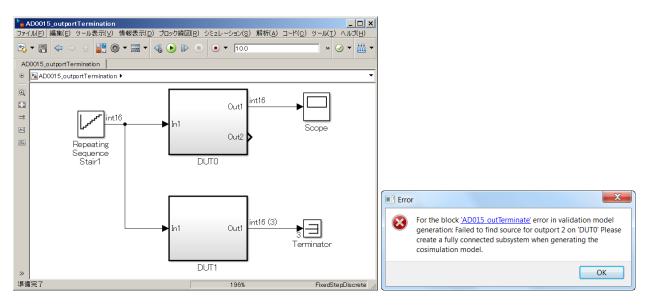

### 1.1.6 Terminate unconnected block outputs with Terminator blocks

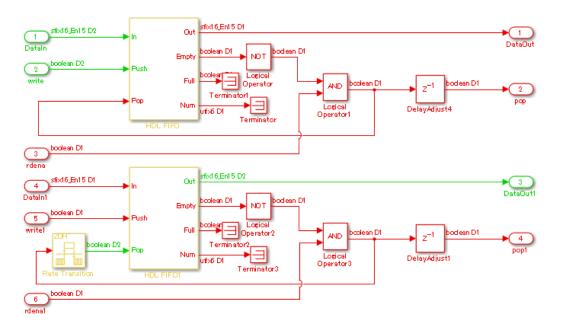

HDL code generation will fail and generate an error when output ports of blocks are unconnected. For output blocks that are intentionally not connected to downstream logic, connect them to a <u>Terminator block</u>. The following illustrates:

Example: AD015\_outTerminate.slx

#### 1.1.7 Proper usage of commenting out blocks

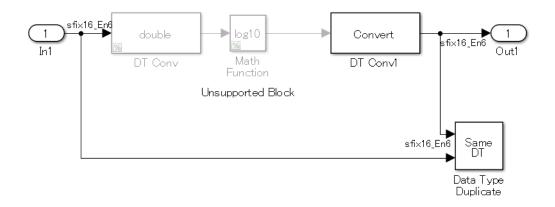

Code generation will fail if a block has been tagged as a "comment through" pass-through.

Code can be generated for a block that is commented out. The generated code will assign a constant value of 0 to the signal that would have been connected to its output. For instance the following example:

Generates the following HDL:

| VHDL generated from the subsystem containing a<br>commented-out block | Verilog generated from the subsystem containing a<br>commented-out block |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------|

| ENTITY Generated IS                                                   | module Generated                                                         |

| <pre>PORT( In1 : IN std_logic_vector(15 DOWNTO 0);</pre>              | (                                                                        |

| Out1 : OUT std_logic_vector(15 DOWNTO 0)                              | In1,                                                                     |

| );                                                                    | Outl                                                                     |

| END Generated;                                                        | );                                                                       |

| ARCHITECTURE rtl OF Generated IS                                      | input signed [15:0] In1;<br>output signed [15:0] Out1;                   |

| SIGNAL TmpGroundAtDT DupIn1 out1 : signed(15 DOWNTO                   |                                                                          |

| 0);                                                                               | <pre>wire signed [15:0] TmpGroundAtDT_DupIn1_out1;</pre>            |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <pre>BEGIN     TmpGroundAtDT_DupIn1_out1 &lt;= to_signed(16#0000#,     16);</pre> | <pre>assign TmpGroundAtDT_DupIn1_out1 = 16'sb000000000000000;</pre> |

| Out1 <=                                                                           | assign Out1 = TmpGroundAtDT_DupIn1_out1;                            |

| <pre>std_logic_vector(TmpGroundAtDT_DupIn1_out1);</pre>                           | endmodule                                                           |

| END rtl;                                                                          |                                                                     |

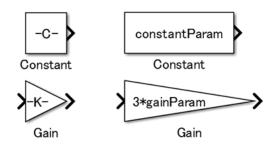

#### 1.1.8 Adjust sizes of constant and gain blocks so that parameters can be identified

For constant blocks and gain blocks that use parameter values, in order to increase readability it is good practice to adjust the size of the block so that the parameter value can be displayed. For instance:

# 1.1.9 Display parameters that will affect HDL code generation

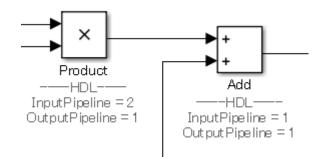

Certain block parameters such as pipelining and resource sharing can significantly affect HDL code generation. Therefore if these parameters are set, it is good practice to display them in the Simulink diagram. It also helps to use delimiters such as "-------" to separate the annotation from the block name. For example:

#### Example: BS013\_blockAnnotation.slx, showHdlBlockParams.m

The sample file showHdlBlockParams.m attaches a delimiter and annotation automatically to the block to which the following HDL block properties are set:

- BalanceDelays

- DistributedPipelining

- ConstrainedOutputPipeline

- InputPipeline, OutputPipeline

- StreamingFactor

- SharingFactor

In order to attach an annotation of the above property via the command-line:

```

>> showHdlBlockParams (<blockname> and 'on -- ')

```

To delete the annotation of the above property:

```

>> showHdlBlockParams (<blockname>, 'off')

```

#### 1.1.10 Change block parameters by using find\_system and set\_param

The functions find\_system and set\_param can be used together to batch modify the parameters of specific blocks. The following is an example script that detects Constant blocks with a **Sample time** of inf and batch modifies it to -1:

```

modelname = 'sfir_fixes'

% Detect all the Constant blocks in a model.

blockConstant = find_system(bdroot, 'blocktype', 'Constant')

```

```

% Sampling time detects the Constant block used as [inf],

% and changes sampling time into [-1].

for n = 1:numel(blockConstant)

sTime = get_param(blockConstant{n}, 'SampleTime')

if strcmp(lower(sTime), 'inf')

set_param(blockConstant{n}, 'SampleTime', '-1')

end

end

```

# 1.2 Subsystem and Model Hierarchy

#### 1.2.1 When the DUT is not at the top level of the model, set the DUT as a non-virtual subsystem

When the DUT (the target subsystem for code generation) exists in a lower hierarchy from the top, HDL Coder converts it to a model reference. Because the execution sequence of a referenced model is equivalent to an Atomic subsystem, when the DUT is a virtual subsystem this conversion may change its operation.

Therefore set the DUT as a non-virtual subsystem before verification and code generation. Subsystem types to which it can be set are: Atomic Subsystem; model reference; Variant Subsystem; and a variant model.

A conditionally-executed subsystem (Enabled Subsystem, Triggered Subsystem) cannot be specified as a DUT. In order to use one as a top-level, create an Atomic Subsystem one level of hierarchy up from it.

If there is a feedback loop out of an atomic subsystem that results in an algebraic loop, it will result in a code generation error. This can be fixed in the design by setting the **Minimize algebraic loop occurrences** in the **Model Referencing** pane of Configuration Parameters.

# 1.2.2 Type of subsystem and hierarchical design for a DUT

Considerations for a DUT subsystem:

- Because a difference in simulation results may occur, it is good practice to <u>make the DUT a non-virtual</u> <u>subsystem</u>, e.g. an Atomic subsystem, when it is not at the top level of the model.

- When generating code from a subsystem which is low in the design hierarchy, make the HDL block property of the subsystem into the default configuration.

- If the DUT is lower in the design hierarchy, because it gets converted to a reference model, a new Simulink model with references to the validation and co-simulation models will be generated in the target directory for code generation.

- The subsystem which is at the top of the hierarchy for code generation cannot be set as a BlackBox.

- Connect outputs with no fanout to a Terminator block.

- Don't place a comment through and a comment out block into the DUT.

Guidelines for usage of various subsystems:

- Virtual subsystem

- A subsystem is virtual if the block is neither conditionally executed nor atomic.

- <u>Don't use it as a DUT</u>. Use this type of subsystem in lower levels of the hierarchy where you want to divide a generated file.

- Atomic Subsystem

- Make the DUT an Atomic Subsystem.

- Use Atomic Subsystems to generate a single HDL file for identical instances of subsystems in lower levels of hierarchy.

- To enable resource sharing in a subsystem unit, make all target subsystems into Atomic Subsystems.

- Variant Subsystem (Example : AD004\_variantSubDivide.slx and AD020\_variantChildOp.slx)

- Use this block to change the behavior of a subsystem by using a MATLAB variable without having to modify the subsystem itself.

- The file name and instance name for the generated code will be unique to the active configuration at the time of code generation.

- It cannot be set as the top hierarchy for a DUT.

- It cannot be a target of resource sharing.

- <u>Model Referencing</u> (Example: AD002\_modelRefDivide.slx and AD019\_modelRefChild.slx)

- Use this block to unify a model composed of smaller partitions. It also enables incremental code generation.

- A reference model can be set as the DUT for code generation. A directory will be created using the reference model name and the HDL code will be placed under it.

- When using a continuous block in a testbench, make the DUT into a reference model.

- The preference of the block parameter [Model argument values] (for this instance) of a reference model is not equivalent to a Code Generation.

- <u>Model Variants</u> (Example: AD003\_modelVariantDivide.slx and AD021\_varianChildRecip.slx)

- This block is the same use-case as a reference model, except its behavior can be changed by using a MATLAB variable.

- Because it becomes the model name set as the file name/instance name generated being effective, if an effective subsystem is changed, it will be cautious of the file name/instance name generated changing.

- Similar to a Variant Subsystem, it cannot be set as a code generation target subsystem.

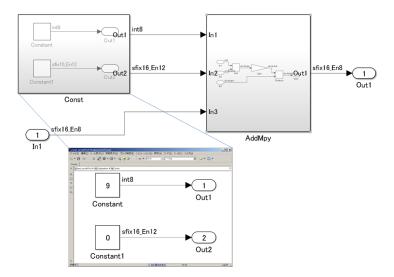

#### 1.2.3 Do not connect constant blocks to ports directly crossing subsystem boundaries

For an example such as the following, where a constant is directly connected to the output port of a subsystem:

Logic synthesis may optimize away the constant, resulted in an unconnected output port.

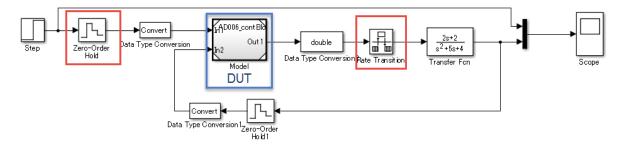

# 1.2.4 For testbenches that use blocks in continuous solver mode, make the DUT a model reference with a discrete solver.

Some testbenches may include parts that require continuous solvers, such as the Continuous library and Simscape. Since the lower levels of hierarchy inherit the solver settings by default, convert the DUT subsystem to a referenced model and that points to a model that uses a discrete solver.

You will need to insert sample time conversion blocks such as Rate Transition or Zero-Order Hold at the boundaries of the DUT to convert the input and output signals.

#### Examples: AD005\_continuous.slx, AD006\_contBlock.slx

#### 1.2.5 Generate re-usable HDL code from identical subsystems

When there are two or more subsystems (including library blocks) which perform the same function, by default an HDL file for each of these virtual subsystems will be generated. In order to generate a single HDL file, convert this subsystem to an Atomic Subsystem. This will make the generated files easier to manage. See <u>Generate Reusable</u> <u>Code from Atomic Subsystems</u> in the product documentation for an example.

#### 1.2.6 Generate parameterized HDL code for gain and constant blocks

When using several masked subsystems for which only the Constant or Gain parameters differ, you can reduce the number of generated HDL files by setting <u>Generate parameterized HDL code from masked subsystem</u> to "on" in the HDL Code Generation pane.

#### Example: AD012\_HDLParameter.slx

#### 1.2.7 Insert handwritten code for a block into the generated code for the DUT

Some cases, such as re-using pre-verified RTL IP, require insertion of existing code for a block into the DUT. In order to ease this process, create the block in Simulink in order to be plug-in-compatible with the generated code. This includes the following:

- Name the block the same name as the VHDL entity or Verilog module

- Define the same inputs and outputs, including the same types, sizes, and names

- Define the same clock, reset, and clock enable. Note that only one clock, reset, and clock enable per block is allowed.

- The block can only be single-rate

Then set the block to be a Black Box in order to disable code generation. See the documentation for details.

#### 1.2.8 Only use numerical values and string data types for mask parameters for user-defined subsystems

By using parameterized values for masked subsystems, you can generate parameterized HDL code. But code can only be generated if the mask parameters are numerical values or strings. Using objects, types, or Simulink API commands such as add\_block, add\_line, etc. will result in a code generation error.

# 1.3 Signal types

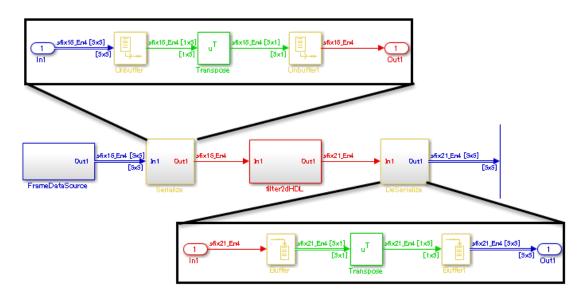

1.3.1 Serialize 2D matrix signals into a 1D signal before it enters an HDL subsystem, and vice versa for the output Because hardware interfaces are one-dimensional, any multi-dimensional matrix must be serialized into a hardware-friendly one-dimensional scalar or vector. For image/video signals, use the Frame-To-Pixels block in the Vision HDL Toolbox product.

#### Example: AD001\_matrix.slx

This example model performs serialization of two-dimensional data at the input, and then deserialization at the output.

- Serialize: Converts the two-dimensional matrix data of size MxN into scalar data. It consists of two Unbuffer blocks and a Transpose block. The first Unbuffer block divides data into a line writing direction, and divides the 5x5 matrix data into four 1x5 vectors. Note that the sampling time is set to one-fourth since there will be four output vectors for each input sample. The Transpose block that follows transposes the 1x5 vector into a 5x1 vector. The last Unbuffer block divides the 5x1 vector data into scalar data for input to the image processing subsystem (filter2HDL).

- DeSerialize: Converts the scalar data output from the filter2HDL subsystem into a two-dimensional matrix. It consists of two Buffers and one Transpose block. This converts the scalar data to lines then to the MxN matrix, in an inverse operation from the Serialize block. Note that the output sample time ends up being the same as the sample time on the input to the Serialize block.

In addition, two-dimensional processing is supported within the MATLAB code and the MATLAB Function block. For details, refer to <u>2.11.10 Use MATLAB code for [M and N] matrix operation</u>.

#### 1.3.2 Using a signal bus to improve readability

When a DUT has many input or output signals, to improve readability, create a bus signal using a Bus Creator block to create a single structure for the input or output

Example: AD022\_bus.slx

The bus signal can be a structure of different data types or a vector signal of the same data types. However, since the amount of blocks that support bus signals is limited, when performing signal conditioning, it is necessary to extract the desired signal from a bus using a Bus Selector block. The HDL code corresponding to the signal line in a bus signal serves as a signal name in an input or output port as the generated code shown below.

| signal     signal       ENTITY DUT IS<br>PORT(clk     : IN std_logic;<br>clk_enable     : IN std_logic;<br>clk_enable     module DUT       DataIn_CounterForParam     : IN std_logic;<br>DataIn_CounterForParam     : Clk,<br>reset,<br>clk_enable,<br>DataIn_CounterForParam     clk_enable,<br>DataIn_dataI_En,<br>DataIn_dataI_En,<br>DataIn_dataI_En,<br>DataIn_garam       std_logic_vector(7 DOWNTO 0); ufix3 [8]<br>DataIn_sin     : IN<br>DataIn_faram     DataIn_dataI_En,<br>DataIn_Param_0,<br>DataIn_Param_1,<br>DataIn_Param_2,<br>DataIn_Param_3,<br>ce_out     DataIn_Param_1,<br>DataIn_Param_3,<br>DataIn_Param_3,<br>DataIn_Param_6,<br>DataIn_Param_6,<br>DataIn_Param_7,<br>DataIn_Param_6,<br>DataIn_Param_7,<br>DataIn_Param_7,<br>DataIn_Param_7,<br>DataIn_Param_7,<br>DataIn_Param_7,<br>DataIn_param_6,<br>DataIn_Param_7,<br>DataIn_Param_7,<br>DataIn_Param_7,<br>DataIn_sin,<br>ce_out,<br>DataOut | VHDL generated from the model containing a bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Verilog generated from the model containing a bus |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| <pre>ENTITY DUT IS<br/>PORT(clk : IN std_logic;<br/>reset : IN std_logic;<br/>DataIn_datal_En : IN std_logic;<br/>DataIn_CounterForParam : IN<br/>std_logic_vector(7 DOWNTO 0); ufix3 [8]<br/>DataIn_Param : IN<br/>vector_of_std_logic_vector3(0 TO 7); ufix3 [8]<br/>DataValidOut : OUT std_logic;<br/>DataValidOut : OUT std_logic;<br/>DataIn_param_3,<br/>ce_out : OUT std_logic;<br/>DataIn_Param 6,<br/>DataIn_Param_7,<br/>Std_logic_vector(18 DOWNTO 0) sfix19_En14<br/>);<br/>END DUT;<br/>SIGNAL Bus_Creator2_out1_Param<br/>vector_of_std_logic_vector3(0 TO 7); ufix3 [8]</pre>                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                   |

| <pre>u_Enabled_Subsystem : Enabled_Subsystem<br/>PORT MAP( clk =&gt; clk,</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <pre>ENTITY DUT IS<br/>PORT ( clk : IN std_logic;<br/>reset : IN std_logic;<br/>DataIn_data1_En : IN std_logic;<br/>DataIn_CounterForParam : IN<br/>std_logic_vector(7 DOWNTO 0); ufix8<br/>DataIn_Param : IN<br/>vector_of_std_logic_vector3(0 TO 7); ufix3 [8]<br/>DataIn_sin : IN<br/>std_logic_vector(15 DOWNTO 0); sfix16_En14<br/>ce_out : OUT std_logic;<br/>DataValidOut : OUT std_logic;<br/>DataValidOut : OUT std_logic;<br/> ufix1<br/>DataOut : OUT<br/>std_logic_vector(18 DOWNTO 0) sfix19_En14<br/>);<br/>END DUT;</pre> | <pre>module DUT</pre>                             |

| assign ce_out = clk_enable;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | assign ce_out - cik_endble;                       |

|  | ٦. |

|--|----|

|  |    |

|  |    |

|  |    |

The blocks that support the Input a bus signal property for HDL generation are:

- Bus Creator

- Bus Selector

- MATLAB Function

- Delay, Memory

- Zero-order Hold

- Rate Transition (both up and down)

- Signal Specification

- From/Goto

- Switch

- Multi-Port Switch

- Stateflow

- Model Reference

- Vision HDL toolbox blocks (accept a pixel control bus for their control input)

To extract and use a signal from a Simulink bus signal to a block other than those listed above, use a Bus Selector block:

For more on HDL code generation support of bus structures, see <u>Signal and Data Type Support</u> in the documentation.

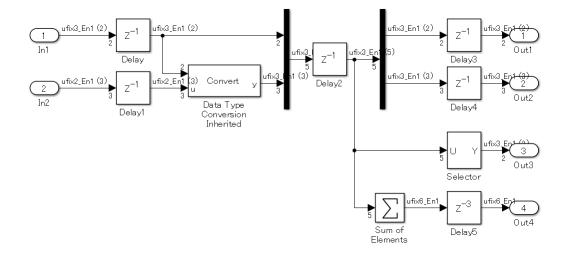

#### 1.3.3 Design considerations for vector signals

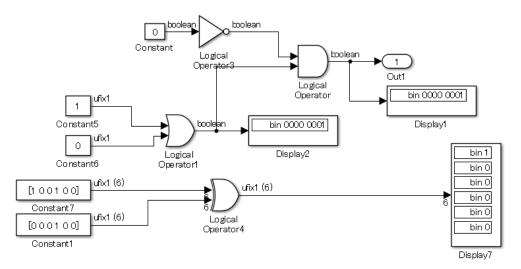

In order to process a group of signals with the same attributes as a vector signal, use a Mux block.

Example: AD014\_vector.slx

The signals to combine into a vector can be different dimensions. However they must be of the same data type. If they are not the same data type, use a Data Type Conversion block to avoid an error.

When separating and choosing the signal of a desired number of element from a vector signal, use a Demux block or a Selector block. In the following figure, two branches separate the vector signal of the number of element 5 into the vector signal of the number of elements 2 and 3 in the Demux block.

| Tunction Block Parameters: Demux                                                                          |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Demux                                                                                                     |  |  |  |  |  |  |  |

| Split vector signals into scalars or smaller vectors. Check 'Bus<br>Selection Mode' to split bus signals. |  |  |  |  |  |  |  |

| Parameters                                                                                                |  |  |  |  |  |  |  |

| Number of outputs:                                                                                        |  |  |  |  |  |  |  |

| [2 3]                                                                                                     |  |  |  |  |  |  |  |

| Display option: bar                                                                                       |  |  |  |  |  |  |  |

| Bus selection mode                                                                                        |  |  |  |  |  |  |  |

|                                                                                                           |  |  |  |  |  |  |  |

|                                                                                                           |  |  |  |  |  |  |  |

| OK Cancel Help Apply                                                                                      |  |  |  |  |  |  |  |

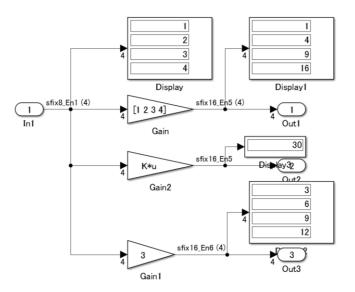

Methods for performing operations using vector signals are as follows:

- Various methods can be used for constant multiplication using a Gain block :

- 1 block of Gain(s): Multiplication for every element of a vector [A\*a, B\*b, C\*c, and D\*d]

- 2 blocks of Gain(s): Matrix multiplication A\*a+B\*b+C\*c+D\*d of a vector

- 3 blocks of Gain(s): Multiplication of a vector and a scalar [A\*a, B\*a, C\*a, and D\*a]

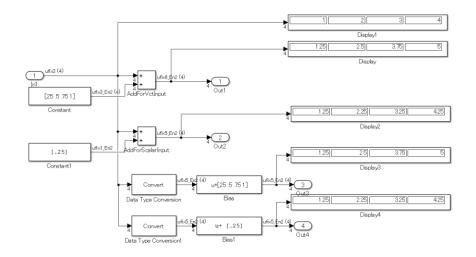

- Various methods can be used for performing constant addition/subtraction using either a constant and an Add block, or a Bias block.

- Addition of a vector signal and a scalar [A+a, B+a, C+a, and D+a]

- Addition of a vector signal and a vector [A+a, B+b, C+c, and D+d]

• When addition and subtraction of the elements of a vector signal are performed, Refer to <u>2.6.1 Input vector</u> with Mux block to multi-input adder, multi-input product, and multi-input Min/Max.

1.3.4 One-dimensional vectors created by Delay, Mux, and Constant blocks generate HDL with ascending bit order In order to assure compatibility with MATLAB vector signals, Simulink by default will create one-dimensional vectors specified in ascending order from LSB to MSB when using Delay and Mux blocks. This goes against convention in VHDL and Verilog and will trigger a warning from HDL rule checkers. You can either ignore the rule checker warning and ensure that all of your vector connections match in their ordering, or make the following changes to make sure that all vectors conform to the [MSB:LSB] convention.

#### Example: BS054\_downto.slx

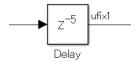

1. Delay block with delay value greater than 1 :

Generated VHDL:

```

-- <<u><S1>/Delay</u>

Delay_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

Delay_reg <= (OTHERS => '0');

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

Delay_reg(0) <= In1;

Delay_reg(0) <= In1;

END IF;

END IF;

END IF;

END PROCESS Delay_process;</pre>

```

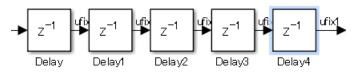

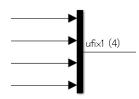

This can be addressed by using single-delay blocks in series:

The resulting VHDL will use scalar signals instead of vector signals.

2. Mux block

#### Generated VHDL:

```

SIGNAL Mux out1 : std_logic_vector(0 TO 3); -- ufix1 [4]

-- <<u>S1>/Mux</u>

Mux_out1(0) <= In1;

Mux_out1(1) <= In1;

Mux_out1(2) <= In1;

Mux_out1(3) <= In1;</pre>

```

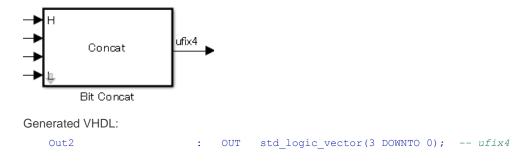

This can be addressed by using the Bit Concat block from the HDL Coder > HDL Operations library:

```

-- <S1>/Bit Concat

Bit_Concat_out1 <= unsigned'(In1 & In1 & In1 & In1);

Out2 <= std_logic_vector(Bit_Concat_out1);

</pre>

```

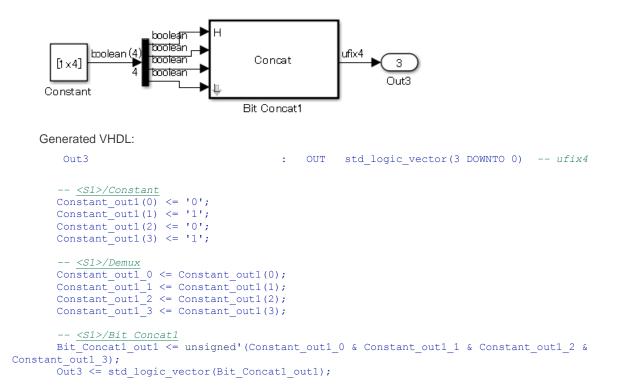

# 3. Constant block

Generated VHDL:

This can be addressed by using a Demux together with the Bit Concat block from the HDL Coder > HDL Operations library:

#### 1.3.5 Manually write HDL control logic for bidirectional ports

You can <u>specify bidirectional ports</u> for Subsystem blocks with black box implementation. In the generated code, the bidirectional ports have the Verilog or VHDL inout keyword.

However since Simulink cannot simulate the behavior of bidirectional ports, you will need to manually write HDL control logic in the black box in order to properly verify system-level behavior.

#### 1.4 Clock and Reset

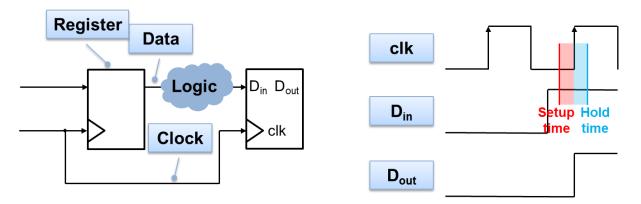

In Simulink, global signals such as clock, clock enable and reset are not explicitly modeled. Instead, they are created during code generation. You represent clock cycles in a Simulink model using sample time.

For a single-rate model, 1 sample time in Simulink maps to 1 clock cycle in HDL. You can use a relative mapping (e.g. 1 second in Simulink = 1 HDL clock) or an absolute mapping (e.g. 10e-9 second in Simulink = one 10 ns clock in HDL), depending on your preference and design requirement.

#### 1.4.1 Creating a frequency-divided clock from the Simulink model's base sample rate

You can assign a frequency-divided clock rate for HDL code generation to be a multiple of the Simulink base sample rate. For instance in a case where the Simulink base rate is 1 MHz and your target hardware will run at 50 MHz, you can assign a global <u>oversampling factor</u> of 50 in the **HDL Code Generation > Global Settings** pane in Configuration Parameters.

#### 1.4.2 Use master-clock division or a clock multiple for proper multi-rate model operation

For a multi-rate model, the fastest sample time maps to 1 clock cycle in HDL. Blocks operating at slower sample times use the same clock in HDL, but are gated with clock enable signals that are active once every N clock cycles. You can also specify HDL Coder to generate multiple synchronous clock signals. Each of the clock signals corresponds to one rate in Simulink.

Note: Some optimization settings (e.g. sharing factor) and alternative block architecture (e.g. Newton-Raphson square root) introduces additional sample rates not present in the original model. In those cases, the fastest generated sample time is mapped to 1 HDL clock

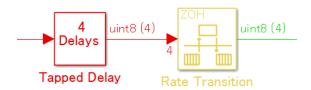

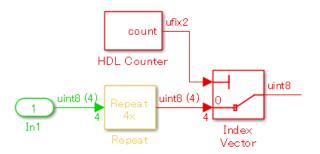

In order to model multi-rate clocks in Simulink, use the following blocks:

- Simulink > Signal Attributes > Rate Transition

- DSP System Toolbox > Signal Operations > Upsample, Downsample, Repeat

- HDL Coder > HDL Operations > HDL FIFO

For a Rate Transition block, select the block parameters **Ensure data integrity during data transfer** and **Ensure deterministic data transfer (maximum delay).** The output sample rate needs to be an integer multiple of the input – for input sample time Ts1 = 4 and output sampling time Ts2 = 12 can be used, however Ts1 = 3 and Ts2 = 4 will produce an error.

There are two ways to generate a clock signal for a DUT that has multiple sample rates:

| 🕲 Configuration Parameters: AD010_multiClock/Configuration (Active) |                      |                                 |                          |                    |  |  |  |

|---------------------------------------------------------------------|----------------------|---------------------------------|--------------------------|--------------------|--|--|--|

| Select:                                                             | Clock settings       |                                 |                          |                    |  |  |  |

| Solver                                                              | Reset type:          | Asynchronous                    | Reset asserted level:    | Active-high 🔹      |  |  |  |

| Data Import/Export <ul> <li>Optimization</li> </ul>                 | Clock input port:    | clk                             | Clock enable input port: | clk_enable         |  |  |  |

| Diagnostics<br>Hardware Implementation                              | Reset input port:    | reset                           | Clock inputs:            | Single             |  |  |  |

| Model Referencing                                                   | Oversampling factor: | 1                               | Clock edge:              | Single<br>Multiple |  |  |  |

| <ul> <li>Simulation Target</li> <li>Code Generation</li> </ul>      | Additional settings  |                                 |                          | Multiple           |  |  |  |

| <ul> <li>HDL Code Generation</li> <li>Global Settings</li> </ul>    | General Ports        | Optimization Coding style Codin | g standards Diagnosti    | CS E               |  |  |  |

| Test Bench<br>EDA Tool Scripts                                      | Comment in header:   |                                 |                          |                    |  |  |  |

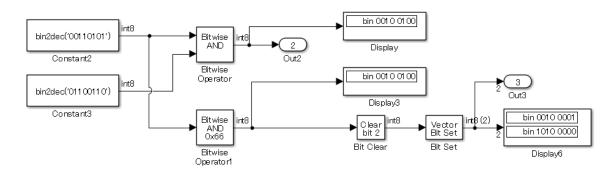

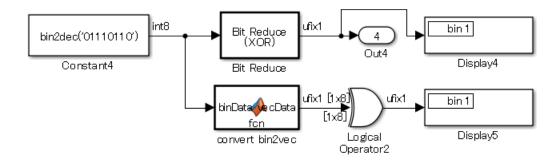

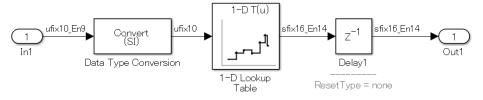

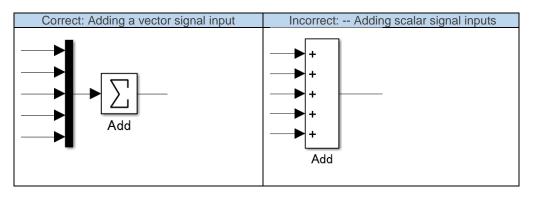

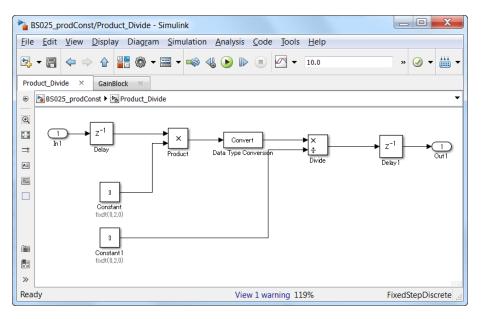

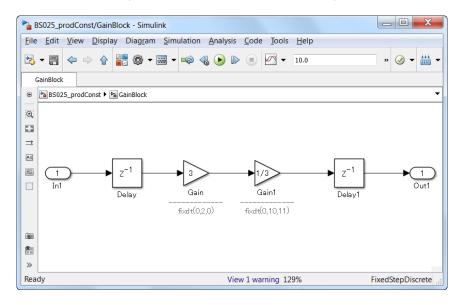

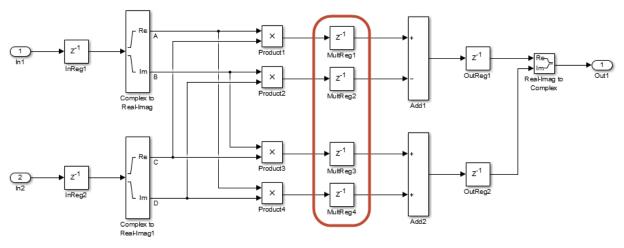

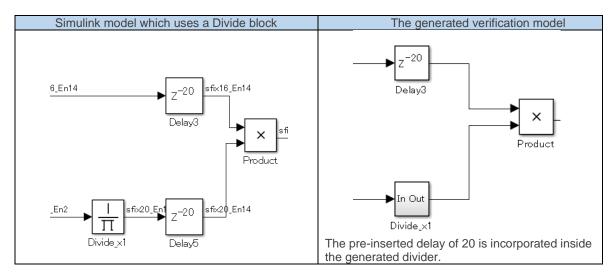

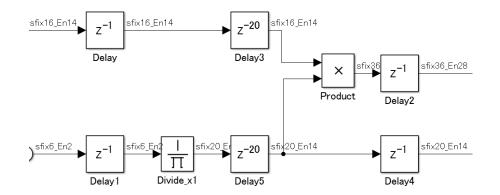

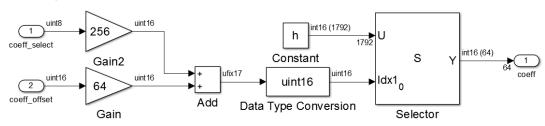

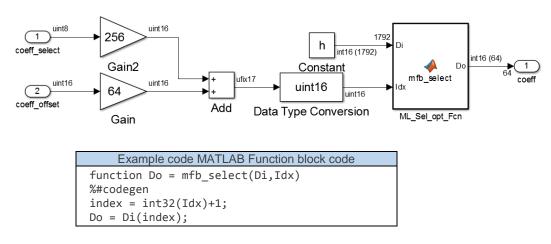

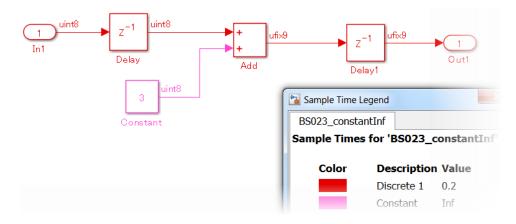

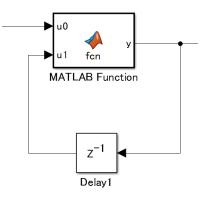

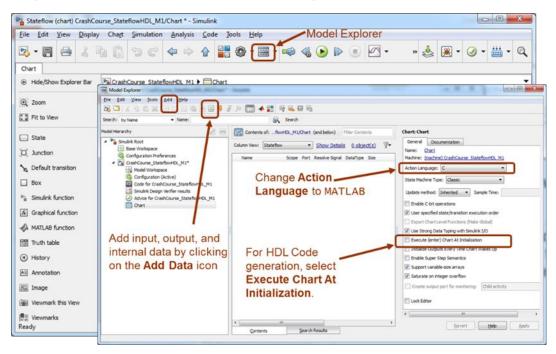

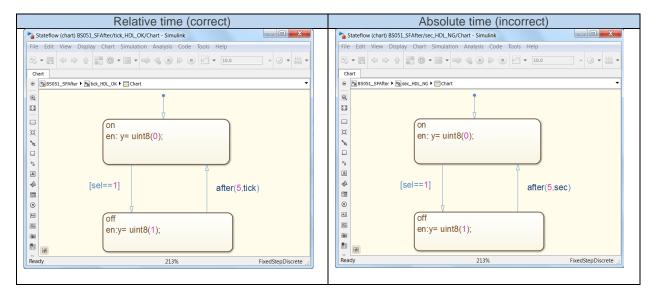

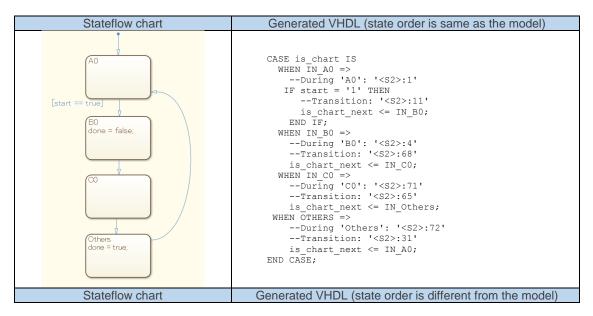

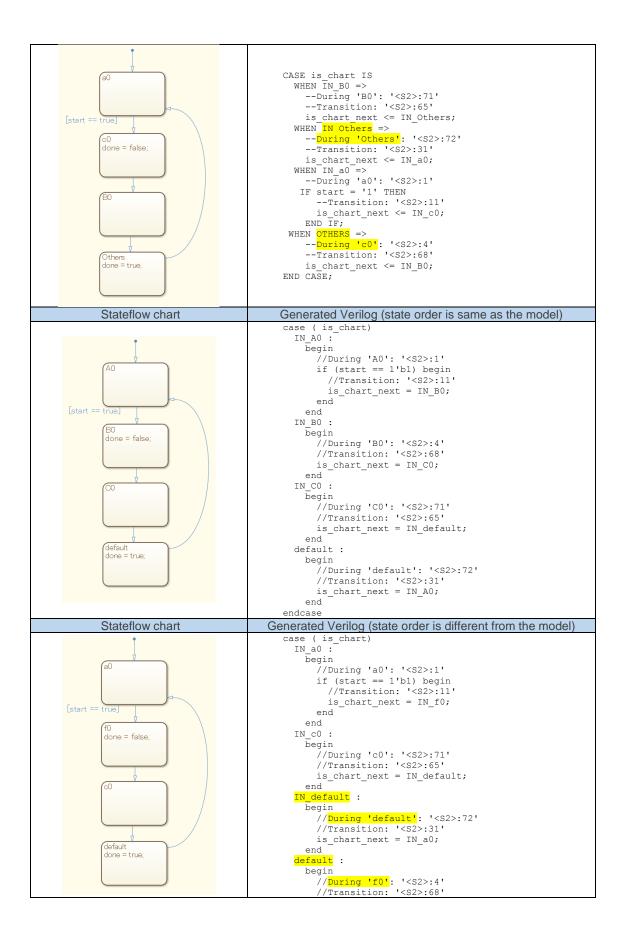

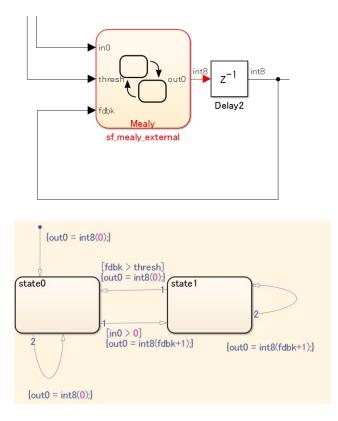

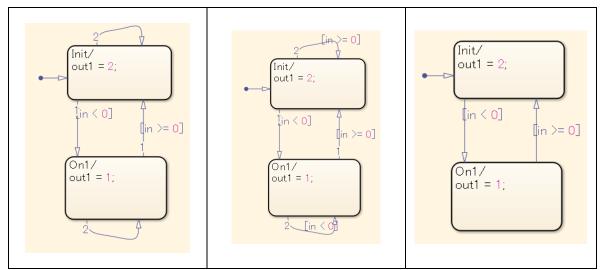

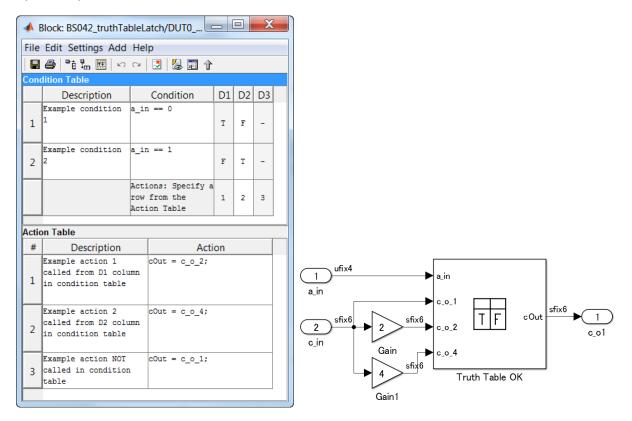

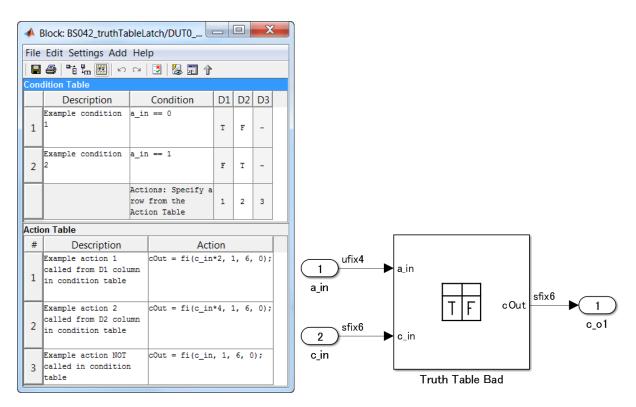

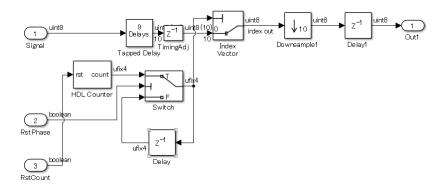

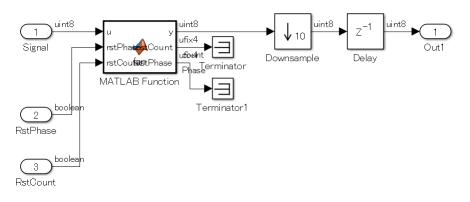

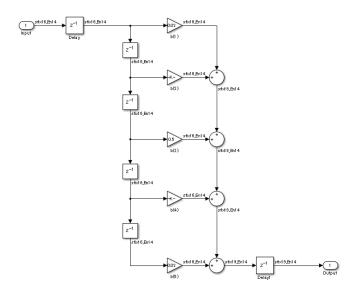

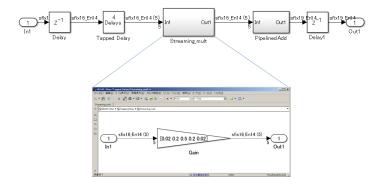

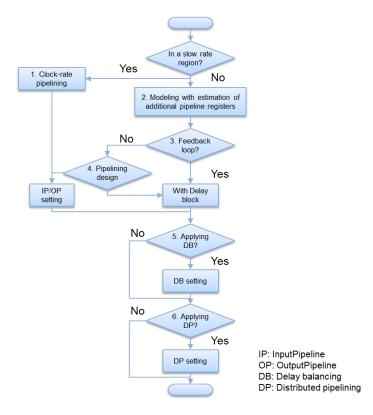

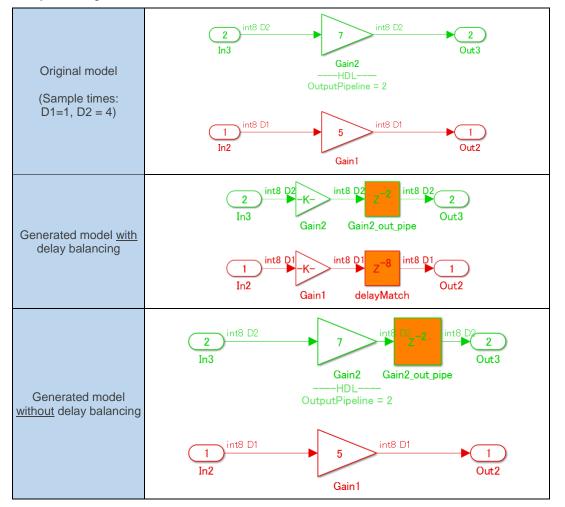

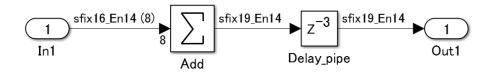

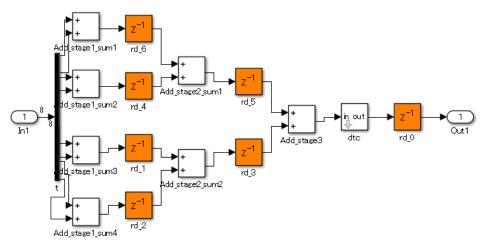

Example: AD010\_multiClock.slx