UCRL-53515

19980513

126

# Heat-Transfer Microstructures for Integrated Circuits

David Bazeley Tuckerman (Ph.D. Thesis)

> DISTRIBUTION STATEMENT A Approved for public release; Distribution Unlimited

February 1984

PLEASE RETURN TO:

BMD TECHNICAL INFORMATION CENTER BALLISTIC MISSILE DEFENSE ORGANIZATION 7100 DEFENSE PENTAGON WASHINGTON D.C. 20301-7100

U3181

MIG COLDER LENGTHER

#### DISCLAIMER

This document was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor the University of California nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial products, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government thereof, and shall not be used for advertising or product endorsement purposes.

Work performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract W-7405-Eng-48.

Accession Number: 3181

Publication Date: Feb 01, 1984

Title: Heat-Transfer Microstructures for Integrated Circuits

Personal Author: Tuckerman, D.B.

Corporate Author Or Publisher: Lawrence Livermore National Laboratory, Univ. of Cal., Livermore, CA 9 Report Number: UCRL-53515

Comments on Document: Dissertation in partial fulfillment of requirements for degree of Doctor of Philosophy at Stanford University Inventory for TN

Descriptors, Keywords: Heat-Transfer Microstructure Integrated Circuit

Pages: 00141

Cataloged Date: Oct 11, 1991

Contract Number: W-7405-ENG-48

Document Type: HC

Number of Copies In Library: 000001

Record ID: 22667

UCRL-53515 Distribution Category UC-38

# Heat-Transfer Microstructures for Integrated Circuits

David Bazeley Tuckerman (Ph.D. Thesis)

Manuscript date: February 1984

LAWRENCE LIVERMORE NATIONAL LABORATORY University of California • Livermore, California • 94550

Available from: National Technical Information Service • U.S. Department of Commerce 5285 Port Royal Road • Springfield, VA 22161 • \$16.00 per copy • (Microfiche \$4.50 )

### Heat-Transfer Microstructures for Integrated Circuits

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By David Bazeley Tuckerman

> > February 1984

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Prof. R. F. W. Pease Principal Advisor Dept. of Electrical Engineering

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

llh nrenn of. J. D. Plummer

Dept. of Electrical Engineering

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Prof. R. J. Moffat

Prof. R. J. Moliat Dept. of Mechanical Engineering

Approved for the University Committee on Graduate Studies:

Dean of Graduate Studies & Research

#### Abstract

The design of high-speed integrated circuits and systems is often constrained by thermal considerations. As late as 1981, it was authoritatively predicted that the maximum achievable power flux for liquid-cooled, densely-packed integrated circuits (ICs) would be about  $20 \text{ W/cm}^2$ .

Convective heat-transfer theory indicates that well over  $1000 \text{ W/cm}^2$  can be compactly removed from ICs at normal operating temperatures, provided microscopic (e.g.,  $50 \cdot \mu \text{m}$  wide) extended-surface structures are used. The difficulty of constructing high-conductance, low-stress thermal interfaces between ICs and heat sinks suggests the use of an integral heat sink. Accordingly, IC microfabrication techniques were employed to design, fabricate, and test novel, ultracompact water-cooled, laminar-flow, optimized plate-fin and pin-fin heat sinks directly within standard-thickness silicon substrates. Worst-case thermal resistances as low as  $0.083^{\circ}$ C/W were measured from 1-cm<sup>2</sup> thin-film resistors (e.g., a  $108^{\circ}$ C temperature rise at 1309 W), in good agreement with predictions. Further increases in heat transfer are achievable.

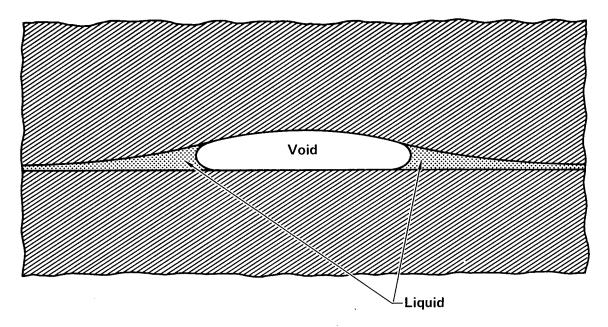

The use of integral liquid-cooled heat sinks in multichip systems presents potential yield, reliability, cost and packaging problems. Attachment of unmodified ICs to micro-heat sinks seems a more attractive approach. A novel die-attachment technique has been developed which avoids the problems of conventional attachments. In this technique, a liquid partially fills an array of micron-wide reentrant capillaries in the heat sink substrate, so that surface tension holds the polished back of an IC in intimate thermal contact with the heat sink. The bond is void-free, virtually stress-free, long-lived, and allows repeated detachment and replacement of ICs without damaging the heat sink substrate. The reentrant grooves were fabricated by a novel process using electroless plating of nickel onto vertical silicon microgrooves. For a 1-cm<sup>2</sup> area, typical interfacial thermal resistances of 0.022<sup>o</sup>C/W at 300 W have been measured.

In summary, microfabrication techniques have been employed to fabricate new, very highperformance liquid-cooled heat sinks having negligible volume (0.1 cm<sup>3</sup>), and also to make a novel, stress-free, reusable microcapillary thermal interface between such heat sinks and integrated circuit substrates. These techniques allow the VLSI system designer more freedom, in that power consumption may be greatly increased while simultaneously realizing the reliability benefits of a much lower operating temperature.

### Acknowledgments

First and foremost, I would like to thank my thesis supervisor Prof. R. Fabian Pease for his enthusiastic supervision and support of this work. I would also like to express my appreciation to the Fannie and John Hertz Foundation which provided the financial support for my graduate education and hence made possible a relatively unconstrained choice of research project at Stanford University. The encouragement of Lowell L. Wood of Lawrence Livermore National Laboratory (Hertz Foundation Graduate Fellowship Coordinator) throughout this work was greatly appreciated.

A number of individuals at Stanford provided invaluable consultations during this work. Profs. R. J. Moffat, W. M. Kays and A. L. London (masters of the art and science of heat transfer) were extremely helpful. Profs. J. D. Plummer, T. W. Sigmon, and R. M. Swanson were valuable instructors on various aspects of semiconductor technology, as were P. Barth, J. Beaudoin, J. McVittie, and J. Shott. I would also like to acknowledge discussions with R. W. Keyes of IBM Corp. and B. H. Whalen of TRW Corp.

Valuable supplies of materials and equipment were provided by K. Bean of Texas Instruments Inc., Pei-Yu Wu of Stanford University, and B. McWilliams of Lawrence Livermore National Laboratory.

The technical assistance of W. Holmes and Z. Norris of Stanford University is gratefully acknowledged.

Thanks are due Profs. J. D. Plummer and R. J. Moffat for reading the manuscript.

The final preparation of this document was done while the author was a staff member at Lawrence Livermore National Laboratory.

Financial support for various parts of this research was provided by the Semiconductor Research Corporation, TRW Corporation, Honeywell Corporation, and the Joint Services Electronics Program.

## **Table of Contents**

| 1. Introduction and Background                                              | 1           |

|-----------------------------------------------------------------------------|-------------|

| 1.1. Preface                                                                | 1           |

| 1.2. Physics of Heat Conduction                                             | . 5         |

| 1.3. Components of Thermal Resistance                                       | 9           |

| 2. Microscopic Silicon Heat Sinks: Theory                                   | 13          |

| 2.0.1. The Thermal and Hydrodynamic Boundary Layers                         | 13          |

| 2.1. Elementary Optimization                                                | 15          |

| 2.1.1. General Considerations                                               | 15          |

| 2.1.2. First-Order Design                                                   | 17          |

| 2.1.2.1. Constant-Pressure Constraint                                       | 23          |

| 2.1.2.2. Constant-Pressure, Constant-Fin-Height Constraint                  | 26          |

| 2.1.2.3. Constant-Pumping-Power Constraint                                  | 27          |

| 2.1.3. Discussion                                                           | 29          |

| 2.2. Refinements                                                            | 33          |

| 2.2.1. Developing Thermal Boundary Layer                                    | 33          |

| 2.2.2. Low-Aspect-Ratio Designs (Turbulent Flow)                            | 35          |

| 2.2.3. Friction-Coefficient Corrections                                     | 41          |

| 2.2.3.1. Constant-Pressure Case                                             | 42          |

| 2.2.3.2. Constant-Pumping-Power case                                        | 42          |

| 2.2.4. Nonlinearities in Thermal Resistance                                 | 42          |

| 2.2.5. Thermal Spreading in the Silicon Substrate<br>2.2.6. Ultimate Limits | 45          |

|                                                                             | 47          |

| 3. Microscopic Silicon Heat Sinks: Experiments                              | 49          |

| 3.1. Fabrication                                                            | · <b>49</b> |

| 3.1.1. Silicon Micromachining                                               | 49          |

| 3.1.1.1. Orientation-Dependent Etching                                      | 49          |

| 3.1.1.2. Precision Mechanical Sawing                                        | 54          |

| 3.1.2. Bonding Materials to Silicon                                         | 55          |

| 3.1.3. Heater Resistor Metallization and Contacts                           | 60<br>62    |

| 3.1.4. Packaging and Sealing<br>3.1.5. Procedures                           | 62<br>65    |

| 3.2. Experiments                                                            | 68          |

| 3.2.1. Test Apparatus and Techniques                                        | 68          |

| 3.2.2. Data Analysis and Experimental Errors                                | 70          |

| 3.2.3. Flow-Friction Measurements                                           | 75          |

| 3.2.4. Heat-Transfer Measurements                                           | 80          |

| 3.2.5. Long-Term Reliability                                                | 85          |

| 4. Microcapillary Thermal Interface: Design                                 | 87          |

| 4.1. Background and Prior Art                                               | 87          |

| 4.1.1. Solid Thermal Interfaces                                             | 87          |

| 4.1.2. Gaseous Thermal Interfaces                                           | 90          |

.

.

| 4.2. Principles of Liquid Thermal-Conduction Interfaces | 91  |

|---------------------------------------------------------|-----|

| 4.2.1. The Basic Idea                                   | 91  |

| 4.2.2. Reentrant Grooves                                | 95  |

| 4.3. Interfacial Gap                                    | 99  |

| 4.3.1. Wafer Warpage                                    | 100 |

| 4.3.2. Smooth Plate Deflection Theory                   | 101 |

| 4.3.3. Dust                                             | 103 |

| 4.4. Design                                             | 106 |

| 4.4.1. Choice of liquid                                 | 106 |

| 4.4.2. Capillary Dimensions                             | 108 |

| 5. Microcapillary Interface: Experiments                | 109 |

| 5.1. Fabrication                                        | 109 |

| 5.1.1. Selection of a Fabrication Technique             | 109 |

| 5.1.2. Electroless Nickel Plating                       | 112 |

| 5.1.3. Anomalous Behavior of Electroless Plating        | 115 |

| 5.1.4. Interface Fabrication Procedures                 | 120 |

| 5.2. Experiments                                        | 125 |

| 5.2.1. Measurement Techniques                           | 125 |

| 5.2.2. Thermal Resistance Maps                          | 125 |

| 5.2.3. Hot Spots                                        | 127 |

| 5.2.4. Long-Term Reliability                            | 129 |

| 6. Summary and Conclusions                              | 131 |

| 6.1. Results and Contributions                          | 131 |

| 6.2. Recommendations                                    | 133 |

| 6.2.1. Thermal Considerations                           | 133 |

| 6.2.2. Electrical Considerations                        | 133 |

| 6.3. Other applications                                 | 134 |

| References                                              | 135 |

# List of Figures

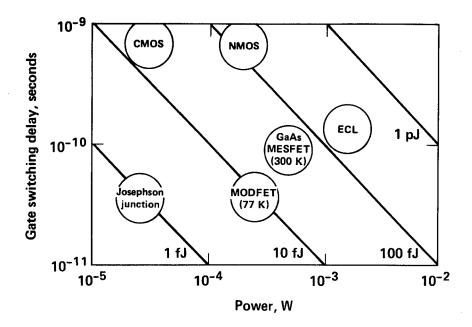

| Figure 1-1: | Speed-power relationships for various logic families (adapted from Ref. [9]).                                                                                                                                                              | 3  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

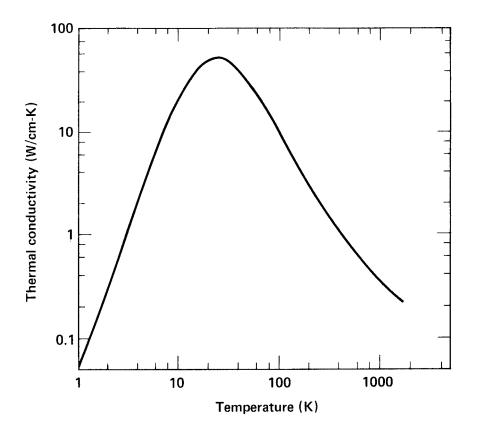

| Figure 1-2: | Thermal conductivity of intrinsic silicon vs. temperature (from Ho [30]).                                                                                                                                                                  | 8  |

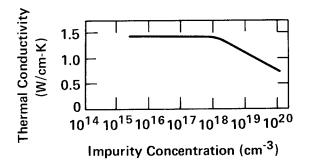

| Figure 1-3: | Thermal conductivity of single-crystal Si vs. impurity concentration at 300 K. Silicon was doped with As, Sb, P, and Ga (data of Arasli and Aliev [31]).                                                                                   | 8  |

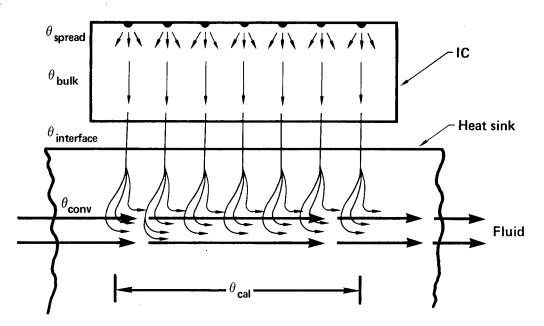

| Figure 1-4: | Components of thermal resistance in convectively cooled ICs.                                                                                                                                                                               | 9  |

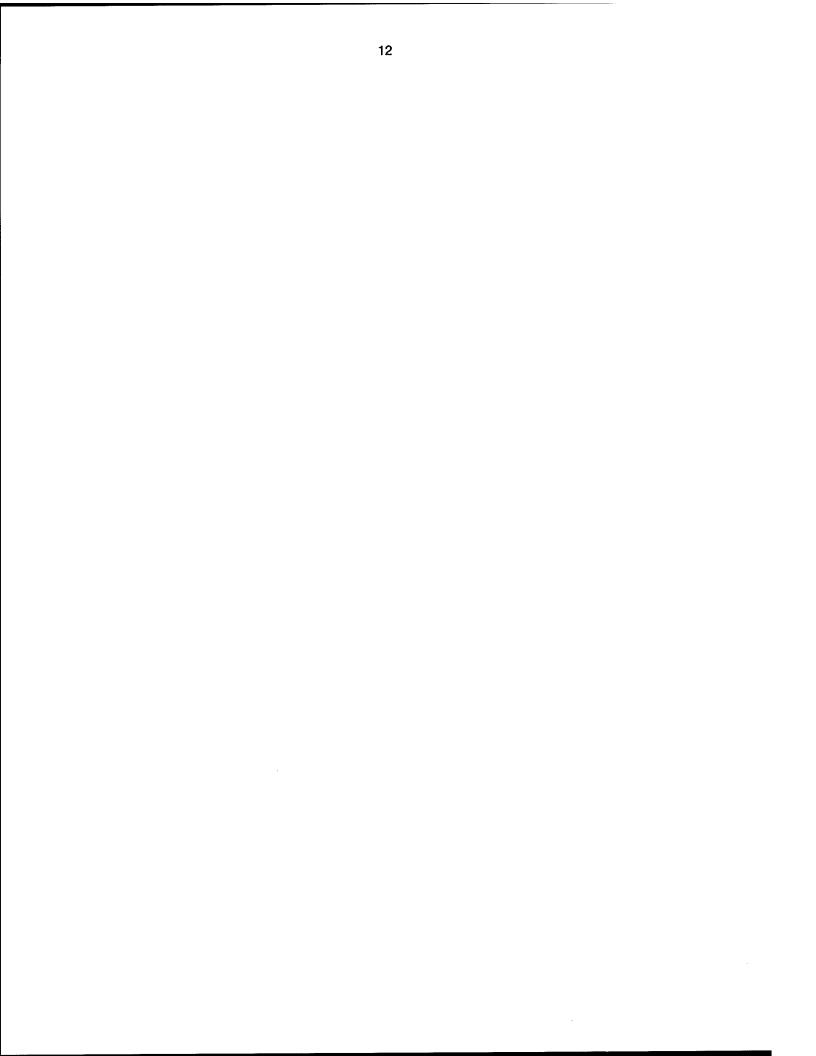

|             | Development of a laminar momentum boundary layer between parallel plates.                                                                                                                                                                  | 13 |

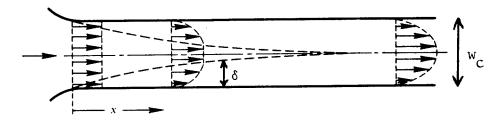

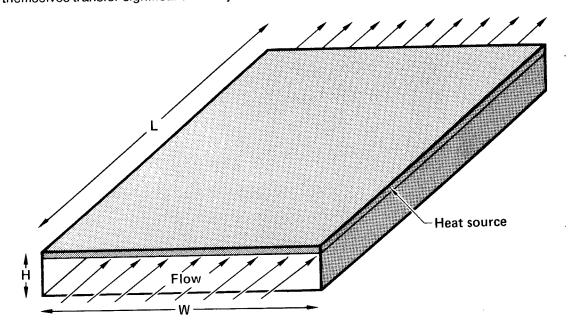

| Figure 2-2: | Schematic of the compact heat sink incorporated into an IC chip.                                                                                                                                                                           | 17 |

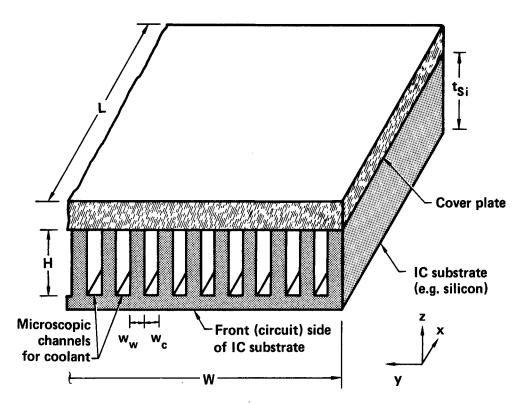

| Figure 2-3: | Local Nusselt number for laminar flow between parallel plates with uniform heat flux, as a function of dimensionless length $L^* \equiv L/(D \cdot \text{Re} \cdot \text{Pr})$ .                                                           | 22 |

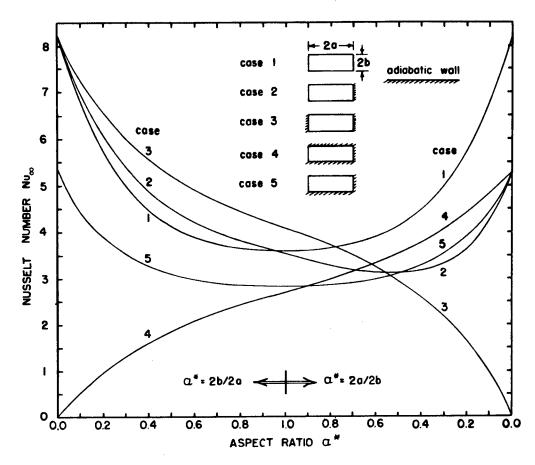

| Figure 2-4: | Uniform-flux Nusselt number for fully-developed laminar flow in rectangular ducts, with one or more walls transferring heat; Nu is based on <u>wetted</u> perimeter (figure courtesy of A. L. London [34]).                                | 23 |

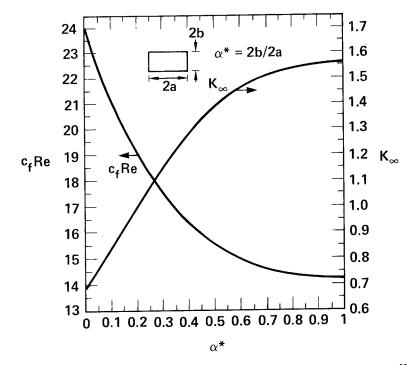

| Figure 2-5: | Normalized friction factor $\Phi \equiv c_f \text{Re}$ and entrance-effect loss factor $K_{\infty}$ for fully-developed laminar flow (Ref. [34]).                                                                                          | 24 |

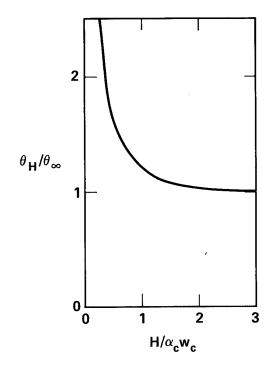

| Figure 2-6: | Optimized thermal resistance as a function of fin height.                                                                                                                                                                                  | 27 |

|             | A simple turbulent-flow cooling duct would be optimal if $Nu \gg k_w/k_c$ .                                                                                                                                                                | 36 |

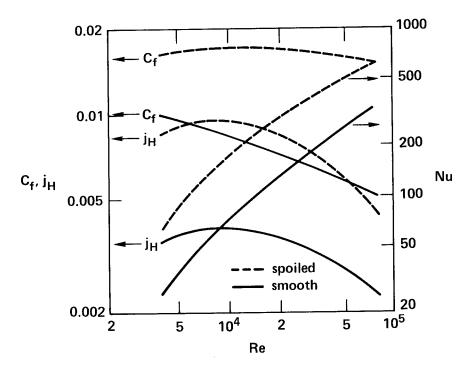

| Figure 2-8: | Nusselt number Nu, Colburn factor $j_{H}$ , and friction factor $c_{f}$ vs. Re for smooth tubes and for optimally roughened (spoiled) surfaces (from Ref. [40]).                                                                           | 38 |

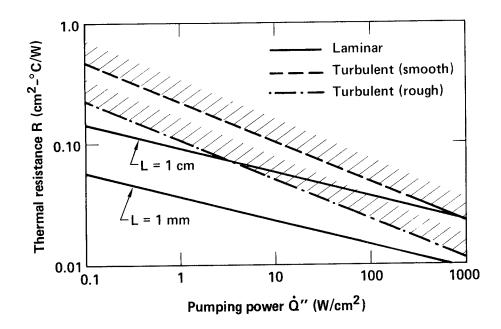

| Figure 2-9: | Optimized thermal resistance R (normalized for $1 \text{ cm}^2$ ) as a function of normalized pumping power Q" for laminar flow (L = 1 cm or 1 mm), and lower bounds for highly turbulent flow with smooth or optimally roughened pipes.   | 40 |

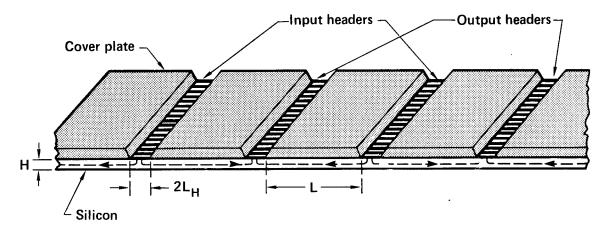

| Figure 2-10 | : A multiple-header arrangement to allow scaling down of the channel length L. The header width $L_H$ should be comparable to the silicon thickness H for proper heat transfer over the header regions.                                    | 47 |

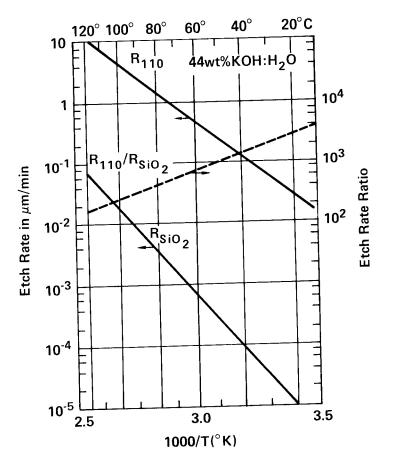

| Figure 3-1: | Etch rate of unobstructed $\langle 110 \rangle$ silicon in KOH. Narrow grooves etch at 70% of these values. Also shown are maximum SiO <sub>2</sub> etch rates (data of Kendall [50]).                                                     | 50 |

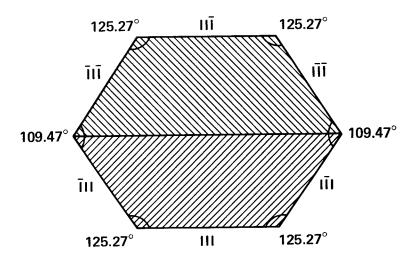

| Figure 3-2: | General shape of the etch pit formed when etching through a small hole in the $SiO_2$ mask covering a <110> silicon wafer using KOH. The pit is bounded on all sides by <111> planes, two pairs of which are perpendicular to the surface. | 52 |

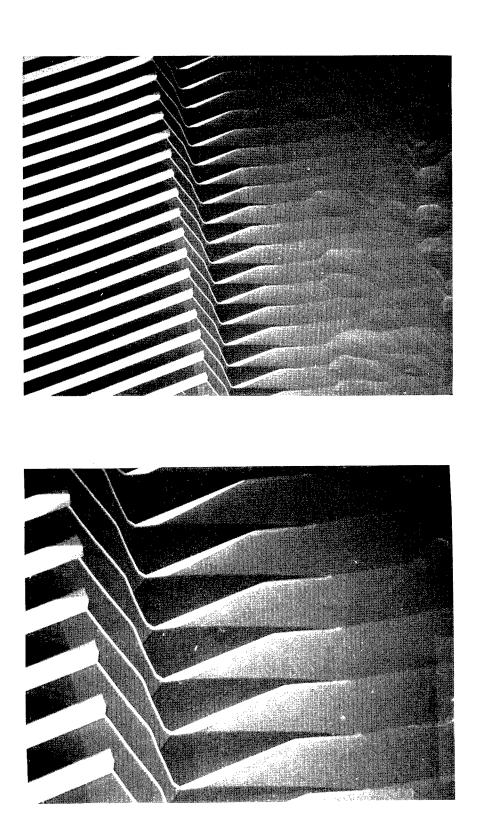

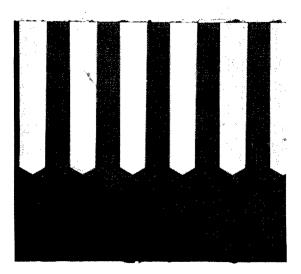

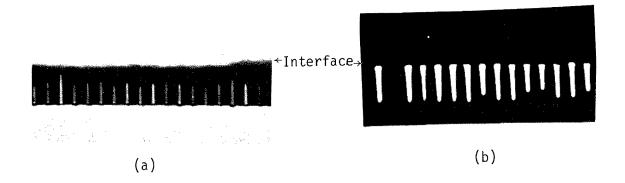

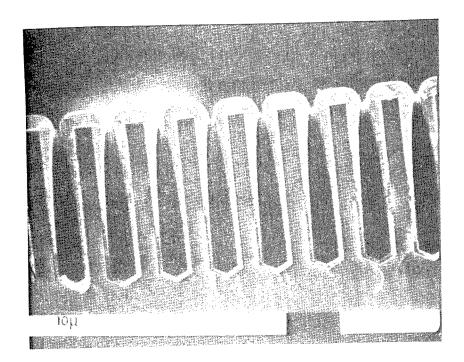

| Figure 3-3: | SEMs of microchannels etched in $\langle 110 \rangle$ silicon using KOH. The spatial period is 100 $\mu$ m.                                                                                                                                | 53 |

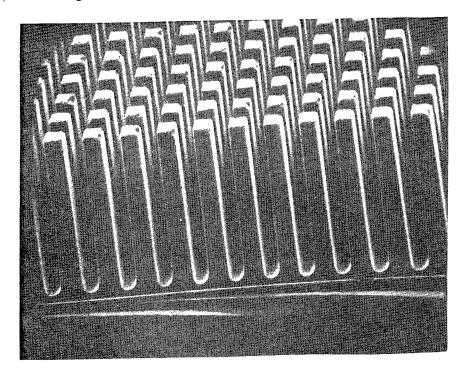

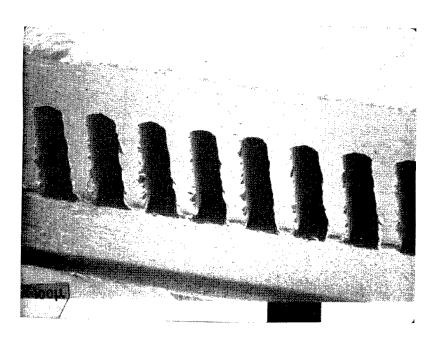

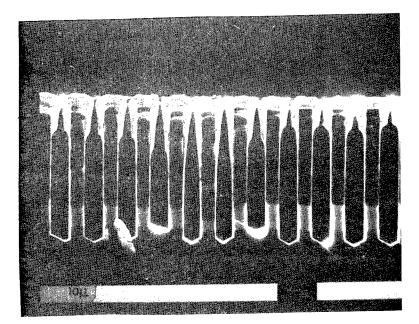

| Figure 3-4: | SEM of rectangular pin-fin structures fabricated in silicon by precision mechanical sawing. The spatial period is 80 $\mu$ m in both directions.                                                                                           | 54 |

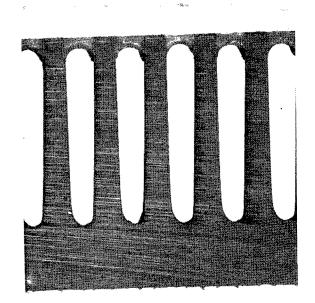

| Figure 3-5:               | Transmission photomicrograph of a silicon microchannel heat sink cross section, where a spin-on epoxy adhesive was used to bond the cover plate. These channels were formed by precision sawing (100 $\mu$ m period). | 56       |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

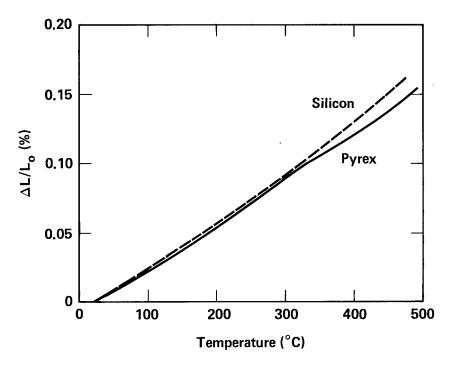

|                           | Linear thermal of expansion of silicon and Pyrex 7740 (from Ref. [60]).                                                                                                                                               | 57<br>59 |

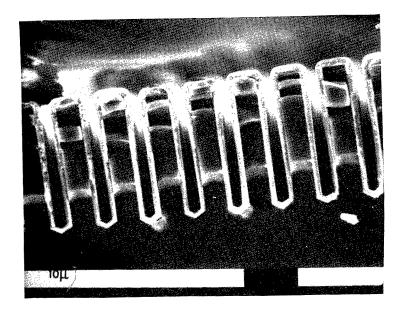

| Figure 3-8:               | SEM of the same microchannel heat sink, viewed at a 45° angle.                                                                                                                                                        | 59       |

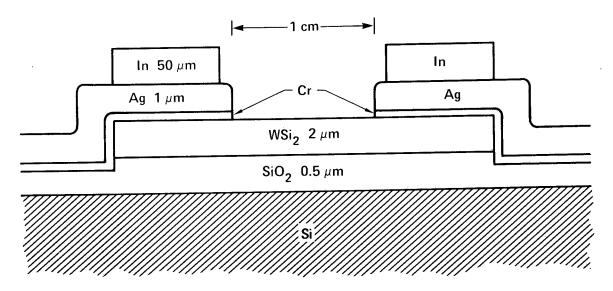

|                           | Metallization used to fabricate heater resistor and contacts.                                                                                                                                                         | 60       |

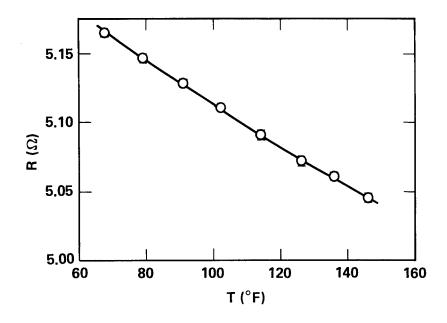

|                           | : Sheet resistance of sputtered WSi <sub>2</sub> (0.95 $\mu$ m, as deposited) vs.                                                                                                                                     | 61       |

| i iguic de los            | temperature.                                                                                                                                                                                                          | -        |

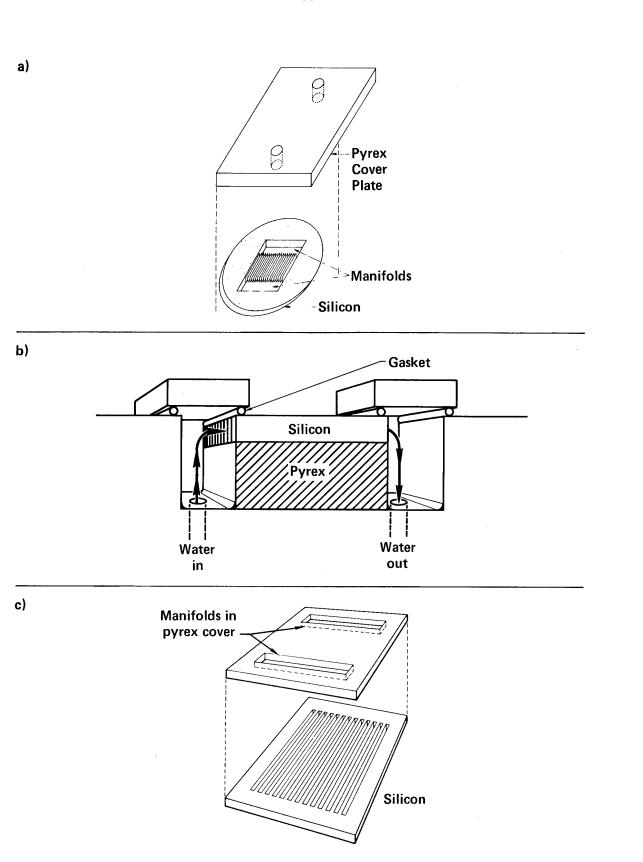

| Figure 2.11               | Several approaches to packaging and headering silicon heat sinks.                                                                                                                                                     | 63       |

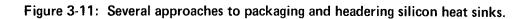

| Figure 3-12:              | -                                                                                                                                                                                                                     | 68       |

| Figure 5-12               | measurements.                                                                                                                                                                                                         |          |

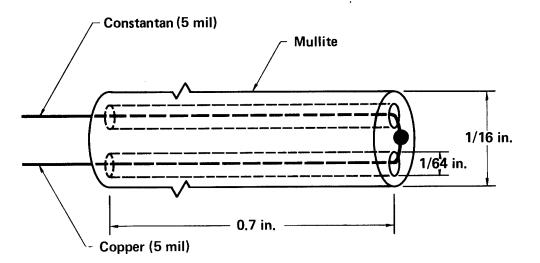

| Figure 2 12               | Thermocouple probe to measure surface temperature. The bead is                                                                                                                                                        | 69       |

| Figure 5-15               |                                                                                                                                                                                                                       | 00       |

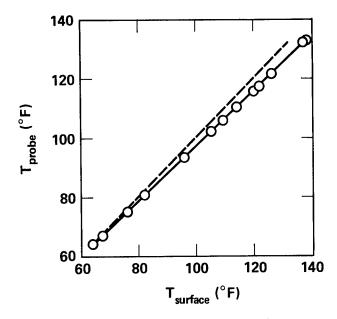

|                           | epoxied flat against the end of the mullite insulator.<br>The manual probability $(T = 67^{\circ}F)$ The dashed line                                                                                                  | 73       |

| Figure 3-14               | : Thermocouple probe calibration ( $T_A = 67^{\circ}$ F). The dashed line                                                                                                                                             | 10       |

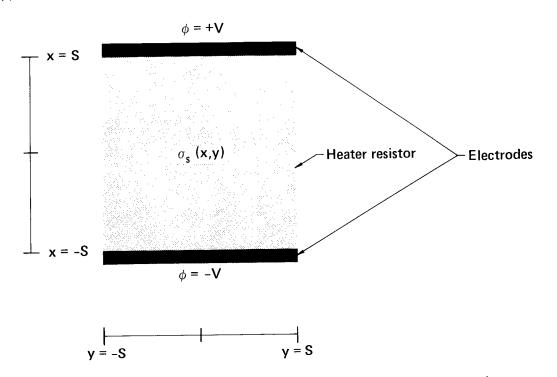

| <b></b>                   | (T <sub>probe</sub> = T <sub>surface</sub> ) would be for a perfectly thermally insulated probe.<br>Notation used to calculate effects of nonuniform heater sheet                                                     | 74       |

| Figure 3-15               |                                                                                                                                                                                                                       | /4       |

|                           | resistance.                                                                                                                                                                                                           | 76       |

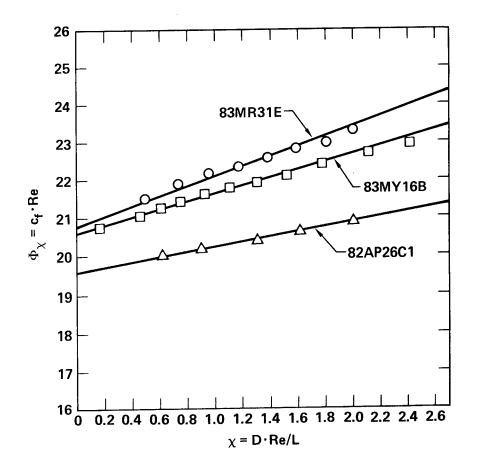

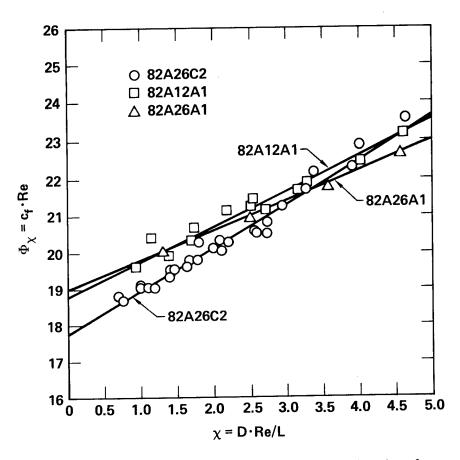

| Figure 3-16               | Flow friction parameter $\Phi_{\chi} \equiv c_f Re$ as a function of $\chi \equiv D \cdot Re/L$ for plate-fin microchannel heat sinks (includes header losses).                                                       | 10       |

|                           |                                                                                                                                                                                                                       | 78       |

| Figure 3-17:              |                                                                                                                                                                                                                       | 10       |

|                           | pin-fin microchannel heat šinks.                                                                                                                                                                                      | 82       |

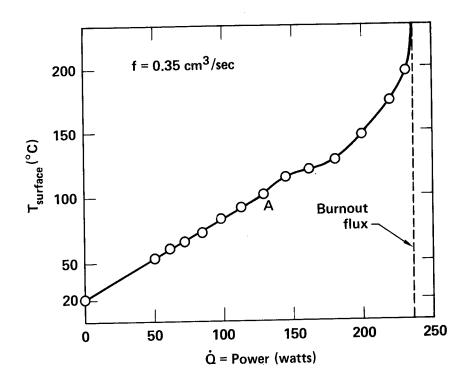

|                           | Temperature vs. power of a heat sink through the boiling regime.                                                                                                                                                      | 83       |

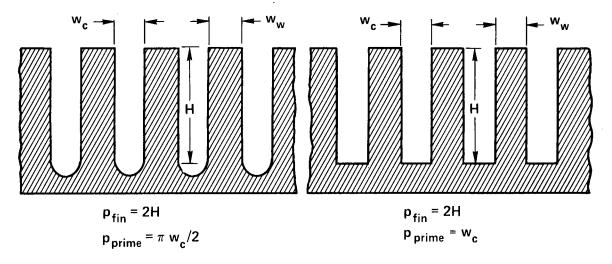

| Figure 3-19:              | Model of sawn grooves (circular bottoms), etched grooves (square bottoms).                                                                                                                                            | 00       |

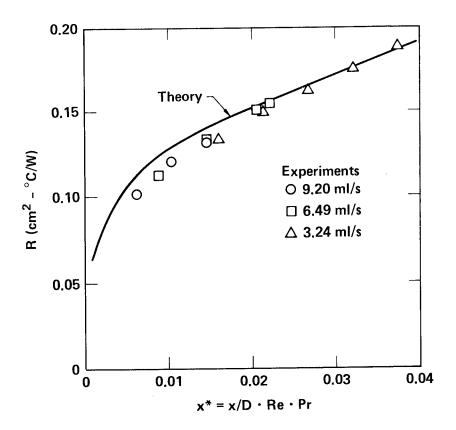

| Eiguro 2.20               | Thermal resistance R vs. dimensionless position x <sup>*</sup> for sample                                                                                                                                             | 84       |

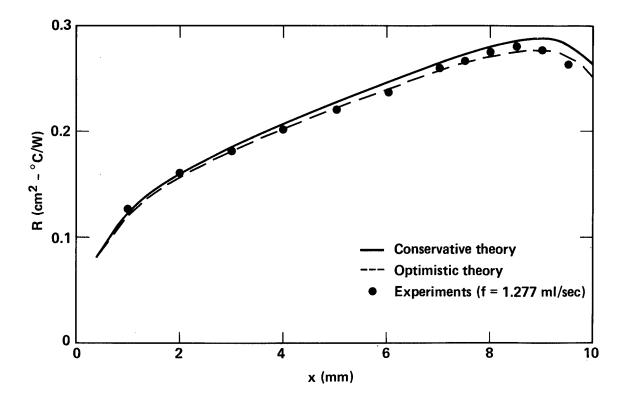

| rigule 5-20               | 82A26A2.                                                                                                                                                                                                              | 0.       |

| Figure 3-21:              |                                                                                                                                                                                                                       | 85       |

| rigure o-z r              | 82A26C1.                                                                                                                                                                                                              | ••       |

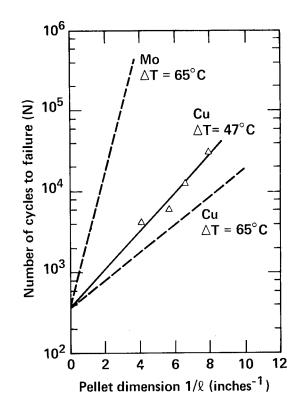

| Figure 4-1:               | Thermal fatigue failure curves for silicon mounted on molybdenum or                                                                                                                                                   | 89       |

| ingalo <u>-</u> in        | copper (from Lang <u>et al</u> [75]).                                                                                                                                                                                 |          |

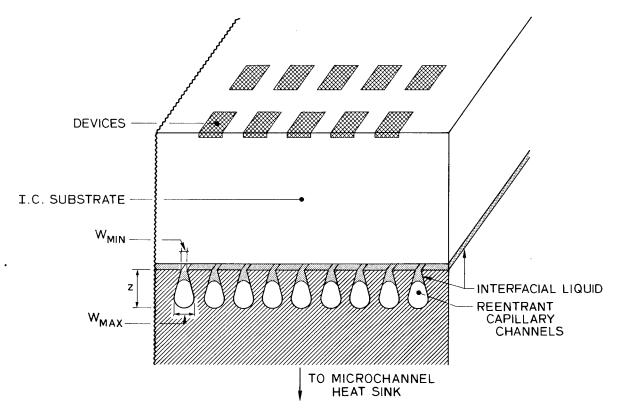

| Figure 4-2.               | Microcapillary thermal interface concept.                                                                                                                                                                             | 92       |

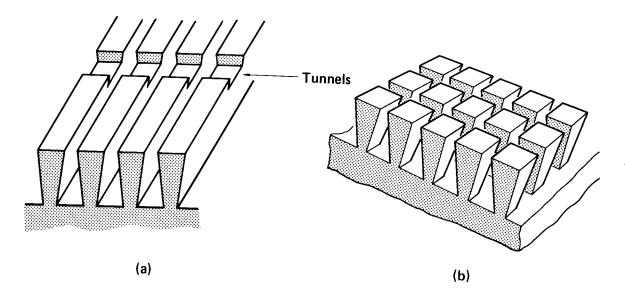

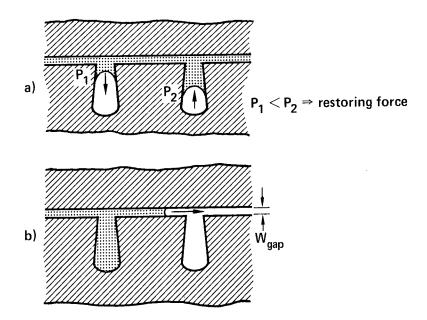

|                           | a) Tunnels between adjacent capillaries facilitate global equilibration                                                                                                                                               | 95       |

|                           | of liquid. b) Proposed two-dimensional array of reentrant grooves.                                                                                                                                                    |          |

| Figure 4-4:               | Capillary stability properties of long reentrant grooves.                                                                                                                                                             | 96       |

|                           | Abruptly-tapered reentrant capillary grooves would also be                                                                                                                                                            | 97       |

| riguro i ol               | acceptable.                                                                                                                                                                                                           |          |

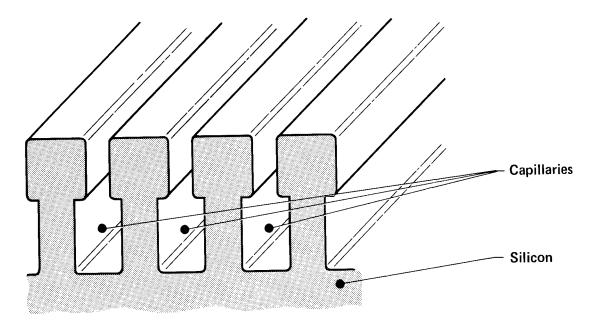

| Figure 4-6:               | (a) Verification of reentrant capillary stability using $30-\mu m$ wide,                                                                                                                                              | 97       |

| i iguio i oi              | $400 \cdot \mu m$ deep reentrant grooves. The menisci show that the interfacial                                                                                                                                       |          |

|                           | oil (dark portions of grooves) congregates near the interface. (b) With                                                                                                                                               |          |

|                           | normally-tapered grooves, the oil congregates away from the                                                                                                                                                           |          |

|                           | interface (at the bottoms of the capillaries).                                                                                                                                                                        |          |

| Figure 4.7.               | SEM of photoresist spun on: a) reentrant microcapillaries, and b)                                                                                                                                                     | 98       |

| · 19010/.                 | conventional-taper microcapillaries.                                                                                                                                                                                  |          |

| Figure 4-8.               | Voids would congregate at local maxima in the gap between planar                                                                                                                                                      | 99       |

| - iguie <del>- </del> .0. | surfaces.                                                                                                                                                                                                             |          |

|                           |                                                                                                                                                                                                                       |          |

viii

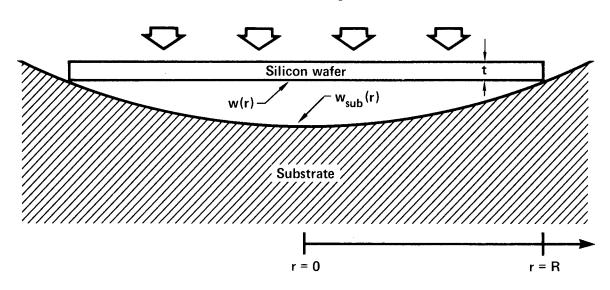

| Figure 4-9: | Deflection of a wafer against a concave substrate under uniform           | 101 |

|-------------|---------------------------------------------------------------------------|-----|

|             | pressure P <sub>2</sub> .                                                 |     |

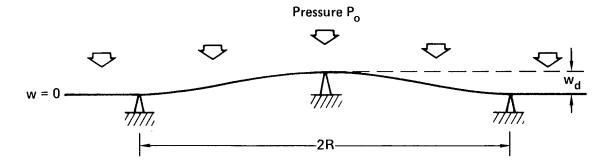

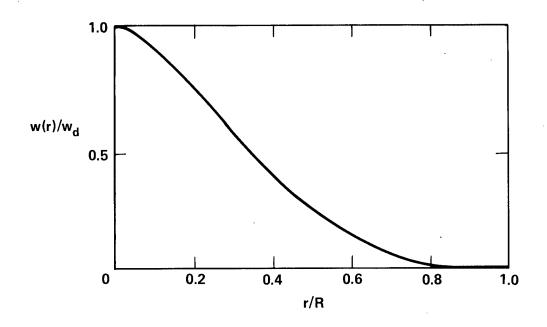

| Figure 4-10 | Elastic plate model of a trapped dust particle.                           | 103 |

| Figure 4-11 | : Predicted plate elevation around a trapped dust particle (Eq. (4.4)).   | 105 |

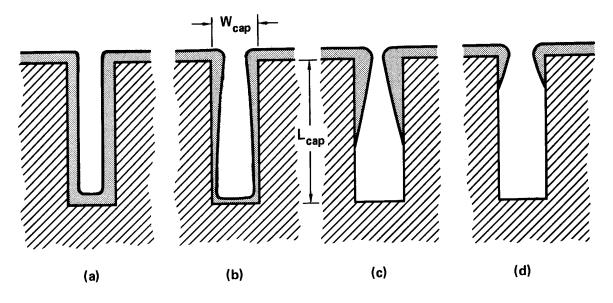

| Figure 5-1: | Isotropic deposition (e.g., CVD, oxidation, or electroless plating)       | 110 |

|             | under various kinetic conditions. In (a), the surface deposition is rate- |     |

| ,           | limiting; in (d), diffusion into the groove is rate-limiting.             |     |

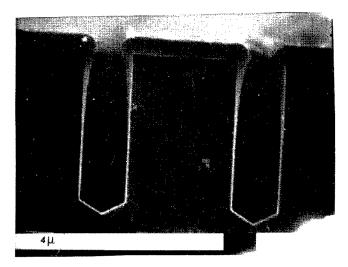

| Figure 5-2: | SEM of CVD-deposited SiO <sub>2</sub> on vertical silicon grooves.        | 111 |

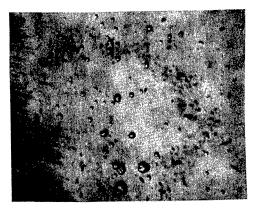

| Figure 5-3: | Hemispherical nickel particles due to impurities (nucleation sites) in    | 113 |

|             | electroless plating solution; magnification $700 \times .$                |     |

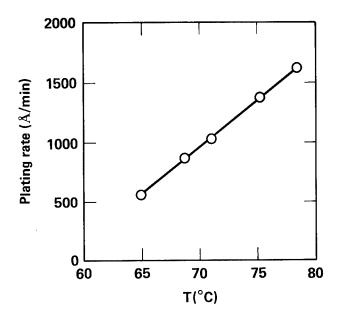

| Figure 5-4: | Measured plating rate vs. temperature of Anomet <sup>®</sup> 24 plating   | 115 |

|             | solution.                                                                 |     |

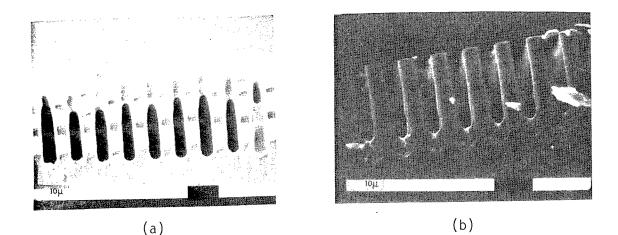

| Figure 5-5: | SEM of silicon grooves electrolessly plated with nickel (sample           | 116 |

|             | 82S29D2).                                                                 |     |

| Figure 5-6: | Anomalous shapes of electrolessly plated grooves, presumably due to       | 116 |

|             | trapped $H_2$ gas bubbles (sample 82D9B2).                                |     |

| Figure 5-7: | Silicon microcapillaries damaged (melted) with an E-beam prior to         | 119 |

|             | plating.                                                                  |     |

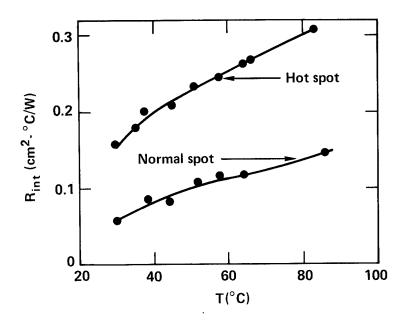

| Figure 5-8: | Thermal resistance vs. temperature of a typical spot and a hot spot.      | 127 |

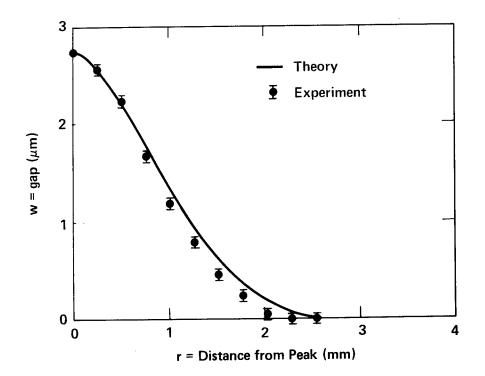

| Figure 5-9: | Interfacial gap near a hot spot (predicted and experimentally             | 128 |

|             | deduced).                                                                 |     |

|             |                                                                           |     |

## List of Tables

•

| Table 1-1: | Typical room-temperature thermal transport parameters (very                        | 6   |

|------------|------------------------------------------------------------------------------------|-----|

|            | approximate).                                                                      | 7   |

| Table 1-2: | Thermal conductivity of various materials; $T = 20-27^{\circ}C$ unless noted.      | 27  |

| Table 2-1: | Optimized dimensions and thermal resistance for various fixed fin                  | 21  |

|            | heights H.                                                                         | 30  |

| Table 2-2: | Coolant Figure of Merit (CFOM) for several fluids at 20-27°C and 1 atm             | 00  |

|            | (unless noted), normalized so that CFOM = 1 for water. The subscripts              |     |

|            | P and Q denote constant-pressure and constant-pumping-power                        |     |

|            | optimization, respectively.                                                        | 45  |

| Table 2-3: | Effects of nonlinear material parameters on optimized $\theta$ (water-cooled       | .0  |

|            | Si).                                                                               | 66  |

| Table 3-1: | Fabrication schedule for silicon microscopic heat sinks                            | 67  |

| Table 3-2: | Standard fabrication subprocedures                                                 | 77  |

| Table 3-3: | Summary of flow-friction properties of plate-fin silicon microchannel              | ••  |

|            | heat sinks.<br>Summary of flow-friction properties of pin-fin silicon microchannel | 79  |

| Table 3-4: |                                                                                    |     |

|            | heat sinks.<br>Maximum (downstream) thermal resistance of various silicon          | 81  |

| Table 3-5: | microchannel heat sinks at maximum tested power.                                   |     |

| Tabla E 11 | Fabrication schedule for microcapillary thermal interfaces                         | 122 |

|            | Fabrication schedule for heater resistor                                           | 124 |

| Table 5-2: | Thermal resistance (R <sub>tot</sub> ) map of a typical chip/interface/heat sink   | 126 |

|            | assembly.                                                                          |     |

| Table 5-4: | Thermal resistance maps $(R_{tot}(x,y))$ before and after 2 million thermal        | 130 |

|            | cycles.                                                                            |     |

|            | -                                                                                  |     |

### List of Symbols

Note: The metric units (e.g. Watts, gm, cm, <sup>o</sup>C, dynes/cm<sup>2</sup>) used in this work are not all standard SI units, but they are traditionally used in the semiconductor industry.

#### **English letter symbols**

- A = silicon substrate area,  $cm^2$ ;

- also, load-bearing area of an entrapped dust particle, cm<sup>2</sup>

- $A_{f} = fin area, cm^{2}$

- $c_{f}$  = local friction coefficient or "friction factor" of channels

- $c_{fm}$  = mean friction coefficient

- C = heat capacity at constant pressure, J/gm-°C

- C<sub>1</sub> = flow coefficient (e.g., of a filter)

- d = effective molecular collision diameter, cm

- D = channel hydraulic diameter =  $4 \cdot (cross-sectional area)/(perimeter)$ , cm; also, elastic plate-deflection modulus D =  $Et^3/[12(1 - \nu^2)]$ , dynes-cm; also, diffusivity of chemical species, cm<sup>2</sup>/sec

- E = elastic (Young's) modulus, dynes/cm<sup>2</sup>

- f = coolant volume flow rate, cm<sup>3</sup>/sec

- F<sub>dust</sub> = force supported by a trapped dust particle between plates, dynes

- G = shear modulus, dynes/cm<sup>2</sup>

- h = convective heat-transfer coefficient, W/cm<sup>2</sup>-K; also, enthalpy of coolant, J/gm

- $h_{IC}$  = effective heat-transfer coefficient from surface of IC, W/cm<sup>2</sup>-K

- H = fin height (in z-direction), cm

- $H_s = t_{si} H$ , residual substrate thickness, cm

- I = current, amperes

- $j_v = heat flux into coolant from fins (in y direction), W/cm<sup>2</sup>$

- $j_{\mu} = Nu/(Re \cdot Pr^{1/3})$ , the Colburn factor

- $J_{-}$  = heat flux up fins (in z direction), W/cm<sup>2</sup>

- $J_{s}$  = sheet current, A/cm

- k = thermal conductivity, W/cm-K

- $k_{\rm B}$  = Boltzmann's constant, 8.617  $\times$  10<sup>-5</sup> eV/K

- $k_c = \text{coolant thermal conductivity, W/cm-K}$

- k<sub>avg</sub> = average thermal conductivity of silicon/coolant aggregate

- (for thermal spreading calculations), W/cm-K

- $k_{eff} = \sqrt{k_c k_w} \cdot 2\sqrt{w_c w_w} / (w_c + w_w), W/cm-K$

- $k_s =$  thermal conductivity of substrate ("wall" or "fin"), usually silicon, W/cm-K

- $k_{\rm B}$  = Boltzmann's constant, 8.617  $\times$  10<sup>-12</sup> eV/K

- $\bar{K}$  = loss coefficient [pressure drop =  $K \cdot (\rho v^2/2)$ ]

- $K_c = contraction loss coefficient (entering a header)$

- K<sub>a</sub> = expansion loss coefficient (exiting a header)

- $K_{\infty}$  = loss coefficient due to development of momentum boundary layer

- L = length of heated area (sometimes equal to L<sub>2</sub>), cm

- $L^*$  = dimensionless channel length, L/(D · Re · Pr)

- L<sub>e</sub> = length of cooling channels (i.e., substrate length), cm

- L<sub>o</sub> = decay length of lateral thermal spreading in silicon heat sink, cm

- $L_{\mu}$  = length of header (in direction of flow), cm

- m = normalized fin height (number of characteristic lengths, seldom exceeds 2); also, molecular mass, gm

- n = number of channels in heat sink

- $Nu = Nusselt number, hD/k_c$

- Nu<sub>x</sub> = local Nusselt number at location x

- Nu<sub>1</sub> = local Nusselt number at location L (output end of channel)

- $Nu_{\infty}$  = Nusselt number for fully-developed temperature profile

- p = perimeter of cooling channel, cm

- P = pressure drop in channels, dynes/cm<sup>2</sup>

- $P_o = suction pressure in microcapillary interface, dynes/cm<sup>2</sup>$

- $P_{core}$  = pressure drop in channels neglecting all entrance and header effects, dynes/cm<sup>2</sup>

- $P_{\infty}$  = stagnation pressure, dynes/cm<sup>2</sup>

- $Pr = Prandtl number = \mu C/k$

- q = heat flow (total heat-transfer rate), W

- q" = heat flux (heat-transfer rate per unit of area), W/cm<sup>2</sup>

- $\dot{Q}$  = mechanical pumping power, W

- $\dot{Q}$ " = mechanical pumping power per unit area of cooled area, W/cm<sup>2</sup>

- $\dot{Q}''_{crit}$  = mechanical pumping power per unit area below which laminar flow designs are believed superior (conservative estimate), W/cm<sup>2</sup>

- r = radius or radial distance, cm

- $R = LW\theta$ , thermal resistance normalized to unit area, cm<sup>2</sup>-°C/W

$$R_{cal} = LW\theta_{cal}, cm^{2.0}C/W$$

$$R_{int} = LW\theta_{ound}, cm^{2.0}C/W$$

$$R = LW\theta$$

,  $cm^2 \cdot {}^{\circ}C/W$

- conv  $R_{int} = LW\theta_{interface}, cm^{2} \circ C/W$   $R_{opt} = LW\theta_{opt}, cm^{2} \circ C/W$

- Re = Reynolds number =  $vD\rho/\mu$

- t = thickness (of silicon, solder, oil, etc. as subscripted), cm; also, time, sec

- $T = temperature (^{\circ}C, ^{\circ}F, or K, as specified)$

- $T_A$  = ambient temperature (refers either to ambient air or to cooling water, depending on context)

- T<sub>Debye</sub> = Debye temperature

- T<sub>c</sub> = mixed mean fluid (coolant) temperature, <sup>o</sup>C or K

- T<sub>i</sub> = semiconductor device (junction) temperature, <sup>o</sup>C or K

- $T_{w}$  = wall (fin) temperature, <sup>o</sup>C or K

- $u_{1}(x) =$  Heaviside step function

- v = velocity (usually a <u>mean</u> fluid velocity unless <u>v</u> is used, in which case it refers to local velocity), cm/sec

- $v_{o}$  = free stream velocity, cm/sec

- $\underline{v}$  = mean velocity, cm/sec

- v<sub>v</sub>(y) = local velocity at position y in x-direction, cm/sec

- V = voltage, V

- $\dot{w}$  = mass flow, gm/sec

- w(r) = vertical deflection of an elastic plate, cm

- w<sub>how</sub> = interfacial gap due to wafer warpage or "bow", cm

- $w_d$  = dust particle elevation, cm

- $w_c = channel width, cm$

- w<sub>m</sub> = microcapillary groove width at meniscus level, cm

- ww = wall width, cm

- W = width of cooled area (perpendicular to direction of flow), cm

- x = distance from input end of channels for flow-friction calculations or from, or start of heated area for heat-transfer calculations (caloric heat-transfer axis), cm

- $x^*$  = dimensionless axial distance along channel, x/(D · Re · Pr)

- x<sup>+</sup> = hydrodynamic entry length, cm

- $x_{th}^{+}$  = thermal entry length, cm

- y = distance from fin surface into coolant (convective heat-transfer axis), cm

- z = distance up from base of fin (conductive heat-transfer axis), cm

#### **Greek letter symbols**

- $\alpha$  = channel surface area enhancement = (channel surface area)/(heated area)

- $\alpha$  = channel aspect ratio, w/H

- $\alpha_{c}$  = "characteristic" value of  $\alpha$ ; the maximum increase in <u>effective</u> heat-transfer area

- $\beta$  = miscellaneous constant

- $\gamma$  = surface tension, ergs/cm<sup>2</sup>, dynes/cm

- $\delta$  = thickness of a momentum boundary layer, cm

- $\delta_{tb}$  = thickness of a thermal boundary layer, cm

- $\Delta$  = designates a difference when used as a prefix

- $\varepsilon = \alpha / \alpha_c$

- $\varepsilon_{th}$  = thermal strain

- $\eta$  = combined temperature effectiveness of finned and prime surfaces

- $\eta_t$  = temperature fin effectiveness factor (finned area)

- $\theta$  = thermal resistance, °C/W

- $\theta_{\text{bulk}}$  = thermal resistance of bulk substrate (e.g., silicon), °C/W

- $\theta_{cal}$  = caloric thermal resistance due to coolant heating, °C/W

- $\theta_{conv}$  = convective thermal resistance, °C/W

- $\theta_{\rm H}$  = optimized thermal resistance for a fixed fin height H, °C/W

- $\theta_{\infty}$  = optimized thermal resistance for an infinite fin height, °C/W

- $\theta_{int}$  = thermal resistance across an interface, °C/W

- $\theta_{opt}^{m}$  = optimized thermal resistance, °C/W

- $\theta_{\text{spread}}$  = thermal spreading resistance, °C/W

- $\Theta_{c}(x,z) = \text{local coolant temperature averaged in y-direction but <u>not</u> in x-direction, <sup>o</sup>C$

- $\kappa$  = thermal diffusivity, k/ $\rho$ C, cm<sup>2</sup>/sec

- $\lambda$  = characteristic heat penetration length up a fin, cm

- $\mu$  = dynamic viscosity, gm/cm-sec (poise)

- v = kinematic viscosity, cm<sup>2</sup>/sec (stokes);

- also, Poisson's ratio ( $\nu = 0.09$  for silicon)

- $\rho = \text{density}, \text{gm/cm}^3;$

- also, radius of curvature, cm;

- also, normalized distance from a dust particle ( $\rho = r/R$ )

- $\sigma$  = tensile stress, dynes/cm<sup>2</sup>

- $\sigma_{rad}$  = Stefan-Boltzmann constant, 5.679×10<sup>-12</sup> W/cm<sup>2</sup>-K<sup>4</sup>

- $\sigma_{0}$  = mean sheet conductivity,  $(\Omega/\Box)^{-1}$

- $\sigma_{x,y}$  = local sheet conductivity,  $(\Omega/\Box)^{-1}$

- $\sigma_{Si}$  = fracture stress of silicon, 3.47  $\times$  10<sup>9</sup> dynes/cm<sup>2</sup>

- $\tau$  = shear stress, dynes/cm<sup>2</sup>

- $\tau_{\rm d}$  = characteristic reaction time for a monolayer of species to deposit

- $\hat{T}$  = dimensionless thermal resistance, k<sub>eff</sub>LW $\theta$ /D

- $\varphi$  = potential, volts

- $\Phi = c_{f\infty}Re$  (product of fully-developed friction factor and Reynolds number)

- $\Phi_{\chi} = c_f Re$  (product of Reynolds number and friction factor at given  $\chi = D \cdot Re/L$

- $\hat{\chi} = D \cdot \text{Re/L}$ , the reciprocal of the Peclet number

- $\omega$  = angular frequency, radians/sec

#### subscripts

- c = coolant

- lam = laminar

- m = mean

- o, opt = optimum design point

- s = refers to heat sink substrate (e.g. silicon)

- th = thermal (as opposed to hydrodynamic)

- turb = turbulent

- w = wall (i.e., fin material)

- $\infty$  = asymptotic (long-channel) limiting value

# Glossary

| chip, die, wafer | Used interchangeably in this work to mean a slice of silicon containing integrated circuits. Unless specified, the size of the slice is arbitrary. |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| CFOM             | Coolant Figure of Merit                                                                                                                            |

| CMOS             | Complementary Metal-Oxide-Semiconductor                                                                                                            |

| ECL              | Emitter-Coupled Logic                                                                                                                              |

| IC               | Integrated Circuit                                                                                                                                 |

| MOS              | Metal-Oxide-Semiconductor                                                                                                                          |

| MTF              | Median Time to Failure                                                                                                                             |

| ODE              | Orientation-Dependent Etching                                                                                                                      |

| RMS              | Root Mean Square                                                                                                                                   |

| SEM              | Scanning Electron Micrograph or Scanning Electron Microscope                                                                                       |

| TCE              | Temperature Coefficient of Expansion                                                                                                               |

| TCR              | Temperature Coefficient of Resistance                                                                                                              |

| VLSI             | Very Large-Scale Integrated or Very Large-Scale Integration                                                                                        |

xv

### Chapter 1 Introduction and Background

#### 1.1. Preface

Ŷ.,

÷.,

The design of modern computing systems comprised of millions of switching elements calls upon a large range of engineering skills and talents. A common and convenient partitioning has evolved between system architects and device designers. Device designers and device physicists concern themselves primarily with the detailed physics of individual devices, in order to produce an optimized logic family. System architects usually deal with the logic gate as their smallest building block; the gate is characterized by its function and propagation delay, but all the physics has been removed from the model. However, in real systems a variety of physical and technological problems arise from the aggregation of large numbers of devices into a system. These system-induced problems are not necessarily anticipated by the device physicist, as they may not arise at small scales of integration. They likely will not be anticipated by the systems architect, because the relevant physical phenomena do not exist at the level of abstraction of a logic gate. Perhaps we should categorize those who work on such problems as "system physicists" (as opposed to device physicists).

One example of a "system physics" problem is system reliability. A single logic device having a median time to failure (MTF) of 100 years may, for practical purposes, be considered perfectly reliable. Yet a system fabricated out of millions of such devices would have an unacceptably short lifetime, assuming a typical failure distribution function and ignoring the possibility of a fault-tolerant design. The physical mechanisms responsible for "hard" failures might be electromigration [1], intermetallic formation, impurity diffusion through dielectrics [2], etc.; "soft" errors could also occur, for example due to alpha particles [3]. The problem of integrated circuit (IC) manufacturing yield might also be considered a system physics problem, and physical phenomena which influence yield continue to be uncovered.

Another system physics problem involves unwanted interactions among nominally independent devices; for example, electromagnetic coupling (crosstalk) between adjacent long, parallel wires on an IC, especially when a ground plane is remote or absent [4]. The

phenomenon of "sneak" paths in memory cells due to parasitic capacitances is another well known example [5]. Often the interaction may not be a problem except when a number of logic gates switch simultaneously; this can cause a power-supply voltage fluctuation due to the presence of a relatively large parasitic resistance or inductance in series with the power bus [6].

- 🛉

1

<u>A</u>.,

Interconnections (wiring) between circuits, both intra-chip and inter-chip, are another system physics problem. The design of suitably compact, low-inductance, low-resistance, low-crosstalk, high-speed <u>inter-chip</u> connectors for high-performance computers has long been a problem to the packaging engineer. More recently, it has become clear that the design of high-speed <u>intra-chip</u> wiring is a formidable problem as critical dimensions are shrunk [7, 8].

Yet another system physics problem is the removal of the heat generated by denselypacked arrays of integrated circuits. That is the subject of this thesis, and much more will be said of it in the following chapters.

The purpose of this preface is to convince the reader of the importance of studying the physical problems associated with large electronic systems. Historically these problems have been addressed whenever they present a major (often unexpected) impediment to system design, but not otherwise. Thus the progress which is made tends to be very incremental, adequately solving the problem at hand but not anticipating future needs. As a consequence, the device and system architects tend to accept the constraints of system physics as fairly firm and not subject to drastic improvements. However, it is a tenet of this thesis that major efforts in improving heat transfer, reliability, yield, device interactions, interconnect technology, and packaging would in many cases benefit system performance far more than would an equivalent amount of time and money spent on improving device design or system architecture.

An important physical problem in computer systems is that of heat dissipation and removal. The heat generated by a single logic gate is small: at most a few milliwatts for most high-speed logic such as ECL; much less for other logic families such as CMOS (Fig. 1-1). When tens or hundreds of thousands of logic gates are fabricated on a single VLSI chip, the total power consumption could conceivably reach the kilowatt level if high-performance logic is used. Even if a low-power logic family is used, a complete high-performance computer system might have  $10^7$  to  $10^8$  switching elements (e.g., transistors) and hence comprise

Figure 1-1: Speed-power relationships for various logic families (adapted from Ref. [9]).

hundreds of chips. If these chips are packed very closely together to minimize propagation delays, the problem of removing tens (or even hundreds) of kilowatts of heat while maintaining normal circuit temperatures (usually less than 120°C; preferably even lower for enhanced reliability) from a system volume of less than 1 liter becomes challenging.

It has been widely claimed that such a heat-removal task is effectively impossible. One pioneer of system physics has estimated that forced air cooling of logic chips is limited to power densities of about 1 W/cm<sup>2</sup>, and that liquid cooling is limited to about 20 W/cm<sup>2</sup> [10, 11]. Another leader in high-speed Josephson systems has stated that with present technology it would be impossible to remove 20 kW from a room-temperature computer having a volume less than 640 cm<sup>3</sup>, and that even a tenfold reduction in power to 2 kW would still present a "difficult, if not impossible" cooling task [12]. Indeed, the best commercial technologies presently available for cooling densely packed arrays of ICs are the IBM Thermal Conduction Module (TCM) [13, 14] and the Honeywell Silent Liquid Integral Cooler (SLIC) [15], both of which are limited to heat fluxes of ~20 W/cm<sup>2</sup>. However, the arguments that this represents a practical limit are not convincing, and we shall show that these estimates are low by at least 2 orders of magnitude.

In this work the physical limits on compact cooling of densely packed arrays are critically examined, and two new technologies are described which allow one to approach these limits. The remainder of Chapter 1 reviews the physics of heat transport in materials, and describes

the components of thermal resistance in conventional integrated circuit packaging. Chapter 2 develops the theory and design optimization of ultracompact liquid-cooled laminar-flow heat sinks (particularly water-cooled silicon), using classical convective heat-transfer theory [16] and compact heat-exchanger theory [17]. Various refinements in the design as well as techniques for further improving performance are discussed. The specific optimization procedures and the suggestion of scaling compact heat-exchanger technology to microscopic duct dimensions ( $\sim$ 50 µm) for cooling IC's are believed to be original. The idea of constructing an integral heat sink in silicon chips is not new [12, 18, 19], but previous workers evidently performance benefits which could result from an optimized micro-heat sink design.

Chapter 3 describes the fabrication and testing of integral silicon micro-heat sinks using variations on conventional IC fabrication technology. The dimensions are about an order of magnitude smaller than in conventional compact heat-exchangers [17, 20]. Accurate flow-friction and heat-transfer measurements were performed. The experiments confirmed the very high performance of the silicon heat sinks, with power levels as high as 1309 W/cm<sup>2</sup> demonstrated at normal operating temperatures. Various portions of the work in Chaps. 2 and 3 have been previously published by the author in Refs. [21], [22], and [23].

Chapter 4 describes the design of a novel, stress-free, detachable thermal interface between ICs and separate micro-heat sinks. The interface uses a liquid as the thermal interface material. The technology would be useful for multi-chip or wafer-scale packaging and/or testing in applications where an integral heat sink is deemed impractical. While liquid thermal interfaces have been suggested previously [24, 25, 26, 27], this configuration is unique in that specially designed microscopic (2- $\mu$ m wide) partially-filled capillaries were used to insure that the interface is void-free and tolerant of mechanical perturbations (flexure), and to maintain a strong, continual suction pressure between the surfaces to correct for wafer warpage.

Chapter 5 describes the fabrication and testing of the microcapillary thermal interface technology devised in Chapter 4. A novel process was developed for fabricating micron-wide reentrant grooves using electroless nickel plating. Very good thermal performance was demonstrated (typical 0.022°C/W thermal resistance for a 1-cm<sup>2</sup> area). Portions of this work have been published previously in Ref. [28].

Chapter 6 briefly summarizes the results and contributions of this work and suggests directions for future research.

#### **1.2.** Physics of Heat Conduction

Heat may be transported by conduction, convection, or radiation; however convection is simply conduction in a moving fluid, so the essential physics is still a conduction process. Radiative heat transport is a negligible factor in cooling of semiconductor devices, because junction temperatures  $T_j$  typically must not exceed 120°C. Thus the maximum possible radiated power is

$\dot{q}" \leq \sigma_{rad} T_j^4 = (5.679 \times 10^{-12} \text{ W/cm}^2 \text{-} \text{K}^4) \cdot (393 \text{ K})^4 = 0.14 \text{ W/cm}^2 \text{,}$  which is a rather small heat flux.

Over distances which are long compared to the mean free path of the dominant heat carrier, heat conduction is described by Fourier's Law and by energy conservation:

$\rho C(\partial T/\partial t) = -\nabla \cdot \dot{\mathbf{q}}^{"} ,$

where k = (thermal conductivity) and  $\rho C$  = (volumetric heat capacity). If the heat carriers have a constant velocity v and mean free path  $\lambda$ , then from elementary kinetic theory [29] one finds that k =  $\rho Cv\lambda/3$ . More generally v is not constant, and we would approximate k $\simeq \rho C v \lambda/3$  where v is an average carrier velocity. Table 1-1 summarizes typical theoretical and experimental values of these parameters for various forms of matter. Although these numbers are highly approximate, they provide insight into why different materials have the thermal conductivities that they do. Table 1-2 lists room-temperature thermal conductivities of some frequently-encountered materials.

For a perfect monatomic gas, the heat carrier is the gas molecule itself, and kinetic theory predicts that

$k = (0.54 k_B^{3/2} T^{1/2}) m^{-1/2} d^{-2}$ ,

where m is the molecular mass, d is the effective molecular collision diameter, and  $k_B$  is Boltzmann's constant. The main point is that light (hence fast) molecules with small collision cross sections have the highest thermal conductivity. Thus helium gas has 5.6 times the thermal conductivity of air.

The high thermal conductivity of crystalline metals can be understood in view of the electron's very high velocity ( $\sim 10^8$  cm/sec) due to its light mass, and the its long mean free

| Type of Material            | ρC                                                                                                                            | ⊻<br>⊻                                                                      | λ                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------|

| Gases                       | (3/2)k <sub>B</sub> n<br>(monatomic)                                                                                          | $\sqrt{8k_{B}T/\pi m}$<br>( $\sim 10^{5} cm/sec$ )                          | $(\sqrt{2}\pi d^2 n)^{-1}$<br>(60-300 nm, at STP) |

| Metals (crystalline)        | ρC <sub>el</sub> $\simeq$ 4.9(T/T <sub>F</sub> )k <sub>B</sub> n<br>(T <sub>F</sub> $\simeq$ 2-17 $\times$ 10 <sup>4</sup> K) |                                                                             | ⊻ <sub>el</sub> ≁ <sub>el-ph</sub><br>(5-100 nm)  |

| Insulators (crystalline)    | 3k <sub>B</sub> n                                                                                                             | $\underline{v}_{ph} = c_{sound}$<br>( $\sim 5 \times 10^5 \text{ cm/sec}$ ) | ⊻ <sub>ph</sub> ≁ <sub>ph-ph</sub><br>(2-50 nm)   |

| Liquids or Amorphous Solids | varies (~k <sub>B</sub> n)                                                                                                    | c <sub>sound</sub><br>(∼10 <sup>5</sup> cm/sec)                             | intermolecular dist.<br>(0.5 nm)                  |

Notes:  $T_F =$  Fermi temperature,  $c_{sound} =$  speed of sound, n = # atoms/cm<sup>3</sup>,  $\tau =$  mean collision time with phonons,  $m_e =$  mass of electron.

Table 1-1: Typical room-temperature thermal transport parameters (very approximate).

path. The high thermal conductivity of crystalline insulators such as silicon (thermal conductivity 1/3 that of copper) or diamond (5 times that of copper) at room temperatures is due to the relatively long phonon mean free paths, comparable in magnitude to electron mean free paths in crystalline metals. Although the phonon velocity (speed of sound) is 2 or 3 orders of magnitude less than electron velocities, the phonon (lattice) heat capacity of an insulator is much greater than the electronic heat capacity of a metal, at room temperature. Note that amorphous substances (e.g., liquids or glasses) have thermal conductivities 2 or 3 orders of magnitude less than their crystalline counterparts; this is due to the reduction of the electron or phonon mean free path to intermolecular distances.

The thermal conductivity of silicon will be of particular interest to us; Fig. 1-2 plots it as a function of temperature. The rapid rise in thermal conductivity with decreasing temperature is due to the dramatic increase in phonon mean-free-path length (the phonon population diminishes exponentially with temperature when  $T \ll T_{Debye}$ ). As shown in Fig. 1-3, silicon's room-temperature thermal conductivity is reduced somewhat by doping with impurity concentrations greater than  $10^{18}$  cm<sup>-3</sup>. The average phonon mean free path  $\lambda$  at  $25^{\circ}$ C may be approximated from Eq. 1.1 as

|                     | Material             | k (W/cm-K) |

|---------------------|----------------------|------------|

| Gases:              | Air                  | .00026     |

|                     | Helium               | .00145     |

| Liquids:            | Water                | .0061      |

|                     | Silicone oil (typ.)  | .0015      |

|                     | Nitrogen @ 77 K      | .00140     |

|                     | Mercury              | .0830      |

|                     |                      |            |

| Nonmetallic Solids: | Pyrex                | 0.0109     |

|                     | Carbon (amorphous)   | 0.0159     |

|                     | Carbon (diamond IIA) | 23.2       |

|                     | Silicon (intrinsic)  | 1.48       |

|                     | GaAs                 | 0.54       |

|                     |                      |            |

| Metallic Solids:    | Copper               | 4.01       |

|                     | Aluminum             | 2.35       |

|                     | Stainless Steel      | 0.18       |

Table 1-2: Thermal conductivity of various materials; T = 20-27°C unless noted.

$\lambda = 3k/\rho Cv = 3(1.48 \text{ W/cm-K})/(1.64 \text{ J/cm}^3\text{-K})(9.0 \times 10^5 \text{ cm/sec}) = 300 \text{ Angstroms.}$

Since this is much smaller than any device structures of present interest, we shall use Fourier's law without any corrections from the microscopic theory of heat flow. It should be noted that direct measurement of phonon mean free path lengths by means of transmited phonon drag have found much longer lengths (several microns at room temperature) [32]. However, these phonons are presumably very long-wavelength ones, and due to the low density of states they do not make a major contribution to the heat conduction process.

Figure 1-2: Thermal conductivity of intrinsic silicon vs. temperature (from Ho [30]).

Figure 1-3: Thermal conductivity of single-crystal Si vs. impurity concentration at 300 K. Silicon was doped with As, Sb, P, and Ga (data of Arasli and Aliev [31]).

#### **1.3. Components of Thermal Resistance**

The performance of a convective heat-transfer system for integrated circuits is measured by its thermal resistance  $\theta = \Delta T/\dot{q}$ , where  $\Delta T$  is the temperature rise of the circuit above ambient, and  $\dot{q}$  is the IC power dissipation. This formalism is primarily useful when the heat transfer is a linear problem, i.e.,  $\theta$  is independent of temperature. This is often a good approximation in forced convection cooling systems. For cooling semiconductor integrated circuits,  $\theta$  is in general the sum of 5 components (Fig. 1-4):  $\theta_{spread}$ , the spreading resistance from the individual heat-generating devices in the semiconductor substrate;  $\theta_{bulk}$ , due to heat conduction through the bulk semiconductor;  $\theta_{interface}$ , the thermal resistance associated with the IC/heat-sink interface (if any);  $\theta_{conv}$ , the convective thermal resistance between the heat sink and the coolant fluid; and  $\theta_{cal}$ , the "caloric" thermal resistance due to the heating of the fluid as it absorbs energy passing through the heat sink. We now examine these components to determine which of them present the most fundamental impediments to the compact removal of high heat flux.

Figure 1-4: Components of thermal resistance in convectively cooled ICs.

Of these 5 components of thermal resistance,  $\theta_{\text{bulk}}$  is the easiest to minimize. For silicon substrates,  $\theta_{\text{bulk}} = t_{\text{Si}}/k_{\text{Si}}A$  where  $t_{\text{Si}} = (\text{silicon substrate thickness})$  and A = (substrate area). Thus if a 1-cm<sup>2</sup> IC substrate is thinned to 100  $\mu$ m, then  $\theta_{\text{bulk}} = .007^{\circ}\text{C/W}$  at room temperature, which is very small; furthermore there is no fundamental limit to thinning the

substrate even further (down to the thickness of the active device layers, which seldom exceed 20  $\mu$ m even in bipolar technology).

The caloric thermal resistance  $\theta_{cal}$  also has a very simple form:  $\theta_{cal} = 1/\rho Cf$  where  $\rho C$  is the volumetric heat capacity and f is the volume flow rate. Obviously  $\theta_{cal}$  is made small by choosing a coolant fluid having high volumetric heat capacity (water is one of the best;  $\rho C = 4.18 \text{ J/}^{\circ}\text{C}\cdot\text{cm}^{3}$ ) and using a very high flow rate. For example, 10 cm<sup>3</sup>/sec of water provides a caloric thermal resistance of only 0.024°C/W. The limits on reducing  $\theta_{cal}$  will be determined by the maximum fluid flow rate, which in turn is set by the fluid mechanics of the problem (to be discussed in Chapter 2).

Thermal spreading resistance  $\theta_{spread}$  is sometimes quoted as an important limiting thermal resistance. However, for the high levels of integration (more than 10<sup>5</sup> devices/cm<sup>2</sup>) which are contemplated, it is only a minor contributor, and becomes relatively less important as device dimensions are scaled down. The thermal spreading resistance of a plane square (dimensions  $L_i \times L_i$ ) heat source embedded in the surface of a silicon substrate has been calculated [33] to be  $\theta_{spread} = 0.56/k_{Si}L_{j}$ , which for a  $L_{j} = 2 \mu m$  heat source works out to be  $\theta_{\rm spread}$  = 1.9°C/mW for each device. A somewhat lower figure is obtained if the heat source is hemispherical rather than planar; then  $\theta_{spread} = 1/\pi k_{Si}L_{j} = 1.1 \text{ °C/mW}$ . (The actual value for a real device is presumably somewhere in between). Now we believe that for electrical (not thermal) reasons it is unlikely that VLSI integrated circuits would be designed for power densities greater than 1000 W/cm<sup>2</sup> (present practice is under 20 W/cm<sup>2</sup>). Thus for densities exceeding 10<sup>5</sup>/cm<sup>2</sup>, one must design devices which consume an average of less than 10 mW each; hence the device temperature rise due to thermal spreading would be less than 20°C, which is usually acceptable. The situation improves as devices are scaled down, because in order to maintain the power density at or below 1000 W/cm<sup>2</sup>, the device power must scale as  $L_i^{-2}$ , whereas the thermal spreading resistance  $\theta_{spread}$  increases only as L, hence the temperature rise will decrease as L<sup>-1</sup>. Of course specific devices such as off-chip driver transistors may substantially exceed the average device power level, but these could be dealt with specially (say, by paralleling a number of smaller-area transistors instead of fabricating one large-area transistor).

The remaining components of thermal resistance are the convective ( $\theta_{conv}$ ) and interfacial ( $\theta_{interface}$ ) components. These are the most difficult ones to optimize in practical, compact computer systems, and in fact one or both of them usually dominate the overall thermal resistance. The optimization of these thermal resistances for semiconductor ICs is the main

subject of this work. Note that one can conceive of eliminating  $\theta_{int}$  entirely by constructing a heat exchanger as an integral part of the heat-generating circuits; this is the approach taken in Chapters 2 and 3. If this is not practical, a variety of approaches exist for making high-performance thermal interfaces between ICs and heat sinks; Chapters 4 and 5 describe a new technique for doing so which avoids many of the limitations of conventional die attachment techniques.

## Chapter 2 Microscopic Silicon Heat Sinks: Theory

This chapter describes the design and optimization procedures for microscopic silicon liquid-cooled heat sinks. The first section briefly reviews some aspects of convective heat-transfer theory which will motivate the design of microscopic liquid-cooled heat sinks for compact cooling of semiconductors. Our discussion will be brief and appeal to intuition; a detailed exposition may be found in the book by Kays and Crawford [16]. All subsequent sections assume familiarity with Ref. [16] or equivalent texts.

#### 2.0.1. The Thermal and Hydrodynamic Boundary Layers

When a fluid having a free-stream velocity of  $v_0$  flows past a solid surface or "wall" (e.g., a flat plate, or the inside of a pipe), the fluid velocity will be constrained to be zero at the wall (the "no-slip" boundary condition). The velocity therefore varies from zero at the wall to  $v_0$  far from the wall, and the region near the wall over which the majority of the transition occurs is called the hydrodynamic boundary layer or the momentum boundary layer. The boundary layer thickness will increase as one moves downstream until its growth is constrained by another nearby wall (e.g., laminar flow in a pipe) or by the mixing action of turbulent eddies (in the case of turbulent flow). Fig. 2-1 is a sketch of the development of a laminar momentum boundary layer in the hydrodynamic entry region of a flow between parallel plates.

Figure 2-1: Development of a laminar momentum boundary layer between parallel plates.

The approximate functional form of the laminar boundary layer thickness can be deduced by a simple argument. Referring to Fig. 2-1, we define the position along the wall in the

direction of flow as x (x = 0 at the entrance), and the boundary layer thickness as  $\delta$ . Momentum transfer in fluids occurs by diffusion, where the diffusion constant is the kinematic viscosity v (units of cm<sup>2</sup>/sec);  $v = \mu/\rho$  where  $\mu$  is viscosity and  $\rho$  is density. Thus the information that the fluid velocity at the wall is zero propagates transversely in the flowing liquid by a diffusion process. In an elapsed time t, this information will be primarily confined within a diffusion length (vt)<sup>1/2</sup>; this is the approximate boundary layer thickness  $\delta$ . Since the fluid free-stream velocity is  $v_{o}$ , the fluid outside the boundary layer will have moved a distance x = v<sub>o</sub>t in the direction of flow; but since  $\delta \simeq (vt)^{1/2}$ , we can eliminate t and we conclude that  $\delta \simeq (\nu x / v_o)^{1/2}$ , i.e., the hydrodynamic boundary layer thickness grows as the square root of x. We might consider the velocity profile to be "fully developed" at the position  $x^+$  where this approximate analysis shows  $\delta$  to be equal to one-half the plate spacing (i.e., the boundary layers merge at the center of the flow). That is,  $\delta = w_c/2$ , where  $w_c$  is the spacing between the parallel walls. Defining the hydraulic diameter D of this parallel-plate pipe in accordance with convention, we have  $D = 4 \cdot (cross-sectional area)/(perimeter) = 2w_c$ . Solving for x<sup>+</sup> gives  $x^+ \simeq v_o D\rho/16\mu = D \cdot Re/16$ , where  $Re = v_o D\rho/\mu$  is the Reynolds number. Thus we see that the laminar hydrodynamic entry length should be proportional to the product of the hydraulic diameter D and the Reynolds number Re. Detailed numerical calculations [34] show the actual hydrodynamic entry length  $x^+$  for laminar flow through a pipe to be typically  $x^+ \simeq .05$  (D · Re). Here  $x^+$  is defined as the distance beyond which the local friction coefficient (proportional to the shear stress at the wall) is within 2% of its final value.

When a fluid flows through a pipe having a wall temperature  $T_w$  which is greater than the mixed mean temperature  $T_c$  of the fluid, heat is transported to the fluid. Since the temperature of the fluid in contact with the wall must be continuous (hence equal to  $T_w$ ), there will develop a thermal boundary layer (in analogy to the momentum boundary layer) over which the major part of the temperature transition from  $T_w$  to  $T_c$  occurs. Again, the heat is transported by a diffusion process; the diffusion constant is the thermal diffusivity  $\kappa = k_c/\rho C$  where  $k_c$  is the fluid's thermal conductivity and  $\rho C$  is its volumetric heat capacity. In a time interval t, the heat will diffuse transversely into the coolant stream a diffusion length  $\delta_{th} \simeq (\kappa t)^{1/2}$ ; this is the approximate thermal boundary layer thickness. If we assume that the velocity profile is laminar and fully developed (parabolic), then the velocity gradient can be approximated as linear near the wall: for parallel plates,  $dx/dt = v_x \simeq 12 \underline{vy}/D$ , where  $\underline{v}$  is the mean velocity and y is the distance from the wall. So setting  $y = \delta_{th}$  and integrating with respect to time, we get  $\delta_{th} \simeq (\kappa D x/8 \underline{v})^{1/3}$ . Thus we see that the thermal boundary layer thickness grows as the **cube root** of x.

As before, the boundary layer might be considered to be fully developed when  $\delta_{th} \simeq w_c/2 = D/4$ ; solving for the thermal entry length gives  $x_{th}^+ \simeq D \cdot \text{Re} \cdot \text{Pr/8}$  where  $\text{Pr} = v/\kappa$ . More precisely, numerical calculations [34] show that the heat transfer typically approaches within 2% of its asymptotic limit when  $x \gtrsim 02(D \cdot \text{Re} \cdot \text{Pr})$ .

To summarize: the laminar momentum boundary layer thickness grows as  $x^{1/2}$ , and is fully developed in a pipe of hydraulic diameter D when  $x \gtrsim .05(D \cdot Re)$ . The thermal boundary layer thickness grows as  $x^{1/3}$ , and is fully developed when  $x \gtrsim .02(D \cdot Re \cdot Pr)$ . Since  $Pr \gg 1$  for nonmetallic liquids, the hydrodynamic boundary layer is fully developed substantially before the thermal boundary layer.

#### 2.1. Elementary Optimization

We now describe the basic optimization procedure which led to the design of microscopic heat sinks. Many approximations and simplifications were made to arrive at the first-order design described here; they will be examined more critically in Section 2.2.

#### 2.1.1. General Considerations