AIN SHAMS UNIVERSITY FACULTY OF ENGINEERING Computer and Systems Engineering

### Homomorphic Encryption for Secure Data Computations

A Thesis submitted in partial fulfillment of the requirements of Master of Science in Electrical Engineering (Computer and Systems Engineering)

by

Mohamed Tarek Ibn Ziad Mohamed Hassan Bachelor of Science in Electrical Engineering

(Computer and Systems Engineering) Faculty of Engineering, Ain Shams University, 2014

Supervised By Dr. Hassan Mohamed Shehata Bedour Dr. Yousra Mohsen Ali Alkabani

Cairo, 2017

AIN SHAMS UNIVERSITY FACULTY OF ENGINEERING Computer and Systems Engineering

**Examiners' Committee**

Name: Mohamed Tarek Ibn Ziad Mohamed Hassan Thesis: Homomorphic Encryption for Secure Data Computations Degree: Master of Science in Electrical Engineering (Computer and Systems Engineering)

| Name and affiliation                                                                                                                                      | Signature |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|

| <b>Prof. Dr. Hossam Aly Hassan Fahmy</b><br>Prof. at Electronics and Communications Engineering Dept.<br>Faculty of Engineering, Cairo University.        |           |  |

| <b>Prof. Dr. Mohamed Watheq Ali Kamel El-Kharashi</b><br>Prof. at Computer and Systems Engineering Dept.<br>Faculty of Engineering, Ain shams University. |           |  |

| <b>Dr. Hassan Mohamed Shehata Bedour</b><br>Associative Prof. at Computer and Systems Engineering Dept.<br>Faculty of Engineering, Ain shams University.  |           |  |

Date: June 2017

## Statement

This Thesis is submitted as a partial fulfillment of Master of Science in Electrical Engineering, Faculty of Engineering, Ain shams University. The author carried out the work included in this Thesis, and no part of it has been submitted for a degree or a qualification at any other scientific entity.

Mohamed Tarek Ibn Ziad Mohamed Hassan Signature

Date: 01 June 2017

## **Researcher Data**

Name: Mohamed Tarek Ibn Ziad Mohamed Hassan

Date of Birth: 25/06/1992

Place of Birth: Cairo, Egypt

Last academic degree: Bachelor of Science

Field of specialization: Electrical Engineering

University issued the degree : Ain Shams University

Date of issued degree : 07/2014

Current job : Teaching Assistant at the Faculty of Engineering, Ain Shams University

### Abstract

The tremendously increasing amount of the available data nowadays opens the door to using third parties to handle data storage and processing. This raises many concerns regarding end-users' privacy and whether the targeted third parties are trusted or not. On the one hand, end-users, either clients or organizations, cannot afford the cost and complexity of processing their own data by their local trusted components. On the other hand, depending only on third parties, such as cloud computing services, with no security guarantee in mind, will be more like building castles out of mud. One possible solution for the former issue is using homomorphic encryption (HE) techniques. These techniques allow third party services to compute over data while the data itself remains encrypted. Thus, one can make use of the great computational power offered by third parties without sacrificing his/her own privacy.

HE could be categorized into two main categories; partially homomorphic encryption (PHE), and fully homomorphic encryption (FHE). While FHE can help solve privacy issues completely, it introduces high performance overhead. To avoid such overhead, PHE can be used. Thus, the main goal of this Thesis is to "*explore the efficiency of using PHE techniques in solving real-world problems, in which computing over encrypted data is a must*".

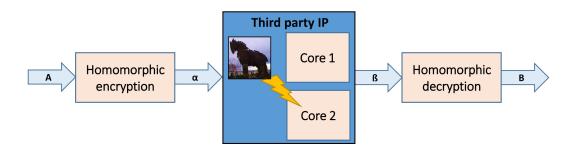

The contributions of this Thesis are multi-fold. We selected three different domains of applications; securing electronic voting (e-voting) systems, defeating Hardware Trojans (HTs) in FPGA-based designs, and operating blindly over encrypted images. The common part of all the above different domains is the availability of secure data that needs to be processed by third parties without being revealed.

In the context of *securing e-voting systems*, we implement an FPGA-based e-voting system, which uses a VGA screen and a Xilinx Spartan 3E FPGA board as a voting site and a remote server to collect results. We launch a couple of attacks on the system by injecting an HT in our e-voting machine to tamper with the voting results. We show the role of HE in securing our design via the usage of ElGamal cryptosystem. Protection techniques are proposed and implemented. Then, they are evaluated by showing their delay, power, and area overheads. The reported power overhead is negligible, the delay overhead does not exceed 10%, and the device resources overhead does not exceed 4%.

In the context of *defeating HTs in FPGA-based designs*, we implement two designs that support PHE (multiplicative only and additive only) based on ElGamal encryption/decryption scheme. Furthermore, we integrate the two designs together and introduce a dual-circuit design that achieves a higher improvement in area and power than a regular design that combines the two original separated designs. Our architectures are implemented on a Spartan-6 FPGA board from Xilinx. The area reduction reached 30% and savings in power consumption were 20% for encryption and 12% for decryption.

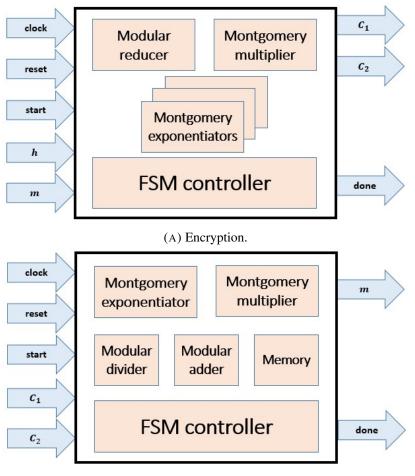

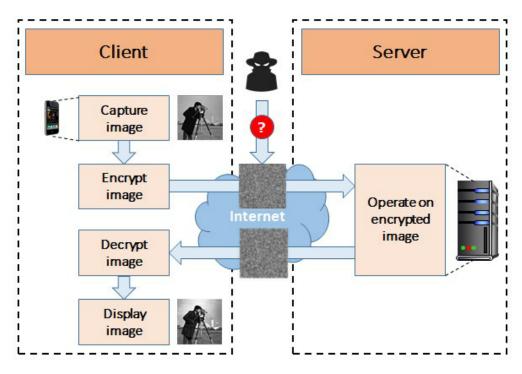

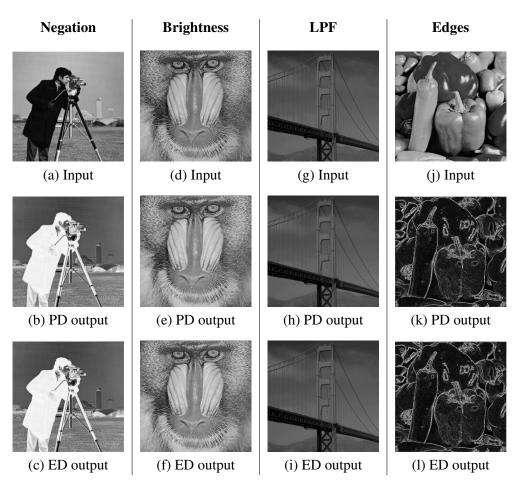

In the context of *operating blindly over encrypted images*, we introduce *CryptoImg*, a library of modular privacy preserving image processing operations over encrypted images using the homomorphic properties of Paillier cryptosystem. Secure operations, such as image adjustment, spatial filtering, edge sharpening, edge detection, morphological operations, and histogram equalization, are safely outsourced to third-party servers with no privacy issues. We present how these operations can be implemented with much less time overhead, and a single communication round. *CryptoImg* can be used from either mobile or desktop clients with low client-side overheads. Experiments show the efficiency of our proposed library. For instance, the image negation operation in the encrypted domain requires less than one minute with zero error using 1024-bit key size.

To conclude, the Thesis successfully managed to show the efficiency of using PHE techniques, such as ElGamal and Paillier, as a replacement of FHE ones in three different real-world problems, which require computing over encrypted data. The overheads accompanied by using such techniques are reasonable compared to the huge overheads of the FHE techniques reported in the literature.

### **Summary**

Encryption is the art of converting text messages into a secret code using a certain encryption key. Hundreds of years ago, people used to propose new encryption algorithms to secure their own data and protect their privacy. Unfortunately, once the data is encrypted, it would remain in its secret-useless form till a certain key is used to decrypt it. Homomorphic encryption is the kind of encryption that permits one to perform useful computations on encrypted data without decrypting them. The results of these computations are equivalent to the results of the similar computations done over the plain data. By this way, one could safely allow third parties to make useful computations over his own data without scarifying his privacy.

Building on the above description, the Thesis aims at exploring the efficiency of using homomorphic encryption techniques in solving real-world problems, in which computing over encrypted data is a must. Although homomorphic encryption includes two different categories; the fully homomorphic encryption techniques, and the partially homomorphic encryption ones, the Thesis focuses on the second category only. The reason behind this research direction is to avoid the high overheads associated with the usage of fully homomorphic encryption methods.

The Thesis is divided into six chapters, along with the table of contents, list of figures, list of tables, abbreviations, symbols, and the references.

The Thesis contents are presented hereafter.

<u>Chapter 1</u> presents the introduction to the Thesis. It mainly highlights the motivation behind the proposed work. It also states the Thesis contributions, which span through three different applications. Each contribution/application is illustrated in a separate chapter with its experimental setup and numerical results.

<u>Chapter 2</u> describes the needed background about homomorphism and surveys existing fully and partially homomorphic encryption schemes. It mainly focuses on the two partially homomorphic cryptosystems, used in this work; ElGamal and Paillier.

<u>Chapter 3</u> illustrates the first Thesis contribution, which is using homomorphism in E-voting systems. It introduces a couple of possible attacks and countermeasures to an FPGA-based voting machine. The full hardware implementation is described and the countermeasures overheads are highlighted.

<u>Chapter 4</u> introduces the second contribution, which is securing FPGA-based designs from Hardware Trojans using homomorphism. The Thesis implements two partially homomorphic encryption designs based on ElGamal encryption/decryption scheme. The first design is a multiplicative homomorphic, whereas the second one is an additive homomorphic. The design realization on a low-cost FPGA is described and the area/timing results are reported.

<u>Chapter 5</u> describes the third contribution, which is a cloud-based library, *CryptoImg*, which allows performing image processing operations over encrypted images. New algorithms are introduced and the communication/computation overhead are stated using various test cases.

<u>Chapter 6</u> concludes the work, states the list of contributions, and discusses some possible future work directions.

### Keywords

Electronic voting, ElGamal Encryption, Fully homomorphic encryption, Hardware Trojans, Homomorphism, Image Processing, Paillier Encryption, Partially homomorphic encryption, Secure computations.

## Acknowledgment

All praise is due to Allah, Most Merciful, the Lord of the Worlds, Who taught man what he knew out. I would like to thank God almighty for bestowing upon me the chance, strength and ability to complete this work.

I always struggle writing acknowledgments because words cannot do justice to my gratitude. However, I will do my best. I wish to express my deep gratitude to my advisors, Dr. Hassan Mohamed Shehata Bedour and Dr. Yousra Mohsen Ali Alkabani for their guidance and important remarks on the developed results and the written manuscript. I was greatly inspired by their excitement, vision, and creativity. I would also like to thank Prof. Mohamed Watheq Ali Kamel El-Kharashi for his constant and enthusiastic support.

I would also like to thank the following researchers from University of California Los Angeles (UCLA), Amr Alanwar, Moustafa Alzantot, and Mani Srivastava, for their help on the development and review of *CryptoImg*, discussed in Chapter 5.

I am always thankful to my parents for their unfailing help along my life and for their efforts during the Thesis development. I am also thankful to my wonderful friends who make me enjoy a lot of aspects of life outside of work.

Mohamed Tarek Ibn Ziad Mohamed Hassan Computer and Systems Engineering Department Faculty of Engineering Ain Shams University Cairo, Egypt June 2017

# Contents

| Abstract              | ix    |

|-----------------------|-------|

| Summary               | xi    |

| Acknowledgment        | xiii  |

| Table of Contents     | xiv   |

| List of Figures       | xix   |

| List of Tables        | xxi   |

| List of Abbreviations | xxiii |

| List of Symbols       | XXV   |

| 1 | Intr | troduction                         |   |  |

|---|------|------------------------------------|---|--|

|   | 1.1  | Motivation                         | 1 |  |

|   | 1.2  |                                    | 2 |  |

|   | 1.3  | Thesis Organization                | 3 |  |

| 2 | Bac  | sground                            | 5 |  |

|   | 2.1  | Fully Homomorphic Encryption (FHE) | 5 |  |

|   | 2.2  |                                    | 7 |  |

|   |      |                                    | 8 |  |

|   |      |                                    | 9 |  |

|   |      |                                    | 9 |  |

|   | 2.3  | Hardware Trojan                    | 1 |  |

|   | 2.4  | Hardware Trojan Taxonomy 12        | 1 |  |

|   |      | 2.4.1 Phase of Insertion           |   |  |

|   |      | 2.4.2 Level of Abstraction         |   |  |

|   |      | 2.4.3 Methods of Activation        |   |  |

|   |      | 2.4.4 Effects                      | - |  |

|   |      | 2.4.5         Location         10  | - |  |

|   |      |                                    |   |  |

### 3 E-voting Attacks and Countermeasures

|   | 3.1               | Motivation                                                                     | 18              |

|---|-------------------|--------------------------------------------------------------------------------|-----------------|

|   | 3.2               | Related Work                                                                   | 19              |

|   | 3.3               | E-voting System Overview                                                       | 21              |

|   | 3.4               | Scenario for a Possible Attack                                                 | 23              |

|   | 3.5               | Protection Against Proposed Attack                                             | 24              |

|   | 3.6               | Other Attacks and Countermeasures                                              | 25              |

|   |                   | 3.6.1 Sequence Cheat Code Attack                                               | 26              |

|   |                   | 3.6.2 Used Bits Attack                                                         | 26              |

|   | 3.7               | Evaluation                                                                     | 28              |

|   |                   | 3.7.1 Experimental Setup                                                       | 28              |

|   |                   | 3.7.2 E-voting Protection Results                                              | 29              |

|   |                   | 3.7.2.1 Resetting Unused Bits                                                  | 29              |

|   |                   | 3.7.2.2 Using Enhanced SB Method                                               | 31              |

|   | 3.8               | Conclusion                                                                     | 32              |

| 4 | Han               | an ambie Date Isolation for Protection against Handware Tusians                | <b></b>         |

| 4 | <b>Hon</b><br>4.1 | nomorphic Data Isolation for Protection against Hardware Trojans<br>Motivation | <b>33</b><br>34 |

|   | 4.1               | Related Work                                                                   | 34<br>34        |

|   | 4.2               | HT Protection using PHE Overview                                               | 36              |

|   | 4.3               | HT Protection using PHE Methods                                                | 30              |

|   | 4.4               | 4.4.1 Sufficient PHE Support                                                   | 37              |

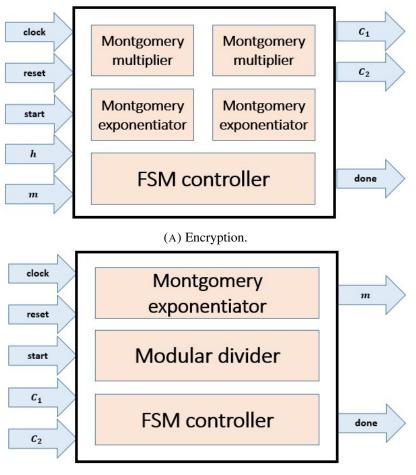

|   |                   | 4.4.1.1 ElGamal Scheme Implementation                                          | 38              |

|   |                   | 4.4.1.2 CEG Scheme Implementation                                              | 39              |

|   |                   | 4.4.2 Dual-Circuit Design                                                      | 40              |

|   | 4.5               | Evaluation                                                                     | 41              |

|   | ч.5               | 4.5.1 Experimental Setup                                                       | 41              |

|   |                   | 4.5.2 PHE Methods Results                                                      | 42              |

|   |                   | 4.5.3 Dual-Circuit Design Results                                              | 42              |

|   | 4.6               | Conclusion                                                                     | 45              |

|   |                   |                                                                                |                 |

| 5 |                   | otoImg: Privacy Preserving Processing over Encrypted Images                    | 47              |

|   | 5.1               | Motivation                                                                     | 48              |

|   | 5.2               | Related Work                                                                   | 49              |

|   | 5.3               | CryptoImg System Overview                                                      | 50              |

|   | 5.4               | Secure Operations in Encrypted Domain                                          | 52              |

|   |                   | 5.4.1 Secure Image Adjustment                                                  | 52              |

|   |                   | 5.4.2 Secure Noise Reduction                                                   | 53              |

|   |                   | 5.4.3 Secure Edge Detection and Sharpening                                     | 54              |

|   |                   | 5.4.4 Secure Morphological Operations                                          | 55              |

|   | ~ ~               | 5.4.5 Secure Histogram Equalization                                            | 56              |

|   | 5.5               | Evaluation                                                                     | 56              |

|   |                   | 5.5.1 Experimental Setup                                                       | 56              |

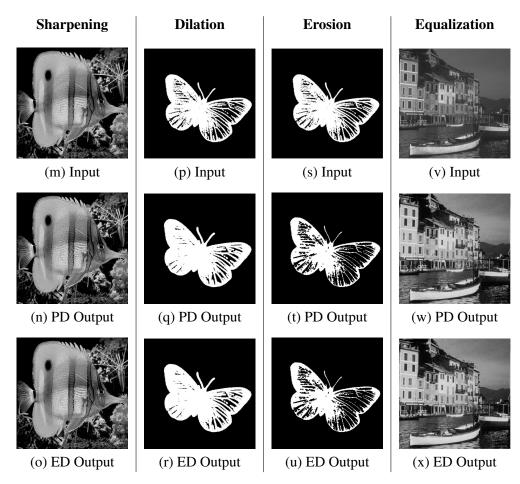

|   |                   | 5.5.2 Visual Output Results                                                    | 57              |

|   |                   | 5.5.3 Computation Time Results                                                 | 59              |

|   | 5.6               | Conclusion                                                                     | 61              |

| 6 | Conclusion and Future Work |        |                           |  |  |  |

|---|----------------------------|--------|---------------------------|--|--|--|

|   | 6.1                        | Conclu | usion                     |  |  |  |

|   | 6.2                        | Contri | butions                   |  |  |  |

|   |                            | 6.2.1  | Secure E-voting           |  |  |  |

|   |                            | 6.2.2  | Secure FPGA-based Designs |  |  |  |

|   |                            | 6.2.3  | Secure Image Processing   |  |  |  |

|   | 6.3                        | Future | Work                      |  |  |  |

|   |                            | 6.3.1  | Secure E-voting           |  |  |  |

|   |                            | 6.3.2  | Secure FPGA-based Designs |  |  |  |

|   |                            | 6.3.3  | Secure Image Processing   |  |  |  |

### Bibliography

67

# **List of Figures**

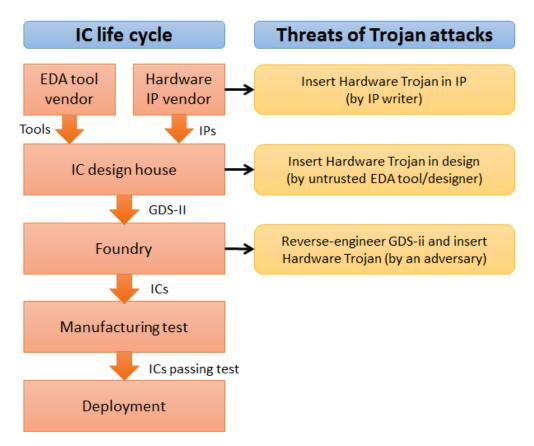

| 2.1  | Possible stages for launching Hardware Trojan attacks by third parties.     | 12 |

|------|-----------------------------------------------------------------------------|----|

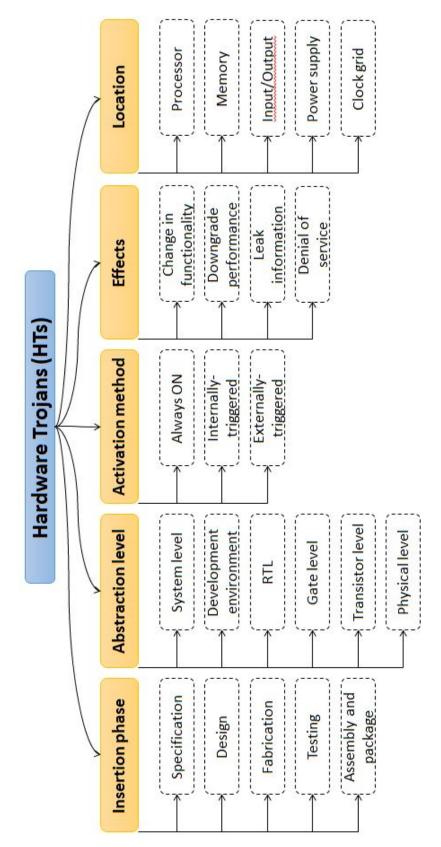

| 2.2  | Hardware Trojan taxonomy.                                                   | 13 |

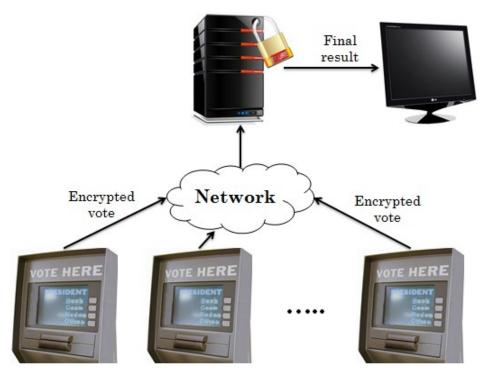

| 3.1  | E-voting versus regular voting.                                             | 19 |

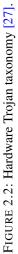

| 3.2  | The e-voting process.                                                       | 22 |

| 3.3  | Abstract view of our proposed e-voting machine.                             | 22 |

| 3.4  | MicroBlaze block diagram.                                                   | 23 |

| 3.5  | Block diagram of using a malicious secret core within an untrusted e-       |    |

|      | voting machine.                                                             | 24 |

| 3.6  | Simple obfuscating function depending on data xoring                        | 25 |

| 3.7  | Inverse obfuscating function in order to retrieve data.                     | 25 |

| 3.8  | E-voting protection against proposed attack.                                | 25 |

| 3.9  | Experimental setup for the e-voting system.                                 | 28 |

| 3.10 | The Xilinx Spartan 3E starter kit overview.                                 | 29 |

| 4.1  | Homomorphic encryption to protect from Hardware Trojans                     | 37 |

| 4.2  | Block diagram for ElGamal encryption/decryption scheme                      | 38 |

| 4.3  | Block diagram for the CRT-based ElGamal (CEG) encryption/decryp-            |    |

|      | tion scheme                                                                 | 40 |

| 5.1  | System Architecture of <i>CryptoImg</i> .                                   | 51 |

| 5.2  | The different edge detection operators supported by <i>CryptoImg</i>        | 54 |

| 5.3  | Visual output evaluation for the first operations set applied in PD and ED. | 57 |

| 5.4  | Visual output evaluation for the second operations set applied in PD and    |    |

|      | ED                                                                          | 58 |

# **List of Tables**

| 3.1 | Device utilization comparison for resetting unused bits method                         | 30 |

|-----|----------------------------------------------------------------------------------------|----|

| 3.2 | Power comparison for resetting unused bits method                                      | 30 |

| 3.3 | Device utilization comparison for enhanced Simple Blockage method.                     | 31 |

| 3.4 | Power comparison for enhanced Simple Blockage method                                   | 31 |

| 4.1 | Resource utilization of ElGamal and CEG schemes.                                       | 42 |

| 4.2 | Timing performance of ElGamal and CEG schemes                                          | 42 |

| 4.3 | Power consumption (mW) of ElGamal and CEG encryption/decryption schemes.               | 43 |

| 4.4 | Area reduction of our dual ElGamal design over the regular ElGamal design.             | 43 |

| 4.5 | Timing comparisons between our dual ElGamal design and the regular ElGamal design.     | 44 |

| 4.6 | Power consumption (mW) of our dual ElGamal design and the regular ElGamal design.      | 44 |

| 5.1 | Precision effect on the introduced <i>CryptoImg</i> error                              | 59 |

| 5.2 | Execution Time (sec) of the Paillier encryption/decryption of an image.                | 60 |

| 5.3 | Execution Time (sec) of the proposed <i>CryptoImg</i> operations on different clients. | 60 |

# **List of Abbreviations**

| AES             | Advanced Encryption Standard            |

|-----------------|-----------------------------------------|

| ASIC            | Application Specific Integrated Circuit |

| CBIR            | Content-Based Image Retrieval           |

| CEG             | CRT-based ElGamal                       |

| CRC             | Cyclic Redundancy Check                 |

| CRT             | Chinese Remainder Theorem               |

| DCR             | Decisional Composite Residuosity        |

| DLP             | Discrete Logarithm Problem              |

| DoS             | Denial of Service                       |

| ED              | Encrypted Domain                        |

| EDA             | Electronic Design Automation            |

| EM              | Estimation Maximization                 |

| EN              | Encoding Function                       |

| <b>E-voting</b> | Electronic voting                       |

| EVM             | Electronic Voting Machine               |

| FHE             | Fully Homomorphic Encryption            |

| FP              | Floating Point                          |

| FSM             | Finite State Machine                    |

| FSL             | Fast Simplex Link                       |

| НТ              | Hardware Trojan                         |

| IP              | Intellectual Property                   |

| ISE             | Integrated Synthesis Environment        |

| JTAG            | Joint Test Action Group                 |

| LPF             | Low Pass Filter                         |

| LWE             | Learning With Errors                    |

|                 |                                         |

xxiii

| Mob  | Mobile device                     |

|------|-----------------------------------|

| NLM  | Non-Local Means                   |

| OS   | Operating System                  |

| PC   | Personal Computer                 |

| PD   | Plaintext Domain                  |

| PHE  | Partially Homomorphic Encryption  |

| PCB  | Printed Circuit Board             |

| RO   | Ring Oscillators                  |

| RISC | Reduced Instruction Set Computer  |

| RLWE | Ring Learning With Errors         |

| RNS  | Residue-Number System             |

| RSA  | Rivest-Shamir-Adleman             |

| RTL  | Register Transfer Level           |

| SaaS | Software-as-a-Service             |

| SB   | Simple Blockage                   |

| SIFT | Scale-Invariant Feature Transform |

| SMC  | Secure Multi-party Computation    |

| SRAM | Static Read Access Memory         |

| SSS  | Shamir's Secret Sharing           |

| SHE  | Somewhat Homomorphic Encryption   |

| TRNG | True Random Number Generator      |

| XPA  | Xilinx Power Analyzer             |

| XPS  | Xilinx Platform Studio            |

# **List of Symbols**

| С            | ciphertext message               |

|--------------|----------------------------------|

| F            | frequency                        |

| $G_{x}$      | horizontal gradient component    |

| $G_y$        | vertical gradient component      |

| 8            | generator                        |

| $h_1$        | horizontal kernel                |

| $h_2$        | vertical kernel                  |

| Ι            | image                            |

| i            | image pixel                      |

| k            | secret random exponent           |

| l            | secret random exponent           |

| т            | plaintext message                |

| п            | prime number                     |

| 0            | image pixel                      |

| r            | secret random exponent           |

| R            | result image                     |

| Т            | image transformation             |

| x            | plaintext number                 |

| Θ            | gradient direction               |

| $\phi_{add}$ | addition operation error         |

| $\phi_{mul}$ | multiplication operation error   |

| $\otimes$    | self binding over floats         |

| $\oplus$     | additive homomorphic over floats |

To my princess

### **Chapter 1**

## Introduction

The principal target of our introductory chapter is to highlight the motivation behind this work, state the main contributions of the Thesis, and define its organization.

### **1.1 Motivation**

The keyword "Homomorphism" originally comes from the concatenation of two ancient Greek words; *homos*, which means "same", and *morphe*, which means "shape" or "form" [1]. So, homomorphism could be interpreted as "the same shape". The word was first used in algebra, where it means a certain transformation of one algebraic set to another one preserving all the relations between the first set elements in the second one too [2]. In the domain of cryptography, Homomorphism is used along with encryption. Homomorphic encryption is the notation used to describe the kind of encryption, which can be used to perform different arithmetic operations on encrypted data to directly obtain an encrypted result. Thus, using such encryption techniques enables the execution of specific computations, while maintaining the privacy of both the input data and the results. Depending on the number of arithmetic computations that are supported by an algorithm, a homomorphic encryption can be considered as either fully homomorphic encryption (FHE) or partially homomorphic encryption (PHE).

Nowadays, the homomorphic property of various cryptosystems, such as ElGamal and Paillier encryption schemes, is used to build many applications, such as secure voting systems [3], introduce privacy-preserving face recognition [4], fingerprint recognition [5], zero-knowledge watermarking [6], and location-based services. Furthermore, the use of cloud computing services, in which computations performed on user data are outsourced to a public cloud, raises the need for a final solution to maintain the privacy of user data. On one hand, clients have many privacy and security concerns over their data. On the other hand, third-parties are vulnerable to malicious interventions or monitoring like hacking or eavesdropping. Combining those two opposite requirements together establishes one of the main motivations behind this work.

While FHE can help solve privacy issues, it is also desirable to reduce the performance overhead introduced by such methods. Thus, it is a good practice to utilize PHE techniques in the desired applications, instead of the FHE ones, to avoid such overheads. As a result, we started this research with the aim of designing and implementing efficient algorithms to use homomorphic encryption techniques in performing secure computations over encrypted data. We selected three different areas of applications; securing electronic voting (e-voting) systems, defeating Hardware Trojans (HTs) in FPGA-based designs, and operating blindly over encrypted images. We only used PHE techniques to reach our goals, as will be shown in coming chapters.

### **1.2 Main Contributions**

The contributions of this Thesis could be categorized into three main parts as follows:

### 1. Secure e-voting

- (a) Implementing an e-voting machine using Xilinx FPGA board.

- (b) Injecting an HT within the FPGA design to tamper voting results.

- (c) Providing a protection technique against the proposed attack.

- (d) Showing the different overheads resulting from the protection technique, such as area, timing, and power.

- (e) Introducing two other attacks and their protection scenarios.

#### 2. Secure FPGA-based designs

- (a) Discussing new ideas to have a blind data processing by the third party IP with a minimal cost.

- (b) Implementing ElGamal encryption scheme, which is a multiplicative PHE scheme and the CRT-based ElGamal (CEG) encryption scheme, which is additive PHE scheme, on a low-cost FPGA and showing the resource utilization, timing performance, and power analysis of both schemes.

(c) Introducing a dual-circuit design that supports both, multiplicative and additive homomorphic properties and providing the obtained savings on area and power over a regular design that has no resource sharing.

#### 3. Secure image processing

- (a) Proposing a secure framework to perform image processing computations over images stored on a third-party server based on Paillier cryptosystem.

- (b) Supporting basic image processing operations such as image adjustment operations, spatial filtering, edge detection, morphological operations, and histogram equalization.

- (c) Discussing the benefit of integrating Paillier cryptosystem with a floatingpoint support in decreasing the pre/post processing in the similar work mentioned in the literature.

- (d) Introducing a user friendly Android application to submit encrypted images for secure processing.

### **1.3** Thesis Organization

The Thesis is organized as follows. Chapter 2 describes the needed background about the PHE cryptosystems, used in this work. Chapter 3 illustrates the first contribution, which is using homomorphism in E-voting systems. It introduces a couple of possible attacks and countermeasures to an FPGA-based voting machine. The full hardware implementation is described and the countermeasures' overheads are highlighted. After that, Chapter 4 introduces the second contribution, which is securing FPGA-based designs from Hardware Trojans (HTs) using homomorphism. The design realization on a low-cost FPGA is described and the area/timing results are presented. Then, Chapter 5 describes the third contribution, which is a cloud-based library, *CryptoImg*, that allows performing image processing operations over encrypted images. New algorithms are introduced and the communication/computation overhead are stated using various test cases. Finally, Chapter 6 concludes the work and states some possible directions for future work.

### **Chapter 2**

## Background

The aim of this chapter is to give a brief description of the idea of homomorphism, survey existing fully and partially homomorphic encryption schemes, with emphasis on the ElGamal and Paillier security schemes. Moreover, the chapter highlights the different attributes used to classify Hardware Trojans, as they are our main topic of interest in Chapters 3 and 4.

### 2.1 Fully Homomorphic Encryption (FHE)

As the most commonly used computations include the usage of both kind of basic operations; the addition and the multiplication, partially homomorphic encryption (PHE) techniques are not sufficient. As a result, FHE was introduced by Rivest, Adleman, and Dertouzos around forty years ago [7]. However, the research community had to wait till 2009. when it has been revisited again by Gentry [8]. The most attracting point regarding Gentry's proposal is that it was the first feasible FHE cryptosystem. In general, a FHE technique is a kind of encryptions, which provides the capabilities to perform any operation directly on encrypted data by converting it into a circuit of a certain depth.

In general, FHE includes four basic algorithms: Keygen, Encrypt, Decrypt, and Eval. The Keygen algorithm is responsible for generating the required keys. The Encrypt and Decrypt algorithms are used for encrypting and decrypting the plaintext messages, respectively. The Eval algorithm is built based on three different algorithms: Add, Mult, and Recrypt. The Add and Mult algorithms are used for addition and multiplication operations over ciphertexts, while the Recrypt operation cleans the ciphertext from the noise due to the homomorphic addition and multiplication operations. Without this function the scheme would be Somewhat Homomorphic and therefore it would only evaluate circuits of a fixed depth.

Since its introduction in 2009, there were many trials to introduce more FHE techniques. For instance, Van Dijk *et al.* introduced a FHE technique based on ideals defined over integers [9]. Gentry *et al.* enhanced his FHE implementation by adding many tricks to overcome the performance degradation issues of FHE [10]. However, they did not fully managed to handle them. For instance, the key generation process in this implementation required an overall time of two seconds in the best case and two hours in the worst case. The main cause of this low performance was due to the noise, which resulted from performing new successive homomorphic operations. To get rid of such noise, FHE cryptosystems used to recrypt the messages after every homomorphic operation. The overheads corresponded to the *Recrypt* operation was very high and affected the whole system performance.

One shot towards reducing the FHE overheads was the introduction of the somewhat homomorphic encryption (SHE) cryptosystems. They have less overheads compared to FHE cryptosystems, as they eliminate the need for the high cost *Recrypt* operation. As a side effect, the SHE techniques can only perform a limited number of homomorphic operations. Many authors in the literature tried to tackle the noise problem by introducing new SHE techniques. For instance, Brakerski *et al.* suggested using the concept of learning with errors (LWE) to reduce the accumulative noise [11]. This new idea allowed computing more operations on encrypted data, i.e., circuits with deeper depth, using the lower overheads of the SHE cryptosystems.

In 2012, López-Alt, *et al.* introduced a SHE cryptosystems, which handle inputs from more than one public key [12]. Bos *et al.* proposed another FHE scheme, in which the security of the system only relies on the standard assumptions of lattice [13]. In the same context, three researchers led by Gentry described a LWE-based FHE scheme, which is highly customized to evaluate the advanced encryption standard (AES) circuit efficiently [14]. The results reported in their paper showed that their proposal was capable of successfully evaluating a single AES encryption operation within five minutes.

Although new FHE and SHE cryptosystems had made a noticeable enhancements compared to previous ones, the large ciphertext sizes and timing overheads remain a major obstacles in the way of using such cryptosystems. Those overheads are very high while being compared to the overheads of the PHE cryptosystems. This opens the door for using hardware to accelerate the computations of FHE techniques. For example, Göttert *et al.* implemented FPGA-based modules for lattice-based computations, which represented a major part of the FHE cryptosystems [15]. Moreover, Pöppelmann and Güneysu introduced an efficient hardware implementation of a FHE technique based on the ring-learning-with-errors (RLWE) theorem [16]. However, these implementations did not achieve a stable state that allowed them to be used efficiently in real-world applications. Thus, we focus on PHE in this Thesis.

### **2.2** Partially Homomorphic Encryption (PHE)

As mentioned before, PHE has been introduced many years ago. It gives the chance to perform only one kind of operations, either addition or multiplication, on ciphertexts without revealing data. For example, let us consider the two messages,  $m_1$  and  $m_2$ , where both messages are encrypted and their ciphertexts are given by  $E(m_1)$  and  $E(m_2)$ , respectively. If the multiplication of the two ciphertexts is equivalent to the ciphertext of the multiplication of the two messages as shown in (2.1), we call this a multiplicative homomorphic scheme. On the other hand, if the multiplication of the two ciphertexts equals the ciphertext of the addition of the two messages as shown in (2.2), we call this an additive homomorphic scheme.

$$E(m_1) \times E(m_2) = E(m_1 \times m_2) \tag{2.1}$$

$$E(m_1) \times E(m_2) = E(m_1 + m_2)$$

(2.2)

One of the earliest discoveries in the area of PHE was the Goldwasser-Micali encryption scheme [17]. This technique offers the ability to perform homomorphic operations with respect to the bitwise xor logic operation. The security of the former technique relied on the "quadratic residuosity problem". There also exist PHE techniques that support another kind of operation, the addition operation. Benaloh [18] and Paillier [19] cryptosystems are two stunning examples for the additive PHE methods.

On the other hand, there exist two well-known schemes, which are multiplicative homomorphic schemes. The first one is the Rivest-Shamir-Adleman (RSA), which is considered as one of the most excessively used public-key cryptosystems [20]. The second is ElGamal encryption scheme [21]. In this Thesis, we selected ElGamal and Paillier cryptosystems to be used in our proposed solutions.

#### 2.2.1 ElGamal Scheme

ElGamal cryptosystems is an efficient and widely used technique, which has many applications in different domains. To illustrate its functionality, let us assume that we have two users, called *Alice* and *Bob*, respectively. *Alice* has a certain message *m* and she would like to send it to *Bob*. ElGamal process works as follows. *Bob* generates his keys by choosing a secret random exponent *k* and a generator *g*. So, his public key is (g,h), where  $h = g^k (mod n)$  and *n* is a large prime. Before sending *m* to *Bob*, *Alice* must generate a random exponent *l* and sends the ordered pair  $(c_1, c_2)$  to *Bob*, where  $c_1$  and  $c_2$  are defined by (2.3) [21].

$$c_1 = g^l (mod n)$$

$$c_2 = h^l \times m(mod n)$$

(2.3)

Bob can easily decrypt the ciphertext using (2.4).

$$m = c_1^{-k} \times c_2(mod n) \tag{2.4}$$

This PHE scheme is considered homomorphic with respect to multiplication because if  $(x_1, y_1)$  and  $(x_2, y_2)$  are valid encryptions for messages  $m_1$  and  $m_2$ , with the same key, then  $(x_1x_2, y_1y_2)$  is a valid encryption of  $m_1m_2$  [21].

Hu *et al.* proposed a simple modification to make ElGamal additively homomorphic by placing the message *m* in the exponent [22]. So, if we encrypt two messages  $m_1$ and  $m_2$  using (2.3) but multiply  $h^l$  with  $g^m$  instead of *m*, the multiplication of the two ciphertexts results in a valid encryption of  $g^{m_1+m_2}$ . The problem here is that recovering the message requires finding the solution of the Discrete Logarithm Problem (DLP). ElGamal security itself is built upon the hardness of the DLP. To solve this problem, they introduced a new scheme, called CRT-based ElGamal (CEG) scheme, which depends on the Chinese Remainder Theorem (CRT). They managed to convert a single large-space DLP problem into multiple small-space DLP problems. This allows obtaining  $m_1 + m_2$ easily, while retaining the full security of the scheme, as shown later.

#### 2.2.2 CRT-based ElGamal (CEG) Scheme

To illustrate how CEG works, let us reuse the previous example of *Alice* and *Bob*. In the first step, *Bob* selects a secret random exponent k along with a generator g. He also chooses  $d_i$  for i = 1, ..., t, such that  $gcd(d_i, d_j) = 1$  for  $i \neq j$ . So, *Bob*'s public key is  $(g, h, (d_1, ..., d_t))$ , where  $h = g^k (mod n)$  and n is a large prime. For encryption, *Alice* sends the encryption of message m as a t-tuple of pairs  $(c_1, c_2)$  by using (2.5).

$$c_1 = g^{l_i} (mod n)$$

$$c_2 = h^{l_i} \times g^{m_i} (mod n)$$

(2.5)

where  $m_i = m \pmod{d_i}$  and  $l_i$  is a generated random exponent for i = 1, ..., t. Bob can decrypt the ciphertext using (2.6) and (2.7).

$$m = CRT^{-1}[(\log_g(c_{2_i} \times c_{1_i}^{-k}(mod\,n)), i = 1, \dots, t)]$$

(2.6)

$$CRT^{-1}[c_i] = \sum_{i=1}^{t} c_i \frac{d}{d_i} (\frac{d}{d_i}^{-1} \mod d_i) \mod d$$

(2.7)

Correctness and efficiency of the illustrated scheme is discussed in details in [22]. As part of this work, we implement the CEG scheme in hardware and show its resource utilization and power consumption in Chapter 4.

#### 2.2.3 Paillier Cryptosystem

Our *CryptoImg* system, described in Chapter 5, relies upon the homomorphic properties of the Paillier cryptosystem [19]. Paillier cryptosystem is one of the most widely used PHE schemes.

To briefly describe the Paillier cryptosystem, *Alice* can select any two large prime numbers, for example p and q. Then, let N = pq. Now, we can define a new domain  $Z_{N^2}$ , where  $Z_{N^2} = \{0, 1, ..., N^2 - 1\}$ . The set of non-negative integers, which have multiplicative inverse modulo  $N^2$  is denoted by  $Z_{N^2}^*$ , where  $Z_{N^2} \subset Z_{N^2}$ . Then, she needs to select a number g from  $Z_{N^2}^*$ , where g satisfies the conditions in (2.8).

$$gcd(L(g\lambda \mod N^2), N) = 1$$

(2.8)

where  $L(u) = \frac{u-1}{N}$  and  $\lambda = lcm(p-1,q-1)$ . By the end of the key generation process, *Alice* would have the pair (g,N) as a public key and  $\lambda$  as a private key. It is worth mentioning that the length of N should be greater than 1024 bits to ensure a powerful security level.

Before sending the message *m* to *Bob*, *Alice* should encrypt it using (2.9)

$$c = E(m, r)$$

=  $g^m r^N modN^2$  (2.9)

where  $c \in Z_{N^2}$  denotes the ciphertext and *r* is another random exponent. It is worth noting that the Paillier cryptosystem is a provable semantically secure encryption system whose security guarantees are proven based on the computational hardness assumption of the Decisional Composite Residuosity (DCR) problem.

Equation (2.10) gives an optimized notation for the encryption process.

$$c = E(m, r) \equiv \llbracket m \rrbracket \tag{2.10}$$

For *Bob* to obtain the actual message m from the ciphertext, c, he should compute the operations mentioned in (2.11).

$$m = D(c, \lambda)$$

=  $\frac{L(c^{\lambda} mod N^2)}{L(g^{\lambda} mod N^2)} mod N$  (2.11)

Paillier cryptosystem is an additive HE scheme as it provides a public-key operation  $\oplus_z$  over two encrypted integers, which is equivalent to their plain-text addition, as shown in (2.12). It also supports a self-blinding operation  $\otimes_z$ , which allows multiplication of encrypted integer by a plaintext scalar *d*, as shown in (2.13)  $\forall m_1, m_2 \in \mathbb{Z}_N$  [19].

$$DEC(\llbracket m_1 \rrbracket \oplus_z \llbracket m_2 \rrbracket) = DEC((\llbracket m_1 \rrbracket \times \llbracket m_2 \rrbracket) \mod n^2)$$

$$= (m_1 + m_2) \mod n \qquad (2.12)$$

$$DEC(\llbracket m_1 \rrbracket \otimes_z d) = DEC(\llbracket m_1 \rrbracket^d \mod n^2)$$

$$= (m \times d) \mod n \qquad (2.13)$$

# 2.3 Hardware Trojan

Nowadays, HT is considered one of the hot research directions due to the popularity of the usage of hardware ICs in various domains [23]. Those applications include, but not limited to, cars, cell phones, satellites, medical devices, and strategically military components.

HT is simply defined as a malicious alteration of one's own hardware. This alternation may, under specific rare circumstances, result in information leakage out of the system or functional changes of the system itself [24]. As shown in Figure 2.1, those kinds of malicious circuitry can be injected by either third party IP owners or fabrication facilities. This obviously threatens the entire design community.

# 2.4 Hardware Trojan Taxonomy

The aim of this section is to make the reader familiar with the different types of HTs in general and to briefly highlight the various categories that could be used to classify them.

Generally speaking, HTs can be divided into five main categories, as shown in Figure 2.2. As introduced by Karri *et al.*, the classification is based on phase of insertion, level of abstraction, methods of activation, effects, and location [26].

#### 2.4.1 Phase of Insertion

In order to have a fabricated IC in hand, the chip passes through many phases. Those phases are specification, design, fabrication, testing, and packaging. Each phase of them introduces a possible chance for an attacker to insert an HT.

FIGURE 2.1: Possible stages for launching Hardware Trojan (HT) attacks by third parties during IC life cycle [25].

Firstly, the **specification phase**, could be described as the phase in which the designer states the main the properties of the IC, such as the desired functionality, the maximum amount of power consumption, the allowable size, and the accepted delay. One possible way to insert an HT here is to manipulate one of the required constraints of the IC. In our proposed solution of Chapter 4, we care about the data itself, which is being encrypted using a PHE scheme before traveling to the suspected third party IPs. Thus, manipulating the requirements of those third party IPs in the specification phase would not leak any further information.

After that, the **design phase** comes to business. All the previously prepared characteristics are taken into consideration by the designers while writing the hardware codes. This phase may also require the usage of ready-made implementations from different vendors. That opens the door for inserting unwanted HTs. Again, this will not affect our solution as even if the used IPs are suspicious, they will know nothing about our encrypted data.

The **fabrication** and **assembly phases** are more related to the ASIC flow, where complete designs are moved to the fabrication facilities in order to produce them. If such

facilities are untrusted, they may add more logic to the users' design before fabricating them. Additionally, they may connect the outputs of the users' IP to a hidden node during the assembly process. This node could be used later to leak important information about the IP behavior. So, we need to make sure that at least the encryption/decryption hardware architectures that we use within our solution is produced at home or using trusted manufacturers.

Finally, the **testing phase** also may be used by an intruder to bypass certain testing vectors that might lead to the discovery of his/her own HT inserted in a previous phase. So, it is very critical to insure the trustworthy of the testing engineers and make sure that the testing coverage is good enough. For our proposed solution, we can safely work with malicious third party IPs as our data is always in an encrypted form.

#### 2.4.2 Level of Abstraction

Here, we move to the second class of HT taxonomy, where the target level of abstraction plays the main role. For the attacker, he/she can insert the HT within different levels, such as the system level, development environment level, register-transfer level (RTL), gate level, transistor level, and physical level.

On the **system level**, main IPs are well defined and the required protocols of communication are selected. Any change in those pre-stated points might lead to a misbehavior of the final circuit. One rigid example is introduced in Chapter 3 where the unused bits of the input data could be used to launch an attack on the e-voting machine. This should not happen as those bits are designed to be unused by any system module in the first place.

The **development environment** is a generic name enclosing the processes of simulation, synthesis, placement and routing, etc. The mentioned processes are done using electronic design automation (EDA) tools, which might be used by an outsider to insert HTs. Furthermore, malicious simulation tools could be designed in order to bypasss certain rare conditions that might be a root for HT.

Regarding the **register transfer level (RTL)**, it gives the attacker high flexibility to affect the functionality of the original IP. An intruder can insert any additional logic to the actual code to act as an HT. The added logic can be able to work independently or wait for a certain trigger as will be highlighted in a coming categorization [28]. The same rules are applicable for the **gate level**, in which the attacker can monitor the inputs, outputs, and interconnections between design components.

As the gates are mainly built out of transistors, the **transistor level** is a possible level at which an HT could be inserted. In this case, the HT could appear as the usage of a transistor with different electrical characteristics than the golden one. That might have a noticeable effect on the implementation timing delay and power consumption.

At the **physical level**, the final layout of the circuit is determined. This includes the real size of each component, their locations on the board, and the spacing between each component and its neighbors. An attacker with access to this level of abstraction can modify the dimension of a single wire/component in order to disable the complete IP.

#### 2.4.3 Methods of Activation

One efficient way to classify HTs is to investigate the mechanisms, which are used by HT owner to activate them. In this context, we have three main types of HTs; the "always-on" HT, the "internally-triggered" HT, and the "externally-triggered" HT.

The **always-on** HTs are up and running throughout the life of the infected IP. For example, any HT that is inserted in the physical level could fall under this category.

On the other hand, there exist HTs that remain silent until a certain condition occurs. They are called "triggered" HTs. Those kind of Trojans are very dangerous as the majority of them depends on rare conditions, which could not be discovered in the regular testing phase, to be activated.

If the event, needed to trigger the HT, comes from an outside source, we called those HTs, **externally-triggered**. The e-voting example of Chapter 3 best describes this kind of Trojans, where the HT within the Microblaze core is only activated when it receives a pre-defined trigger from the input keypad.

On the other hand, the **internally-triggered** HTs become active only if a certain condition is reached from within the infected architecture itself. For instance, an HT could be activated when the internal finite state machine (FSM) of the implementation reaches a certain state or when an internal counter reaches a certain large value.

Finally, it is worth mentioning that some "triggered" HTs continue to work after being activated, while others return back to their silent state after a certain amount of time.

#### 2.4.4 Effects

The major issue caused by HTs is their malicious side effects. Hence, it would be helpful to use the different evil effects caused by HTs to classify them. Although there are many undesirable effects for HTs, we will only consider the widely-known ones.

On the top of the list comes the **change in functionality** effect. An HT injected in any fabrication phase could easily change one or more of the IP functions to completely different ones. The functionality change might be as small as altering the value of a single IP output or as large as disabling the whole system.

**Downgrading performance** is a well-known side effect of HTs. A Trojan of this type might increase the architecture critical path or add more useless sequential logic to consume larger amounts of power. Furthermore, HTs could be designed to **leak information** regarding the working IP. The types of leaked information are numerous, such as the applied voltage/current, operational frequency, etc. Those information could be used to estimate the actual functionality of the infected IP. Moreover, HTs might leak sensitive users' information while the infected IPs are running, so users privacy are badly affected.

Furthermore, HTs could be used to cause **denial-of-service** (DoS). That means an HT forcing a certain module to consume a limited circuit resource, like (current, power, network bandwidth). This will cause the rest of the architecture resources to be out of service and hence decreasing system reliability.

#### 2.4.5 Location

Trojans can also be categorized based on their actual locations within the targeted architecture. A global HT could affect the whole design, while a local HT is limited to a certain part of the architecture. This part could be the main **processor** core [29], different **memory** blocks, **input/output** ports, **power supply**, or the **clock grid**. Based on the HT location, one could estimate the dangerous of it. An HT inserted within the power supply circuit might disable the whole architecture, while an HT hidden within the memory could leak sensitive information about the users' data.

It is obvious that a certain HT could be successfully classified to more than one of the previously mentioned categories. For instance, an HT could be inserted in the main processor within the design phase, be written as an RTL code, be triggered by an external event, and cause a performance downgrade.

# Chapter 3

# **E-voting Attacks and Countermeasures**

Since more than 50 years, electronic voting (e-voting) systems have been first introduced. Many changes have been made upon them over the decades. They started to be widely used as they do offer various advantages over the traditional voting methods. However, e-voting also introduces many security challenges that need to be handled wisely, otherwise, it might bomb the whole voting process. E-voting machines may contain harmful back-doors, which can affect the dependability of the system.

Through this chapter, one of the e-voting challenges is introduced; the existence of a hardware Trojan (HT) that totally tampers the voting results. We used a Xilinx FPGA board to implement a simple e-voting machine. Here, the idea of homomorphism appears via the usage of CRT-based ElGamal (CEG) cryptosystem to encrypt the votes before sending them to the main server. We inject an HT within the FPGA design to tamper voting results. We provide a couple of protection mechanisms and evaluate them by showing their overheads. Our solution adds about 4% as per logic resources and less than 10% as per timing delay. The additional power consumption is almost negligible. Furthermore, we highlight the differences between our proposed protection mechanisms and other techniques from the literature.

Starting with the motivation in Section 3.1, we make the literature review in Section 3.2. We then introduce a full e-voting system implementation in Section 3.3. After that, we show a simple scenario for an untrusted machine and how it would be used to affect the election results in Section 3.4. We introduce protection against the proposed Trojan in Section 3.5. Furthermore, we suggest other attacks and countermeasures in Section 3.6. The evaluation is mentioned in Section 3.7. Finally, Section 3.8 concludes the chapter.

#### 3.1 Motivation

Democracy as an expression means "ruling by people". Citizens need to have access to concrete information and to be capable of freely selecting their representatives to claim living in a democratic environment. Democracy itself mainly depends on the election process to satisfy population needs. Elections give the advantages for the citizens to freely select their representatives. No one can deny that the election process integrity is very important to ensure the integrity of democracy itself. Additionally, for the populace to accept the election results, the election system itself must fulfill a set of requirements. These requirements include, but are not limited to, transparency, robustness, and venerability. Without those features, the election system would be very questionable. Through out the mankind history, there existed a lot of election examples, which had been manipulated in order to redirect their output. Thus, designing an "acceptable" voting system, whatever its basis is electronic or paper-based system, is a critical operation that must go through many dedicated filters and competing criteria to verify it.

As shown in Figure 3.1, when a voting system uses a computerized element to either record, check, or collect votes, we can call this system an e-voting one. These types of systems started to become widely used as they introduce many advantages to all election parties; citizens, candidates, and election administrators [30]. Citizens seem to prefer electronic voting systems due to their privacy and accessibility. Candidates and election administrators usually enjoy the efficiency and speed of the entire e-voting process. Administrators, specifically, prefer e-voting lower cost compared to normal voting on the long run. If it is implemented properly, an e-voting system can eliminate a lot of common avenues of fraud, increase accessibility, speedup the process of collecting results, give more accurate and trusted results, increase convenience for voters, and reduce the cost of the entire elections process specially on the long run.

The process of designing an efficient and satisfyable election system is a critical process that requires special care. Common people usually have less trust in computerized operations because of the major stories about system crashes and hacking threats. As a result, e-voting elections must be more secure and trustworthy. Kohno *et al.* discussed some of e-voting system problems, such as certain vulnerabilities to network threats, the incorrect usage of cryptographic techniques, the escalation of unauthorized privileges, and the poor software development processes [31].

Here, we select an FPGA-based e-voting system to be the basis of our work [32]. The security of the selected e-voting system relies on utilizing the PHE additive property of

FIGURE 3.1: E-voting versus regular voting.

the CRT-based ELGamal scheme [22]. We propose three different scenarios to launch malicious attacks on the system and suggest the suitable countermeasures.

# 3.2 Related Work

E-voting security is one of the most important topics nowadays. The Caltech MIT Voting Technology Project highlighted that the public confidence in any voting system not only depends on the system reliability but also on the security of the system it-self [33]. Kumar and Begum introduced an Electronic Voting Machine (EVM) and its variation [34]. They also discussed issues of EVM, Taxonomy, and Bio-metric-based EVM. Additionally, Yumeng *et al.* reviewed the research on the e-voting schemes that aims at achieving a trusted voting system with all its properties and possible challenges.

Fauzia *et al.* described an implementation of a secure yet efficient e-voting system based on the "Fujioka-Okamoto-Ohta" protocol [35]. The proposed implementation includes the automation of an online voting system providing some new features that were not previously offered in the literature. Those features include allowing voters to verify their own votes, introducing simple and easy to use interface, keeping the privacy of voters' choices, and preventing either ineligible voters from voting or eligible voters from voting twice.

Another design of an e-voting machine was introduced by Alam *et al.* [36]. The authors' principal goal of the project was not to design a perfectly efficient device. Instead, the authors' goal was to design a mother component, which could be easily adopted to any recent technology. Their machine also used the voter's ID to recognize valid voters and to prevent multiple votes from the same voter as well.

Talking about FPGA-based e-voting systems, Wollinger *et al.* provided a summary of security issues that might arise in case of performing cryptographic operations on FPGAs [37]. They mainly focused on how to preserve secrets within the FPGA device itself against certain attacks, such as the "readback attack", which aim to read out the FPGA's SRAM contents or its bitstream. The SRAM contains valuable information about the data used. The bitstream, which define the FPGA configuration, may allow an attacker to use reverse-engineering to estimate the actual logic design within it.

FPGA manufacturers, such as Xilinx and Intel FPGA, provided features to prevent those reverse-engineering attacks [38]. For instance, they protected their FPGA chips against "IP core theft" attacks by encrypting the bitstream itself. Then, during the booting phase, the FPGA can launch an internal module that stores the key, which could be used to decrypt the bitstream in order to use it. In this scenario, an invader that has already read the encrypted bitstream would not be able to learn anything. He/She will not also be capable of performing any queries in order to read the decryption key from the FPGA.

On the other hand, Alkabani and Koushanfar presented an alternative method protecting the secrecy of the FPGA's bitstream by leveraging chip-to-chip behavioral variations in order to achieve what is called *active hardware metering* [39]. The method, which they used mainly depends on making the FPGA configuration unique for any given chip. So, the movement of a certain configuration from one chip to another would not cause a correctly functioning implementation.

Oksuzoglu *et al.* presented a minimal design of a secure e-voting system [32]. They realized their implementation using a simple FPGA board from Xilinx. They named their proposed system "VoteBox Nano" as they have already followed the same guidelines firstly illustrated by the original "VoteBox". They only restricted some network features so as to fit on a cheap FPGA. It is a very simple design running without any operating system (OS). It only consists of an FPGA connected to an interface screen (VGA) and a keypad to allow the voter to select his desired candidate and confirm her choice. For the VoteBox Nano, secrecy of the design itself was not the main problem. The main issue was how to detect tampering.

Drimer *et al.* described an algorithm, which permits the FPGA to safely reject any undesirable configuration updates [40]. Dutt *et al.* proposed the idea of "parity groups" [41]. They simply added parity bits to the logic components implemented on the FPGA. By this method, modifying any block of the internal logic blocks will directly cause a parity failure with no corresponding changes elsewhere. In case of obtaining machine components from third parties, design is exposed to further challenges that need to be faced. That includes hardware spywares and hidden back-doors. Old-fashioned testing and verification methods are not the suitable candidates for detecting the issues, resulting from HTs. Generally, HTs are not designed to be activated at test time as they mainly depend on certain rare conditions to trigger them. In the last decade, various techniques have been proposed to detect HT within FPGA-based designs. Those techniques could be divided into two main parties; architectural techniques [42], and side-channel dependent ones [43, 44]. Those techniques would be discussed in detail in Subsection 4.2.

# **3.3** E-voting System Overview

The implemented e-voting system is similar to VoteBox Nano design [32]. Figure 3.2 shows an overview of the full e-voting system. A voter logins to any of the e-voting boxes, which are distributed over the country. Then, e-voting box encrypts the vote using CEG encryption algorithm, which is an additive PHE technique. Encrypted votes are sent to the main secured server via a network connecting the whole country holding the elections. Each single vote would be represented by a v-tuple of encrypted zeros/ones, where v is the total number of voting states (candidate 1, candidate 2, candidate 3, etc.). The main server will receive the encrypted results to the election supervisor. The decryption methodology, performed by the supervisor, follows the same concept of CEG Algorithm used in encrypting votes. Finally, voting results can be ready on even the same day without human interference.

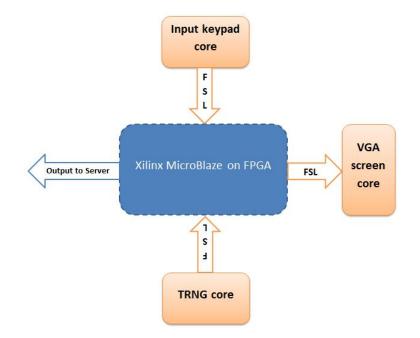

Figure 3.3 shows an abstraction of our proposed e-voting box. The true random number generator (TRNG) core block is responsible for generating keys, which are required for vote encrypting. TRNG depends mainly on post-processing of digitized noise. Every encrypted value in the system needs a unique random number. We should highlight that choosing a TRNG algorithm is critical as numbers prediction may allow the attacker to decrypt the ciphertexts. It is worth mentioning that the voter's privacy mainly depends on the hardness of predicting the selected random numbers. Input keypad and VGA screen cores represent the input and output modules, respectively. The machine screen will display the names of the candidates with their numbers arranged from 1 to n. The voter will use the keypad buttons to select his candidate and confirm his choice. He/She can also control some other features, such as determining the screen brightness.

FIGURE 3.2: The e-voting process.

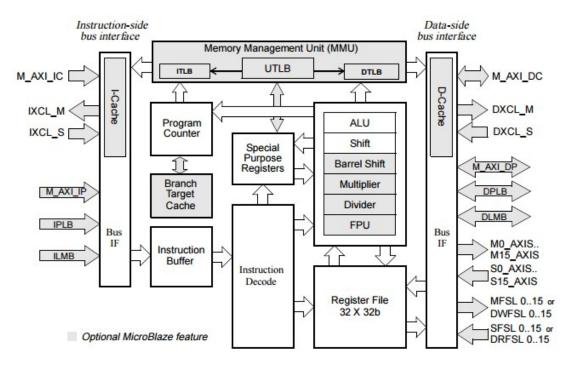

Xilinx MicroBlaze is the main block in the design [45]. Its main block diagram is shown in Figure 3.4. It is a virtual microprocessor, which is built by adding blocks of code, called cores, within a Xilinx FPGA. It presents a 32-bit Harvard RISC architecture with separate 32 bit instruction and data buses. Hence, it supports executing programs and accessing data from both on-chip and external memory at the same time. It is specially

FIGURE 3.3: Abstract view of our proposed e-voting machine.

optimized for Xilinx FPGA boards. The white items, such as the program counter, the special purpose registers, the bus interfaces, and the ALU, represent the backbone of the MicroBlaze architecture. On the other hand, the gray-shaded items represent the MicroBlaze optional features that could be added or removed based on the application needs.

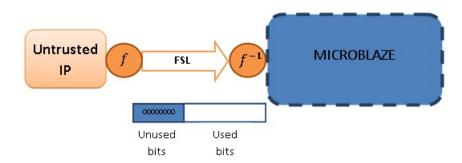

MicroBlaze is connected to other cores using the Fast Simplex Link (FSL). FSL is an interconnect, which supports a point-to-point communication in only one direction. It provides a direct communication between any two IPs on the FPGA when implementing an interface to the FSL interconnect. The MicroBlaze is capable of supporting up to 8 FSLs [45].

FIGURE 3.4: MicroBlaze block diagram [45].

# 3.4 Scenario for a Possible Attack

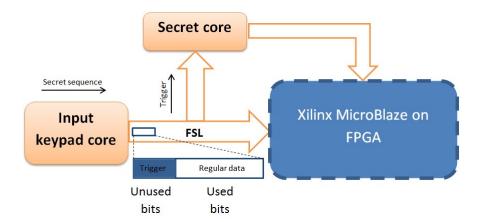

An untrusted FPGA-based voting machine may be used to tamper with the legal votes of users. Attacking vendor may inject cores connected to the MicroBlaze via FSL. These cores are responsible for dealing with inputs from the keypad and interfacing with the output screen. The attacker may add a hidden core that replaces the user's vote with another one, if it receives a special external trigger. In our case study, we assume that the voting system contains a secret core connected to the MicroBlaze core and takes its input from the FSL coming from the input keypad core, as shown in Figure 3.5.

We propose a scenario in which an attacker uses the input keypad as follows. He/She will press the push button that control screen brightness with a secret sequence depending on the position of the wanted candidate. That secret sequence would be translated into data sent to the MicroBlaze via the FSL in the unused bits beside the regular data. As a result of triggering the MicroBlaze back-door, all the coming sent votes will support the wanted candidate whatever the voter chooses. Repeating that several times on several machines will affect the whole election results significantly.

FIGURE 3.5: Block diagram of using a malicious secret core within an untrusted e-voting machine.

# 3.5 Protection Against Proposed Attack

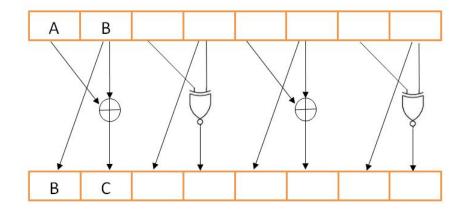

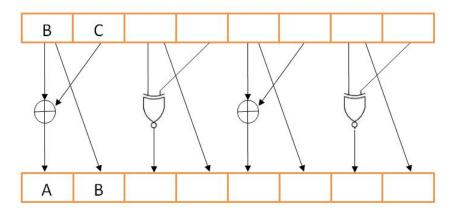

There are several ways to protect our system from untrusted third party IPs. We suggest to use the *Simple Blockage (SB)* method introduced in [46] with a simple improvement. The authors of the original work proposed to obfuscate the output of the IP under suspection before sending any data out of it. Later on, they will undo that obfuscation step at the receiver's input. This idea would help protecting data from leaking and avoiding injected triggering. They introduced using either RC4 or other simple obfuscating function. Here, we choose to protect the design using a simple xoring function, as shown in Figure 3.6 and Figure 3.7. Obfuscation will take place between keypad and MicroBlaze. In our case, the data transmitted via the FSL is 32-bit.

We enhance the *SB* method by resetting any unused bits to zero before receiving them at the MicroBlaze, as shown in Figure 3.8. We only allow the trusted-known used bits to go. Obfuscating the unused bits cost is wasted and will be omitted. Furthermore, an attacker may depend on the unused bits to discover our simple obfuscating function. We did not use the partial reconfiguration feature to change obfuscating function periodically as proposed in [46], as the partial reconfiguration feature doubles FPGA

FIGURE 3.6: Simple obfuscating function depending on data xoring.

FIGURE 3.7: Inverse obfuscating function in order to retrieve data.

and e-voting box area cost. Subsection 3.7.2 shows function overheads in details. Our technique would prevent the trigger that would turn the secret core on.

FIGURE 3.8: E-voting protection against proposed attack.

# **3.6 Other Attacks and Countermeasures**

In this section, we discuss a couple of other feasible attacks and propose the suitable countermeasures for them.

#### **3.6.1** Sequence Cheat Code Attack

In Section 3.4, we assumed that the secret core trigger will be sent to the MicroBlaze core in the unused bits in one data packet. That is called *single-shot cheat code* as described in [47].

Another possible attack may be based on sending a bigger cheat code within a number of successive pieces. Those pieces could be represented by using different cycles/inputs. This attack is called *sequence cheat code* attack. These successive cheat codes can be introduced to the system through the FSL bus connecting the input keypad core and the MicroBlaze.

Waksman and Sethumadhavan proposed two different ways to solve cheat code issues [47]. One for the single-shot cheat code using data obfuscation (i.e., encrypting the suspected IPs input values in order to eliminate any malicious codes). Another way is to use sequence-breaking against sequence cheat code. The sequence breaking method suggests to pseudo-randomly scramble the order of inputs, which enters the suspected IPs. By this way, we can prevent those untrusted units from recognizing the malicious sequences of inputs, which can activate an HT.

However, our proposed method in Section 3.5 is capable of protecting the design from that external trigger either if it is single-shot cheat code or even sequence cheat code. So, we do not have a need for extra hardware for handling sequence cheat code, and that is an advantage of our proposal over Waksman methodology.

#### 3.6.2 Used Bits Attack

Now, let us introduce another attack where we suggest that keypad core is infected with no extra hidden cores. So, the trigger will be sent in the used bits. In all previous attacks, we assumed that the special trigger is sent in the unused bits of the data packet. The main risk is that the MicroBlaze sees that confidential data (user's vote) in unencrypted form and thus can manipulate it. Additionally, this core, along with many other hardware cores, are usually obtained as a third party IP. In this case, using our technique to secure data transfer would not prevent triggering the hidden back-door because the trigger will be obfuscated at the output of the untrusted IP (input keypad core), transferred via the FSL, and then return back to its original form at the input of the MicroBlaze core.

We should mention that Waksman and Sethumadhavan presented a solution for this attack by using data obfuscation for computational units [47]. The selection of the

correct method for obfuscation mainly depends on the IP type. The authors suggested classifying the IPs into two main classes; computational IPs and non-computational ones. For the later class, the IPs do not actually perform any computations on the data. As a result, the authors simply used an encryption method to obfuscate the data values before entering the non-computational IP.

On the other hand, for computational IPs (as in our proposed attack here), data encryption is much more complicated than the non-computational case. In certain scenarios, duplicating the whole design might be more efficient than using obfuscation. This high complexity will appear in our case because our computational unit uses ElGamal Algorithm for public key encryption [21]. They suggested using the third party computational IP without giving it the advantage of recognizing the data. They depend mainly on HE schemes, as shown in (3.1). But, the main problem of this solution will be the overhead cost of all e-voting boxes.

$$Gamal(xy) = Gamal(x)Gamal(y)$$

(3.1)

In case one wants to encrypt a certain data value *x*, where *x* represents the vote in our case, using ElGamal Algorithm on a special purpose encryption core, the following steps should be followed.

- 1. Use a TRNG module in order to generate a random value *y* and calculate its encryption result *Gamal*(*y*)

- 2. Use a trusted, regular ALU to compute z = xy, where x is the user's vote to be encrypted.

- 3. Send z to the encryption core that should returns Gamal(z) = Gamal(xy), which will be sent to the main server.

- 4. Add the received encrypted votes Gamal(z) at the server side.

- 5. Decrypt the summation result and use a trusted ALU on the server side to divide the result by *y*.

We use the untrusted cryptographic unit within the e-voting box to encrypt the vote, x, without allowing this untrusted component of knowing the actual vote value. This will protect from the triggering code injected in the real data.

# 3.7 Evaluation

Here, we will describe the experimental setup, which we used for creating the e-voting system. Furthermore, the numerical results for the area and power overheads are mentioned in detail.

#### 3.7.1 Experimental Setup

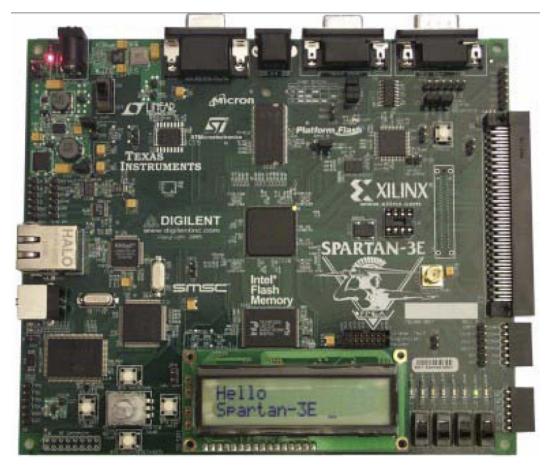

The total experiment was done by using **Spartan 3E starter kit** [48]. The needed logic is implemented using Verilog. Figure 3.9 illustrates the experiment setup. Our FPGA board is connected to a VGA screen via a VGA cable. The input keypad is connected to the FPGA using a PS2 interface.

FIGURE 3.9: Experimental setup for the e-voting system.

Figure 3.10 represents the used FPGA kit. It mainly includes a Xilinx XC3S500E Spartan-3E FPGA (FG 320 package, with a -4 as a speed grade), 232 user Input/Output pins, Over 10,000 logic cells, 16 Mbits of SPI serial Flash, SPI serial Flash configuration, DDR memory interfaces, 64 MByte of DDR SDRAM, PS/2 mouse or keyboard

port, VGA display port, 50 MHz clock oscillator, and a MicroBlaze 32-bit embedded RISC processor.

FIGURE 3.10: The Xilinx Spartan 3E starter kit overview [48].

#### 3.7.2 E-voting Protection Results