# cādence<sup>®</sup>

# **Implementing Force Sense Connection**

Product Version SPB16.6 October 15, 2013 Copyright Statement

© 2013 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence and the Cadence logo are registered trademarks of Cadence Design Systems, Inc. All others are the property of their respective holders.

# Contents

| Purpose                                                   | 4    |

|-----------------------------------------------------------|------|

| Audience                                                  |      |

| Flow Overview                                             | 4    |

| DE HDL library requirements to define Force Sense symbols | 5    |

| Example Schematic Symbol                                  | 5    |

| Footprint Library                                         | 7    |

| Example Footprint                                         | 8    |

| Front to Back Flow Environment Requirement                | 10   |

| Schematic Capture                                         | 10   |

| Example Schematic                                         | . 10 |

| Constraint Assignment                                     |      |

| Max Propagation Delay                                     | . 11 |

| Primary Width                                             | . 11 |

| Board Layout                                              |      |

| Allegro PCB Router                                        | 13   |

| Net Schedule                                              | 13   |

| Identifying intentional short                             | 15   |

| Example IPC-D-356 netlist                                 |      |

| Miscellaneous Notes                                       | 16   |

| Software and License used                                 | .16  |

| Sample Database                                           | .17  |

| Important Database Element                                | . 17 |

| Summary                                                   |      |

| References                                                | .17  |

# Purpose

The use of separate Force (F) and Sense (S) connections (often referred to as a Kelvin connection) is quite a common requirement in the PCB design. These separate Force (F) and Sense (S) connections at the load removes any errors resulting from voltage drops in the force lead. Routing the Kelvin sense lines by separating lines for sensing signals (S) from lines delivering power to loads (F) prevents noise related problems in a closed loop system as it allows for more accurate measurement of the sense voltage.

The requirement is to implement this at the schematic to drive the PCB board so that both Force and Sense signals can be identified and constrained independently and still allowed to be physically shorted in layout.

Before you begin, download the Database from Cadence Online Support. Click Here to Download.

# Audience

Electrical Engineers and PCB Designers using Cadence Allegro tool set and implementing Kelvin connection using Force (F) and Sense (S) signals.

# **Flow Overview**

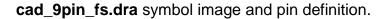

This flow is based on a special logical symbol, which is created and saved in a library.

The force sense library symbol(s) has shorting schemes defined within the symbol definition which allows the engineer to seamless define the nets to be force sense.

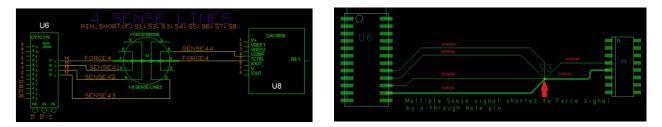

When placed in a schematic, will short at least two sense lines to a force line. During packaging, separate nets are generated and flow to the PCB. As shown in the image four sense lines are connected to a force line using the library symbol.

Inside PCB Editor, a Symbol gets placed, and defines the location of the short for force and sense signals.

To use this flow create a schematic symbol and footprint symbol as shown below.

# DE HDL library requirements to define Force Sense symbols

Use the **PIN\_SHORT** property on the logical symbol. The PIN\_SHORT property uses the logical pin name list in the value. At the time of packaging, based on CPM directive (see page 10), the packager acknowledges the PIN\_SHORT property value and creates NET\_SHORT property with value containing the physical net names connected to the logical pin names.

This can be validated by reviewing the "pstxnet.dat" file for "NET\_SHORT" property on the pin as shown in the example. This file is located in the "projectname/worklib/test/package" directory.

NET\_NAME

'FORCE2'

'@TEST\_LIB.TEST(SCH\_1):FORCE2':

C\_SIGNAL='@test\_lib.test(sch\_1):force2';

#### NODE\_NAME S2 1

'@TEST\_LIB.TEST(SCH\_1):PAGE1\_I13@TEST\_LIB.FORCE\_SENSE(CHIPS)':

#### 'F':NET\_SHORT='FORCE2:SENSE21:SENSE22',

CDS\_PINID='F';

The symbol needs to be ignored from Bill of Material (BOM) utilizing the BOM\_IGNORE = TRUE attribute and is associated to a footprint required to make the connection on board.

#### **Example Schematic Symbol**

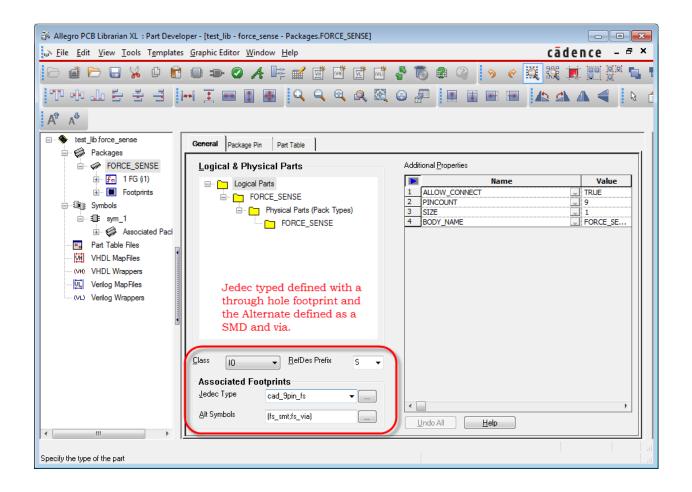

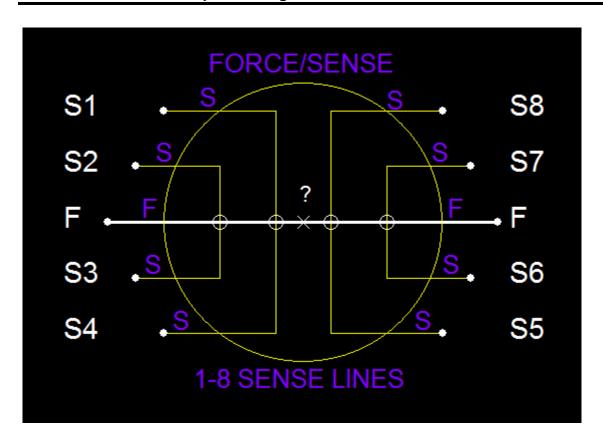

The Force-Sense symbol can connect one force line with one or multiple sense lines. In the example symbol provided, the Force & Sense symbol has been built to accommodate from 1 to 8 sense lines. PIN "F" is defined as pass-thru pin, so the total numbers of pins on the symbol are 9.

PIN\_SHORT should be defined on symbol as-

PIN\_SHORT=F:S1:S2:S3:S4:S5:S6:S7:S8

#### **Implementing Force Sense Connection**

| 🗱 Allegro PCB Librarian XL : Part Developer - [test_lib - force_sense - Symbols.sym_1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Eile Edit View Iools Templates Graphic Editor Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cādence – 🖶 🗙                                                                                                                                      |

| D 🗴 🖻 🖬 🖌 🗘 🖻 🗊 🗢 ⊘ 🛧 📭 🖬 🖬 🖬 🗳 🖏 🖓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ッ 《 👯 🌉 📰 🖉 🐂 🐂 🖷                                                                                                                                  |

| 17 사 쇼 흔 충 크 [HH 王 🖬 🖪 🔍 윽 윽 욕 쯶 @ 🖉 🗐 🖩                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ■ ■ IA A ◀ 👂 🕈 ๖ Lo 🗞 🖥 🕹 🤤 🤹                                                                                                                      |

| A <sup>9</sup> A <sup>0</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    |

| Ceneral Symbol Pins Find Pin_SHORT and BOM_IGNORE properties added as definition of schematic part Properties | FORCE/SENSE<br>S1<br>S2<br>S2<br>S<br>S3<br>S3<br>S<br>S3<br>S<br>S5<br>S5<br>S6<br>S4<br>S5<br>S5<br>S5<br>S5<br>S5<br>S5<br>S5<br>S5<br>S5<br>S5 |

# **Footprint Library**

There are multiple ways to short the signals on the board. The most common methods are-

- Shorting the signals on different layer or on same layer of board. This can be achieved by defining the footprint with Pin 1 defined as a through hole pin/pad combination, and a specified drill diameter. The remaining pins would be defined using a smaller diameter pad and a drill of zero. These would be positioned exactly on top of pin 1. Connections using this part could occur on any layer of the PCB. In the sample database a footprint "cad\_9pin\_fs" is defined for this.

- 2. Shorting the signals on a single layer, without a through hole part, can be achieved with a SMD pad. This can be achieved by defining the footprint with just the SMD pads for all the pins in the symbol. In the sample database a footprint "fs\_smt" is defined for this. This could also be defined as an alternate symbol for the above defined footprint.

NOTE: If using an SMD pad is required on internal layers, the database needs to be set up with Embedded Layers. Setup>Embedded Layer Setup can be accessed to accomplish this. This would require a Miniaturization Option license.

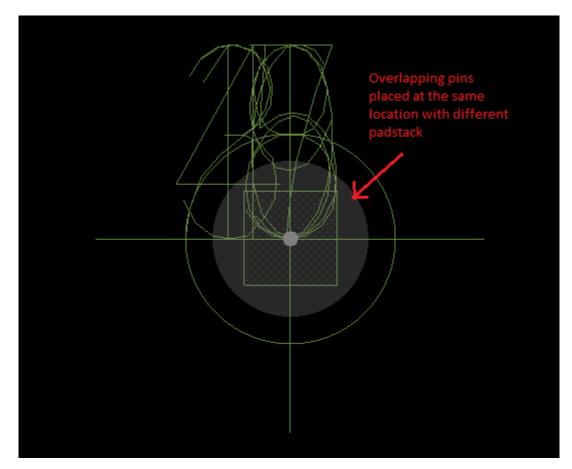

#### **Example Footprint**

The above symbol for Force-Sense with eight sense and a force pin should be associated with a footprint with nine pins at the same location. The pins are defined with the padstack -

Pin 1: 20 mil pad and 8 mil drill hole

Pins 2 - 9: 2 mil pad and 0 mil drill hole

| I Show Element                                                          | x        |

|-------------------------------------------------------------------------|----------|

| <u>F</u> ile <u>C</u> lose <u>H</u> elp                                 |          |

| Item 7 < PIN >                                                          | *        |

| class PIN                                                               |          |

| location-xy: (0.0000 0.0000)                                            |          |

| pin number: 8                                                           |          |

| not on a net<br>Padstack name: CAD_ZERODRILL_SMT<br>Type: through       |          |

| padstack defined from TOP to BOTTOM<br>padstack rotation: 0.000 degrees |          |

| Number of connections: 0                                                |          |

| Item 8 < PIN >                                                          |          |

| class PIN                                                               |          |

| location-xy: (0.0000 0.0000)                                            |          |

| pin number: 2                                                           |          |

| not on a not                                                            |          |

| Padstack name: CAD_ZERODRILL_SMT                                        |          |

| padstack defined from TOP to BOTTOM<br>padstack rotation: 0.000 degrees |          |

| Number of connections: 0                                                |          |

| Item 9 < PIN > Different Padstack<br>used at the same                   |          |

| class PIN location                                                      |          |

| location-xy: (0.0000 0.0000)                                            |          |

| pin number: 1                                                           |          |

| pot on a not                                                            | _        |

| Padstack name: CADCIR_0820<br>Type: through                             | =        |

| padstack defined from TOP to BOTTOM<br>padstack rotation: 0.000 degrees |          |

| Number of connections: 0                                                |          |

| ~ ~ ~ ~ ~ ~ ~end-of-file~ ~ ~ ~ ~ ~ ~                                   |          |

|                                                                         | <b>T</b> |

## Front to Back Flow Environment Requirement

To transfer the NET\_SHORT property to the netlist, and to board file based on the PIN\_SHORT defined on the logical symbol, define the following in the project cpm file or in the site.cpm file in the packager section ("PKGXL") as.

START\_PKGXL

• • •

PROCESS\_PIN\_SHORT\_PROP 'ON'

...

END\_PKGXL

# **Schematic Capture**

Once the logical symbol is defined, then the logical schematic can be created in Allegro Design Entry HDL (DE HDL).

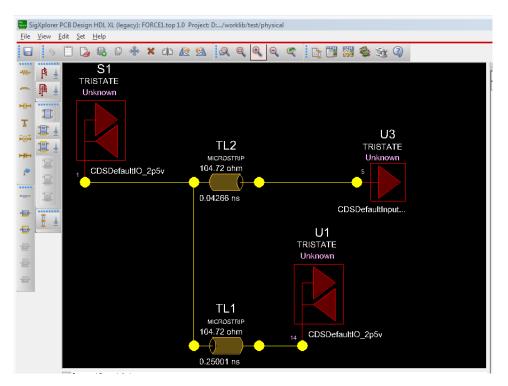

#### **Example Schematic**

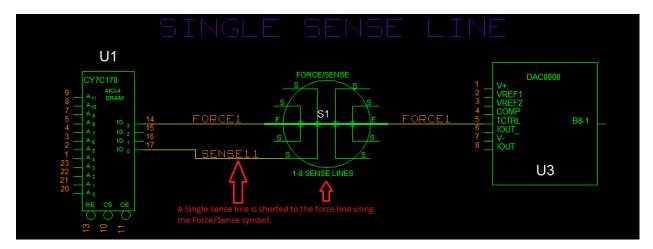

In this case one Force signal is shorted to one sense line using the Force/Sense symbol from the library.

# **Constraint Assignment**

The use of this flow, allows for individual net constraints to be assigned and used in the front to back flow. As an example, Net Schedule, Max Propagation Delay and trace width can be defined.

#### **Max Propagation Delay**

Pin Pairs can be created, then used to control location of short on FORCE.

| <u>File Edit O</u> bjects <u>C</u> olumn <u>V</u> iew A <u>n</u> al | /ze <u>A</u> udit | To      | ols <u>W</u> indow <u>H</u> elp |                 |           |             |     |            |            |              |            |            | cādenc   |

|---------------------------------------------------------------------|-------------------|---------|---------------------------------|-----------------|-----------|-------------|-----|------------|------------|--------------|------------|------------|----------|

| 3 X D A 🧐 🐫 🗖                                                       |                   |         | 💽 🌈 🖓 🕻                         | )e 🔚 🍊 🛦        | 🖬 👘 🔆     | <b>_</b> ⊷  | Yo  | Y6 ¥       | a 🖑 🕯      | ĩ, T         | × 1        | ⊨ _ ⇒ .    |          |

| orksheet selector                                                   | netsh             | ortb    | pard                            |                 |           |             |     |            |            |              |            |            | _        |

| Electrical                                                          |                   |         | Ohlasta                         | Referenced      |           | Pin Delay   |     |            | Prop Delay |              | Prop Delay |            |          |

| Electrical Constraint Set                                           |                   | Objects |                                 | Electrical CSet | Pin Pairs | Pin 1 Pin 2 |     | Min Actual |            | Margin       | Max        | Actual     |          |

| 📄 🜆 Signal Integrity                                                | Type S Name       |         |                                 |                 |           | mil         | mil | ns         | marginns   | ns           | Actual     | Margin     |          |

| Reflection/Edge Distortions                                         | *                 | *       |                                 | *               | *         | *           | *   | *          | *          | *            | *          | *          | *        |

| Xtalk/SSN                                                           | Dsn               |         | netshortboard                   |                 |           |             |     |            |            |              |            |            | 6.4 MIL  |

| 🗄 🖣 Timing                                                          | Net               |         | - FORCE1                        | PROP_SCHEDULE   |           |             |     |            | ×***       | ~~~~         |            |            | 8 MIL    |

| 🗄 📲 Routing                                                         | PPr               |         | S1.1:U1.14                      |                 |           |             |     |            |            |              |            | 1392.0 MIL | 8 MIL    |

| Wiring                                                              | PPr               |         | \$1.1:U3.5                      |                 |           |             |     |            |            |              | 300.0 MIL  | 231.5 MIL  | 62.5 MIL |

| Vias                                                                | Net               |         | FORCE2                          | PROP_SCHEDULE   |           |             |     |            |            |              |            |            | 10.8 MIL |

| Impedance                                                           | PPr               |         | \$2.1:U2.14                     |                 |           |             |     |            |            |              | 1400.0 MIL | 1389.2 MIL | 10.8 MIL |

| Min/Max Propagation Delays                                          | PPr               |         | \$2.1:U4.5                      |                 |           |             |     |            |            |              | 300.0 MIL  | 240.3 MIL  | 59.7 MIL |

| Total Etch Length                                                   | Net               |         | - FORCE3                        | PROP_SCHEDULE   |           |             |     |            |            |              |            |            | 29.5 MIL |

| Differential Pair                                                   | PPr               |         | \$4.1:U5.14                     |                 |           |             |     |            |            |              | 1400.0 MIL | 1361.0 MIL | 39 MIL   |

|                                                                     | PPr               |         | \$4.1:U7.5                      |                 |           |             |     |            |            |              | 300.0 MIL  | 270.5 MIL  | 29.5 MIL |

| Relative Propagation Delay                                          | Net               |         | FORCE4                          | PROP_SCHEDULE   |           |             |     |            |            |              |            |            | 6.4 MIL  |

| 🗄 🕼 All Constraints                                                 | PPr               | Ц.      | \$3.1:U6.14                     |                 |           |             |     |            |            |              | 1400.0 MIL | 1393.6 MIL | 6.4 MIL  |

| 🗁 Net                                                               | PPr               | н.      | \$3.1:U8.5                      |                 |           | _           |     |            |            |              | 300.0 MIL  | 258.7 MIL  | 41.3 MIL |

| 🗄 📲 Signal Integrity                                                | Net               | н.      | SENSE11                         |                 |           |             |     |            |            |              |            |            |          |

| 🗄 💵 Timing                                                          | Net               | -       | SENSE21                         |                 |           |             |     |            |            |              |            |            |          |

| 🗄 🜆 Routing                                                         | Net               | -       | SENSE22<br>SENSE31              |                 |           |             |     |            |            |              |            |            |          |

| Wiring                                                              | Net               | -       | SENSE32                         |                 |           |             |     |            |            |              |            |            |          |

| Vias                                                                | Net               | Η-      | SENSE33                         |                 |           |             |     |            |            | *****        |            |            |          |

| Impedance                                                           | Net               | -       | SENSE41                         |                 |           |             |     |            |            |              |            |            |          |

| Min/Max Propagation Delays                                          | Net               | -       | SENSE41                         |                 |           |             |     |            |            | <del> </del> |            |            |          |

| Total Etch Length                                                   | Net               | -       | SENSE43                         |                 |           |             |     | -          |            | *****        |            |            |          |

| Differential Pair                                                   | Net               | -       | SENSE44                         |                 |           |             |     |            | <u> </u>   |              |            |            |          |

### **Primary Width**

To control the width for FORCE and SENSE signals separately.

| Туре |          | c Phase |           | Min Line |             |              |

|------|----------|---------|-----------|----------|-------------|--------------|

|      | Objects  | Antural | Manualia  | Spacing  | Primary Gap | Primary Widt |

|      |          | Actual  | Margin    | mil      | mil         | mil          |

| *    | ż        | *       | *         | *        | *           | ×            |

| Dsn  | 😑 test   |         |           |          |             |              |

| Net  | FORCE1   |         |           | 8        |             | 12.0000      |

| Net  | FORCE2   |         |           | 8        |             | 12.0000      |

| Net  | FORCE3   |         |           | 8        |             | 12.0000      |

| Net  | FORCE4   |         |           | 8        |             | 12.0000      |

| Net  | FORCE5   |         |           | 8        |             | 12.0000      |

| Net  | SENSE11  |         |           | 8        |             |              |

| Net  | SENSE21  |         |           | X        |             |              |

| Net  | SEN SE22 |         |           | X        |             |              |

| Not  | CENCE24  |         | 400000000 | 히        |             | 1            |

Also different constraints like line impedance, relative propagation can be used to meet the specific requirements.

# **Board Layout**

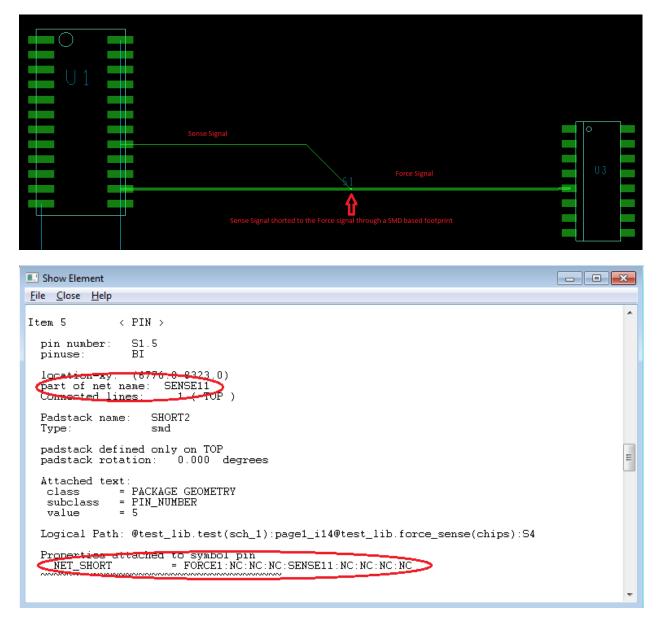

Once the logic information is imported in the board, the NET\_SHORT information is transferred to the pins of the footprint to which Force/Sense symbols is associated.

When interactively routing the F & S nets, it is best if you start from the Sense Pin and work from there, completing each net before moving to the next. There is an issue currently, where if you do not complete the interconnect and leave a dangling stub, when you select the next net to route, your stub gets truncated back into the Sense Pin.

Once routed no DRC is generated for the short because of the NET\_SHORT defined on the pin.

# Allegro PCB Router

Allegro PCB Router has been enhanced to connect the Sense Pins that have the NET\_SHORT property assigned.

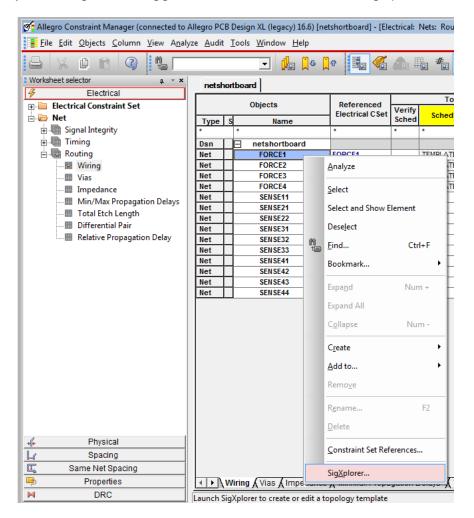

#### **Net Schedule**

To ensure Allegro PCB Router connects in the expected manner, it is suggested to perform a Net Schedule on the Force net. If there are many such connections within your design, it is suggested to exact the net into SigXp:

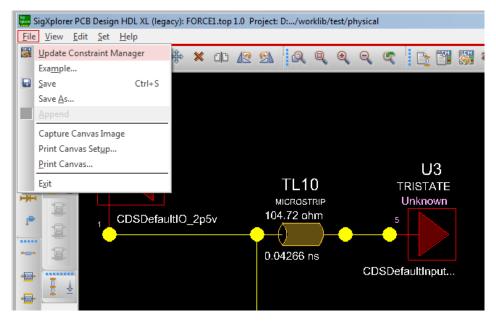

Schedule the net on the SigXp canvas:

Then reapply in Allegro using Update Constraint Manager.

Apply the Referenced ECSet to the remaining Force nets within the Allegro PCB design.

If using Allegro PCB Router, when more than 2 or 3 Sense lines are required, it may be a good idea to schedule the nets on different layers of the design.

# Identifying intentional short

Allegro PCB Editor reports the pins and x,y location with NET\_SHORT property in the IPC356 netlist.

#### **Example IPC-D-356 netlist**

C PIN X+070780Y+054660 FORCE4:NC:NC:SENSE41:SENSE42:SENSE43:NC:SENSE44:NC

C PIN X+070780Y+054660 FORCE4:NC:NC:SENSE41:SENSE42:SENSE43:NC:SENSE44:NC

C PIN X+070780Y+054660 FORCE4:NC:NC:SENSE41:SENSE42:SENSE43:NC:SENSE44:NC

C PIN X+071280Y+067710 FORCE3:NC:NC:SENSE31:SENSE32:SENSE33:NC:NC:NC

## **Miscellaneous Notes**

The use of this flow could potentially cause issues downstream in your manufacturing process. Currently there is no direct way to communicate shorted nets to validation software such as Valor. It would be up to the user to manage the data accordingly to those vendors.

It is recommended to create and use a standard and unique reference designator for the force and sense physical symbol, ex. SP\_1 (Shorting Pin). This would aid in search, and report generation.

There is currently a CCR logged against Allegro PCB Router for the methodology used in this Rapid Adoption Kit. Ensure that you are using the latest SPB 16.6 Hotfix. At this update, there was no date assigned to the fix.

#### Software and License used

This Application Note and its associated database has been modified using Cadence SPB 16.6 release with Hotfix -15.

#### This feature was originally available in SPB 16.5 release. It was not implemented until later in the release stream. If you use this technique, use the latest SPB 16.5 hotfix available on the Cadence downloads site.

Various software and license used are-

Part Developer with PCB Librarian Expert license.

Allegro Design Entry HDL with Allegro Design Authoring license and High Speed option.

Allegro PCB Editor with Allegro PCB Designer license and High Speed option to define different Constraints.

Use the Miniaturization options, if using an SMD pad on internal layers for connection, as that layer needs to be defined as Embedded Layer.

# Sample Database

Download the sample database attached to this application note. Use this database for the evaluation purpose.

#### **Important Database Element**

Force Sense Schematic symbol *"force\_sense"* located in the folder - worklib\force\_sense

Force Sense Footprint symbol ("*cad\_9pin\_fs.dra*" and "*fs\_smt.dra*") located in the folder - worklib\test\physical\symbols

Allegro Design Entry HDL project file - "force\_sense.cpm"

Board file - "netshortboard.brd" located in the folder - worklib\test\physical

# Summary

Using this methodology will reduce the time and effort required to design a board with force and sense connections. Also, nets can be individually constrained. Pin-Pairs can be defined in the schematic to control shorting location. It allows for quick search and navigation in a schematic for these types of signals. Additionally, custom reports can be extracted based on the reference designator to assist with downstream processes.

# References

The following Allegro product documentation may be found in local Cadence SPB16.5 installation (CDSROOT) and also online at Cadence Online Support.

#### Allegro User Guide

(\$CDSROOT\doc\algromast\algromast.pdf)

#### Allegro Design Entry HDL User Guide

(\$CDSROOT\doc\concepthdl\concepthdl.pdf)

#### Allegro Platform Properties Reference Guide

(\$CDSROOT\doc\propref\propref.pdf)