# TI Designs Industrial Ethernet PHY Brick with Fiber-Optic

## **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help *you* accelerate your time to market.

## **Design Resources**

| TIDA-00224 |  |

|------------|--|

| TLK105L    |  |

| TTPS75433  |  |

Tool Folder Containing Design Files Product Folder Product Folder

ASK Our Analog Experts WEBENCH® Calculator Tools

## **Design Features**

- Low Power Consumption <270 mW for EPHY, <850 mW for FO-Transceiver</li>

- TLK105L Ethernet PHY Configured for MII Interface

- Programmable LED Support Link, Activity

- Avago AFBR5803Z. Fiber Transceiver Interface for Longer Distance and Better EMC Performance

- HBM ESD protection on RD± and TD±

## **Featured Applications**

- Industrial Applications Circuit Breakers, Protection Relays, Smart Meters (AMI)

- Substation Automation Products RTU, Protection Relay, IEDs

- Power Quality Analyzer

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

## 1 System Description

A simple and effective design makes Ethernet the most popular networking solution at the physical and data link levels of the Open Systems Interconnection (OSI) model. With high speed options and a variety of media types to choose from, Ethernet is efficient and flexible. In addition, the low cost of Ethernet hardware makes Ethernet an attractive option for industrial networking applications. The opportunity to use open protocols such as TCP/IP over Ethernet networks offers a high level of standardization and interoperability. The result has been an ongoing shift to the use of Ethernet for industrial control and automation applications. Ethernet is increasingly replacing proprietary communications.

## 1.1 Basic Fiber-Optic Communication System

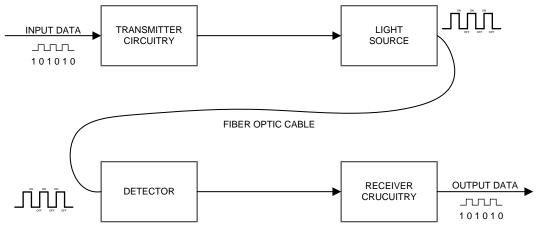

Fiber-optics is a medium for carrying information from one point to another in the form of light. Unlike the copper form of transmission, fiber-optics is not electrical in nature. A basic fiber-optic system consists of a transmitting device that converts an electrical signal into a light signal, an optical fiber cable that carries the light, and a receiver that accepts the light signal and converts the light signal back into an electrical signal.

Figure 1. Basic Fiber-Optic Communication System

The complexity of a fiber-optic system can range from very simple (for example, a local area network) to extremely sophisticated and expensive (for example, long distance telephone or cable television trunking). For example, the system shown in Figure 1 can be built very inexpensively using a visible LED, plastic fiber, a silicon photodetector, and some simple electronic circuitry. The overall cost could be less than \$20. On the other hand, a typical system used for long-distance, high-bandwidth telecommunication that employs wavelength-division multiplexing, erbium-doped fiber amplifiers, external modulation using DFB lasers with temperature compensation, fiber Bragg gratings, and high-speed infrared photodetectors could cost tens or even hundreds of thousands of dollars. The basic question is "how much information is to be sent and how far does it have to go?"

## 1.2 Types of Fiber

- Step-index multimode

- Step-index single mode

- Graded-index

## 1.2.1 Fiber-Optic Transceivers Overview

A fiber-optic transceiver is simply a transmitter-receiver pair. A transceiver is tasked with transmitting and receiving data (1's and 0's). A fiber-optic transceiver accomplishes this task by either turning the light source on or off. Transceivers fall under two categories: LED transceivers and laser transceivers. LEDs are generally more cost effective and extremely reliable. However, due to the nature of the technology, LEDs are limited to shorter link distances and slower speeds. Lasers are generally higher in power and emit a signal of better quality, resulting in longer-link distances. Lasers are used for applications requiring greater speeds.

## 1.2.2 Multimode Communication Links

Multimode communication links are generally the most common, due to the low cost of fiber cabling and transceivers. When forming a multimode link, one must use multimode transceivers as well as multimode cabling. Multimode fiber cable is generally specified as two numbers such as  $62.5/125 \mu m$  or  $50/125 \mu m$ . This specification implies a core size of  $62.5 \mu m$  in diameter and a cladding size of  $125 \mu m$ .  $62.5/125 \mu m$  cabling is generally the most popular, followed by  $50/125 \mu m$ . For historical reasons,  $62.5/125 \mu m$  cabling has a large install base. However,  $50/125 \mu m$  cabling is generally recommended for all new installations to allow for an upgrade path to gigabit (and beyond) speeds.

Multimode fiber cable is called multimode because the light used to transmit the data actually travels multiple paths within the fiber core. The fiber cable is designed with a core and cladding index difference to keep the majority of light energy within the fiber so that the light 'bounces' around. At the other end of the fiber, a data signal is composed of the light beams that took straight paths through the center of the core, as well as the light beams that 'bounced' around. This bouncing-around phenomenon is called modal dispersion. Modal dispersion is the primary characteristic that limits multimode fiber cable link distances.

The major benefits of multimode fiber are as follows.

- Multimode fiber is relatively easy to work with.

- Because of multimode fiber's larger core size, light is easily coupled to and from multimode fiber.

- Multimode fiber can be used with both lasers and LEDs as sources.

- Coupling losses are less than those of single-mode fiber.

The drawback of multimode fiber is that because many modes are allowed to propagate (a function of core diameter, wavelength, and numerical aperture), multimode fiber suffers from modal dispersion. The result of modal dispersion is bandwidth limitation, which translates into lower data rates.

## 1.2.3 Single-Mode Communication Links

Single-mode communication links are less common than multimode links, but single-mode communication links are quickly gaining ground when longer link distances (>3 km) are required. When constructing a single-mode link, the engineer must use single-mode transceivers with single-mode cabling. Single-mode fiber is also specified as two numbers such as  $9/125 \ \mu$ m. The two numbers imply a core of just 9  $\mu$ m, and a cladding 125  $\mu$ m in diameter.

9/125 µm cabling is generally the most common, followed by 8/125 µm. Single-mode cabling is typically slightly more expensive that the multimode counterparts, but can reach distances up to 10 or 20 times farther. The whole idea behind a single-mode link path is that light carrying the data travels a single path. Light energy that strays away from the center path leaves the core and becomes trapped in the cladding due the properties of single-mode cabling. Because almost all the light received at the opposite end travels approximately the same path, modal dispersion (or timing jitter) is no longer a factor. The primary distance-limiting factor for single-mode links is signal power (or amplitude).

## 1.3 Transmission Windows

Optical fiber transmission uses wavelengths that are in the near-infrared portion of the spectrum. These wavelengths are just above the visible spectrum, and therefore undetectable to the unaided eye. Typical optical transmission wavelengths are 850 nm, 1310 nm, and 1550 nm. Both lasers and LEDs are used to transmit light through optical fiber. Lasers are usually used for 1310-nm or 1550-nm single-mode applications. LEDs are used for 850-nm or 1300-nm multimode applications. These ranges are the wavelength ranges that optical fiber transmission operates best.

## 1.3.1 Fiber-Optic Standards

## Table 1. Fiber-Optic Standards

| WAVELENGTH | MODE        |

|------------|-------------|

| 850 nm     | Multimode   |

| 1300 nm    | Multimode   |

| 1310 nm    | Single-mode |

| 1550 nm    | Single-mode |

These wavelengths were chosen because they best match the transmission properties of available light sources with the transmission qualities of optical fiber.

## 1.3.2 Advantages of Fiber-Optic

- Galvanic isolated and robust communication interface

- Cabling distance is greater than UTP cable to meet demand of widely range (communicate over longer distances) and reduced communication failures

- Harsh environment capability: electromagnetic interference (EMI) immunity (insensitive to EMI), high temperature, high pressure, high voltage

- No grounding is required

- Intrinsically safe

- Small size and lightweight

- Integrated telemetry: fiber itself is a data link

- Wide bandwidth

- High sensitivity

## 1.3.3 Disadvantages of Fiber-Optic

- More challenge for cable installation

- Must use expensive fiber-optic cable and connectors

- Need for more expensive optical transmitters and receivers

- · Cannot carry electricity to operate or power terminal devices

## 1.4 Ethernet Fiber-Optic

Copper-based Ethernet connections are limited to a data transmission distance of only 100 meters when using unshielded twisted pair (UTP) cable. By using fiber conversion solution, fiber-optic cabling can be used to extend data transmission over greater distances. An Ethernet with fiber can also be used where there is high level of EMI, which is a common phenomenon found in industrial plants. This interference can cause corruption of data over copper-based ethernet links. Data transmitted over fiber-optic cable, however, is completely immune to this type of noise.

Since fiber can transport more data over longer distances than copper cabling, increased distances provide the ability to reach more users and equipment. Fiber has complete immunity to electrical interference, and provides higher security than copper cabling because fiber has no electro-magnetic emission. These characteristics have made fiber an ideal medium for commercial, utility, government, and financial networks. Distances supported by fiber network infrastructure are limited mostly by the optical power, or brightness, supplied by the active hardware interface. Fiber distances can range from 300 meters to 140 kilometers, depending on the type of media converter, cable, wavelength, and data rate.

The use of Ethernet fiber-optics in LANs has increased due to the inherent advantages of fiber and high data rates can be maintained without electromagnetic (or radio-frequency) interference. Fiber offers higher voltage isolation, intrinsic safety, and elimination of ground loops in geographically-large installations.

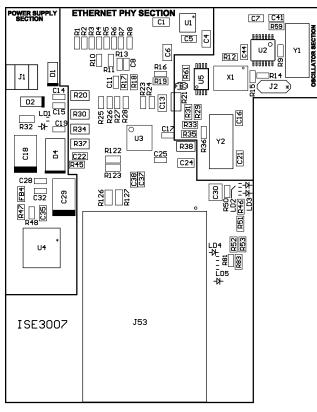

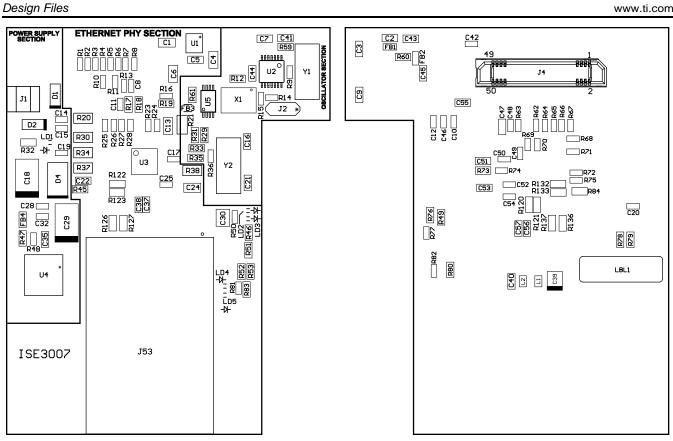

This reference design platform demonstrates the advanced performance of the TLK10xL Ethernet PHY transceiver devices. The brick provides an IEEE 802.3u 100BASE-FX fiber Interface. This reference design operates from a single power supply (5 V with on-board regulator or 3.3 V). All other voltages required for the Ethernet PHY transceiver are generated internally within the device.

This Ethernet PHY brick reference design enables Texas Instruments' customers to quickly design and release to market systems using TI industrial Ethernet PHY transceiver devices. A 50-pin interface has been provided to interface with a 32-bit Cortex M4 processor-based controller board. The board has been designed in a small (2 inches x 3 inches) form factor, which makes it easy to fit into any of the present products.

Table 2. Design Features

|                                | 5                                                                                                                                                                                                                       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ethernet PHY                   | <ul> <li>The TLK105L Ethernet PHY features:</li> <li>Industrial temperature rating: -40°C to 85°C</li> <li>Configurable PHY addresses – resistor strapping</li> <li>MII or RMII – resistor strapping options</li> </ul> |

| Ethernet fiber-optic interface | 1300 nm, multimode, Ethernet 100 base-FX                                                                                                                                                                                |

| Power consumption              | Single Supply: <275 mW, <850 mW for fiber-optic                                                                                                                                                                         |

| Power supply                   | The device is designed for power-supply flexibility and can operate with a single 3.3-V power supply                                                                                                                    |

| Power input options            | <ul> <li>5 V from external 2-pin connector</li> <li>5-V DC input from MII and on-board regulator to generate 3.3 V</li> <li>3.3-V DC input from MII interface with no on-board regulator</li> </ul>                     |

| MAC – controller interface     | 50-pin MII interface connector                                                                                                                                                                                          |

| Clock                          | 25-MHz crystal with internal oscillator                                                                                                                                                                                 |

| Status LEDs                    | Two LEDs<br>[(Link and activity with option to configure as Pull Up (PU) or Pull<br>Down (PD)]                                                                                                                          |

| ESD                            | IEC61000-4-2 – Level 3, Criteria B                                                                                                                                                                                      |

## 2 Design Features

Block Diagram

www.ti.com

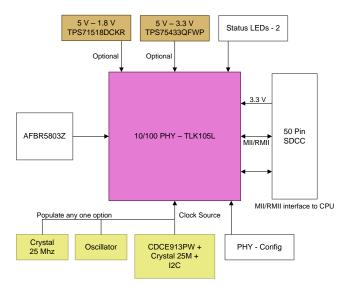

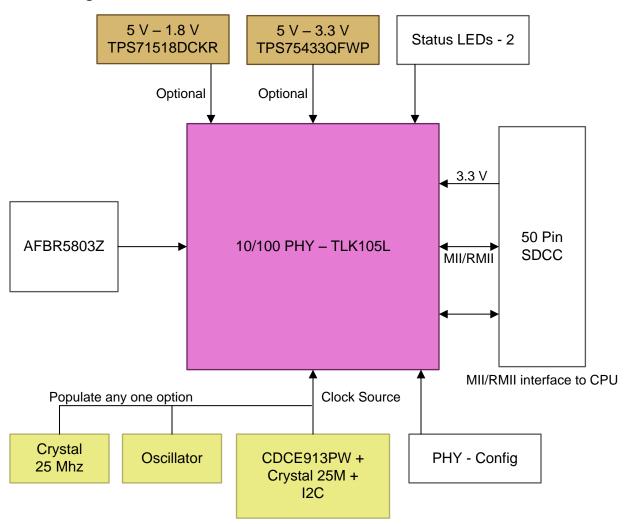

# 3 Block Diagram

Figure 2. Block Diagram

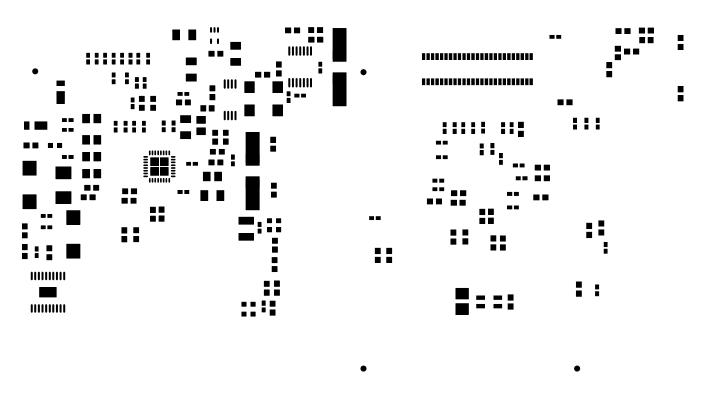

## 4 Board Pictures

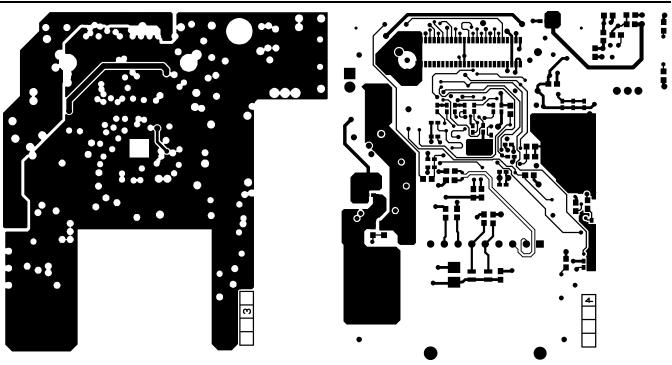

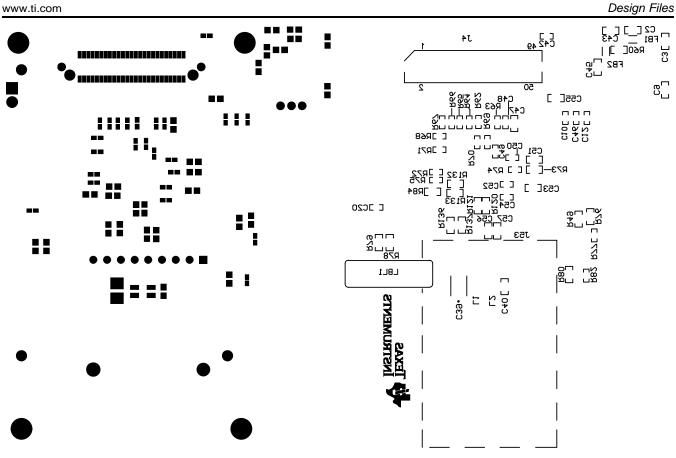

Figure 3. Board Picture – Top

Figure 4. Board Picture – Bottom

## 5 Highlighted Products

For more information on each of these devices, see the respective product folders at <u>www.ti.com</u>.

## 5.1 Single Port 10/100 Mbs Ethernet Physical Layer Transceiver

The Ethernet PHY used in the reference design is TLK105L. The major features of the Ethernet PHY are described as follows.

## 5.1.1 MAC Data Interface (MII)

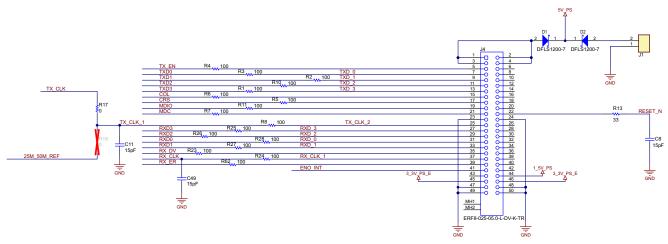

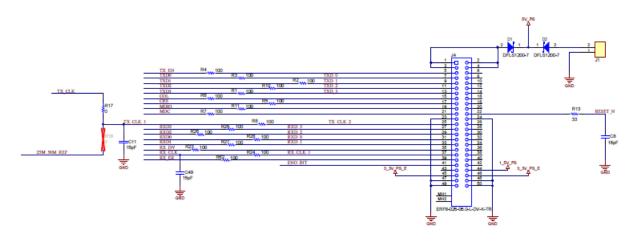

TLK105L is a single port 10/100 Mbs Ethernet physical layer transceiver. In this reference design, the Ethernet PHY brick is interfaced to the MAC through the MII interface.

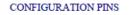

## 5.1.2 Bootstrap Configuration

Provision is provided to configure the PHY through resistors. The details are provided in Section 6.

## 5.1.3 LED

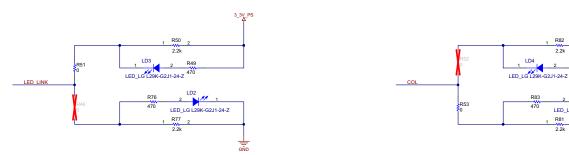

An option for two LEDs has been provided.

- Activity

- Link

The LEDs can be configured as active pull-up or active pull-down.

#### 5.1.4 Clock Circuit

For the MII interface, the clock source is a 25-MHz crystal with internal oscillator.

## 5.2 Ethernet - Fiber Transceiver - 100BASE-FX

The TLK10xL supports 100Base-FX signaling via an external optical transceiver. AFBR-5803Z/ FDDI, 100 Mb/s ATM, and Fast Ethernet Transceiver is used in this design.

## 5.3 MII (MAC) - Controller Interface

The interface to the controller is through a 50-pin high speed connector. The male connector is mounted on the controller board, and the female connector is on the Ethernet PHY brick board. The female connector has the MII interface signals and the power input (5-V DC or 3.3-V DC).

## 5.4 Power Supply

The Ethernet PHY operates on a single power supply. The Ethernet PHY brick board can be powered by:

- External 5 V

- 5 V from the controller board

- 3.3 V from the controller board

## 5.4.1 Filtering

The required filter capacitors have been provided in the reference design.

## 6 Circuit Design and Component Selection

## 6.1 Single Port 10/100 Mbs Ethernet Physical Layer Transceiver

## 6.1.1 MAC Data Interface (MII)

TLK105L is a single port 10/100 Mbs Ethernet physical layer transceiver which has the signals for the MII interface shown in Figure 5.

| РНҮ              |           | MAC |

|------------------|-----------|-----|

| TX_CLK           | TX_CLK    |     |

| TX_EN            | TX_EN     |     |

| TXD [3:0]        | TXD [3:0] |     |

|                  | RX_CLK    |     |

| RX_CLK           | RX_DV     |     |

| RX_DV<br>RX_ER   | RX_ER     |     |

|                  | RXD [3:0] |     |

| RXD [3:0]<br>CRS | CRS       |     |

| COL              | COL       |     |

|                  |           |     |

|                  |           |     |

## Figure 5. MII Signaling

The Media Independent Interface (MII) is a synchronous, 4-bit wide nibble data interface that connects the PHY to the CPU MAC in 100B-TX and 10B-T modes. The MII is fully compliant with IEEE802.3-2002 clause 22.

The MII signals are summarized as follows:

- Data signals TXD [3:0],RXD [3:0]

- Transmit and receive-valid signals TX\_EN,RX\_DV

- Line-status signals CRS (carrier sense)

- COL (LED\_LINK )

Additionally, the MII interface includes the carrier sense signal CRS, as well as a collision detect signal COL. The CRS signal asserts to indicate the reception of data from the network or as a function of transmit data in half-duplex mode. The COL signal asserts as an indication of a collision, which can occur during half-duplex operation when both transmit and receive operations occur simultaneously.

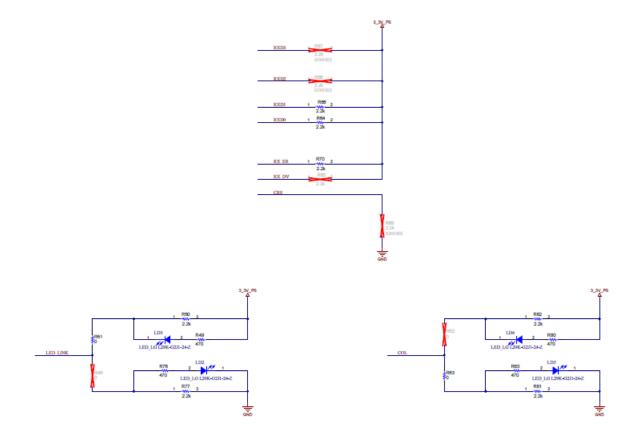

#### 6.1.2 Bootstrap Configuration

Bootstrap configuration is a convenient way to configure the TLK10xL device into specific modes of operation. Some of the functional pins are used as configuration inputs, as shown in Figure 6. The logic states of these pins are sampled during reset and are used to configure the TLK10xL device into specific modes of operation. Table 3 describes bootstrap configuration. A 2.2-k $\Omega$  resistor is used for pull-down or pull-up to change the default configuration. If the default option is desired, there is no need for external pull-up or pull-down resistors. Because these terminals may have alternate functions after reset is deasserted, these terminals must not be connected directly to V<sub>cc</sub> or GND.

| TERMINAL            | COMPONENTS   | DESCRI                                                                                                                                                                                                                                                                                                                 | DTION                                                                                                                                                                                                                                                                                                                                    |                                         |  |

|---------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| TERMINAL            | OF THE BOARD | DESCRI                                                                                                                                                                                                                                                                                                                 | PTION                                                                                                                                                                                                                                                                                                                                    |                                         |  |

| PHYAD0 (COL)        | R52, R53     |                                                                                                                                                                                                                                                                                                                        | <b>PHY Address [4:0]:</b> The TLK10xL provides five PHY address terminals, the states of which are latched into an internal register at system hardware reset. The TLK10xL supports PHY Address values 0 (<00000>) through 31 (<11111>). PHYAD [4:1] terminals have weak internal pull-down resistors, and PHYAD [0] has a weak internal |                                         |  |

| PHYAD1 (RXD_0)      | R64,         |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

| PHYAD2 (RXD_1)      | R65,         |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

| PHYAD3 (RXD_2)      | R66,         | pull-up r                                                                                                                                                                                                                                                                                                              | esistor, setting the default PHYAD                                                                                                                                                                                                                                                                                                       | if no external resistors are connected. |  |

| PHYAD4 (RXD_3)      | R67          |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

| AN_0 (LED_LINK)     | R46, R51     | AN_0: F                                                                                                                                                                                                                                                                                                                | D-HD config. FD = pull-up.                                                                                                                                                                                                                                                                                                               |                                         |  |

|                     |              | The default wake-up is autonegotiation enable 100BT.         AN_0       Forced Mode         0       10Base-T, Half-duplex         100Base-TX, Half-duplex       100Base-TX, Half-duplex         1       10Base-T, Half- or full-duplex         100Base-TX, Half- or full-duplex       100Base-TX, Half- or full-duplex |                                                                                                                                                                                                                                                                                                                                          | able 100BT.                             |  |

|                     |              |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

|                     |              |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

|                     |              |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

| LED_CFG (CRS)       | R69          | <b>LED Configuration:</b> This option selects the operation mode of the LED_LINK terminal (the default mode is Mode 1). All modes are also configurable via register access. See PHY Control Register (PHYCR), Address 0x0019.                                                                                         |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

| AMDIX_EN<br>(RX_ER) | R70          | Auto-MDIX Enable: This option sets the Auto-MDIX mode. By default, it enables Auto-MDIX. An external pull-down resistor disables Auto-MDIX mode.                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

| MII_MODE<br>(RX_DV) | R63          | MII Mode Select: This option selects the operating mode of the MAC data interface.<br>This terminal has a weak internal pull-down, and it defaults to normal MII operation<br>mode. An external pull-up causes the device to operate in RMII mode.                                                                     |                                                                                                                                                                                                                                                                                                                                          |                                         |  |

#### Table 3. Bootstrap Configuration

R82

2.2k

2.2k

R80

470

LD5 2 1 LED\_LG L29K-G2J1-24-Z R81 2

3\_3V\_PS

GND

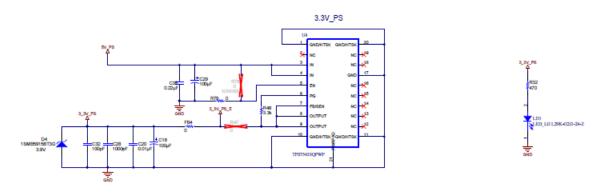

#### 6.1.3 LED

The TLK10xL devices support the use of two LEDs. The LEDs can be configured for pull-up or pull-down using the resistors as shown in Figure 7.

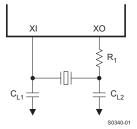

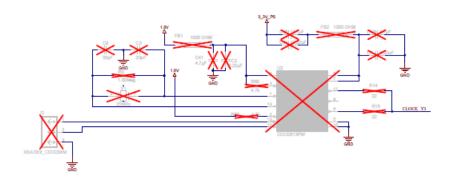

## 6.1.4 Clock Circuit [Clock In (XI) Requirements]

The TLK10xL supports an external CMOS-level oscillator source or an internal oscillator with an external crystal. The use of a 25-MHz, parallel, 20-pF load crystal is recommended if a crystal source is desired. Figure 8 shows a typical connection for a crystal resonator circuit. The load capacitor values will vary with the crystal vendors; check with the vendor for the recommended loads.

The oscillator circuit is designed to drive a parallel-resonance AT-cut crystal with a minimum drive level of 100  $\mu$ W and a maximum of 500  $\mu$ W. If a crystal is specified for a lower drive level, a current limiting resistor must be placed in series between XO and the crystal. As a starting point for evaluating an oscillator circuit, if the requirements for the crystal are not known, set the values for CL1 and CL2 at 33 pF, and set R1 at 0  $\Omega$ . Specifications for a 25-MHz crystal are listed in Table 4.

Figure 8. Crystal Oscillator Circuit

| PARAMETER              | TEST CONDITIONS         | MIN | ТҮР | MAX | UNIT |

|------------------------|-------------------------|-----|-----|-----|------|

| Frequency              |                         |     | 25  |     | MHz  |

| Frequency<br>tolerance | Operational temperature |     |     | ±50 | ppm  |

| Frequency stability    | 1 year aging            |     |     | ±50 | ppm  |

| Rise / Fall time       | 10%–90%                 |     |     | 8   | nsec |

| Jitter (short term)    | Cycle-to-cycle          |     | 50  |     | psec |

| Jitter (long term)     | Accumulative over 10 ms |     |     | 1   | nsec |

| Symmetry               | Duty cycle              | 40% |     | 60% |      |

| Load capacitance       |                         |     | 15  | 30  | pF   |

#### Table 4. 25-MHz Oscillator Specifications

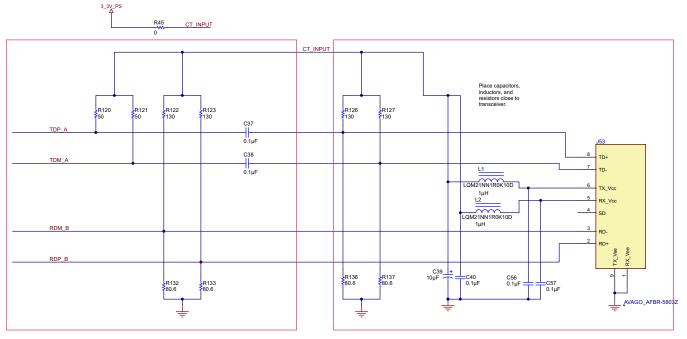

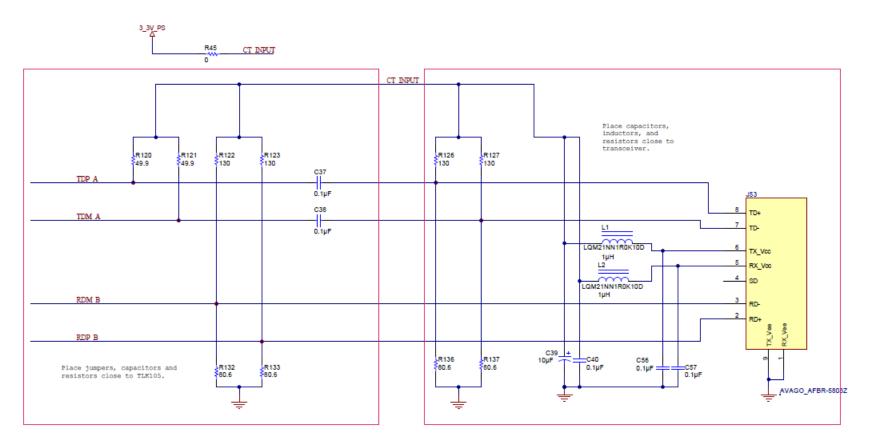

## 6.2 Ethernet - Fiber Transceiver - 100BASE-FX

Figure 9. Ethernet - Fiber Transceiver - 100BASE-FX

## 6.2.1 Transmitter Sections

The transmitter section of the AFBR-5803Z utilizes 1300–nm surface-emitting, InGaAsP LEDs. These receiver sections are packaged in the optical subassembly portion of the transmitter section. These LED are driven by a custom silicon IC, which converts differential PECL logic signals, ECL referenced (shifted) to a 3.3-V supply, into an analog LED drive current.

## 6.2.2 Receiver Sections

The receiver sections of the AFBR-5803Z utilize InGaAsPIN photodiodes coupled to a custom silicon trans-impedance preamplifier IC. These are packaged in the optical subassembly portion of the receiver. These pin and preamplifier combinations are coupled to a custom-quantizer IC which provides the final pulse shaping for the logic output and the signal detect function. The data output is differential. The signal-detect output is single-ended. Both data and signal-detect outputs are PECL compatible, ECL referenced (shifted) to a 3.3-V or 5-V power supply.

In 100BASE-FX mode, the device-transmit pins connect to an industry standard fiber transceiver with PECL signaling through a capacitively-coupled circuit. In FX mode, on the TX path, the device bypasses the scrambler and the MLT3 encoder, enabling the transmission of serialized 5B4B-encoded, NRZI data at 125 MHz. On the RX path, the device bypasses the MLT3 decoder and the descrambler, enabling the reception of serialized 5B4B-encoded, NRZI data at 125 MHz. The only added functionality in the aspect of data transmission for 100BASE-FX (compared to 100BASE-TX) is the support of far-end fault detection and transmission.

## 6.2.3 Far-End Fault (FEF) Mechanism

Because 100BASE-FX does not support autonegotiation, a far-end fault facility is included in the design. The far-end fault facility allows detection and transmission of link failures. When no signal is being received as determined by the signal detect function, the device sends a far-end fault indication to the far-end peer.

#### Circuit Design and Component Selection

www.ti.com

The far-end fault indication detects repeating cycles. Each cycle consists of 84 ones followed by a single zero. The cycle pattern will not satisfy the 100BASE-FX carrier sense mechanism. However, the cycle pattern is easily detected as the fault indication. The cycle pattern will be transparent to devices that do not support far-end fault detection. The far-end fault detected, the link monitor is forced to de-assert link status, causing the device to begin transmitting far-end fault signaling to the far-end peer.

## 6.3 MII(MAC) - Controller Interface

The Ethernet PHY has been interfaced and tested with the TM4C129XNCZAD 32-bit ARM® Cortex<sup>™</sup>-M4F MCU. The drivers required to interface TLK105L to the MCU are available.

Figure 10. MII (MAC) - Controller Interface

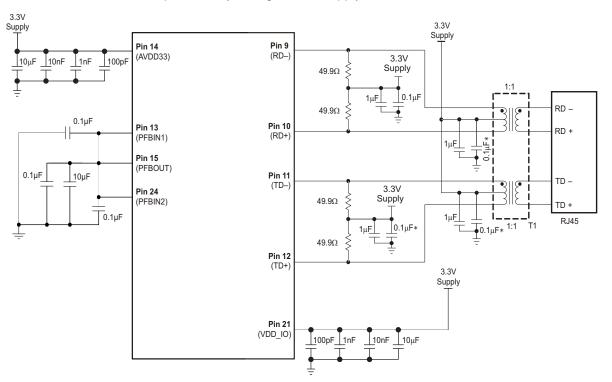

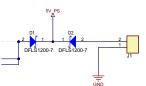

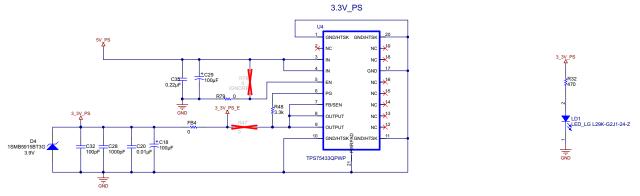

# 6.4 Power Supply

The Ethernet PHY can be powered by a single 3.3-V supply.

Figure 11. Power Connections for Single Supply Operation

The Ethernet PHY brick board can be powered by either of the following two methods as shown in Figure 12 and Figure 13.

Figure 12. Powered By External 5 V or 5 V from the Controller Board

## 6.4.1 Filtering

Bypass the power rails with the following low-impedance surface mount capacitors: 10  $\mu$ F, 10 nF, 1 nF, and 100 pF. To reduce EMI, place the capacitors as close as possible to the component's V<sub>DD</sub> supply pins, preferably between the supply pins and the vias connecting to the power plane. In some systems, it may be desirable to add 0- $\Omega$  resistors in series with supply pins, as the resistor pads provide flexibility by adding an EMI bead when the design needs to meet system–level certification and testing requirements.

PCBs should have at least one solid ground plane and one solid  $V_{DD}$  plane to provide a low impedance power source to the component. This also provides a low impedance return path for non-differential digital MII and clock signals. Place a 10.0-µF capacitor near the PHY component for local bulk bypassing between the  $V_{DD}$  and ground planes. The rise time of the  $V_{DD}$  should typically be 500 µs.

| Table 5. | Power | Consumption | at 3.3 | ۷ |

|----------|-------|-------------|--------|---|

|----------|-------|-------------|--------|---|

| PARAMETERS                   | POWER (MAX) |

|------------------------------|-------------|

| Ethernet PHY – single supply | 270 mW      |

| Fiber-optic – transmit       | 600 mW      |

| Fiber-optic - receive        | 250 mW      |

| Total                        | 1220 mW     |

## 6.5 4.5 Fiber-Optic Cords Ideal for Ethernet Applications

Figure 14. Fiber-Optic Cords

Fiber-optic patch cords are ideal for high data-rate systems including FDDI, multimedia, Ethernet backbone, ATM, or any network that requires the transfer of large and time-consuming files.

## Features

- · Ideal for use in Ethernet applications

- High bandwidth supporting longer distances

## Table 6. Major Specifications for Fiber-Optic Cords for Ideal Use in Ethernet Application

| First connector  | SC duplex         |

|------------------|-------------------|

| Second connector | SC duplex         |

| Cable diameter   | 0.12" (3 mm)      |

| Cable type       | Buffered fiber    |

| Fiber type       | 62.5/125          |

| Length - overall | 16.4' (5 m)       |

| Туре             | Multimode, duplex |

## SC Connector

- The SC connector is a fiber-optic connector, with a push-pull latching mechanism which provides quick insertion and removal, while also ensuring a positive connection.

- The SC connector has been standardized as FOCIS 3 (Fiber Optic Connector Intermateability Standards) in EIA/TIA-604-03.

Circuit Design and Component Selection

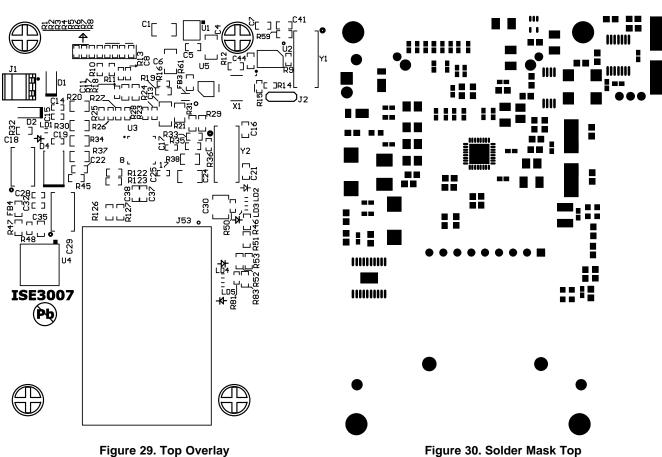

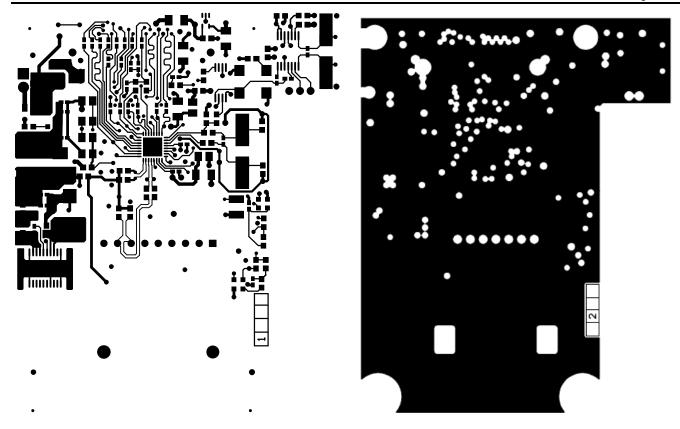

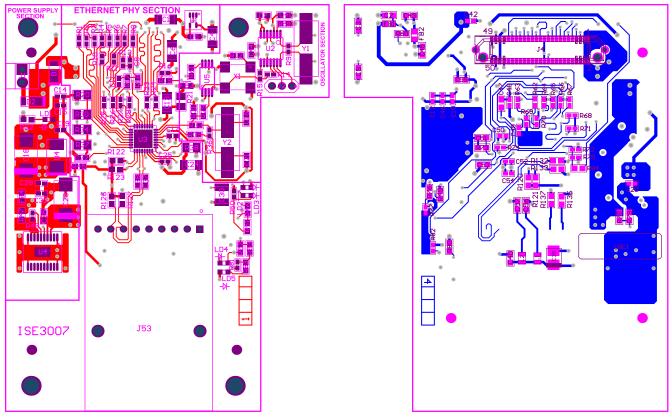

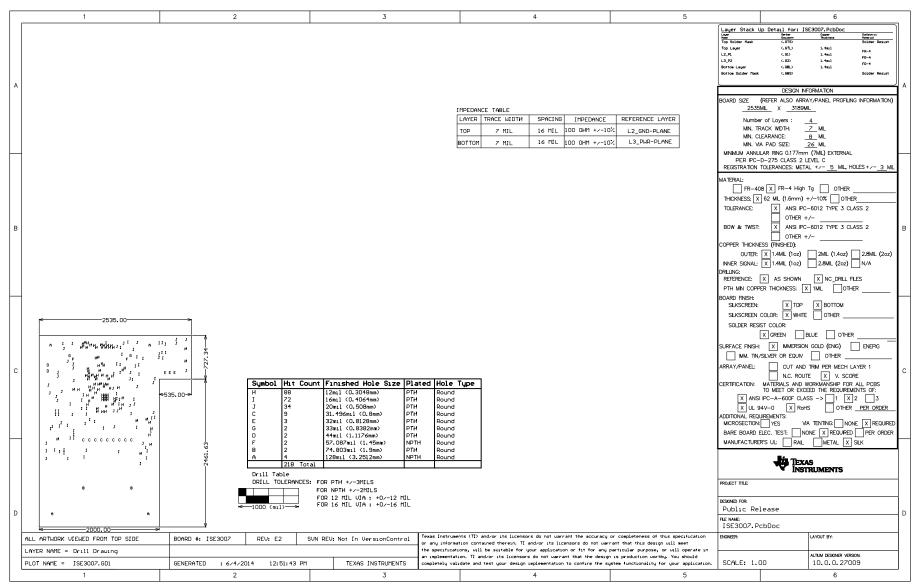

## 6.6 PCB Dimensions and Physical Layout

Figure 15. PCB Dimensions and Physical Layout

## **PCB Dimensions**

Total dimensions - the current board is 3 inch × 2 inches. The board has provisions for the following:

- Power supply

- Ethernet PHY and associated components

- RMII interface

The size can be reduced based on the application.

- **PCB Physical Layout**

- FR4 material

- Trace impedance differential impedance 100 ohms, ±5%

- Uniform supply and ground plane

- Four layers

- Combination of through-hole and surface-mount technology

# 6.7 ESD Protection

The network or medium dependent interface (MDI) connection is via the transmit (TD+ and TD–) and receive (RD+ and RD–). Both transmit and receive are ESD protected. On-chip HBM, ESD protection on RD $\pm$  and TD $\pm$  of 16 kV is provided.

# 7 Software Description

Software Description

# Table 7. Software Description

| FUNCTIONALITY                   | CONFIGURATION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware reset                  | A hardware reset is accomplished by applying a low pulse (TTL level), with a duration of at least 1 $\mu$ s, to /RESET. This pulse resets the device so that all registers are reinitialized to default values, and the hardware configuration values are re-latched into the device (similar to the power-up/reset operation). The time from the point when the reset pin is de-asserted to the point when the reset has concluded internally is approximately 200 $\mu$ s.                                                                                                                                                                                                                                                                                                       |

| External MII PHY initialization | Set the external PHY address (as per the boot strap<br>configuration).<br>All the read and write requests to the PHY use the configured<br>external PHY address.<br>Reset the PHY:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                 | <ol> <li>MII reset - Set the BMCR (0x00) register bit 15 to one.</li> <li>Software/Digital reset - Set PHYRCR (0x1F) data register<br/>bit15 and bit14 to one.</li> <li>Issue a delay of 500 microseconds.</li> <li>Set the BMCR (0x00) register autonegotiation enable and<br/>autonegotiation restart by setting bit-12 and bit-8 to one.</li> <li>Poll the BMSR (0x01) register bit5 to check if autonegotiation is<br/>complete.</li> </ol>                                                                                                                                                                                                                                                                                                                                    |

| MII_MODE                        | The MII_MODE is selected by pin 26 (RX_DV). This pin has internal weak pull-down and defaults to MII mode. (External pull-up makes the PHY to operate in RMII mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PHY ID                          | PHY ID is decided by the pull-up registers (refer to the Bootstrap section of <i>Industrial Temp, Single Port 10/100Mbs Ethernet Physical Layer Transceiver</i> , TLK105L/6L Data Sheet <u>SLLSEE3</u> ). Care has to be taken that the appropriate PHY id is used for appropriate hardware bootstrap configuration (per pull-up registers). This values of pins 29, 30, 31, 32, and 1 (PHYAD0/COL, PHYAD1/ RXD0, PHYAD2/ RXD1, PHYAD3/ RXD2, and PHYAD4/ RXD3) are latched into an internal register at hardware reset.                                                                                                                                                                                                                                                           |

| LED configuration               | Pin 17 and pin 29 can be used for LED configuration either as pull-up or pull-down. Pin 17 indicates link status (fully lit) by default; activity is indicated by blinking the same LED. If the designer needs to use pin 29 for indicating LED status, MLEDCR has to be configured. Configuring MLEDCR provides an option to route the activity signal to pin 29 instead of pin 17. In order to route the activity signal to pin 29 instead of pin 17, the COL signal has to be disabled. For further details. refer the LED Interface section of <i>Industrial Temp, Single Port 10/100Mbs Ethernet Physical Layer Transceiver</i> , TLK105L/6L Data Sheet SLLSEE3.                                                                                                              |

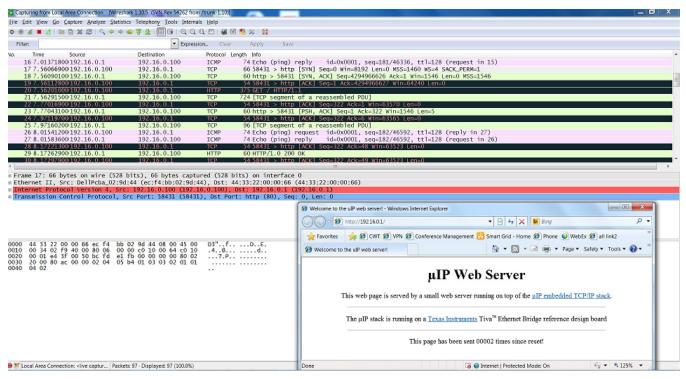

| Testing TLK105L                 | This design has been created with the assumption that the hardware is connected to one end of the Ethernet cable and the other end of the Ethernet cable is connected to the PC. TX clock and RX clock can be probed or measured (after the PHY is powered up and not in reset state). Initiate a ping request with an IP address that is within the PC's subnet. For example, 192.16.0.100 is the PC IP address and 255.255.255.0 is the subnet mask. Initiate a ping command, for example, ping 192.16.0.1 –t TX[0:3] and RX[0:3]. The ping result will show some data patterns. Ping will create traffic at every plug-in of the Ethernet cable. After some time, when a destination host unreachable message is seen, there may not be a further Ethernet message on the wire. |

## 7.1 FO Register Configuration for TLK105L

| BIT   | NAME                           | DEFAULT         | FUNCTION                                                                                                                                                                                                                                                                                                                                                           |

|-------|--------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | FX FEF<br>faulting status      | RO, LH          | Asserted when the FEF (far-end fault) detection mechanism detects FEF signaling from the far-end peer.                                                                                                                                                                                                                                                             |

| 14    | FX PECL<br>signaling<br>status | RO ,LH          | Asserted if the FX receiver detects violation of the PECL signaling from the optic transceiver (such as glitches or invalid pulse width).                                                                                                                                                                                                                          |

| 13    | FX SD status                   | RO, LL          | Indicates the Status of SD_IN signal in the fiber RX path. If SD_IN is de-<br>asserted, SD_IN will be latched low. Upon read, the value of the bit will be<br>updated with the current value.                                                                                                                                                                      |

| 12:10 | RESERVED                       | 011, RO         |                                                                                                                                                                                                                                                                                                                                                                    |

| 9     | Enable auto<br>SD Indication   | 0, RW           | When asserted, this bit enables auto detection of the SD_IN signal based on the optic transceiver output. This mode assumes that when SD_IN is low, the optic transceiver does not transmit valid PECL signaling. The Auto SD_IN feature can detect Valid PECL signaling, and once detected, Auto SD_IN assumes the SD_IN is asserted and establishes the FX link. |

| 8:0   | RESERVED                       | 1 0110 0100, RO |                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 8. Fiber Mode Control Register, Address 0x00FD

#### Table 9. Fiber Mode Control Register, Address 0x0102

| BIT  | NAME                       | DEFAULT                  | FUNCTION                                                                                                                                                                                                                                                                           |

|------|----------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Enable manual SD_IN Config | 0, RW                    | Allows manual configuration of the SD_IN signal. Manual configuration of the SD_IN signal allows the MAC to control the start of an FX link, assuming the MAC is in 'PHY link partners connected' status. The actual control on the SD_IN is done using bit [14] in this register. |

| 14   | SD_IN manual<br>Config     | 0, RW                    | SD_IN manual control: '1' - notifies the PHY SD_IN is on and '0' notifies the PHY the SD_IN is off. Manual configuration overrides all other SD_IN mechanisms.                                                                                                                     |

| 13:0 | RESERVED                   | 00 0010 0000 0000,<br>RO | Writes ignored, read as 0x200h.                                                                                                                                                                                                                                                    |

## 7.2 Sample Code

EMACPHYWrite(EMAC0\_BASE, ui8PHYAddr, EPHY\_BMCR, EPHY\_BMCR\_SPEED);//Force 100Mbps using register 0x0000

EMACPHYWrite(EMAC0\_BASE, ui8PHYAddr, 0x0040, 0x2000);//set bit 13//force link SysCtlDelay(100);

EMACPHYWrite(EMAC0\_BASE, ui8PHYAddr, EPHY\_CFG2, 0x4000);//set bit 14 for PHY register 0x000A

SysCtlDelay(100);

status = EMACPHYRead(EMACO\_BASE, ui8PHYAddr, EPHY\_BMSR);//PHY register 0x0001

SysCtlDelay(100);

// EMACPHYExtendedWrite(EMAC0\_BASE, ui8PHYAddr, 0xFD, 0x0200);

status = EMACPHYExtendedRead(EMAC0\_BASE, ui8PHYAddr, 0xFD);

SysCtlDelay(10000);

## 8 Test Results

# 8.1 Functional Testing

# Table 10. Functional Testing

| Clock                         | 25 MHz    |

|-------------------------------|-----------|

| V <sub>cc</sub> ( 3 V–3.6 V ) | 3.31-V DC |

| Internal 1.55 V               | 1.55-V DC |

| MII interface                 | ОК        |

| Link and activity LED         | ОК        |

Test Results

## 8.2 Communication Interface Testing (Computer to Device)

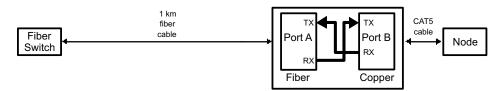

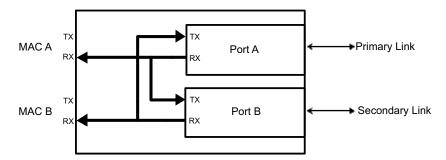

Media converter mode, shown in Figure 16, allows conversion of copper to fiber and conversion of fiber to copper at 100 Mbs. This configuration allows longer-run fiber to be used in situations where fiber support is not built into the end device. This configuration can also be combined with power over Ethernet on the copper side.

Figure 16. Media Converter Example

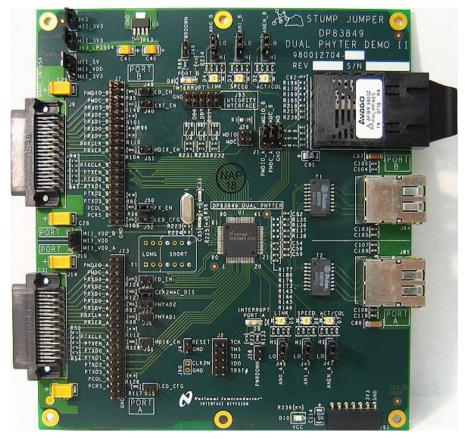

Figure 17. DP83849IVS-EVK with Copper and Fiber Options

Figure 18. DP83849IVS-EVK Connected with FO-Brick

Figure 19. FO-Brick Connected to Tiva TM4C129XNCZAD (TIDA-00226)

#### Test Results

#### 8.2.1 Extender/Media Converter Implementation

The PHYTER dual incorporates two methods of configuring extender/media converter mode: via a simple strap option or register control. *The definitions of extender and media converter only differ in their physical (copper or fiber) interfaces; the port swapping is the same.* The optional use of RMII mode in conjunction with Extender/Media Converter mode allows flexibility in the system design.

## 8.2.2 Notes and Restrictions

Both ports must be operating at the same speed (100 MBPS). This can be accomplished using straps or port register controls. Both ports must be in full-duplex mode. Both ports must use a common-clock mode, either RMII mode (RBR:RMII\_EN = 1) or single clock MII mode (RBR:SCMII\_RX = 1 and RBR:SCMII\_TX = 1) to ensure synchronous operation. If single clock MII mode is used and only one RX to TX path is enabled, RBR:SCMII\_RX in the RX port and RBR:SCMII\_TX in the TX port must be set to 1. Media Conversion is only supported in 100-Mb mode.

## 8.2.3 Strapped Extender or Media Converter Mode

The PHYTER dual provides a simple strap option to automatically configure both ports for extender or media converter mode, shown in Figure 20, with no device register configuration necessary. The RXD\_2\_B/EXTENDER\_EN strap is used in conjunction with two autonegotiation straps (LED\_ACTCOL/AN\_EN, LED\_SPD/AN1), the RMII mode strap (RX\_DV/MII\_MODE), and the fiber mode (COL/FX\_EN) strap to allow many possible configurations.

If extender mode is strapped but RMII mode is not strapped, both ports will automatically be configured for single clock MII receive and transmit modes. *Note that in strapped extender/media converter mode, the RX MAC interfaces are still active, allowing easy monitoring of the data received on each port.*

Figure 20. Extender/Media Converter (Strapped)

Several common configurations are shown in Table 11. Note that either single-clock MII or RMII can be configured independently from the flexible port mode. However, there is a requirement that both ports must be configured to the same common-clock mode.

Since the EXTENDER\_EN strap forces full-duplex mode (including autonegotiation advertisement), the AN0 (duplex) strap is not shown. If the receive MII ports are to be monitored, energy-detect and power-down modes should be disabled.

|                           | A           | UTONEGOTIA  | TION STRAP  | FIBER MOD   | DE STRAPS |         |                                                   |

|---------------------------|-------------|-------------|-------------|-------------|-----------|---------|---------------------------------------------------|

| MODE                      | AN_EN_A     | AN1_A       | AN_EN_B     | AN1_B       | FX_EN_A   | FX_EN_B | NOTES                                             |

| 100-Mb copper<br>extender | 1           | 1           | 1           | 1           | 0         | 0       | Advertise 10/100 Mb<br>full-duplex                |

|                           | 0           | 1           | 0           | 1           | 0         | 0       | Force 100-Mb full-<br>duplex                      |

| 100-Mb fiber<br>extender  | Do not care | Do not care | Do not care | Do not care | 1         | 1       | No autonegotiation                                |

| 100-Mb copper<br>extender | 1           | 0           | 1           | 0           | 0         | 0       | Advertise 10-Mb full-<br>duplex                   |

|                           | 0           | 0           | 0           | 0           | 0         | 0       | Force 10-Mb full-<br>duplex                       |

| 100-Mb media<br>converter | Do not care | Do not care | 1           | 1           | 1         | 0       | Port A is fiber, B is copper with autonegotiation |

|                           | 1           | 1           | Do not care | Do not care | 0         | 1       | Port A is copper with autonegotiation, B is fiber |

|                           | Do not care | Do not care | 0           | 1           | 1         | 0       | Port A is fiber, B is copper-forced               |

|                           | 0           | 1           | Do not care | Do not care | 0         | 1       | Port A is copper-<br>forced, B is fiber           |

Table 11. Common Strapped Extender/Media Converter Mode Configurations

www.ti.com

## Table 12. Jumper Tables

| JUMPER          | NAME                                                              | FUNCTION                                                                                                                                                                 | SETTING       |

|-----------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| AUTONEGOTIATION | I                                                                 |                                                                                                                                                                          |               |

| J42             | ANEN_B                                                            | Port B – enable/disable autonegotiation                                                                                                                                  | Jumpered-low  |

| J43             | AN1_B                                                             | Port B – forced/advertised<br>operation mode in<br>autonegotiation                                                                                                       | Jumpered-low  |

| J44             | AN0_B                                                             | Port B – forced/advertised<br>operation mode in<br>autonegotiation                                                                                                       | Jumpered-high |

| J45             | AN0_A                                                             | Port A – forced/advertised<br>operation mode in<br>autonegotiation                                                                                                       | Jumpered-high |

| J46             | AN1_A                                                             | Port A – forced/advertised<br>operation mode in<br>autonegotiation                                                                                                       | Jumpered-high |

| J47             | ANEN_A                                                            | Port A – enable/disable autonegotiation                                                                                                                                  | Jumpered-high |

| FUNCTION        |                                                                   |                                                                                                                                                                          |               |

| J40             | XTENDER_EN                                                        | Allow extender mode (For DP83849IVS/IFVS)                                                                                                                                | Jumpered      |

| J41             | CLK2MAC_DIS                                                       | Disable clock to MAC output                                                                                                                                              |               |

| J48             | PWRDOWN_INT_B                                                     | Port B – allow power down and interrupt mode                                                                                                                             |               |

| J49             | ED_EN_B Port B – enable energy dete<br>mode                       |                                                                                                                                                                          |               |

| J50             | FX_EN_B Port B – enable fiber mode<br>(For DP83849IDVS/IFVS)      |                                                                                                                                                                          | Jumpered      |

| J51             | MDIX_EN_B Port B – enable/disable MDIX mode (default is enabling) |                                                                                                                                                                          | Jumpered-high |

| J52             | LED_CFG_B                                                         | Port B – allow LEDs<br>configuration. See Industrial<br>Temp, Single Port 10/100Mbs<br>Ethernet Physical Layer<br>Transceiver, TLK105L/6L Data<br>Sheet <u>SLLSEE3</u> . |               |

| J55             | LED_CFG_A                                                         | Port A – allow LEDs<br>configuration. See Industrial<br>Temp, Single Port 10/100Mbs<br>Ethernet Physical Layer<br>Transceiver, TLK105L/6L Data<br>Sheet <u>SLLSEE3</u> . |               |

| J56             | MDIX_EN_A                                                         | Port A – enable/disable MDIX mode (default is enabling)                                                                                                                  | Jumpered-high |

| J57             | ED_EN_A                                                           | Port A – enable energy detect mode                                                                                                                                       |               |

| J58             | PWRDOWN_INT_A                                                     | Port A – allow power down and interrupt mode                                                                                                                             |               |

| J13             | PCOL_A                                                            |                                                                                                                                                                          | Jumpered      |

| J92             | 3V3                                                               | Remove jumper and connect<br>3.3 V to power externally, use<br>J13 ground pins                                                                                           |               |

## 8.2.4 Ping Test

| File Edit View Go Capture Ana                              | lyze Statistics Telephony Tools                                                  | s Internals Help | In .                                                                                                                                                             |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                            |                                                                                  |                  |                                                                                                                                                                  |  |  |  |  |

| Filter: Clear Apply                                        |                                                                                  |                  |                                                                                                                                                                  |  |  |  |  |

| No. Time Source                                            | Destination                                                                      | Protocol         | Length Info                                                                                                                                                      |  |  |  |  |

| 133 97.861046 192.16.0.1                                   |                                                                                  | ICMP             | 74 Echo (ping) repty id=0x0001, seq=35734975, tt=128                                                                                                             |  |  |  |  |

| 134 98.862251 192.16.0.1                                   |                                                                                  | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3876/9231, t1=128                                                                                                            |  |  |  |  |

| 135 99.864300 192.16.0.1                                   |                                                                                  | ICMP             | 74 Echo (ping) reply id=0x0001, seq=877/9487, tt1=128                                                                                                            |  |  |  |  |

| 136 100.865202 192.16.0.1                                  |                                                                                  | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3878/9743, ttl=128                                                                                                           |  |  |  |  |

| 137 101.866381 192.16.0.1                                  | 192.16.0.100                                                                     | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3879/9999, ttl=128                                                                                                           |  |  |  |  |

| 138 102.868328 192.16.0.1                                  | 192.16.0.100                                                                     | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3880/10255 ±±1=128                                                                                                           |  |  |  |  |

| 139 103.869210 192.16.0.1                                  | 192.16.0.100                                                                     | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3881 🗰 Command Prompt - ping 192.16.0.1 -t 💷 📼                                                                               |  |  |  |  |

| 140 104.871517 192.16.0.1                                  |                                                                                  | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3882 puper for 100 10 of hubber 20 him fine fire fire 75 at 20                                                               |  |  |  |  |

| 141 105.873248 192.16.0.1                                  |                                                                                  | ICMP             | 74 Echo (phig) reply ru=0x0001, seq=3885 parts from 100 10 0 1 hubbrr 00 him (1m TTL 100                                                                         |  |  |  |  |

| 142 106.875364 192.16.0.1                                  |                                                                                  | ICMP             | 74 Ecro (pring) repry rueoxood, seq-soon parts from too to be here the XII atoo                                                                                  |  |  |  |  |

| 143 107.876520 192.16.0.1                                  |                                                                                  | ICMP             | 74 Echo (pring) repry rueox0001, seq 3883 parti from 100 10 0 to but sector TTL-100                                                                              |  |  |  |  |

| 144 108.878551 192.16.0.1                                  |                                                                                  | ICMP             | 74 ECHO (pHig) Fepty Tu=0x0001, Seq=3660 public face 100 10 0 1 hubber 00 him (1m 77) at 00                                                                      |  |  |  |  |

| 145 109.880628 192.16.0.1                                  | 192.16.0.100                                                                     | ICMP             | 74 Echo (ping) reply id=0x0001, seq=3887 Reply from 192.16.0.1: bytes=32 time <ims 192.16.0.1:="" bytes="32" from="" reply="" time<ims="" tl="128&lt;/td"></ims> |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192 16 A 1; butes:32 time(1ms TTL:128                                                                                                                 |  |  |  |  |

| Frame 1: 169 bytes on wire                                 |                                                                                  |                  |                                                                                                                                                                  |  |  |  |  |

|                                                            |                                                                                  |                  | Pv6mcast_00:01:00:02 (33:33:00:01:00:02) Reply from 192.16.0.1: bytes=32 time<1ms TL=128                                                                         |  |  |  |  |

|                                                            |                                                                                  |                  | 30::e1a1:d05:8d95:9603), Dst: ff02::1: 2 (ff02::1: Reply from 192.16.0.1: bytes:32 time(ims TTL=128                                                              |  |  |  |  |

| User Datagram Protocol, Si<br>DHCPv6                       | C Port: ancpvb-client (54                                                        | (6), DST POPT:   | hepry from 152.10.0.11 byces-52 crime(ins fre-120                                                                                                                |  |  |  |  |

| P DHCPV0                                                   |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time<1ms TL=128                                                                                                                  |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time<1ms TTL=128                                                                                                                 |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time<1ms TL=128                                                                                                                  |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1; bytes=32 time(1mm TTL=128                                                                                                                 |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1; bytes:32 time(1ms TTL:128                                                                                                                 |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time<1ms TTL=128<br>Reply from 192.16.0.1: bytes=32 time=1ms TTL=128                                                             |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 times/ms TL=128                                                                                                                  |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time/ims TL=128                                                                                                                  |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time/ims TL=128                                                                                                                  |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time(1ms TTL=128                                                                                                                 |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time<1ms TTL=128                                                                                                                 |  |  |  |  |

|                                                            |                                                                                  |                  | Reply from 192.16.0.1: bytes=32 time<1ms TTL=128                                                                                                                 |  |  |  |  |

| 0000 33 33 00 01 00 02 ec 1                                | F4 bb 02 9d 44 86 dd 60 0                                                        |                  | Reply from 192.16.0.1: bytes=32 time<1ms TTL=128                                                                                                                 |  |  |  |  |

| 0010 00 00 00 73 11 01 fe 8                                | 30 00 00 00 00 00 00 e1 a                                                        |                  | Reply from 192.16.0.1: bytes=32 time<1ms TTL=128                                                                                                                 |  |  |  |  |

| 0020 0d 05 8d 95 96 03 ff 0<br>0030 00 00 00 01 00 02 02 2 | 02 00 00 00 00 00 00 00 00 0<br>22 02 23 00 73 10 4b 01 f                        |                  | A.s.K. Reply from 192.16.0.1: bytes=32 time<1ms TL=128                                                                                                           |  |  |  |  |

| 0040 15 0c 00 08 00 02 00 0                                | 00 00 01 00 0e 00 01 00 0                                                        | )1               | Reply from 192.16.0.1: bytes=32 time<1ms IIL=128                                                                                                                 |  |  |  |  |

| 0050 1a 8c 2d 04 ec f4 bb (                                | 02 9d 44 00 03 00 0c 0e e                                                        | ec               | .D Reply from 192.16.0.1: bytes=32 time<1ms TTL=128                                                                                                              |  |  |  |  |