| Integrated Monolithic MEMS                                                                                                                                                                                                                                          |                                                 |                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|--|--|--|

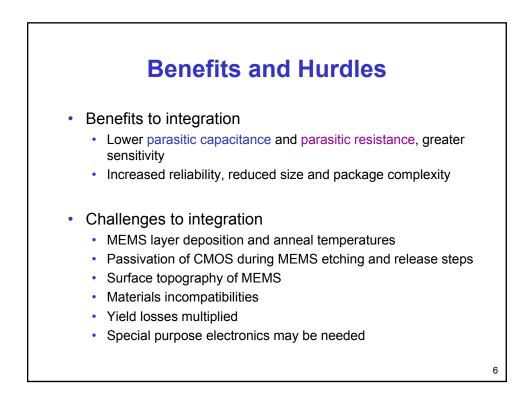

| <ul> <li>Motivation for co-fabrication</li> <li>Improved device performance, higher signal-to-noise ratio</li> <li>Reduced size, power requirement</li> <li>IC compatibility = economical manufacturing</li> <li>Automatic alignment; packaging combined</li> </ul> |                                                 |                        |  |  |  |

|                                                                                                                                                                                                                                                                     | CMOS                                            | Surface Micromachining |  |  |  |

| Common features                                                                                                                                                                                                                                                     | Si-based, same materials and etching principles |                        |  |  |  |

| Process Flow                                                                                                                                                                                                                                                        | Standard                                        | Application specific   |  |  |  |

| Vertical Dimension                                                                                                                                                                                                                                                  | ~1 µm                                           | ~1-5 µm                |  |  |  |

| Lateral Dimension                                                                                                                                                                                                                                                   | <1 µm                                           | 2-10 µm                |  |  |  |

| Complexity                                                                                                                                                                                                                                                          | >10 masks                                       | 2-6 masks              |  |  |  |

|                                                                                                                                                                                                                                                                     |                                                 | 4                      |  |  |  |

| Thermal Budget                                                                                                                                                             |                                   |                                                                              |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------|--|--|

| <ul> <li>Critical temperatures for AI metallization</li> <li>Degradation at T &gt; 400-450°C</li> <li>Junction migration at T = 950°C</li> <li>Junction spiking</li> </ul> |                                   |                                                                              |  |  |

| <ul> <li>Critical process temperatures for MEMS</li> </ul>                                                                                                                 |                                   |                                                                              |  |  |

|                                                                                                                                                                            | Temperature                       | Material                                                                     |  |  |

| LPCVD                                                                                                                                                                      | 450°C<br>610<br>650<br>800<br>950 | LTO/PSG<br>Low stress polySi<br>Doped polySi<br>Nitride<br>PSG densification |  |  |

|                                                                                                                                                                            | 1050                              | PolySi stress annealing<br>W. Yun, PhD Thesis, BSAC 5                        |  |  |

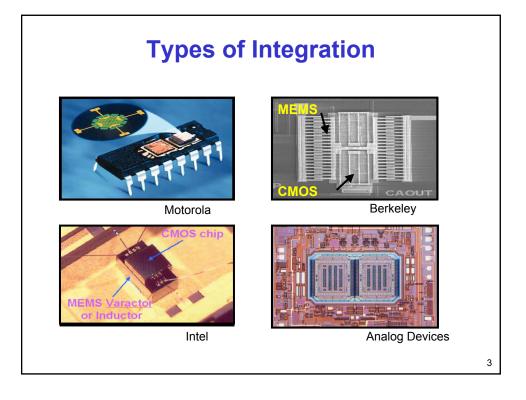

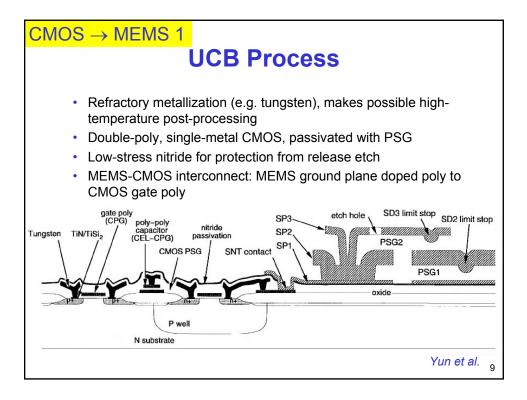

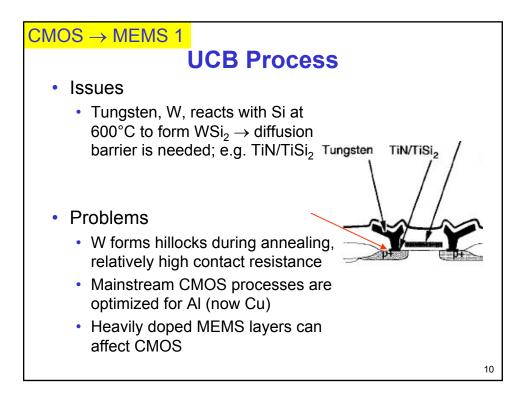

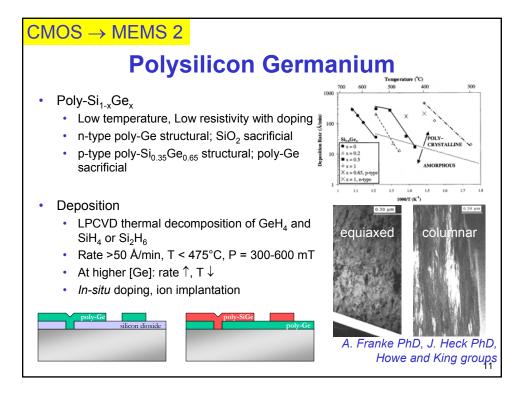

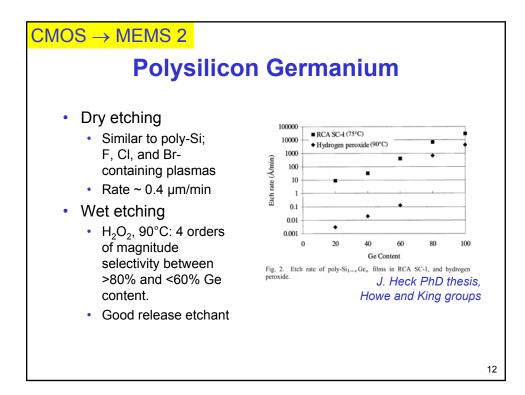

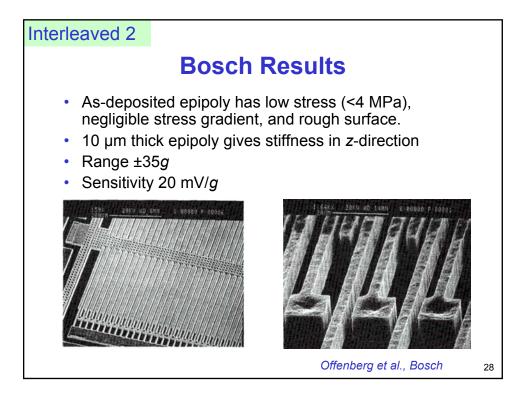

## **This Lecture** Modular processes CMOS before MEMS UC Berkeley Modular Integration UCB polysilicon germanium SOI MEMS, UCB and Analog Devices MEMS before CMOS Sandia Labs MM/CMOS Interleaved CMOS and MEMS • Analog Devices BiMEMS Bosch epipoly MEMS by CMOS foundry ٠ • Parameswaran et al., University of Alberta, 1988 • Fedder et al., Carnegie Mellon, 1996 7

| Modular Processes                                                                                                                                                                                                                                                                 |   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

| <ul> <li>CMOS before MEMS</li> <li>+ IC foundry can be used</li> <li>+ Chip area may be minimized</li> <li>- Thermal budget is an issue</li> </ul>                                                                                                                                |   |  |  |

| <ul> <li>MEMS before CMOS         <ul> <li>No thermal budget for MEMS</li> <li>Microstructure topography is an issue</li> <li>Electronics and MEMS cannot be easily stacked</li> <li>IC foundries are wary of pre-processed wafers (materials constraints)</li> </ul> </li> </ul> |   |  |  |

|                                                                                                                                                                                                                                                                                   | 8 |  |  |

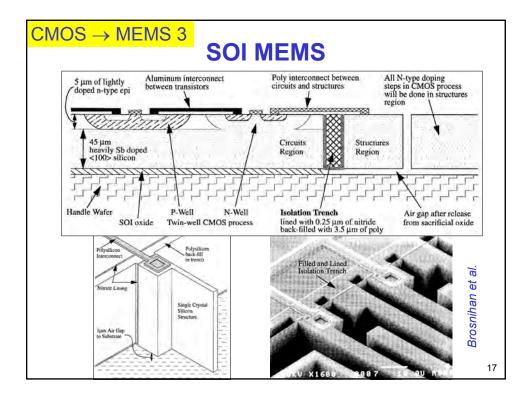

| $CMOS \to MEMS\ 3$                     |                               |  |  |  |

|----------------------------------------|-------------------------------|--|--|--|

| <b>SOI Accelerometer Parameters</b>    |                               |  |  |  |

|                                        |                               |  |  |  |

| Chip size                              | $3.4 \times 2.9 \text{ mm}^2$ |  |  |  |

| Sensor size                            | $1 \times 1.5 \text{ mm}^2$   |  |  |  |

| <ul> <li>Proof mass</li> </ul>         | 52 µg                         |  |  |  |

| <ul> <li>Resonant frequency</li> </ul> | 3 kHz                         |  |  |  |

| Sense capacitance                      | 9.7 pF                        |  |  |  |

| Full scale                             | ±1.75 g                       |  |  |  |

| <ul> <li>Power consumption</li> </ul>  | 5 V x 5 mA                    |  |  |  |

| Sensitivity                            | 102 fF / <i>g</i>             |  |  |  |

| Noise floor                            | 25 µ <i>g</i> / √Hz           |  |  |  |

| On-chip A/D conversion                 |                               |  |  |  |

|                                        |                               |  |  |  |

|                                        | Lemkin et al. 18              |  |  |  |

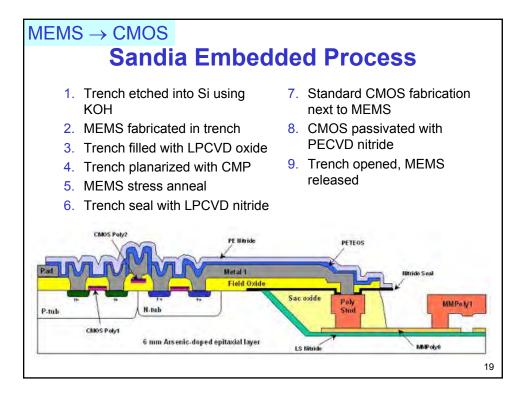

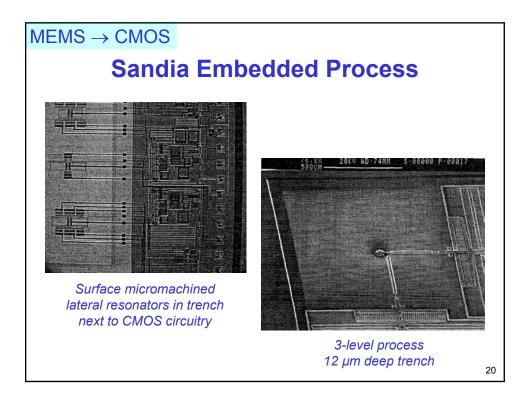

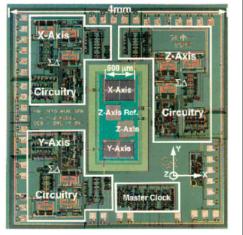

## $\mathsf{MEMS} \to \mathsf{CMOS}$

# Sandia Embedded Process

- 3 axis accelerometer

- 4 × 4 mm<sup>2</sup> chip

- 3 proof masses to capacitively measure acceleration

- X, Y: comb finger array

- Z: parallel-plate capacitor

- Each sensor has own interface circuitry

- Differential circuitry allows sensing of fractions of attoFarad changes in capacitance

- Measures up to ±25 g

M. Lemkin et al. BSAC and Sandia Labs 21

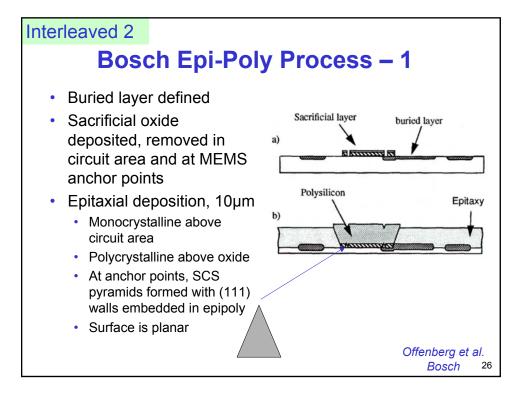

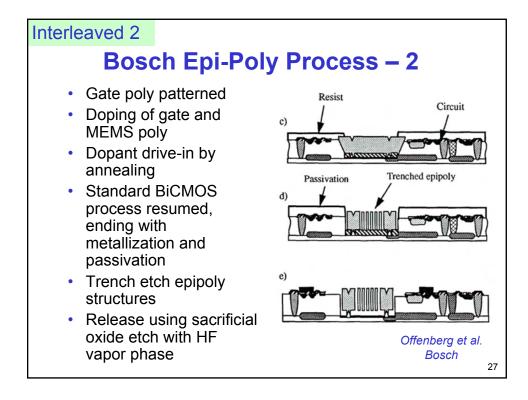

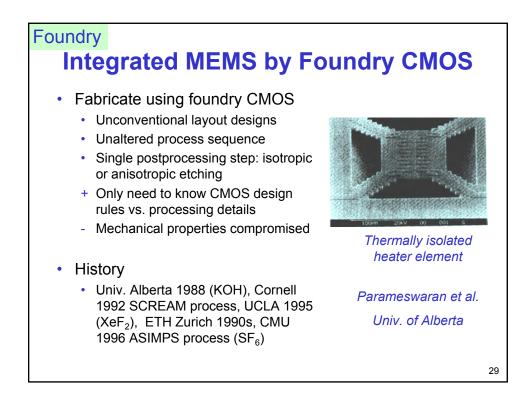

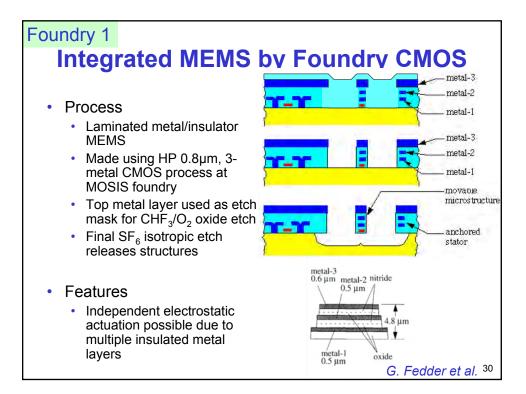

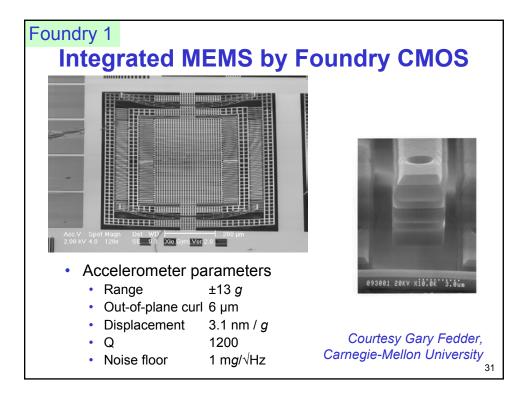

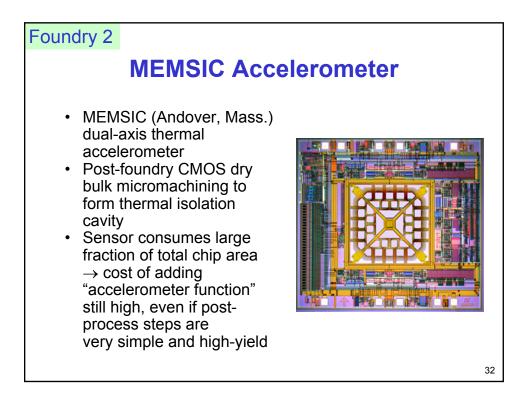

# Interleaved and Foundry Processes CMOS and MEMS mixed More control over materials, processes Optimize or compromise mechanical and electrical components Need your own fab Foundry processes

- + Economical, reliability and yield high

- + Simple post processing step releases MEMS

- Cost of increased chip area

- Mechanical properties of CMOS layers compromised

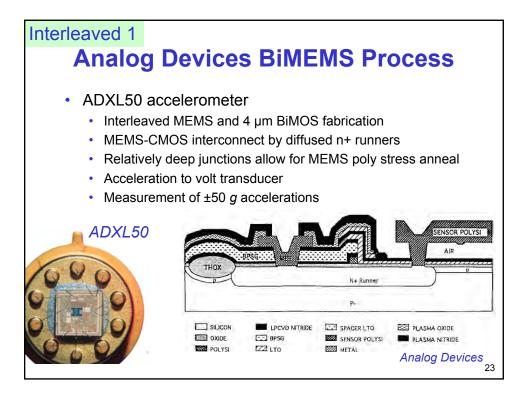

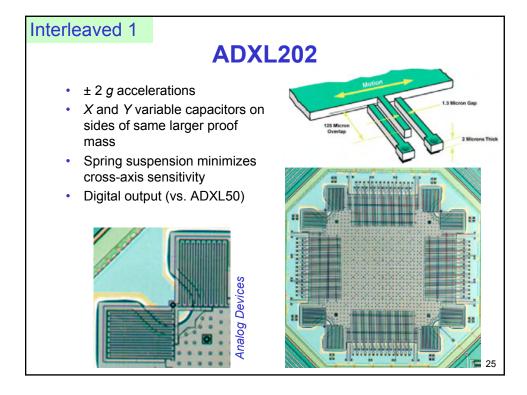

| Interleaved 1                              |                           |                               |  |  |

|--------------------------------------------|---------------------------|-------------------------------|--|--|

| ADXL150 Specifications                     |                           |                               |  |  |

|                                            | ADXL150                   | SOI MEMS                      |  |  |

| Chip size                                  | $3 \times 3 \text{ mm}^2$ | $3.4 \times 2.9 \text{ mm}^2$ |  |  |

| Sensor size                                | $0.6\times0.7\ mm^{2}$    | 1 × 1.5 mm <sup>2</sup>       |  |  |

| Proof mass                                 | 0.28 µg                   | 52 µg                         |  |  |

| <ul> <li>Resonant frequency</li> </ul>     | 12 kHz                    | 3 kHz                         |  |  |

| <ul> <li>Open-loop displacement</li> </ul> | 1.7 nm/ <i>g</i>          |                               |  |  |

| Sense capacitance                          | 120 fF                    | 9.7 pF                        |  |  |

| Full scale                                 | ±5 g                      | ±1.75 <i>g</i>                |  |  |

| <ul> <li>Shock survival</li> </ul>         | 1000 <i>g</i>             |                               |  |  |

| <ul> <li>Power consumption</li> </ul>      | 5 V x 8 mA                | 5 V x 5 mA                    |  |  |

| Sensitivity                                | 200 mV/ <i>g</i>          | 102 fF/ <i>g</i>              |  |  |

| Noise floor                                | 0.6 m <i>g</i> /√Hz       | 25 µg/√Hz                     |  |  |

|                                            |                           |                               |  |  |

|                                            |                           | 24                            |  |  |

# Summary

- CMOS first

- State-of-the-art CMOS foundries can be used

- · Thermal budget of metallization to be accounted for

### MEMS first

- No thermal budget to worry about

- Possible materials incompatibilites (high dopant structural layers, piezoelectrics)

- Topography to overcome

- Interleaved

- Potentially greater control over process steps

- First commercially proven integrated process

- Possibly compromises both CMOS and MEMS

33