(intel)

# INTEL<sup>®</sup> SILICON PHOTONICS: From Research to product

MARCH 8, 2017

#### LING LIAO

Principal Engineer Silicon Photonics Product Division

## **2016 PRODUCT ANNOUNCEMENT AND CELEBRATION**

CNET

Intel: Our laser chips will make sites like Google and Facebook faster

Intel Circuit Marching Band in RNB Courtyard – Silicon Photonics Harmony Bay PRQ Celebration

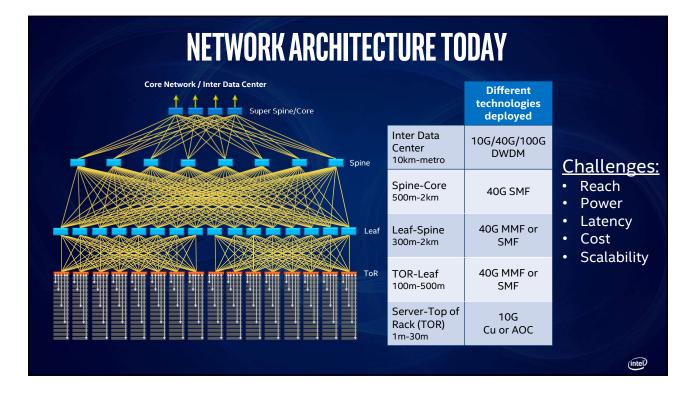

# **EMERGENCE OF HYPER SCALE DATA CENTERS**

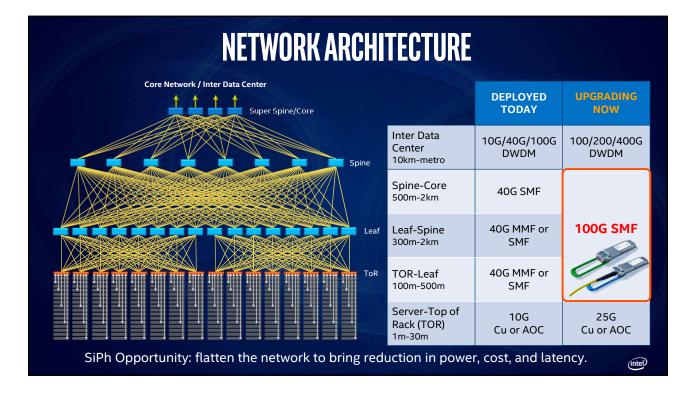

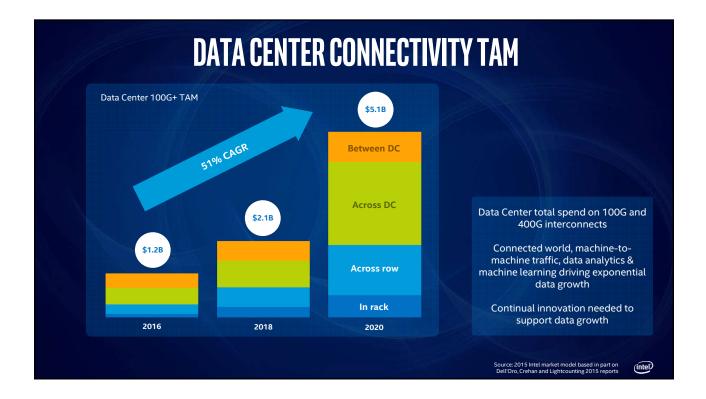

Data center networks are struggling to keep up with exponential data growth

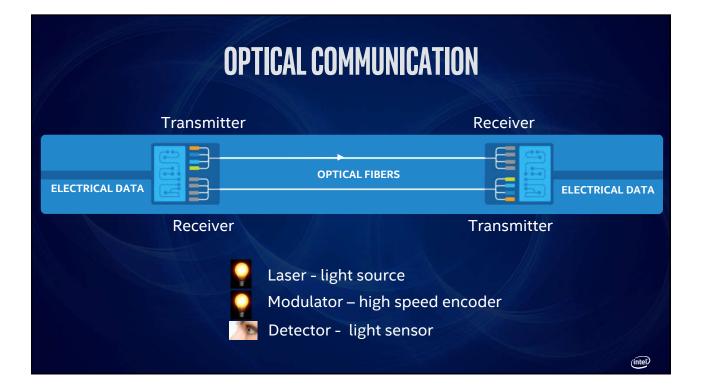

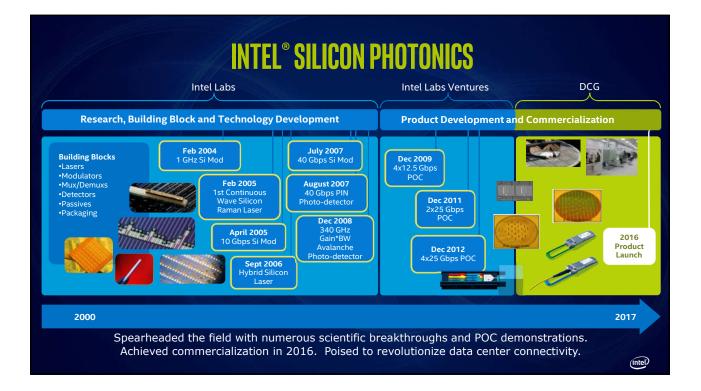

# **SILICON PHOTONICS**

#### TRADITIONAL OPTICS

- Compound semiconductor platform

- Specialized tools and processes

- Relatively low-degree of integration

#### **SILICON PHOTONICS**

- All silicon or silicon-compatible platform

- CMOS manufacturing of photonics

- High density interconnects made at wafer scale

(intel) 6

# **DESIGN: DFX AND PDK**

### DFM/DFT/DFD early to reduce cost and TTM

#### Process Design Kit (PDK)

Standardized Component Library

#### Documentation

- Process design rules

- Package and Assembly design rules

- o Tapeout procedure

#### Automated Verification

- Design rule check (DRC)

- Layout vs schematic (LVS): verify device type, connectivity and parameters

- Parasitic extraction (PEX)

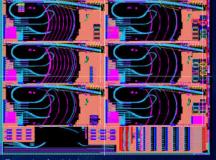

Example of reticle layout: Note heavy use of polygon (non-Manhattan) layout which makes photonics layout tedious vs CMOS

(intel)

# **FAB: ADOPT AND REUSE**

#### Leverage CMOS manufacturing infrastructure and methodologies

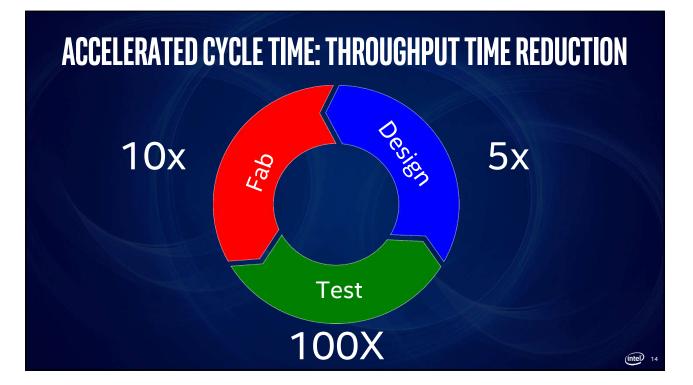

- Cycle time: fast TPT and priority processing can achieve additional 3-4x improvement

- Change control: all changes are documented and reviewed (Whitepapers and xCCB)

- Process control: 1000's of process and tool parameters are monitored and recorded

• <u>"Shift-left"</u>: in-line data and control/spec limits are used to disposition material early

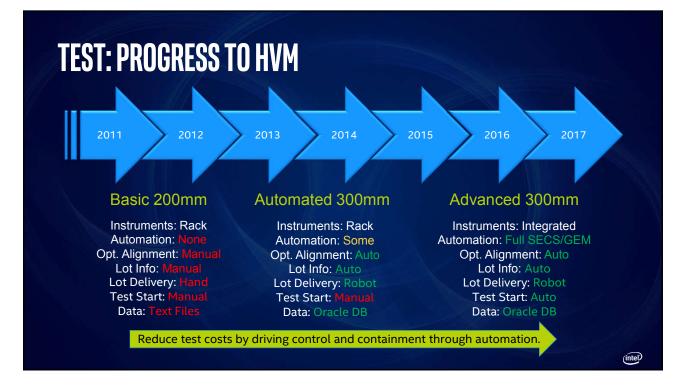

**TEST: ADOPT AND RETROFIT**

## **MODULE PACKAGING**

- PIC and EIC die placement

- Epoxy attach and cure

- Wirebond/flip-chip

- Plasma clean

- ...

#### **Optical products - unique consideration**

- Optical packaging

- Sub-µm alignment

- Stack-up tolerance control

- Mechanical stability over T and life

- Optical back-reflection control

- Thermal management

- Assembly process thermal budget

- Heat dissipation

- Stress management

- Stress/strain reduction

- Stress profile managment

(intel) 1

(intel) 23

## **LEGAL NOTICES AND DISCLAIMERS**

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <u>http://www.intel.com/performance</u>.

Intel, the Intel logo, Xeon and others are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others.

© 2016 Intel Corporation.