• H. B. Bakoglu, Circuits, Interconnections, and Packaging for VLSI, Addison-Wesley Publishing Company.

o J. A. Davis, J. D. Meindl, Interconnect technology and design for gigascale integration, Kluwer. Academic Publishers.

• Nurmi, J.; Tenhunen, H.; Isoaho, J.; Jantsch, A., Interconnect-Centric Design for Advanced SOC and NOC, Springer.

o C.-K. Cheng, J. Lillis, S. Lin, N. Chang, Interconnect Analysis and Synthesis, Wiley Inter-Science.

o Hall, S.H., G. W. Hall and J. McCall, High-Speed Digital System Design, Wiley-Interscience.

o Selected research papers from the literature

3

|                                                                                                                     |          | S        | hort Te  | erm              |          |                            |                              |                |          |

|---------------------------------------------------------------------------------------------------------------------|----------|----------|----------|------------------|----------|----------------------------|------------------------------|----------------|----------|

| Year of Production                                                                                                  | 2005     | 2006     | 2007     | 2008             | 2009     | 2010                       | 2011                         | 2012           | 2013     |

| DRAM ½ Pitch (nm) (contacted)                                                                                       | 80       | 70       | 65       | 57               | 50       | 45                         | 40                           | 36             | 32       |

| MPU/ASIC Metal 1 ½ Pitch<br>(nm)(contacted)                                                                         | 90       | 78       | 68       | 59               | 52       | 45                         | 40                           | 36             | 32       |

| MPU Physical Gate Length (nm)                                                                                       | 32       | 28       | 25       | 22               | 20       | 18                         | 16                           | 14             | 13       |

| Number of metal levels                                                                                              | 11       | 11       | 11       | 12               | 12       | 12                         | 12                           | 12             | 13       |

| Number of optional levels – ground planes/capacitors                                                                | 4        | 4        | 4        | 4                | 4        | 4                          | 4                            | 4              | 4        |

| Total interconnect length (m/cm <sup>2</sup> ) –<br>Metal 1 and five intermediate<br>levels, active wiring only [1] | 1019     | 1212     | 1439     | 1712             | 2000     | 2222                       | 2500                         | 2857           | 3125     |

| FITs/m length/cm <sup>2</sup> × $10^{-3}$ excluding global levels [2]                                               | 4.9      | 4.1      | 3.5      | 2.9              | 2.5      | 2.3                        | 2                            | 1.8            | 1.6      |

| J <sub>max</sub> (A/cm <sup>2</sup> ) – intermediate wire<br>(at 105°C)                                             | 8.91E+05 | 1.37E+06 | 2.08E+06 | 3.08E+06         | 3.88E+06 | 5.15E+06                   | 6.18E+06                     | 6.46E+06       | 8.08E+06 |

| Metal 1 wiring pitch (nm)                                                                                           | 180      | 156      | 136      | 118              | 104      | 90                         | 80                           | 72             | 64       |

| Metal 1 A/R (for Cu)                                                                                                | 1.7      | 1.7      | 1.7      | 1.8              | 1.8      | 1.8                        | 1.8                          | 1.8            | 1.9      |

|                                                                                                                     |          |          | Ma       | mufacturabi<br>1 |          | acturable so<br>Interim so | olutions are<br>olutions are | known<br>known | •        |

## ITRS Interconnect Technology Requirement

|                                                                                                                  | Lo       | ng Terr  | n        |                                                          |                               |                        |          |

|------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------------------------------------------------------|-------------------------------|------------------------|----------|

| Year of Production                                                                                               | 2014     | 2015     | 2016     | 2017                                                     | 2018                          | 2019                   | 2020     |

| DRAM ½ Pitch (nm) (contacted)                                                                                    | 28       | 25       | 22       | 20                                                       | 18                            | 16                     | 14       |

| MPU/ASIC Metal 1 ½ Pitch (nm)(contacted)                                                                         | 28       | 25       | 22       | 20                                                       | 18                            | 16                     | 14       |

| MPU Physical Gate Length (nm)                                                                                    | 11       | 10       | 9        | 8                                                        | 7                             | б                      | б        |

| Number of metal levels                                                                                           | 13       | 13       | 13       | 14                                                       | 14                            | 14                     | 14       |

| Number of optional levels – ground<br>planes/capacitors                                                          | 4        | 4        | 4        | 4                                                        | 4                             | 4                      | 4        |

| Total interconnect length (m/cm <sup>2</sup> ) – Metal 1 and<br>five intermediate levels, active wiring only [1] | 3571     | 4000     | 4545     | 5000                                                     | 5555                          | 6250                   | 7143     |

| FITs/m length/cm <sup>2</sup> × $10^{-3}$ excluding global levels [2]                                            | 1.4      | 1.3      | 1.1      | 1                                                        | 0.9                           | 0.8                    | 0.7      |

| J <sub>max</sub> (A/cm <sup>2</sup> ) – intermediate wire (at 105°C)                                             | 1.06E+07 | 1.14E+07 | 1.47E+07 | 1.54E+07                                                 | 1.80E+07                      | 2.23E+07               | 2.74E+07 |

| Metal 1 wiring pitch (nm)                                                                                        | 56       | 50       | 44       | 40                                                       | 36                            | 32                     | 28       |

| Metal 1 A/R (for Cu)                                                                                             | 1.9      | 1.9      | 2        | 2                                                        | 2                             | 2                      | 2        |

|                                                                                                                  |          | Manufi   |          | utions exist, d<br>Manufactura<br>Inten<br>facturable sc | ble solutions<br>im solutions | are known<br>are known | <b>*</b> |

|                                                                                                                  |          |          |          |                                                          |                               |                        | 23       |

|                              |             | IIRS        | Roa         | lmap        |             |             |

|------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Year                         | 2003        | 2004        | 2005        | 2008        | 2011        | 2014        |

| Parameter                    | 2000        | 2001        | 2000        | 2000        | 2011        | 2011        |

| Technology(nm)               | 120         | 110         | 100         | 70          | 50          | 35          |

| # of Transistors             | 95.2M       | 145M        | 190M        | 539M        | 1523M       | 4308M       |

| Clock Frequency              | 1724 MHz    | 1857 MHz    | 2000 MHz    | 2500 MHz    | 3000 MHz    | 3600 MHz    |

| Chip Area (mm <sup>2</sup> ) | 372         | 372         | 408         | 468         | 536         | 615         |

| Wiring Levels                | 8           | 8           | 8-9         | 9           | 9-10        | 10          |

| Pitch(L/I/G)(nm)             | 330/420/690 | 295/375/620 | 265/340/560 | 185/240/390 | 130/165/275 | 95/115/190  |

| A/R (L/I/G)                  | 1.6/2.2/2.8 | 1.6/2.3/2.8 | 1.7/2.4/2.8 | 1.9/2.5/2.9 | 2.1/2.7/3.0 | 2.3/2.9/3.1 |

| Dielectric Const.            | 2.2-2.7     | 2.2-2.7     | 1.6-2.2     | 1.5         | <1.5        | <1.5        |

|                              | •           | •           | •           | •           | •           | •           |

|                              |             |             |             |             |             |             |

|                              |             |             |             |             |             |             |

| Int                                                                                          | ercon                                                    | nect A                                         | rchite                          | CTURE (Intel 130nm)                  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|---------------------------------|--------------------------------------|

| vias                                                                                         | 6LM 130nm<br>shown (conr<br>ലൂണ്ടാം സ്ഥാ<br>ചാന്ടിം സ്ഥാ | necting layer                                  | s)<br>Hect ratio                |                                      |

| Iralsfron<br>Roly-Sifean<br>Mistell 1<br>Mistell 2, 3<br>Mistell 4<br>Mistell 5<br>Mistell 6 | SC4<br>SSC<br>SSC<br>44S<br>7SC<br>1120<br>1204          | 450<br>160<br>280<br>360<br>570<br>900<br>1200 | 1.6<br>1.6<br>1.5<br>1.6<br>2.0 | P. Bai et al, IEDM 2004              |

|                                                                                              |                                                          |                                                |                                 | Real wiring cross section photograph |

|                                                                                              |                                                          |                                                |                                 | 29                                   |

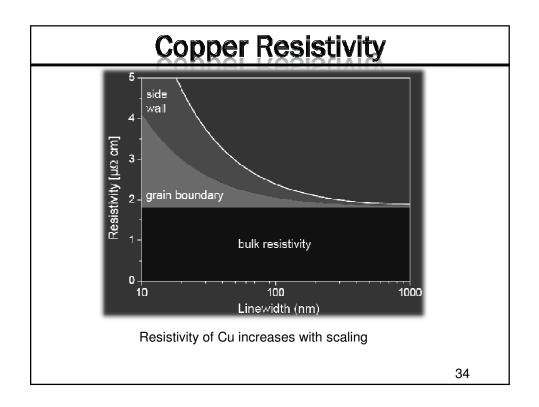

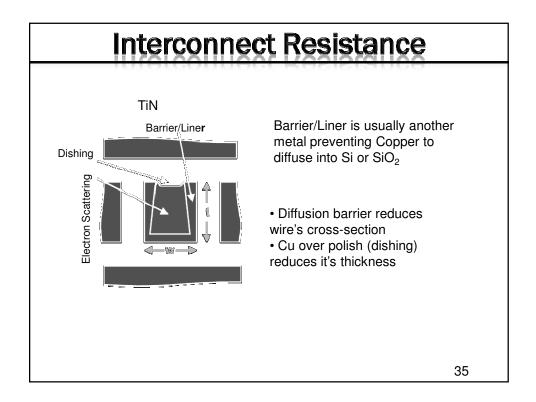

| Modern processes oft<br>Cu atoms diffuse | on, most wires were aluminum<br>ten use copper<br>into silicon and damage FETs<br>led by a diffusion barrier |   |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------|---|

| Metal                                    | Bulk resistivity (mΩ*cm)                                                                                     |   |

| Silver (Ag)                              | 1.6                                                                                                          |   |

| Copper (Cu)                              | 1.7                                                                                                          |   |

| Gold (Au)                                | 2.2                                                                                                          |   |

| Aluminum (Al)                            | 2.8                                                                                                          |   |

| Tungsten (W)                             | 5.3                                                                                                          |   |

| Molybdenum (Mo)                          | 5.3                                                                                                          |   |

|                                          |                                                                                                              | - |

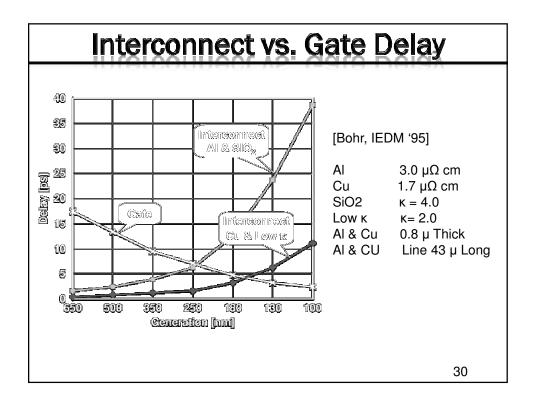

| Interconnect Scaling Scenario                    |        |               |       |  |  |  |

|--------------------------------------------------|--------|---------------|-------|--|--|--|

| Problem with Intercon                            | nects? |               |       |  |  |  |

|                                                  | Tech   | inology gener | ation |  |  |  |

|                                                  | 1um    | 100nm         | 35nm  |  |  |  |

| MOSFET switching delay (ps)                      | ~20    | ~5            | ~2.5  |  |  |  |

| Interconnect <i>RC</i> response time, L=1mm (ps) | ~1     | ~30           | ~250  |  |  |  |

| MOSFET switching energy (fJ)                     | ~30    | ~2            | ~0.1  |  |  |  |

| Interconnect switching energy (fJ)               | ~40    | ~10           | ~3    |  |  |  |

| Calculations made by c<br>bulk resistivity of    |        | 9             |       |  |  |  |

|                                                  |        |               |       |  |  |  |

|                                                  |        |               | 33    |  |  |  |

## **Inductance Figure of Merit** · Should we model wires as full Length (am) transmission line? (no) 10,00 Unless we intentionally make inductance 1. Industance is not important: very wide wires imperiaridescense of $2\sqrt{2C}$ . Heire Koncellan $1 \otimes 2$ Or we are designing the clock grid 1.00 etanet k Transmission line effects can be 1 Ma Inpotenî ignored if the wire is: Very short, when signal transition is slower than 0.10 2. Industance in collimportant Accesses in the large transition firms of the lagst style. the roundtrip delay QØ1 Q.II 0.10 1.0010.00 Very long, when it becomes too lossy ියාන්රික විශ්ය (පත්) (resistance is more than 2Zo) $rL > 2\sqrt{l/c}$ 38

## <text><text><text><text><text><text><text><text><text>

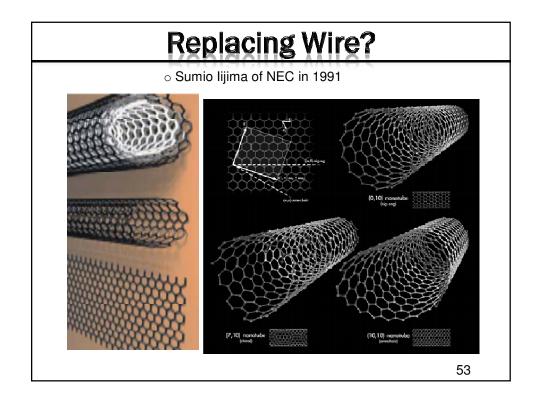

| CNT properties                                                                                                                                                                                                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>Electrical:</li> <li>Ballistic conduction over distances of order 1 micron (~10<sup>-4</sup> Ω·cm).</li> <li>'Metals' with low resistivities, Semiconductors with high mobilities</li> <li>Conductivity a strong function of adsorbates or reactants.</li> </ul> |  |

| Mechanical:<br>• High elastic modulus (high stiffness) (~1 to 5 TPa vs. ~0.2 for steel).<br>• Very high tensile strength (~10 to 100 GPa vs. ~1 for steel).                                                                                                               |  |

| Thermal:<br>• High room temperature thermal conductivity (~2000W/mK vs.<br>~400W/mK for copper).                                                                                                                                                                          |  |

| Electrical Stability:<br>• Maximum current density ( 10 <sup>9</sup> A/cm <sup>2</sup> vs. <10 <sup>7</sup> A/cm <sup>2</sup> for Cu).                                                                                                                                    |  |

| Chemical Stability:<br>• C binding energy in graphene ~12 eV vs. Cu at a Cu surface ~ 4eV                                                                                                                                                                                 |  |

| 54                                                                                                                                                                                                                                                                        |  |