# **Investigation of MOS-Gated Thyristors and Power Diodes**

by

Budong You

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

**Electrical Engineering**

Alex Q. Huang, Chairman Dusan Borojevic Dan Y. Chen Fred C. Lee Robert W. Hendricks

> January 2000 Blacksburg, Virginia

Keywords: Power semiconductor devices, MOS-gated thyristors, Power diodes Copyright 2000, Budong You

# **Investigation of MOS-Gated Thyristors and Power Diodes**

Budong You

#### (ABSTRACT)

The MOS-gated thyristors (MGT) refer to the class of power devices that combine the ease of a MOS gate control with the superior current carrying capability of a thyristor structure for high-power applications. The MOS-controlled thyristor (MCT) is a typical MGT device.

A comprehensive investigation of the reverse-biased safe operating area (RBSOA) characteristics of the MCT has been undertaken. The electrical failure mechanisms of the MCT are discussed, and the relationship between the dynamic avalanche limited RBSOA boundary of the MCT and the lower open-base transistor is identified. An analytical model based on the dynamic current gain concept is proposed to characterize the open-base transistor. For the first time, a RBSOA characteristic equation is developed for the MCT and a unified view of the RBSOA characteristics of the MCT is presented.

The fundamental characteristics of the MCT are compared to those of the insulated gate bipolar transistor (IGBT) at two levels: unit-cell and multi-cell. The investigation of the unit-cell level focuses on the tradeoff between the on-state voltage drop, the turn-off loss, and the RBSOA characteristic. The investigation of the multi-cell level reveals the fundamental difference between the MCT and the IGBT in handling the non-uniform turn-off caused by the internal propagation gate delay of a large-area device. Lack of current saturation capability is identified as the main reason for the severe degradation of the turn-off capability of a large-area multi-cell MCT.

The current saturation and controlled turn-on capabilities can be realized in the MGT devices with dual operation modes. For the first time, a dual operation mode MCT developed with superior current saturation capability is used to demonstrate how the dual operation device

can be beneficial in the switching circuit application. The maximum controllable current density  $(J_{mcc})$  is the most important characteristic of the dual operation mode MGT devices. A first-order analytic model is developed to characterize the  $J_{mcc}$  of the dual operation mode MGT structures compatible with the IGBT fabrication process. A new device structure with improved  $J_{mcc}$  characteristics is proposed and verified by both simulation and experimental results.

The dissertation also carries out a comprehensive investigation of the development of power diodes. A new power diode, called the Trench Bipolar Junction Diode (TBJD), which has superior dynamic characteristics over the conventional P-i-N diode, is proposed. The TBJD controls the anode injection efficiency of the diode by the action of a reverse active transistor structure integrated into its anode junction. The reverse active transistor helps tailor an optimized on-state carrier profile to improve the diode switching characteristics. A novel self-aligned process is developed to fabricate the TBJD. Experimental characteristics without sacrificing the on-state voltage drop and the leakage current characteristics.

To my parents and wife

## Acknowledgments

I would like to thank my advisor, Dr. Alex Q. Huang, for his guidance, support and encouragement during the entire course of my graduate study and research at Virginia Polytechnic Institute and State University. His knowledge, vision and creative thinking have been the source of inspiration throughout. I am also grateful to my other committee members, Dr. Fred C. Lee, Dr. Dusan Borojevic, Dr. Dan Y. Chen and Dr. Robert W. Hendricks for their comments and suggestions.

I would like to thank Dr. Victor A. K. Temple of Harris Semiconductor, for his support of this work. His valuable expertise and advice made this work possible. I am indebted to all the colleagues at Harris Power R&D and the Temples, who made my stay at HPRD during the summer of 1996 and subsequent visits to Latham, NY, pleasant and enjoyable.

I would like to thank Dr. Johnny K. O. Sin of The Hong Kong University of Science and Technology for inviting me to fabricate the TBJD at the Microelectronics Fabrication Facility during the summer of 1999. My sincere thanks go to Dr. Shanqi Zhao, Mr. Yuming Gao and Mr. Yong Gao for their help during my stay in Hong Kong.

I would also like to thank Dr. Paul Chow of the Rensselaer Polytechnic Institute for his help in the fabrication of the DMGT at RPI.

It has been a great pleasure associating with the excellent faculty, staff, and students at the Center for Power Electronics Systems (CPES). The atmosphere that exists at CPES is highly conducive to work, due to the presence of friendly graduate students and cooperative staff. I would like to thank Mr. Bo Zhang, Ms. Julie Dong, Mr. Yuxin Li, Mr. Nick Sun, Dr. Xueling Li, Mr. Kevin Motto, Mr. Aaron Xu, Mr. Yumin Bai, and Mr. Yin Liu for many enlightening discussions and endless exchange of thoughts. Thanks are also due to my fellow students Dr. Wei Chen, Dr. Wilson Zhou, Dr. Kun Xin, Mr. Bryant Zhu, Mr. Henry Zhang, Mr. Fengfeng Tao, Mr. Peng Xu, and Mr. Changrong Liu for their help. I would also like to acknowledge the CPES staff, including Ms. Teresa Shaw, Ms. Evelyn Martin, Ms. Linda Fitzgerald, Ms. Trish Rose, Ms. Ann Craig, Mr. Jeffery Batson, Mr. Steve Chen, and Mr. Joe Price-O'Brien for their assistances.

I thank my parents, Weichi You and Meiqin Hu, for their love and many sacrifices they made to support me to purse higher education.

Special thanks to my wife, Lian, who has always been there with her love, understanding, and support during the past years.

This work was supported in part by Harris Semiconductor, the Office of Navy Research under Power Electronics Building Block (PEBB) program, and the National Science Foundation under Award Number ECS-9733121. This work made use of ERC Shared Facilities supported by the National Science Foundation under Award Number EEC-9731677.

# **Table of Contents**

| List of Figures                                                  | xi  |

|------------------------------------------------------------------|-----|

| List of Tables                                                   | xvi |

| Chapter 1 Introduction                                           | 1   |

| 1.1 Power Semiconductor Devices                                  | 1   |

| 1.2 Scope of the Work                                            | 5   |

| 1.3 Organization of the Dissertation                             | 7   |

| References                                                       | 8   |

| Chapter 2 The Reverse-Biased Safe Operating Area of the MCT      | 10  |

| 2.1 Introduction                                                 | 10  |

| 2.2 Structure and Operation                                      | 11  |

| 2.3 Maximum Controllable Current Density                         | 13  |

| 2.4 Dynamic Avalanche Limitation                                 | 14  |

| 2.4.1 Correlation between the Dynamic and Static Characteristics | 14  |

| 2.4.2 Analytical Model of the Lower Transistor                   | 18  |

| 2.4.3 Dynamic Current Gain Characteristics                       | 23  |

| 2.5 Unified View of The RBSOA of the MCT                         | 29  |

| 2.5.1 Upper-base Modulation Effect                               | 29  |

| 2.5.2 P-MCT vs. N-MCT                                            | 31  |

| 2.6 Conclusion                                                   | 32  |

| References                                                       | 33  |

| Chapter 3 MCT vs. IGBT Comparison                                    |               |

|----------------------------------------------------------------------|---------------|

| 3.1 Introduction                                                     |               |

| 3.2 Three-way Tradeoff of Unit-cell Devices                          |               |

| 3.2.1 Optimized On-state Carrier Profile                             |               |

| 3.2.2 Impact of Buffer Charge                                        |               |

| 3.2.3 Impact of Upper-base Charge                                    |               |

| 3.4 Non-uniform Turn-off in Multi-cell Devices                       |               |

| 3.4.1 Turn-off Failure Due to Gate Delay                             |               |

| 3.4.2 Modeling Approach                                              | 50            |

| 3.4.3 Results and Discussion                                         |               |

| 3.4 Conclusion                                                       |               |

| References                                                           |               |

| Chapter 4 Demonstration of the Dual Operation Mode MCT               |               |

| 4.1 Introduction                                                     |               |

| 4.2 Device Design and Operation                                      |               |

| 4.3 Experimental Results                                             |               |

| 4.3.1 Turn-on Characteristics                                        |               |

| 4.3.2 Turn-off Characteristics                                       |               |

| 4.4 Conclusion                                                       |               |

| References                                                           |               |

| Chapter 5 Dual Operation Mode MGT Structures Compatible with the IGH | BT Process 79 |

| 5.1 Introduction                                                     |               |

| 5.2 Device Structures and Operation                                  |               |

| 5.3 Simulation Results                                               |               |

| 5.4 The J <sub>mcc</sub> Model                                       |               |

| 5.5 Experimental Results                                             |               |

| 5.6 Conclusion                                                       |               |

| References                                                           |               |

| Chapter 6 Background and Analysis of the TBJD       |  |

|-----------------------------------------------------|--|

| 6.1 Introduction                                    |  |

| 6.2 Review of Power Diode Development               |  |

| 6.2.1 Lifetime Controlling Techniques               |  |

| 6.2.2 Cathode Engineering Techniques                |  |

| 6.2.3 Anode Engineering Techniques                  |  |

| 6.3 TBJD Structure and Operation                    |  |

| 6.3.1 Device Structure                              |  |

| 6.3.2 Numerical Simulation                          |  |

| 6.4 Conclusion                                      |  |

| References                                          |  |

| Chapter 7 Design and Fabrication of the TBJD        |  |

| 7.1 Device Design                                   |  |

| 7.2 Process Flow                                    |  |

| 7.3 Spreading Resistance Profile                    |  |

| References                                          |  |

| Chapter 8 Experimental Characterization of the TBJD |  |

| 8.1 Introduction                                    |  |

| 8.2 Experimental Results and Discussion             |  |

| 8.2.1 Reverse Active Transistor                     |  |

| 8.2.2 Forward Characteristics                       |  |

| 8.2.3 Reverse Blocking Characteristics              |  |

| 8.2.4 Reverse Recovery Characteristics              |  |

| 8.3 Conclusion                                      |  |

| References                                          |  |

| Chapter 9 Conclusions and Future Work               |  |

| 9.1 Investigation of the MCT                        |  |

| 9.1.1 Unit-cell Level                               |  |

| Vita                                        |     |

|---------------------------------------------|-----|

| Appendix: Process Flow of the TBJD          | 156 |

| 9.3 Development of the TBJD                 |     |

| 9.2 Exploration of Dual Operation Mode MGTs | 152 |

| 9.1.2 Multi-cell Level                      | 152 |

# List of Figures

| Fig. 1.1 Cross-section view of the IGBT and its equivalent circuit                                  |

|-----------------------------------------------------------------------------------------------------|

| Fig. 1.2 Cross-section view of the MCT and its equivalent circuit                                   |

| Fig. 2.1 Cross-section of the unit-cell of a N-type MCT11                                           |

| Fig. 2.2 Simulated voltage and current waveforms of the P-MCT in gating off two different           |

| inductive loads at a clamped voltage of 400 V 15                                                    |

| Fig. 2.3 Experimental current and voltage waveforms of a P-MCT during a snubberless inductive       |

| turn-off                                                                                            |

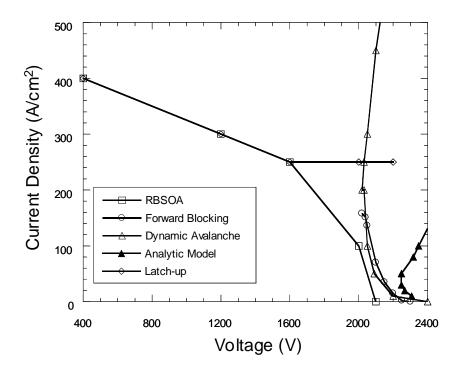

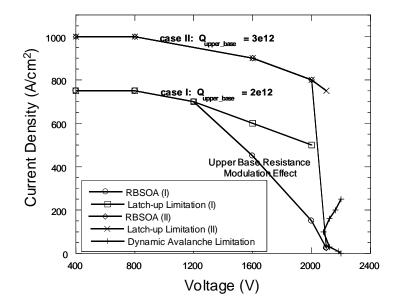

| Fig. 2.4 Limiting factors of the RBSOA of the P-MCT                                                 |

| Fig. 2.5 Electric field distribution in the drift region of the open-base PNP transistor of a N-    |

| MCT                                                                                                 |

| Fig. 2.6 Calculated dynamic current gain value of the lower transistors of MCTs as a function of    |

| current density                                                                                     |

| Fig. 2.7 Limiting factors of the RBSOA of the N-MCT                                                 |

| Fig. 2.8 Simulated forward blocking capability of the lower transistors of the MCTs 26              |

| Fig. 2.9 Calculated dynamic current gain value of the lower NPN transistor of a PT P-MCT with       |

| a varied lower-base buffer charge                                                                   |

| Fig 2.10 Dynamic avalanche limited RBSOAs of the PT P-MCT with a varied lower-base buffer           |

| charge                                                                                              |

| Fig. 2.11 Limiting factors of the RBSOA of a N-MCT with a varied upper-base charge 30               |

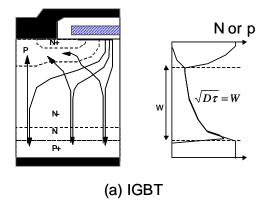

| Fig. 3.1 Basic unit-cell structures and their on-state carrier distribution profiles: (a) N-MCT and |

| (b) N-IGBT                                                                                          |

|                                                                                                     |

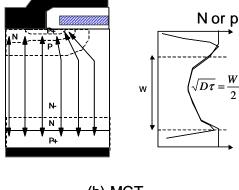

| Fig. 3.2 Simulated on-state carrier (hole) profiles of the 1200 V MCT and IGBT37                              |

|---------------------------------------------------------------------------------------------------------------|

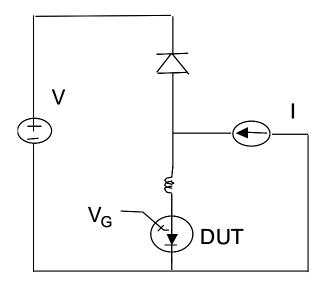

| Fig. 3.3 Schematic of the simulation circuit                                                                  |

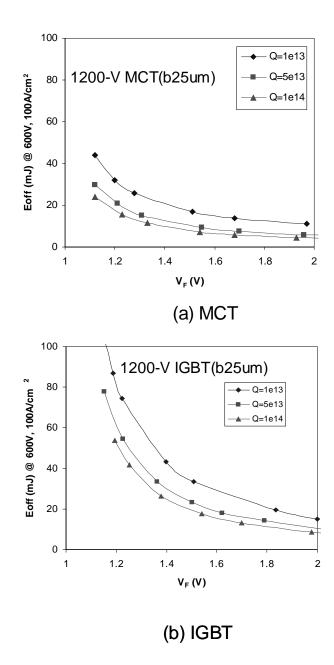

| Fig. 3.4 Tradeoffs between the $V_F$ and the turn-off loss per cycle ( $E_{off}$ ) with varied buffer charge: |

| (a) MCT and (b) IGBT                                                                                          |

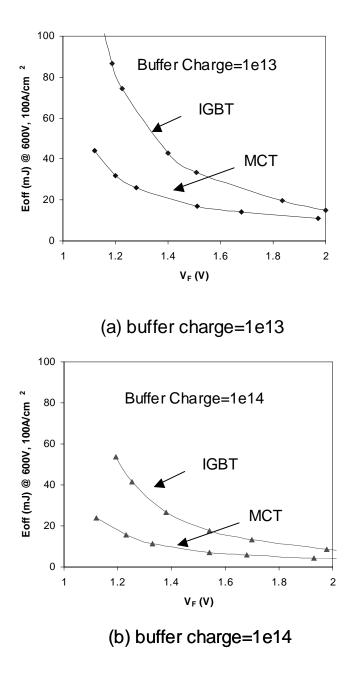

| Fig. 3.5 $V_F$ vs. $E_{off}$ tradeoff comparison between the MCT and the IGBT with two different buffer       |

| charges (Q): (a) Q=1e13 and (b) Q=1e14                                                                        |

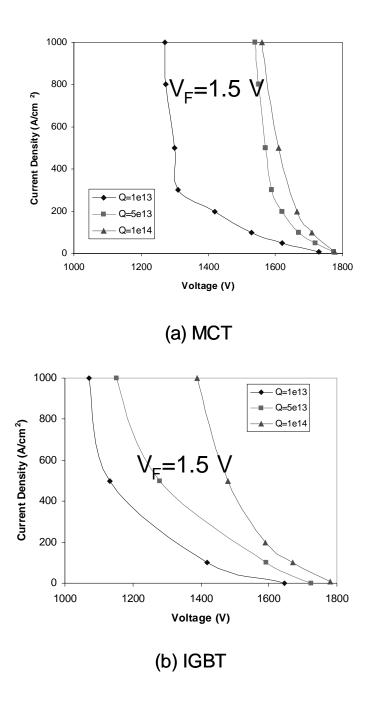

| Fig. 3.6 Dynamic avalanche limited RBSOA characteristics of the devices under the same $V_F$                  |

| condition: (a) MCT and (b) IGBT                                                                               |

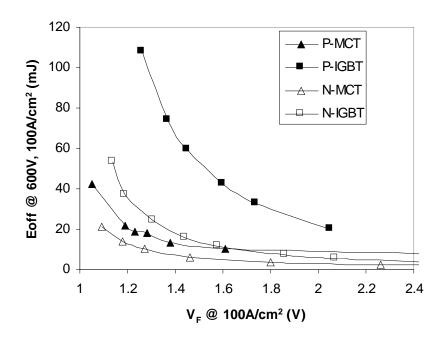

| Fig. 3.7 V <sub>F</sub> vs. E <sub>off</sub> tradeoffs for the 1200 V devices                                 |

| Fig. 3.8 $V_F$ vs. $E_{off}$ tradeoff of a P-MCT with varied upper-base charge ( $Q_{UB}$ )                   |

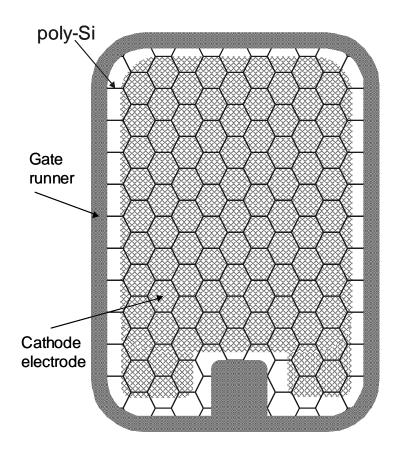

| Fig. 3.9 Typical layout of a multi-cell MCT                                                                   |

| Fig. 3.10 Simplified modeling approach to study the effect of the gate delay on the onset of                  |

| current filament in a multi-cell device                                                                       |

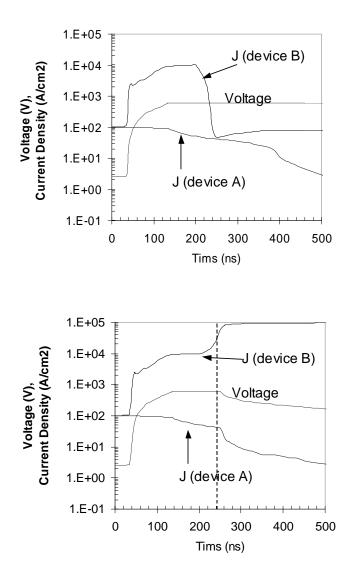

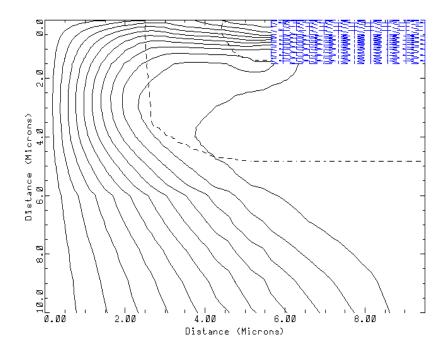

| Fig. 3.11 The difference between what occurs in device B of a multi-cell MCT and in that of an                |

| IGBT when the anode voltage rises                                                                             |

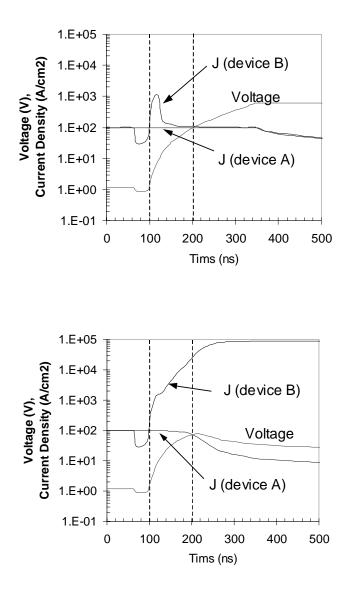

| Fig. 3.12 Simulated current and voltage waveforms of devices A and B during the turn-off of a                 |

| multi-cell MCT: (a) gate delay $t_d$ =40 ns and (b) $t_d$ =50 ns                                              |

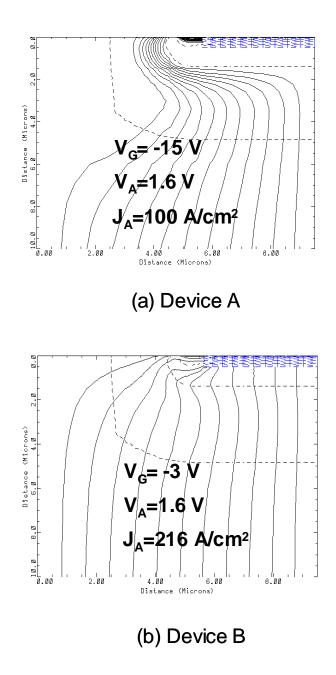

| Fig. 3.13 Current flow lines of device A and device B at t=100 ns during the turn-off of a multi-             |

| cell MCT with a gate delay t <sub>d</sub> =40 ns                                                              |

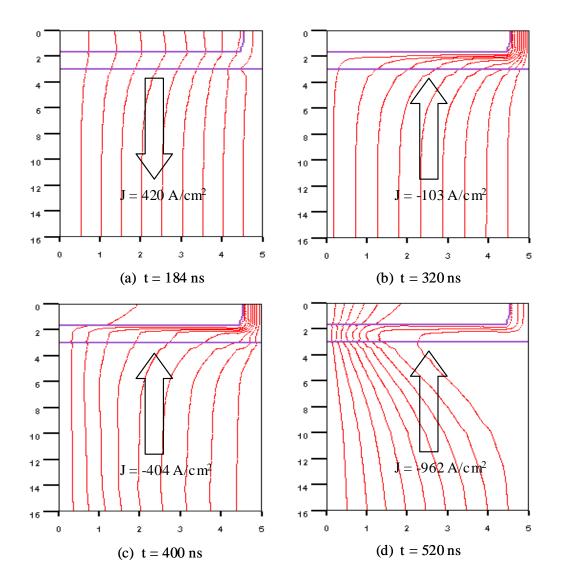

| Fig. 3.14 Current flow lines of device B at four different time steps during the turn-off of a multi-         |

| cell MCT with a gate delay t <sub>d</sub> =50 ns                                                              |

| Fig. 3.15 Simulated current and voltage waveforms of devices A and B during the turn-off of a                 |

| multi-cell IGBT: (a) gate delay $t_d$ =200 ns and (b) $t_d$ =300 ns60                                         |

| Fig. 3.16 Current flow lines of device B at t=240 ns during the turn-off of a multi-cell IGBT with            |

| a gate delay t <sub>d</sub> =300 ns                                                                           |

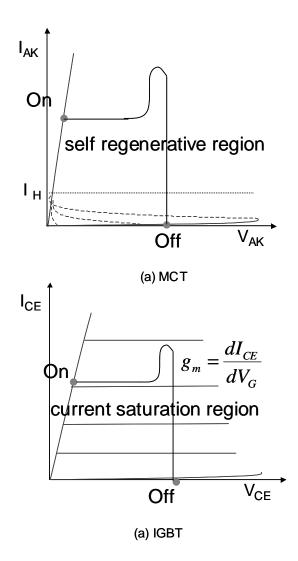

| Fig. 4.1 Static output characteristics and the dynamic switching locus during an inductive turn-              |

| on: (a) MCT and (b) IGBT 65                                                                                   |

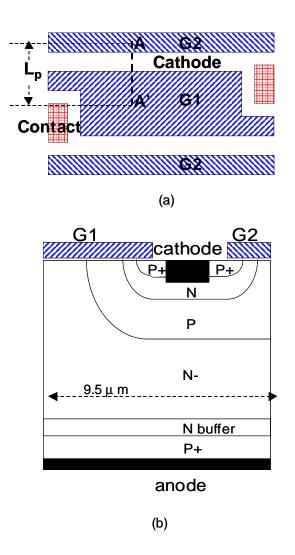

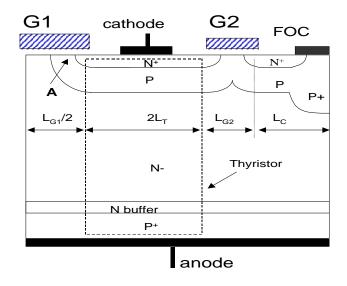

| Fig. 4.2 Schematic diagram of the unit cell of the dual operation mode MCT: (a) top view and    | l (b) |

|-------------------------------------------------------------------------------------------------|-------|

| cross section along line A-A'                                                                   | 68    |

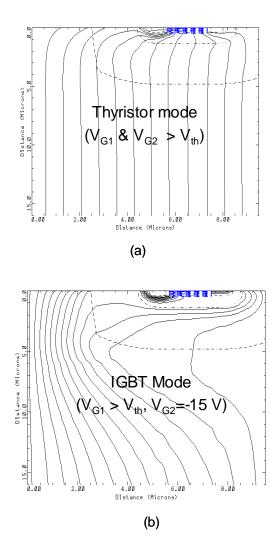

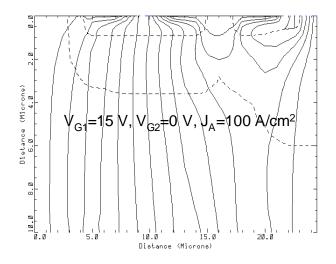

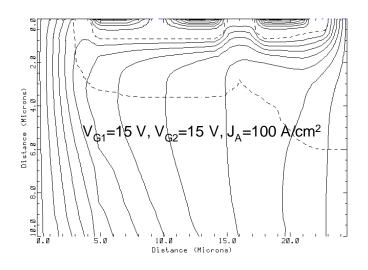

| Fig. 4.3 Current flow lines of the dual operation mode MCT in the forward-conducting state: (   | (a)   |

| thyristor mode operation, and (b) IGBT mode operation.                                          | 69    |

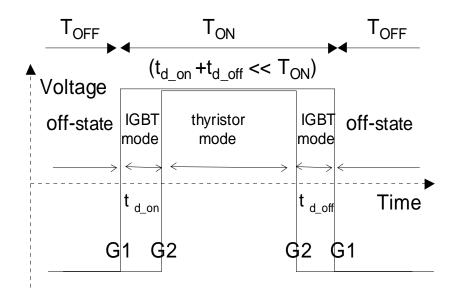

| Fig. 4.4 Control scheme of the dual operation mode MCT                                          | 70    |

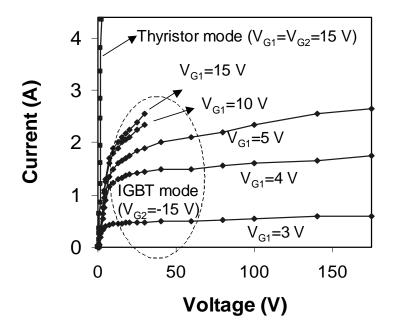

| Fig. 4.5 Experimental output I-V characteristics of the dual operation mode MCT                 | 71    |

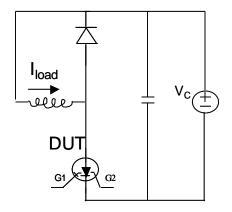

| Fig. 4.6 Schematic of the circuit used to test the dual operation mode MCT.                     | 72    |

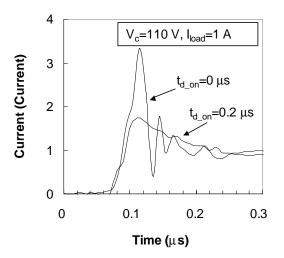

| Fig. 4.7 Turn-on current waveforms of the dual operation model MCT when the freewheeling        |       |

| diode is a fast recovery diode                                                                  | 73    |

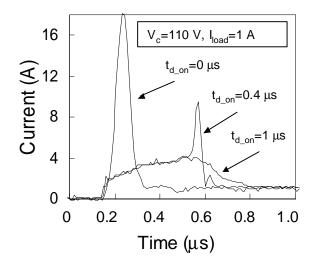

| Fig. 4.8 Turn-on current waveforms of the dual operation model MCT when the freewheeling        |       |

| diode is a slow body diode                                                                      | 74    |

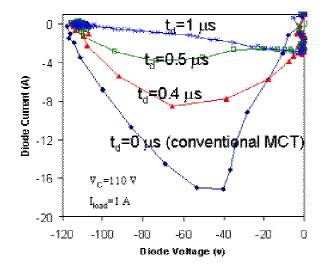

| Fig. 4.9 V-I locus of the freewheeling diode during the turn-on transient of the dual operation |       |

| mode MCT                                                                                        | 74    |

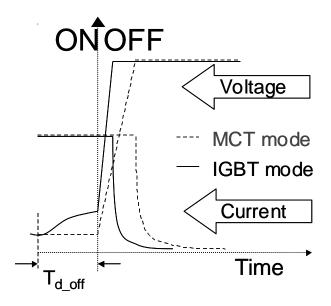

| Fig. 4.10 Schematic view of the voltage and current waveforms of the dual operation mode M      | [CT   |

| during the turn-off transient                                                                   | 76    |

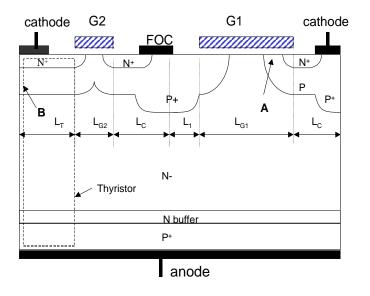

| Fig. 5.1 Cross-section view of the DMGT structure A.                                            | 81    |

| Fig. 5.2 Current flow lines of the DMGT structure A in the thyristor mode                       | 82    |

| Fig. 5.3 Current flow lines of the DMGT structure A in the IGBT mode                            | 83    |

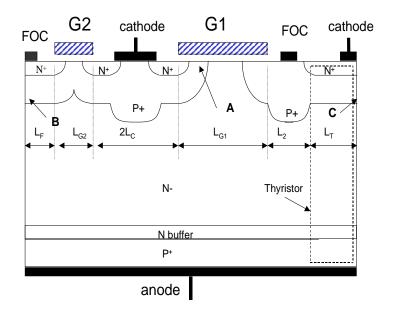

| Fig. 5.4 Cross-section view of the DMGT structure B.                                            | 83    |

| Fig. 5.5 Cross-section view of the proposed DMGT structure C                                    | 84    |

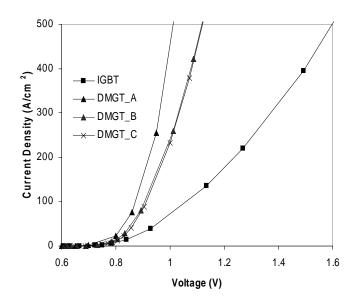

| Fig. 5.6 Simulated on-state characteristics of the DMGTs in the thyristor mode                  | 87    |

| Fig. 5.7 Simulated output characteristics of the DMGTs in the IGBT mode                         | 88    |

| Fig. 5.8 Hole current vectors in the IGBT mode of the DMGT structure A                          | 89    |

| Fig. 5.9 Current flow lines of the DMGT structure A when the device starts to latch in the IGE  | 3T    |

| mode                                                                                            | 91    |

| Fig. 5.10 Current flow lines of the DMGT structure B when the device starts to latch in the IG  | βBT   |

| mode                                                                                            | 93    |

| Fig. | 5.11 Current flow lines of the DMGT structure C when the device starts to latch in the IGBT                |

|------|------------------------------------------------------------------------------------------------------------|

|      | mode                                                                                                       |

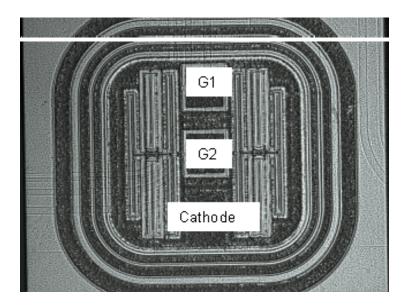

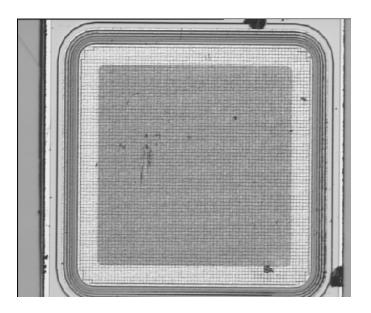

| Fig. | 5.12 Photomicrograph of the fabricated DMGT structure C                                                    |

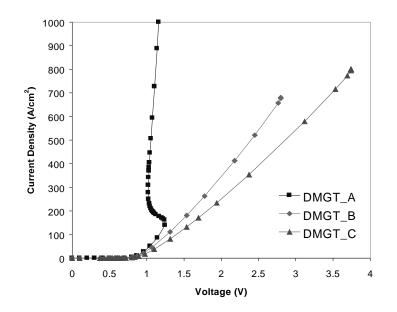

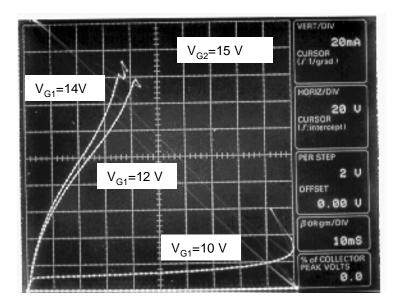

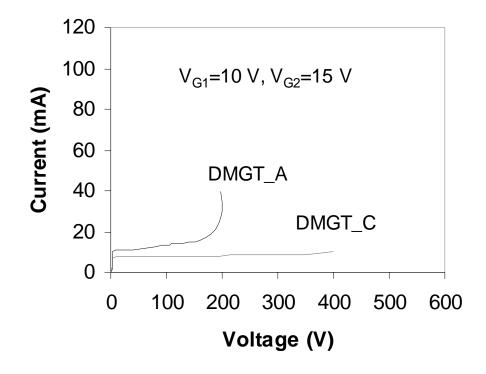

| Fig. | 5.13 Experimental output characteristics of the DMGT structure A in the IGBT mode 98                       |

| Fig. | 5.14 Experimental output characteristics of the DMGT structures A and C in the IGBT mode                   |

|      | with lower gate voltage                                                                                    |

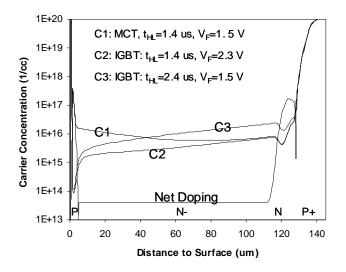

| Fig. | 6.1 Cross-section view of the P-i-N diode                                                                  |

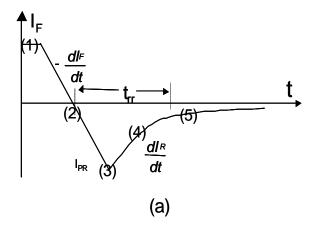

| Fig. | 6.2 Reverse recovery of the P-i-N diode: (a) current waveform, and (b) instant minority                    |

|      | carrier profile during the reverse recovery phase                                                          |

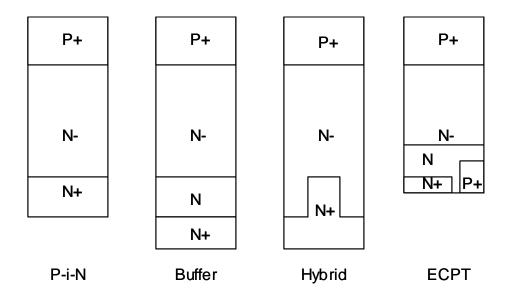

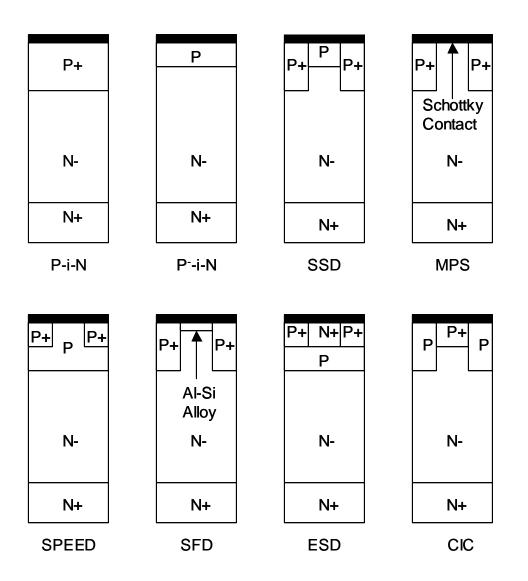

| Fig. | 6.3 Cross-section views of the diode structures using cathode engineering techniques 107                   |

| Fig. | 6.4 Cross-section views of the diode structures using anode engineering techniques 109                     |

| Fig. | 6.5 TBJD: (a) cross-section view, and (b) equivalent circuit                                               |

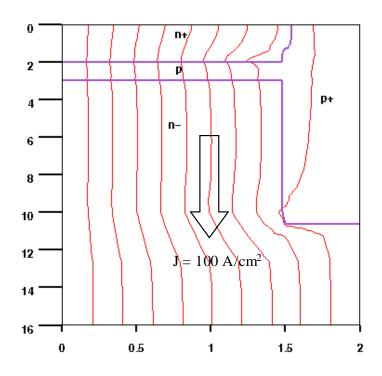

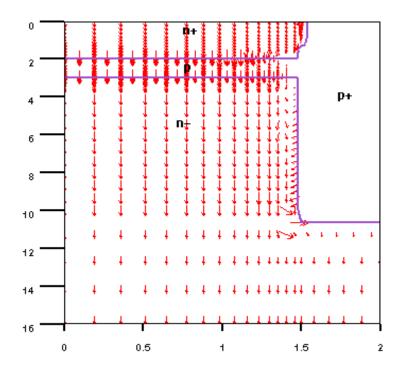

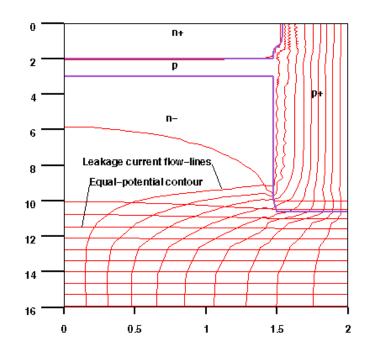

| Fig. | 6.6 Simulated on-state current flow lines of a TBJD114                                                     |

| Fig. | 6.7 On-state electron current vectors in the TBJD 115                                                      |

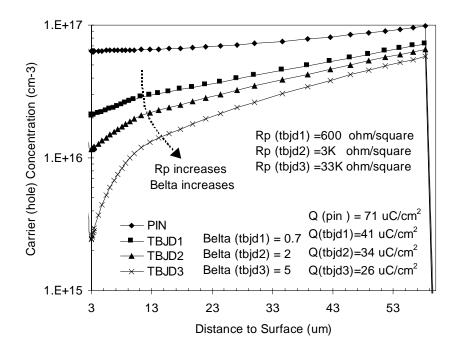

| Fig. | 6.8 On-state carrier distribution profiles in the N- region of a TBJD with varied current gain             |

|      | $\beta$ r while carrying a forward current of 100A/cm <sup>2</sup>                                         |

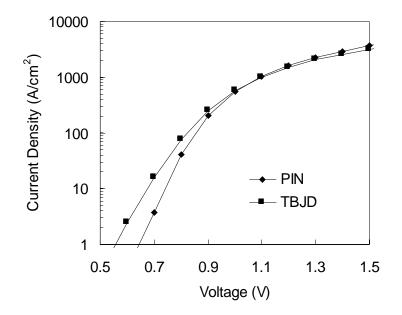

| Fig. | 6.9 Forward I-V curves for the TBJD ( $\beta_r=5$ ) and the comparative P-i-N diode                        |

| Fig. | 6.10 Equal-potential contour and the leakage current flow lines of the TBJD under an 800-V                 |

|      | reverse voltage                                                                                            |

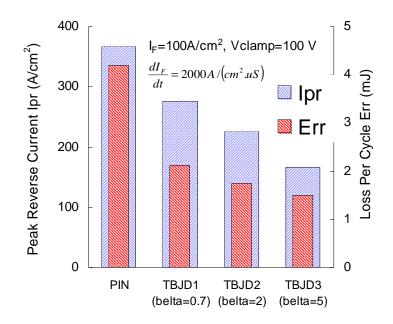

| Fig. | 6.11 Peak reverse current $(I_{pr})$ and the loss per cycle $(E_{off})$ during the reverse recovery of the |

|      | diodes with varied $\beta_r$                                                                               |

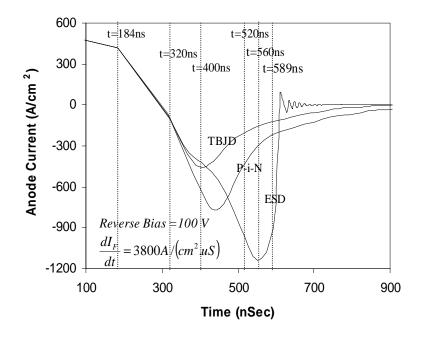

| Fig. | 6.12 Reverse recovery current waveforms of a TBJD and an ESD 122                                           |

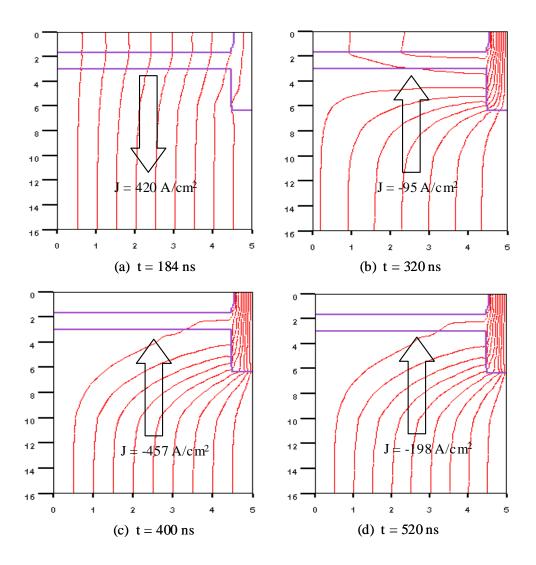

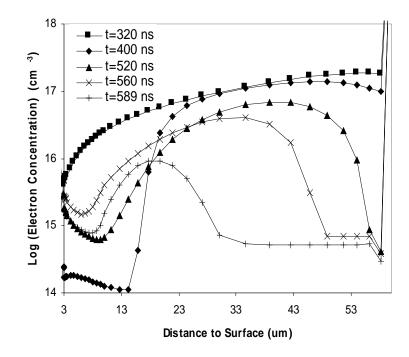

| Fig. | 6.13 Current flow lines of the TBJD during the reverse recovery transient period                           |

| Fig. | 6.14 Current flow lines of the ESD during the reverse recovery transient period 124                        |

| Fig. | 6.15 Instant electron profile in the N- region of the ESD during the reverse recovery transient            |

|      | period                                                                                                     |

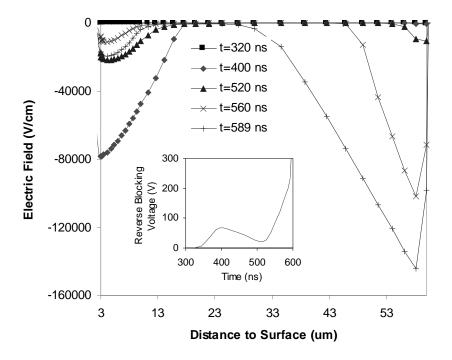

| Fig. | 6.16 Instant electric field distribution in the N- region of the ESD during the reverse  |      |

|------|------------------------------------------------------------------------------------------|------|

|      | recovery period. The figure insert shows the waveform of the reverse blocking voltage.   | 127  |

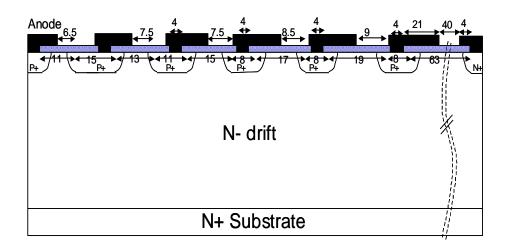

| Fig. | 7.1 Top view of a TBJD die                                                               | 132  |

| Fig. | 7.2 Cross-section view of the TBJD edge termination region.                              | 132  |

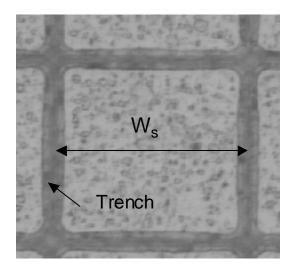

| Fig. | 7.3 Photomicrography of a unit-cell of the TBJD.                                         | 133  |

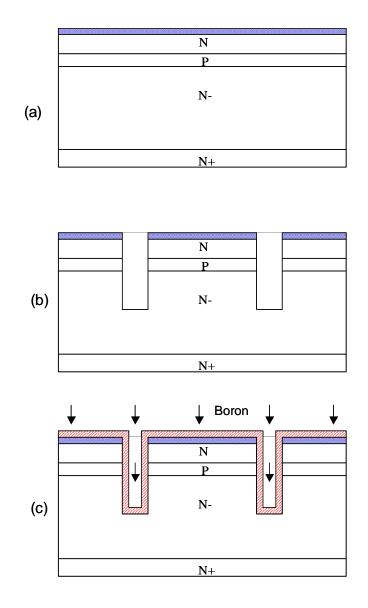

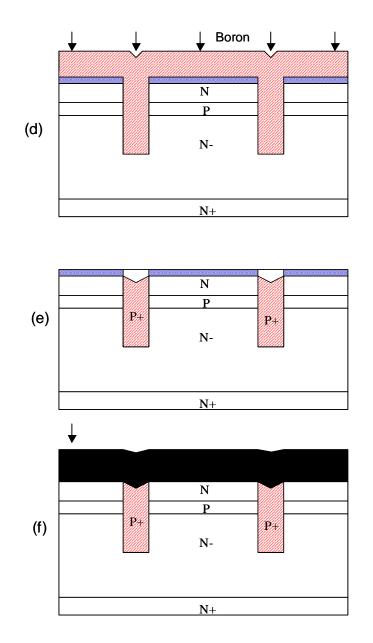

| Fig. | 7.4 Major steps of the TBJD fabrication process                                          | 135  |

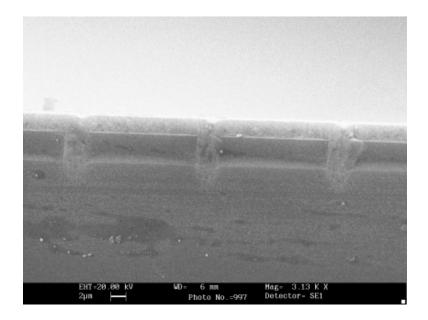

| Fig. | 7.5 A SEM cross-section view of the TBJD after the poly-Si refilling                     | 136  |

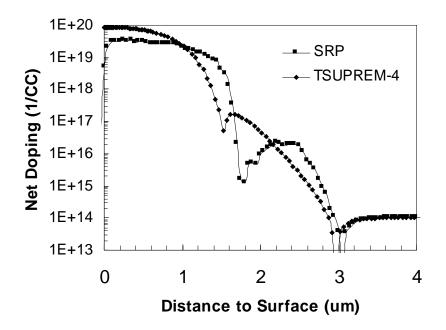

| Fig. | 7.6 Simulated and experimental SRP doping profiles of a TBJD                             | 138  |

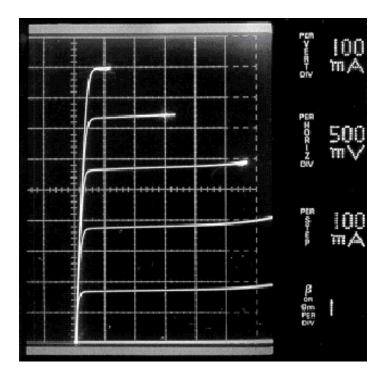

| Fig. | 8.1 Experimental I-V characteristics of the RAT                                          | 141  |

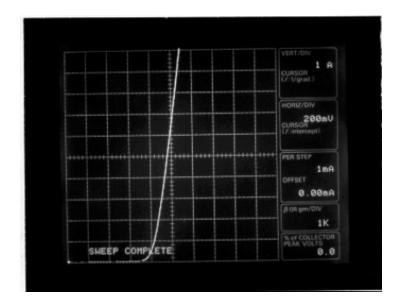

| Fig. | 8.2 Measured forward I-V characteristics of a TBJD.                                      | 142  |

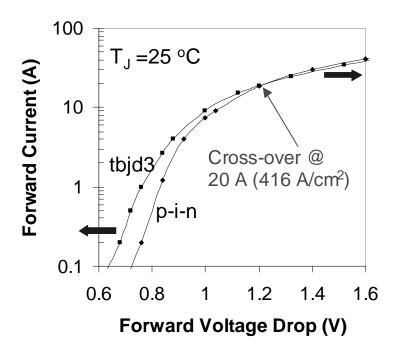

| Fig. | 8.3 Measured forward I-V characteristics of the TBJD and P-i-N diode                     | 143  |

| Fig. | 8.4 Measured reverse blocking characteristics at room temperature: (a) TBJD , and (b) P- | -i-N |

|      | diode                                                                                    | 144  |

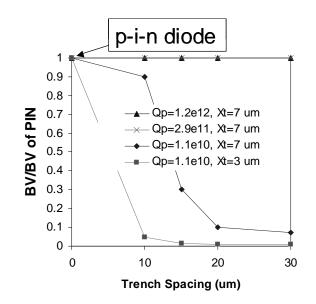

| Fig. | 8.5 Reverse blocking capability of the TBJD as a function of the trench spacing, trench  |      |

|      | depth and P base charge                                                                  | 146  |

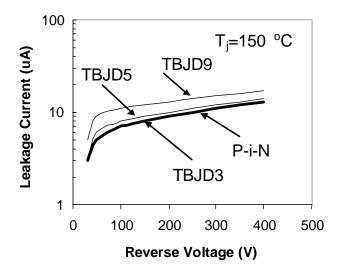

| Fig. | 8.6 Leakage current measured at elevated temperature.                                    | 146  |

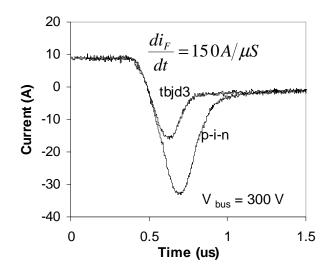

| Fig. | 8.7 Measured reverse recovery current waveforms of the TBJD and the P-i-N diode          | 148  |

|      |                                                                                          |      |

# List of Tables

| Table 4.1 Measured turn-on performance of the dual operation mode MCT                  | .75 |

|----------------------------------------------------------------------------------------|-----|

| Table 4.2 Measured turn-off performance of the dual operation mode MCT                 | .76 |

| Table 5.1 Doping profile and geometrical dimensions used in the simulation of the DMGT | .86 |

| Table 8.1 Measured reverse recovery performance of the diodes                          | 148 |

## **Chapter 1 Introduction**

#### **1.1 Power Semiconductor Devices**

Power semiconductor devices play a crucial role in the regulation and distribution of power and energy in the world. By some estimations, more than sixty percent of all the power utilized in the United States flows through at least one power device, and more often through multiple devices [1]. The performances of power switches and rectifiers have a significant impact on the efficient use of electricity. In the power electronics community, it is well recognized that improvement in system performance in terms of efficiency, size, and weight are driven by enhancements made in semiconductor device characteristics.

Power switches are essential components of all power electronics systems for the regulation of loads. The first power semiconductor switches were thyristors and bipolar transistors developed in the 1950's. Thyristors were used in higher power systems, because their ratings were scaled at a faster pace than bipolar transistors. Gate Turn-off Thyristors (GTO) are now available with ratings of 6000 V and 4000 A. These devices are manufactured from single four-to-five-inch diameter wafers using a mature deep diffusion process technology.

Ever since their introduction in the 1950's, bipolar transistors were favored for low and medium power applications because of their faster switching capability. The ratings for the devices grew steadily until the late 1970's. Since the bipolar transistor is fundamentally a current-controlled device with the magnitude of the collector current determined by the basedriving current, one of the most critical design goals has been to improve the current gain in order to reduce the complexity, size, and weight of the base-driving circuit. Unfortunately, a severe tradeoff exists between the collector-emitter breakdown voltage and the current gain in the conventional bipolar transistor structure due to their conflicting requirements on the transistor base width. Although continuous improvement of the bipolar transistor structure has greatly alleviated this tradeoff, the fall-off in current gain at typical operating current densities due to high-level injection effects leads to a gain of less than ten [2, 3]. The current gain can be improved by using the Darlington configuration at the disadvantage of a considerable increase in the on-state voltage drop [4]. For these reasons, the bipolar transistor has been displaced by the power MOSFET for low power applications in the 1980's, and for medium power applications by Insulated Gate Bipolar Transistors (IGBT) in the 1990's.

The silicon power MOSFET has become the dominant device technology for low power applications. First, the power MOSFET has very high input impedance in the steady state due to its metal-oxide-semiconductor (MOS) gate structure, and is classified as a voltage-controlled device. Second, in comparison with bipolar transistors, the MOSFET has a very fast inherent switching speed due to the absence of minority carrier injection. The switching time for the MOSFET is dictated by the ability to charge and discharge the input capacitance. Third, the MOSFET has superior ruggedness and a forward-biased safe operating area (FBSOA) when compared with bipolar transistors, which allows the elimination of snubber circuits for protection of the switch during operation.

Unfortunately, the specific on-resistance of the drift region of the conventional power MOSFET increases very rapidly with the increasing breakdown voltage, because of the need to reduce its doping concentration and increase its thickness. Thus, the conventional power MOSFET is not satisfactory for applications that require a breakdown voltage above 300 V due to their high on-state power dissipations.

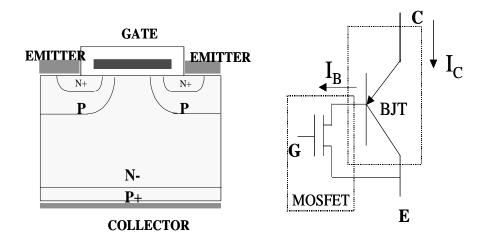

Recently, a new technology called CoolMOS for higher voltage power MOSFETs has been introduced [5,6]. Based on the new device concept of charge compensation, the specific onresistance of the 600-V MOSFET has been reduced by a factor of five. However, even with the new technology, the specific on-resistance of the MOSFET is not expected to be satisfactory for applications that require a breakdown voltage above 1200 V. The high on-resistance problem of a MOSFET at high voltages was resolved in the 1980's by the introduction of the Insulated Gate Bipolar Transistor (IGBT), in which bipolar current conduction is controlled by using a MOS gate structure [7-9]. The cross-section of the planar MOS technology based IGBT and its equivalent circuit are shown in Fig. 1.1. Due to the injection of a high concentration of holes from the P+ substrate into the N- drift region, the IGBT has a much lower forward drop as compared to a power MOSFET structure. Since the input signal for the IGBT shares the high input impedance advantage of the power MOSFET, the IGBT is also classified as a voltage-controlled device. However, unlike the MOSFET, the switching speed of the IGBT is limited by the time taken for removal of the stored charge in the drift region due to injection of holes during the on-state current conduction. The turn-off time for the IGBT is dictated by the minority carrier lifetime, and it is found that the on-state voltage drop of the IGBT increases after lifetime reduction, as observed for all bipolar power devices.

Fig. 1.1 Cross-section view of the IGBT and its equivalent circuit.

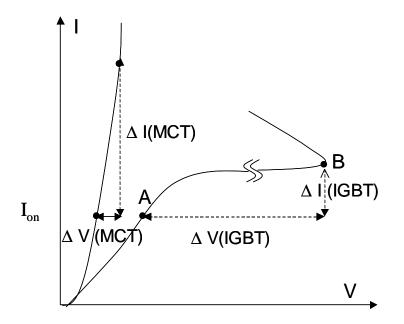

In spite of the on-going refinement of the IGBT structure to improve the trade-off between the on-state voltage drop and the turn-off characteristics, its on-state power dissipation still becomes large when designed for operation at high voltages. For this reason, considerable research has been performed on MOS-Gated Thyristors (MGT), which refers to the class of devices combining a MOS gate control with the current-carrying capability of a thyristor structure, as alternative devices for high power applications.

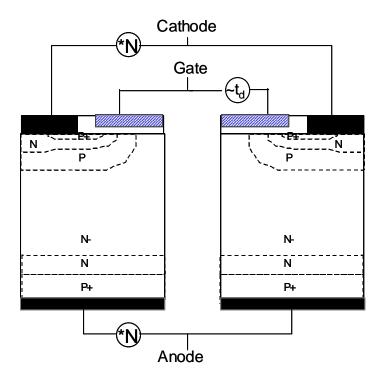

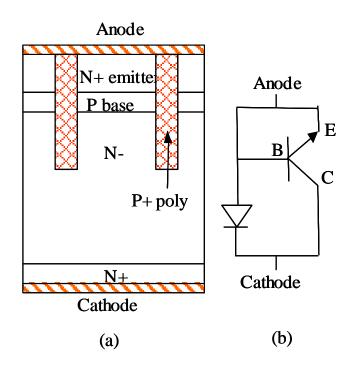

The first reported MGT structure with current turn-off capability was the MOS-Controlled Thyristor (MCT) [10-12]. In this device, whose cross-section and equivalent circuit is shown in Fig. 1.2, the regenerative action of the thyristor structure is interrupted by shortcircuiting the N+ emitter to the P base region by using a P-MOSFET integrated within the P-base region. Although there have been considerable research efforts put into this area and many new MGT structures have been proposed during the past decade, so far the only commercially available MGT device is still the MCT [13-15].

Fig. 1.2 Cross-section view of the MCT and its equivalent circuit.

The ability to control current flowing in a MGT device has been found to be a more challenging problem. The internal regenerative action of the thyristor structure can easily lead to the formation of current filaments that can destroy the device during turn-off. The internal regenerative action of the thyristor structure also accounts for the uncontrollable turn-on behaviors of the MGT, whose turn-on speed is usually too fast and results in a snappy reverse recovery in the associated diodes.

Since the introduction of modern power switches, such as the IGBT and MGT, diodes in many applications are subjected to higher voltage and current levels, and are required to switch at higher speeds and frequencies. Under these conditions, power diodes with low forward voltage drop, low leakage current, low peak reverse recovery current and low reverse recovery charge are needed in order to decrease the overall power loss in the power electronics circuits.

In high-voltage applications, the P-i-N diodes still dominate due to their low forward voltage drop and reverse leakage current. However, the conventional P-i-N diode suffers from poor dynamic characteristics due to the large amount of charge stored in the lightly doped i-region during forward conduction. On the other hand, the Schottky diode has been limited to low-voltage applications because of its high leakage current and soft breakdown. A high-voltage power diode with improved static and dynamic characteristics to match the performance of the modern power switches is essential in high-voltage power electronics applications.

#### **1.2 Scope of the Work**

The research work reported in the dissertation focuses on the following aspects.

- 1) Investigation of the fundamental device characteristics that distinguish the MCT and the IGBT.

- 2) Demonstration of new MGT devices with improved performances.

- 3) Development of a new power diode with superior dynamic characteristics.

The first aspect of this work is carried out by conducting an extensive comparative study between the MCT and the IGBT through numerical simulation. This comparison is especially important because the IGBT is currently the dominant power switch in medium power applications, and the frontier of its application development is being pushed into the high power range.

The second aspect of this work is focused on the dual operation mode MGT. The dual operation mode MGT device possesses current saturation capability, a feature not available in the conventional MCT. The current saturation capability is one of the most desirable features for a power switch. It provides short-circuit protection for the switch, and is used to achieve controlled turn-on capability. Both simulation and experimental results are provided in the investigation of the dual operation mode MGT.

The third portion of this research work covers the development of a new power diode with superior characteristics compared to the conventional P-i-N diode. The diode research work includes: review of the historical development of the power diodes; analysis of a new diode concept; design and fabrication of the new diode; and experimental characterization of the new diode.

The contributions of the research work are listed below.

- Identified the static current-voltage locus of the lower open-base transistor as the dynamic avalanche limited reverse-biased safe operating area (RBSOA) boundary of the MCT. An analytical model was proposed to characterize the dynamic avalanche characteristics of the open-base transistor. For the first time, a RBSOA characteristic equation that applies to all MGT devices has been developed.

- Presented a unified view and design guidelines for the RBSOA characteristics and the trade-off between the on-state voltage drop and the turn-off loss of the MCT.

- 3) Identified the intrinsic problem of a large-area multi-cell MCT. It was found that the multi-cell MCT is vulnerable to the non-uniform turn-off caused by the internal gate delay because the MCT structure lacks the current saturation capability.

- 4) Experimentally demonstrated the application of a dual operation mode MCT with superior current saturation capability in a hard-switching circuit.

- 5) Presented a new dual operation mode MGT structure compatible with the fabrication process of an IGBT. The analytic models developed to describe its maximum controllable current density are verified by simulation and experiment.

- 6) Proposed a new power diode, called the Trench Bipolar Junction Diode (TBJD), and fabricated the TBJD with a novel self-aligned trench process. It has been shown, by both simulation analysis and experiment characterization, that the TBJD has superior static and dynamic characteristics than the conventional P-i-N diode.

#### **1.3 Organization of the Dissertation**

The dissertation is divided into nine chapters, including the introduction and conclusion chapters. Chapters 2 through 5 include the investigation of the MOS Gated Thyristors, and Chapters 6 through Chapter 8 cover the diode work. Within each chapter, except Chapters 1, 7 and 9, there is an introduction section, which provides the background information, and a conclusion section, in which the work and results are summarized. References are listed after each chapter.

Chapter 2 performs a comprehensive investigation of the RBSOA characteristics of the MCT. This chapter discusses the electrical failure mechanisms of the MCT and identifies the relationship between the dynamic avalanche limited RBSOA boundary of the MCT and the lower open-base transistor. An analytical model based on a dynamic current gain concept is proposed to characterize the open-base transistor. A RBSOA characteristic equation is developed and a unified view on the RBSOA characteristics of the MCT is presented.

In Chapter 3, an apple-to-apple MCT vs. IGBT comparison study is undertaken at two levels: unit-cell and multi-cell. The comparison at the unit-cell level focuses on the trade-off among the on-state voltage drop, turn-off loss, and the RBSOA characteristics. The multi-cell level comparison reveals the fundamental difference between the MCT and the IGBT in handing the non-uniform turn-off due to the internal propagation gate delay of a large-area unit-cell device.

Chapter 4 investigates the switching performance of a dual operation mode MCT with superior current saturation capability in a hard-switching circuit, and demonstrates how a dual operation mode MCT can be beneficial in specific applications.

In Chapter 5, the dual operation mode MOS Gated Thyristor (DMGT) devices that are compatible with the IGBT process are analyzed. A first-order analytic model is developed to characterize the maximum controllable current density ( $J_{mcc}$ ) in the IGBT mode operation. A new device structure is proposed and compared with two previously reported DMGT structures. Both simulation and experiment results are provided to back up the analytic model.

Chapter 6 first conducts an extensive literature review of the power diode development. The TBJD concept and operation principles are analyzed in detail with the aid of numerical simulation. The process development and fabrication of 600 V, 10 A TBJDs are described in Chapter 7, while the fabricated and packaged TBJDs are characterized in Chapter 8.

Chapter 9 summaries the findings and conclusions of the research work, and proposes possible future work.

Appendix gives the details of the TBJD fabrication process.

#### References

- B. J. Baliga, "Trends in power Semiconductor device," *IEEE Trans. Electron Devices*, vol. 43, no. 10, pp. 1717-1731, 1996.

- H. Kondo and Y. Yukimoto, "A new bipolar transistor GAT," *IEEE Trans. Electron Devices*, vol. ED-27, no. 2, pp. 373-379, 1980.

- [3] Q. F. Chen, J. K. O. Sin, and Q. X. Chen, "A new trench base-shielded bipolar transistor," *Proc. ISPSD*, pp. 169-172, 1998.

- [4] C. F. Wheatley and W. G. Einthoven, "On the proportioning of chip area for multistage darlington transistor," *IEEE Trans. Electron Devices*, ED-23, pp. 870-878, 1976.

- [5] G. Deboy, M. Marz, J. P. Stengl, H. Strack, J. Tihanyi and H. Weber, "A new generation of high-voltage MOSFETs breaks the limits of silicon," *IEEE Int. Electron Devices Meeting Digest*, pp. 683-686, 1998.

- [6] L. Lorenz, M. Marz and G. Deboy, "COOLMOS- An important milestone towards a new power MOSFET generation," *Proc. of Power Conversion*, pp.151-160, 1998.

- [7] B. J. Baliga, M. S. Adler, P.V. Gray, R. Love, and N. Zommer, "The insulated gate rectifier (IGR): a new power switching device," *IEEE Int. Electron Devices Meeting Digest*, Abstract 10.6, pp. 264-267, 1982.

- [8] J. P. Russell, A. M. Goodman, L. A. Goodman, and J. M. Nielson, "The COMFET: a new high conductance MOS gated device," *IEEE Electron Device Letters*, Vol. 4, pp.63-65, 1983.

- [9] B. J. Baliga, M. S. Adler, P.V. Gray, R. Love, and N. Zommer, "The Insulated Gate Transistor," *IEEE Trans. Electron Devices*, Vol. 31, pp. 821-828, 1984.

- [10] V. A. K. Temple, "MOS Controlled Thyristor (MCT's)," IEEE Int. Electron Devices Meeting Digest, Abstract 10.7, pp. 282-285,1984.

- [11] M. Stoisiek, and H. Strack, "MOS GTO- a turn-off thyristor with MOS controlled emitter shorts," *IEEE Int. Electron Devices Meeting Digest*, Abstract 6.5, pp. 158-161, 1985.

- [12] V. A.K. Temple, "MOS-controlled thyristors a new class of power devices," *IEEE Trans. Electron Devices*, ED-33, No. 10, pp. 1609-1618. 1986.

- [13] F. Bauer et al, "Design Aspects of MOS-Controlled Thyristor Elements: Technology, Simulation, and Experimental Results," *IEEE Trans. Electron Devices*, vol. 38, No. 7, pp 1605-1611, 1991.

- [14] V. A. K. Temple, B. You, A. Q. Huang and F. Holroyd, "Pebb devices and device physics," *Proc. PCIM Power Systems World*, 1998.

- [15] A. Q. Huang, "A unified view of the MOS-gated thyristors," *Solid-State Electronics*, vol.42, no.10, pp.1855-1865, 1998.

## **Chapter 2 The Reverse-Biased Safe Operating Area of the MCT**

#### **2.1 Introduction**

The reverse-biased safe operating area (RBSOA) of a MCT refers to the current-voltage boundary within which the device can be operated without destructive failures during the turn-off transient period [1]. The cause of the destructive failure of power devices can be classified into two categories: thermal and electrical. Although thermal runaway has been a major cause of destructive failure of power devices, it is the electrical failure mechanism that determines the theoretical limitation of the power devices. An isothermal RBSOA study offers insights into the electrical failure mechanism of power devices.

The RBSOA characteristic is arguably the most important characteristics of any power semiconductor device. There are two main types of electrical failure mechanisms of the MCT: current induced latch-up and dynamic avalanche [2]. It has been generally understood that the turn-off capability of the MCT is limited by the onset of latch-up of the thyristor at low voltages, and limited by the onset of dynamic avalanche at high voltages. A reported experimental evaluation of the RBSOA of the MCT observed that, compared to the BJT, the MCT exhibits very different turn-off breakdown characteristics [3]. However, no in-depth theoretical investigation of the electrical failure mechanism of the MCT has been reported in the literature before the paper published through this research work [4].

This chapter performs a comprehensive investigation of the electrical turn-off failure mechanism of the MCT with the aid of two-dimensional numerical simulation. For the first time, the relationship between the RBSOA characteristics of the MCT and the static forward blocking characteristics of its lower open-base transistor has been identified. The dynamic avalanche limitation of the MCT was analyzed both qualitatively and quantitatively, based on a first-order model proposed to characterize the lower open-base transistor. It was discovered that the dynamic current gain characteristics of the lower open base transistor account for the performance discrepancy between the P and N type MCTs. The impact of the upper-base charge on the RBSOA characteristics of the MCT has also been investigated. A unified view of the theoretical limitations on the RBSOA of the MCT is presented.

#### 2.2 Structure and Operation

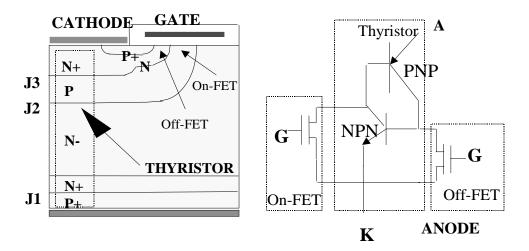

Fig. 2.1 shows a cross-section of the unit-cell of a N-type MCT. The cross-section shown is for a non-punch-through MCT. For a punch-through MCT, there is a N buffer layer between the anode P+ emitter and the N- drift regions. The P-type MCT is a complementary device of the N-MCT, and has a reverse polarity in each of the doping regions. The concept and operating principle of the MCT have been well-documented [5-7].

Fig. 2.1 Cross-section of the unit-cell of a N-type MCT.

When a positive voltage is applied to the gate electrode, the turn-on N-MOSFET is conducting, and electrons are supplied to the base region of the PNP transistor from the N+ emitter via the turn-on channel. This results in the injection of holes from the anode into the Ndrift region. These holes diffuse across the N- drift region and are collected at the reverse-biased junction  $J_2$ , and are then swept into the P base region. If the injection of the holes is strong enough, the holes collected by the base will forward bias the P base/N+ emitter junction  $J_3$  to start the injection of electrons directly from the N+ emitter into the P base region. This triggers the regenerative feedback mechanism between the two coupled transistors within the thyristor structure. The MCT therefore is turned on.

The on-state current conduction in the MCT is accompanied by the injection of a high concentration of both electrons and holes into the lower base or drift region. When the turn-off P-MOSFET is turned on to short the P base/N+ emitter junction of the upper NPN transistor in the thyristor path, all or part of the holes entering the P base region are diverted to the turn-off channel, and, as a consequence, the holding current level of the thyristor increases. The success in turning off the MCT relies on the fact that the latching condition can be broken. Therefore, the amount of current that a MCT can turn off is mainly decided by the conductivity of the inversion channel and the resistance of the upper P base region. As long as the thyristor's latched condition is broken (N+ emitter stops injection), the turn-off then proceeds like an open-base transistor with a rapid current fall followed by a current tail while excess carriers inside the N- drift recombine.

The simulated N-MCT devices are chosen to have a turn-off channel length of 0.5  $\mu$ m and a turn-on channel length of 4  $\mu$ m. The N- drift region has a doping concentration of 5×10<sup>13</sup> cm<sup>-3</sup> and a thickness of 400  $\mu$ m. The N+ emitter and the P base region have a surface concentration of 1×10<sup>19</sup> cm<sup>-3</sup> and 2×10<sup>17</sup> cm<sup>-3</sup>, and a junction depth of 2.5  $\mu$ m and 7  $\mu$ m, respectively. The simulated P-MCT has the same doping profile as the N-MCT except with a reversed doping polarity. The lifetime of the electron is assumed to be seven times that of the

hole in the simulation, unless otherwise indicated. This ratio is based on experimental results obtained on irradiated MCTs and diodes [8].

#### 2.3 Maximum Controllable Current Density

As discussed before, the turn-off of the MCT relies on breaking the regenerative action of the thyristor structure through the action of the turn-off MOSFET. For switching applications, it is essential that the MCT operate within the range of the current densities that can be interrupted by the gate. The highest current density that can be interrupted by the gate is defined as the Maximum Controllable Current Density ( $J_{mcc}$ ) of the MCT.

When the turn-off MOSFET is turned on to short the P base/N emitter junction of the upper NPN transistor of a N-MCT, the holes entering the P base region are diverted to the turn-off channel. Consider the cross-section of the N-MCT shown in Fig. 2.1. The voltage drop at the center of the P base (V<sub>B</sub>), due to the flowing of the hole current along the turn-off path, is given by  $V_r = I_h(R_P + R_{SP} + R_{CH})$ , where, R<sub>P</sub>, R<sub>SP</sub>, and R<sub>CH</sub> are the P base lateral resistance below the N+ emitter, the spreading resistance between the channel and P base region, and the channel resistance of the turn-off MOSFET, respectively. Assuming the channel resistance is dominant, then

$$V_B = \alpha_{PNP} JAR_{CH} \tag{2.1}$$

where  $\alpha_{PNP}$  is the current gain of the lower PNP transistor, J is the current density and A is the total area of the unit cell. Assuming the turn-off P-MOSFET is operated in the linear region, the channel resistance is given by

$$R_{CH} = \frac{L_{CH}}{W_{CH}\mu_{IS}C_{OX}(V_G - V_T)}$$

(2.2)

In Eq. 2.2,  $L_{CH}$  is the channel length,  $W_{CH}$  is the channel width of the half-unit cell,  $U_{IS}$  is the hole mobility in the inversion layer,  $C_{OX}$  is the specific capacitance of the gate oxide,  $V_G$  is the applied gate bias, and  $V_T$  is the threshold voltage. Substituting Eq. 2.2 into Eq. 2.1, and considering the fact that the turn-off MOSFET will fail to interrupt the emitter junction injection when the voltage drop at P base exceeds the build-in potential ( $V_{bi}$ ) of the emitter junction, the maximum controllable current density can then be derived as

$$J_{mcc} = \frac{\mu_{IS} C_{OX} (V_G - V_T) V_{bi}}{\alpha_{PNP} L_{CH}} \frac{W_{CH}}{A}$$

(2.3)

The MCT is not able to turn off current densities higher than its maximum controllable current density value. Therefore, the  $J_{mcc}$  given by Eq. 2.3 imposes a current limitation line in the RBSOA of the MCT. One primary design goal for a MCT device is a high  $J_{mcc}$  capability. The  $J_{mcc}$  is determined by various geometrical and technology parameters as shown in Eq. 2.3. According to Eq. 2.3, the  $J_{mcc}$  of the MCT can be increased by either reducing the channel length ( $L_{CH}$ ) or increasing the off-channel density ( $W_{CH}/A$ ), which is defined as the channel width ( $W_{CH}$ ) within a unit area (A).

#### 2.4 Dynamic Avalanche Limitation

#### 2.4.1 Correlation between the Dynamic and Static Characteristics

If the on-state current density of the MCT is lower than its  $J_{mcc}$ , injection from the upper emitter will cease after the turn-off MOSFET is turned on. The cessation of the injection at the

N+ emitter cuts off the base-driving electron current of the lower transistor. Since the device is typically turning off an inductive load, the current flowing through the lower transistor of the MCT remains constant. The constant current is sustained by extracting stored carriers out of the drift region. As a result, the depletion region is developed, and the anode voltage of the MCT starts to rise with respect to the cathode. During a clamped inductive turn-off, a successful turn-off is accomplished when the inductive current is totally bypassed by the free-wheeling diode after the voltage rises to the clamped value.

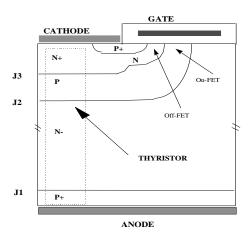

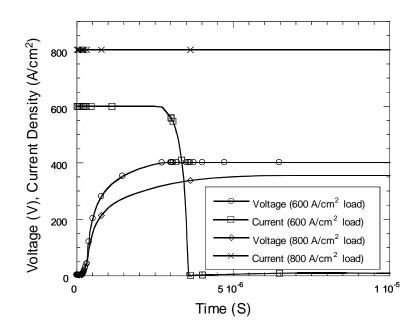

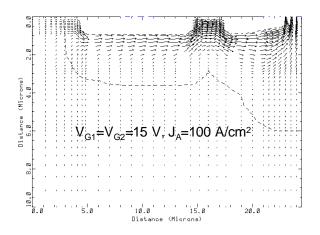

Fig. 2.2 shows the simulated voltage and current waveforms of the P-MCT in gating off two inductive loads at a clamped voltage of 400 V. In the case of turning off a 600 A/cm<sup>2</sup>, the anode voltage climbs to 400 V, then the current begins to decrease, and a successful turn-off is accomplished.

Fig. 2.2 Simulated voltage and current waveforms of the P-MCT in gating off two different inductive loads at a clamped voltage of 400 V.

However, during the process of building up the voltage, a large number of carriers exist inside the depletion region due to the inductive load. The electric field generated by the voltage may therefore be sufficiently high to initiate avalanche. With the onset of avalanche at a high electric field, the constant load current across the depletion region can then be supported by the drift of carriers generated by the avalanche multiplication. If the free carriers generated in the space charge region are sufficient to carry the inductive load current, the load current will stop extracting stored carriers. As a consequence, the depletion region will no longer expand, and the voltage will stop rising. If the terminal voltage of the MCT enters a saturation state before it rises to the clamped voltage value, as in the case of gating off an 800 A/cm<sup>2</sup> load in Fig. 2.2, the turn-off is considered unsuccessful due to the dynamic avalanche.

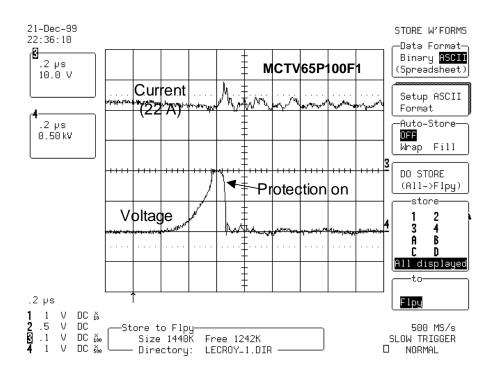

Fig. 2.3 shows the experimental voltage and current waveforms of a P-MCT tested in an snubberless inductive turn-off circuit. The voltage of the device is saturated at 1000 V due to the avalanche while carrying a 22 A constant current. The turn-off will fail if the clamped voltage is higher than 1000 V.

The avalanche happens during the turn-off transient, and therefore is a dynamic phenomenon. However, from the electrical failure mechanism point of view, only the avalanche which results in a saturation of terminal voltage will cause a turn-off failure; otherwise the inductive load will continue to force the anode voltage of the MCT to the clamped voltage. When a turn-off failure due to dynamic avalanche happens, both the anode voltage and the anode current will no longer change with time. Therefore, this can be considered as a quasi-static characteristic. If the load current and the saturation voltage are taken as a pair of operating points, these points must also be on the locus defined by the terminal voltage and current of the MCT in its forward blocking state. In other words, the dynamic avalanche limitation boundary, and hence the RBSOA of the MCT, are indeed imposed by the locus of the MCT in its forward blocking state. The correlation between the dynamic RBSOA and the static forward blocking characteristics has also been reported in an independent parallel work on the IGBT [9].

Fig. 2.3 Experimental current and voltage waveforms of a P-MCT during a snubberless inductive turn-off.

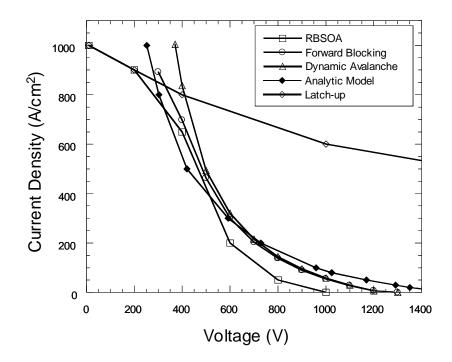

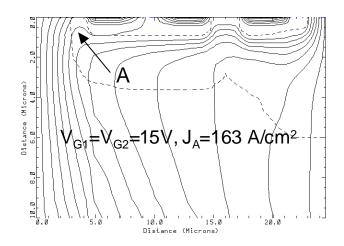

To verify the above statement, several sets of simulations were carried out on the P-MCT shown in Fig. 2.2. The maximum initial current density that can be successfully turned off under each specified clamped voltage was marked as a RBSOA point, and the resulting RBSOA of the P-MCT is shown in Fig. 2.4. In another set of simulations, the forward blocking current-voltage curve of the P-MCT after the static breakdown was obtained and is also shown in Fig. 2.4. It is shown that these two curves fit well at high voltages, a region which is generally described as the dynamic avalanche-limiting region. Since an MCT acts as an open-base transistor in series with a turn-off MOSFET when the current is lower than its  $J_{mcc}$  value during its forward blocking state, the forward blocking current-voltage curve of the MCT is essentially the current-voltage locus of its lower open-base transistor. It is the lower open-base transistor that determines the dynamic avalanche characteristics of the MCT. In the next section, a first order analytic model is proposed to characterize the lower open-base transistor of the MCT.

Fig. 2.4 Limiting factors of the RBSOA of the P-MCT.

#### 2.4.2 Analytical Model of the Lower Transistor

The lower open-base transistor of a MCT has a different structure from traditional bipolar power transistors. Traditional bipolar power transistors have a narrow base necessary for a high current gain and a wide collector region used to support the high voltage, while the lower open-base transistor of the MCT relies on a wide base region to withstand the voltage. The static breakdown voltage of an open-base transistor is termed  $BV_{CEO}$ , and is given by [1]

$$BV_{CEO} = BV_{pp} (1 - \alpha_o)^{\frac{1}{n}}$$

(2.4)

where  $\alpha_0$  is the common base current gain of the open-base transistor,  $BV_{PP}$  is the parallel plane junction breakdown voltage, and n is a constant, which has different values for NPN and PNP transistors. It needs to be noted that  $\alpha_0$  is the common base current gain of the open-base transistor at a very low leakage current level.

During the high-current and high-voltage operation of the open-base transistor, the current in the depletion region is supported by the drift of both electrons and holes under the influence of strong impact ionization created by the high electric field. Due to the high electric field prevalent in the depletion region, the electrons and holes can be assumed to be transported through the depletion region at their saturated velocities. Consequently, the electron and hole concentration in the drift region are related to the corresponding current densities  $J_n$  and  $J_p$  by

$$n = \frac{J_n}{qv_{sat,n}} \tag{2.5}$$

and

$$p = \frac{J_p}{q_{v_{sat,p}}}$$

(2.6)

where  $v_{sat, n}$  and  $v_{sat, p}$  are the saturated velocities for electrons and holes, respectively. Assuming the doping concentration in the base region is  $N_B$ , the net charge in the drift region of the PNP transistor is then given by

$$N = N_B - \frac{J_n}{qv_{sat,n}} + \frac{J_p}{qv_{sat,p}}$$

(2.7)

The saturated velocity of electrons is believed to be higher than that of holes in the high field region [1]. Assume  $v_{sat,h} = v_{sat}$  and  $v_{sat,n} = \rho v_{sat}$ , then  $\rho$  is a ratio factor greater than unity.

The carrier current density can be expressed as  $J_p = \alpha J$  and  $J_n = (1-\alpha)J$ , where J is the total current density and  $\alpha$  is the dynamic current gain, which is defined as the ratio of minority current to the total current in the drift region of the open-base PNP transistor. Eq. 2.7 can then be rewritten as

$$N = N_B + Q \tag{2.8}$$

where Q is the net free carrier charge defined by

$$Q = \frac{J}{qv_{sat}g_1}(\alpha - g_2) \tag{2.9}$$

and

$$g_1 = \frac{\rho}{1+\rho}, \ g_2 = \frac{1}{1+\rho}$$

(2.10)

The electric field distribution in the drift region is determined by the net charge N. Poisson's equation in the drift region is

$$\frac{dE(x)}{dx} = -\frac{q}{\varepsilon}N = -\frac{q}{\varepsilon}(N_B + Q)$$

(2.11)

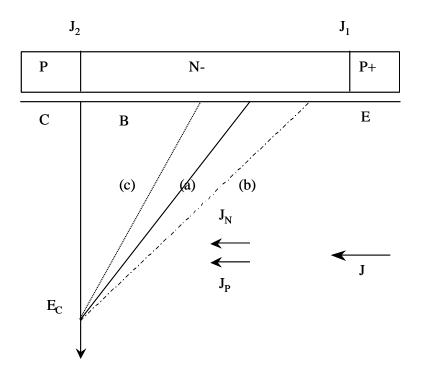

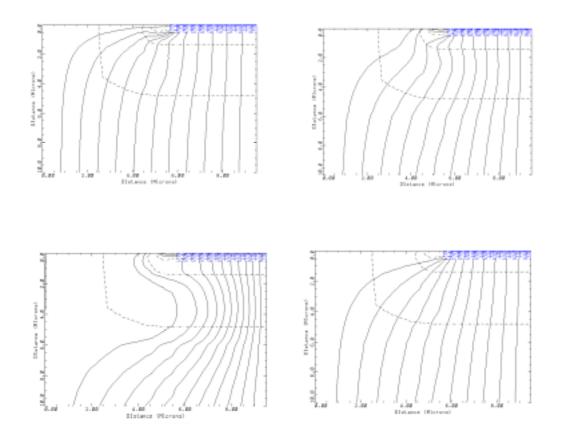

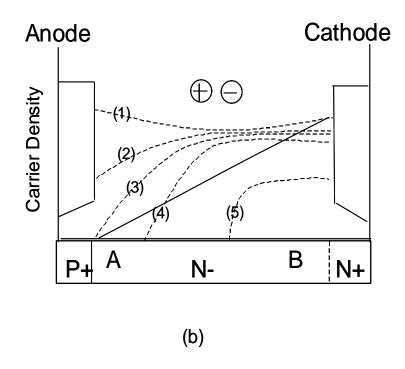

The presence of the free carrier charge Q alters the electric field distribution in the drift region as shown in Fig. 2.5. It can be seen that the electric field in the drift region varies linearly with distance, as in the case of a reversed biased junction, but its rate of variation is dependent upon the free carrier charge Q, which is a function of current density J and dynamic current gain  $\alpha$ . Assume the electric field distribution when the static breakdown starts to initiate is indicated

by the curve 'a' in Fig. 2.5. As the current increases, the free carrier charge Q will step in, and change the slope of the electric field profile. If the value of Q is positive, the slope of the electric field profile is shown by curve 'c'. If the value of Q is negative, the slope will be changed to curve 'b'.

Fig. 2.5 Electric field distribution in the drift region of the open-base PNP transistor of a N-MCT.

After the onset of avalanche in the drift region of the open-base transistor, the peak electric field can be assumed to be a fixed value  $E_c$ . Assuming a triangle-shaped electric field, the voltage supported by the drift region, therefore, is reversed proportional to the net charge N by

$$V = \frac{E_c^2 \varepsilon}{2qN}$$

(2.12)

Substituting Eq. 2.8 into Eq. 2.12 will give rise to

$$V = \frac{E_c^2 \varepsilon}{2qN_B [1 + \frac{J}{qN_B v_{sat} g_1} (\alpha - g_2)]}$$

(2.13)

Since the blocking voltage when the current is very small is the static breakdown voltage of the open-base transistor, i. e.,  $BV_{CEO}$ , Eq. 2.13 can then be expressed as

$$V = \frac{BV_{CEO}}{[1 + \frac{J}{qN_B v_{sat} g_1} (\alpha - g_2)]}$$

(2.14)

Eq. 2.14 is the characteristic equation for the lower open-base PNP transistor of the N-MCT at high-voltage and high-current states. The lower open-base NPN transistor of the P-MCT has the same characteristic equation as Eq. 2.14, except with

$$g_1 = g_2 = \frac{\rho}{1+\rho}$$

(2.15)

The dynamic current gain appearing in Eq. 2.14 is not a constant value, and itself is also a function of the current density J. Since the root locus of Eq. 2.14 sets the dynamic avalanche limitation boundary of the MCT, it is this dynamic current gain  $\alpha$  of the lower open-base transistor that determines the dynamic avalanche limited RBSOA of the MCT. The characteristic equation also indicates that the current-voltage curve will exhibit a snapback if the dynamic current gain value is higher than the value of  $g_2$ . The higher the dynamic gain, the more severe the snapback. The value of  $g_2$  can be considered a critical gain, which determines whether the device can achieve a full static blocking capability or not. If the saturated velocity of electrons is

assumed to be the same as that of holes, i. e.,  $\rho$ =1, the critical gain for both P-MCT and N-MCT will be 0.5. In the simulation using Silvaco's Atlas [10], the saturated velocity of electrons is about  $1.0 \times 10^7$  cm/sec, and that of holes is about  $0.8 \times 10^7$  cm/sec. Therefore, the critical gain for P-MCTs is about 0.56, while the critical gain for N-MCTs is 0.44.

#### 2.4.3 Dynamic Current Gain Characteristics

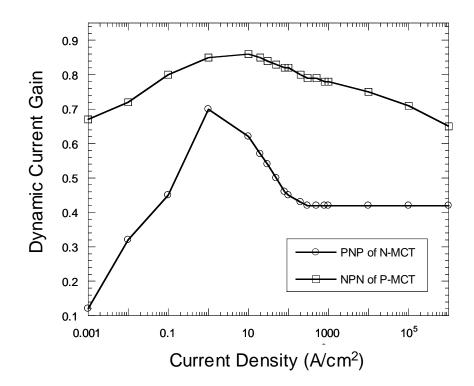

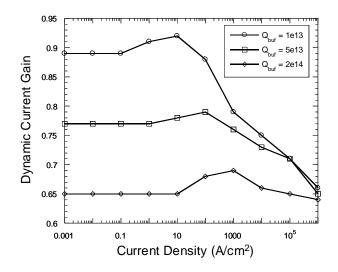

The common base current gain  $\alpha_0$  is a function of the lower transistor doping profile, base/collector voltage, transistor type, temperature, and current level [11]. Among these, the current dependence can be significant. However, the dynamic current gain characteristics of an open-base transistor at high-current and high-voltage states have not yet been reported in any literature. In this study, the dynamic current gain value of lower transistors was extracted from the simulation data. The ratio of the minority carrier current to the total current in the drift region was measured and considered as the dynamic current gain  $\alpha$ .

Fig. 2.6 shows the calculated dynamic current gain value of the lower NPN transistor of the P-MCT as a function of the current density. The origin point represents  $\alpha_0$ , the current gain used to determine the static breakdown voltage BV<sub>CEO</sub>. The  $\alpha_0$  is about 0.67. It is shown that the peak dynamic current gain is about 0.86, which happens when the current is around 10 A/cm<sup>2</sup>. The dynamic current gain of the P-MCT will stay as high as 0.8 in the range of several hundred amperes per square centimeter, the typical operating current level of the MCT. Substitute the gain values shown in Fig. 2.6 into Eq. 2.14, and the calculated voltage versus the current locus defined by the first-order model is then superimposed in Fig. 2.4. It basically fits other curves obtained from the simulation.

Fig. 2.6 Calculated dynamic current gain value of the lower transistors of MCTs as a function of current density.

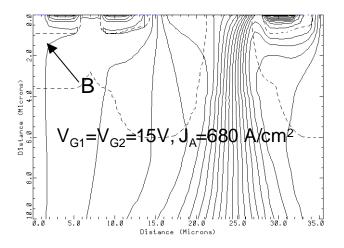

According to Eq. 2.14, a relatively square RBSOA is possible if the high-current dynamic current gain of the MCT can be suppressed. Fig. 2.6 also shows the calculated dynamic current gain of the open-base transistor of the N-MCT. The  $\alpha_0$  is about 0.12. The dynamic current gain initially jumps up to about 0.70 when the current is about 1 A/cm<sup>2</sup>, and gradually stabilizes to a level of 0.42 at about 100 A/cm<sup>2</sup>. In terms of the blocking voltages, it will drop below BV<sub>CEO</sub> first, then stop declining at a certain current level, and will finally move back to BV<sub>CEO</sub> and beyond at high current densities, since the gain value 0.42 is slightly less than the critical gain 0.44. From the viewpoint of RBSOA, this is a favorable characteristic, since the dynamic avalanche limitation only governs a narrow range of voltages, thus making a relatively square

RBSOA possible. Based on the dynamic gain characteristics of the lower transistors, this is more likely to happen in the N-MCT with a lower PNP transistor.

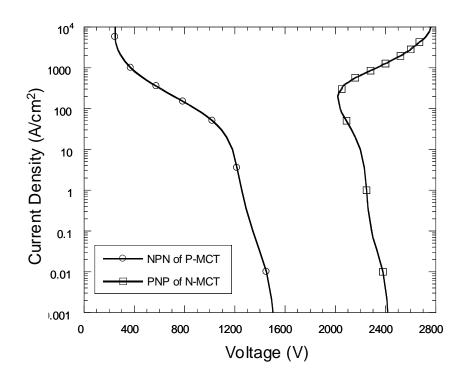

The dynamic current gain characteristics of the lower PNP transistor account for the relatively square RBSOA achieved for the N-MCT. As shown in Fig. 2.7, the lowest forward blocking voltage is about 2000 V for the lower PNP transistor of the N-MCT. Below 2000 V, the RBSOA boundary is limited by the current latch-up, which is less sensitive to the voltage; thus, the N-MCT has a relatively square RBSOA.

Fig. 2.7 Limiting factors of the RBSOA of the N-MCT.

The simulated voltage versus the current locus of the lower transistors of both the N-MCT and the P-MCT in the forward blocking state are shown in Fig. 2.8 over a wide range of current densities. The static breakdown voltage of the PNP transistor of the N-MCT is about 2400 V, 900 V higher than that of the NPN transistor of the P-MCT. Besides this difference, the lower PNP transistor shows distinct I~V characteristics when compared to the lower NPN transistor. Instead of losing a tremendous amount of voltage blocking capability, as shown by the NPN transistor of the P-MCT with the current increase, the voltage blocking capability of the PNP transistor of the N-MCT stops declining around 100 A/cm<sup>2</sup>, and starts to increase beyond that current density.

Fig. 2.8 Simulated forward blocking capability of the lower transistors of the MCTs.

It has been experimentally confirmed that the P-MCT has lost a substantial amount of forward voltage blocking capability compared to the N-MCT [12]. The dynamic current gain characteristics of the lower transistor account for the de-rated forward blocking capability of the

P-MCT. In comparison with the N-MCT, the P-MCT first loses some static breakdown voltage (BV<sub>CEO</sub>) due to its relatively high common base current gain  $\alpha_0$  and higher impact ionization rate of electrons; the latter is expressed in the form of a lower n value in Eq. 2.4. Aside from that, the dynamic current gain characteristics of the P-MCT reduce its forward blocking capability even further, as predicted by Eq. 2.14.

From the above discussion, it is clear that a lower transistor with a low dynamic gain is needed in order to obtain a good forward blocking capability and hence a square RBSOA. Among the factors that determine that common base current gain  $\alpha_0$ , doping profile of the lower transistor is one of the design parameters that can be optimized.

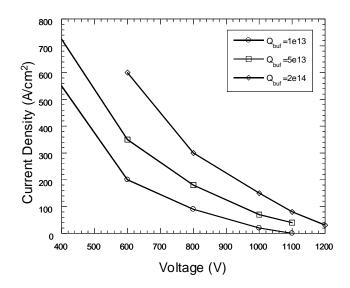

To investigate the impact of the doping profile on the dynamic gain characteristic, a punch-through P-MCT with a varied lower base buffer charge has been studied. This PT P-MCT has a similar top MCT structure to that of the NPT P-MCT except the former has a narrower drift region. The simulated dynamic current gain characteristics of the lower NPN transistor with a varied buffer charge are shown in Fig. 2.9. This figure shows that increasing the buffer charge can reduce the current gain, thus improving the RBSOA of the P-MCT, as shown clearly in Fig. 2.10. However, the dynamic current gains of the P-MCT are still higher than the critical gain value of 0.56, and the strong voltage-dependent RBSOA characteristic has not yet been changed. The dynamic current gain of all these transistors will eventually merge toward the same value at an extremely high current level. This gain characteristic of the lower open-base transistor depends more and more on the intrinsic properties of carriers such as the impact ionization rate, the saturated velocity, etc., while the doping profile will gradually lose its control on the dynamic gain characteristic.

Fig. 2.9 Calculated dynamic current gain value of the lower NPN transistor of a PT P-MCT with a varied lower-base buffer charge.

Fig 2.10 Dynamic avalanche limited RBSOAs of the PT P-MCT with a varied lowerbase buffer charge.

## 2.5 Unified View of The RBSOA of the MCT

#### **2.5.1 Upper-base Modulation Effect**

As stated at the beginning of this chapter, there are two main types of electrical failure mechanisms of the MCT: current induced latch-up and dynamic avalanche. The current induced latch-up limitation is characterized by Eq. 2.3, which calculates the  $J_{mcc}$  capability of the turn-off MOSFET of the MCT. The dynamic avalanche limitation is described by Eq. 2.14, which characterizes the lower open-base transistor of the MCT. Therefore, the combination of Eq. 2.3 and Eq. 2.14 determines the RBSOA boundary of the MCT.

The simulated RBSOA boundary imposed by the latch-up limitation individually, as well as that imposed by the dynamic avalanche as discussed in previous sections, is then superimposed on the simulated RBSOA curve, and shown in Fig. 2.4 for the P-MCT, and in Fig. 2.7 for the N-MCT. These two figures confirm that the RBSOA of the MCT is limited by the onset of the latch-up at low voltages, and by dynamic avalanche at high voltages. While the latch-up limitation is relatively insensitive to the operating voltage, the dynamic avalanche limitation could be either strongly voltage-dependent, as shown in the P-MCT, or insensitive to the operating voltage, as observed in the N-MCT. A relatively square RBSOA, which is mainly current-limited, has been achieved for the N-MCT.

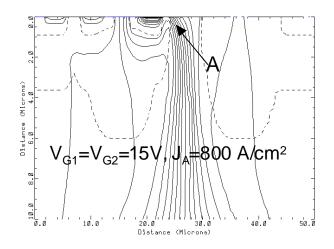

During the study, a drastic loss of current control capability in the transition region between the latch-up limitation and the dynamic avalanche limitation boundaries has been observed in some devices. As shown in Fig 2.11, the RBSOA boundary of a 2400-V N-MCT (case I) is substantially lower than the latch-up limitation ( $J_{mcc}$ ) line in the range of 1200 V to 2000 V. The reason for the degradation of the RBSOA characteristics was found due to a strong upper-base resistance modulation effect, which occurs in the MCT with a relatively low charge in the upper base. During the turn-off phase of building up the voltage, the expansion of the depletion region into the upper-base region increases the lateral resistance of the upper base. This base resistance modulation effect is particularly pronounced when the MCT has a shallow upper base with a low charge. The lateral resistance may cause current crowding during the turn-off transient, and triggers the injection from the emitter junction. The injected carriers will undergo a multification process due to the existence of a high electric field in the upper-base/lower-base junction, and eventually makes the device reenter a state of latch-up. This failure mechanism can be viewed as the joined effect of dynamic latch-up and dynamic avalanche, and it has been demonstrated that increasing the upper-base charge can eliminate the degradation of the turn-off capability due to the upper-base resistance modulation effect. A sharp transition between the two distinctive limitation boundaries has been achieved on the N-MCT by increasing the upper-base charge from  $2x10^{12}$  to  $3x10^{12}$ , as shown in Fig. 2.11.

Fig. 2.11 Limiting factors of the RBSOA of a N-MCT with a varied upper-base charge.

#### 2.5.2 P-MCT vs. N-MCT

Based on the polarity of the device, the MCTs can be classified into two categories: Ntype MCTs and P-type MCTs. The N-MCT has a P-type turn-off MOSFET and a lower PNP transistor, while both the turn-off MOSFET and the lower transistor of the P-MCT are N-type.

According to Eq. 2.3, the P-MCT has a higher  $J_{mcc}$  value than the N-MCT because the mobility of the electrons in the turn-off N-MOSFET of the P-MCT is two to three times higher than that of the holes in the turn-off P-MOSFET of the N-MCT. Therefore, the P-MCT is a superior structure from the  $J_{mcc}$  point of view. However, the P-MCT has a very poor dynamic avalanche characteristic because of the lower NPN transistor. The strong voltage-dependent RBSOA characteristics of the P-MCT eventually diminish the benefit of its high  $J_{mcc}$  capability. Although the N-MCT has a P-type turn-off MOSFET with a lower  $J_{mcc}$  value when compared to its complementary P-MCT, the N-MCT, with a PNP transistor as the lower transistor, has much better dynamic avalanche limited RBSOA characteristics. Therefore, the N-MCT is preferred not only from the application point of view, but also from the RBSOA point of view. Besides the better RBSOA characteristics, the N-MCT also has better turn-off characteristics, such as the turn-off loss, than its P-type counterpart [8].

Based on the above discussion, one would not expect Harris Semiconductor's first MCT product to be a P-MCT. The reason for this lay in the device channel densities practical at that time. The problem with making the N-type MCT was never the vertical device tradeoff, such as the dynamic avalanche limited RBSOA, or the turn-off loss characteristics, but the fact that the turn-off P-MOSFET was not able to reach a channel density ( $W_{CH}/A$ ) that would allow a J<sub>mcc</sub> at about 400 A/cm<sup>2</sup> at 150 °C to make an N-MCT practical [8].

During the past several years, the off-FET channel densities have increased to the point where a N-MCT with a  $J_{mcc}$  at several hundreds of amperes per square centimeter can be made. The latest reported N-MCT has been able to turn off 1100 A/cm<sup>2</sup> at room temperature, and greater than 500 A/cm<sup>2</sup> at 150 °C by using an off-FET channel density of 25 m/cm<sup>2</sup>, twice that of the old generations of the MCT [8]. It has been experimentally confirmed that the N-MCT has a square RBSOA [13].

## **2.6 Conclusion**

This chapter performed a comprehensive theoretical investigation of the electrical failure mechanisms of the MCT, and, for the first time, identified the dynamic avalanche limited RBSOA boundary of the MCT as the voltage versus current locus of the lower open-base transistor in its high-current forward blocking state.

A first-order analytical model, based on the concept of dynamic current gain, was developed to characterize the high-current forward blocking characteristics of the lower openbase transistor of the MCT. A characteristic equation for the dynamic avalanche limited RBSOA boundary of the MCT was developed. It was found that the difference between the dynamic current gain value and a constant critic gain determines the RBSOA boundary.

It is the dynamic current gain characteristic of the lower open-base transistor that accounts for the performance discrepancy between the P-MCT and N-MCT. The impact of the doping profile on the dynamic current gain characteristic has also been investigated, and it has been found that the dynamic current gain characteristic will eventually depend on the intrinsic properties of the carriers, and the doping profile will gradually lose its control with the increase of current.

Since the MCT, the IGBT, and other MGT devices all behave as open-base transistor in the turn-off transient, the RBSOA limitations due to the dynamic avalanche are essentially the same for all these devices. Therefore, the analytical model developed for the dynamic avalanche limitation of the MCT can also apply to other bipolar power devices such as the IGBT.

Finally, a unified view on the limiting factors of the RBSOA of the MCT was presented. It was concluded that the strong voltage-dependent RBSOA characteristics of the P-MCT eventually diminish the benefit of its high  $J_{mcc}$  capability, and the N-MCT is preferred not only from the application point of view, but also from the RBSOA point of view. It was also found

that a high upper-base charge is necessary in order to achieve a relatively square RBSOA in the N-MCT.

## References

- [1] B. J. Baliga, *Power Semiconductor Devices*, (PWS Publishing Company, 1995).

- [2] N. Iwamuro, B. J. Baliga, R. Kurlagunda, G. Mann and A. W. Kelley, "Comparison of RBSOA of ESTs with IGBTs and MCTs," *Proc. ISPSD*, pp. 195-200, 1994.

- [3] D. Y. Chen, F. C. Lee and G. Carpenter, "Nondestructive RBSOA characterization of IGBTs and MCTs," *IEEE Trans. Power Electronics*, vol.10, no.3, pp.368-372, 1995.

- [4] B. You and A. Q. Huang, "Theoretical limitation of the RBSOA of the MOS-Controlled Thyristors," *Solid-State Electronics*, vol. 42, no. 5, pp.785-794, 1998.