## Sequential Circuit Design with Verilog

ECE 152A – Winter 2012

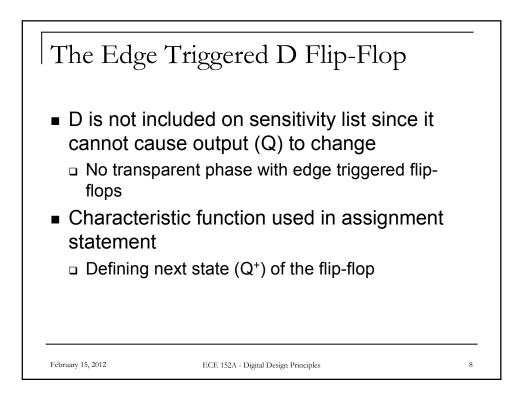

| The Edge          | e Triggered D Flip-Flop                                               |   |

|-------------------|-----------------------------------------------------------------------|---|

| Positive e        | edge triggered                                                        |   |

| inj<br>ou         | le flipflop(D, Clock, Q);<br>put D, Clock;<br>ttput Q;<br>g Q;        |   |

|                   | ways @(posedge Clock)<br>$Q = D; //Q^+ = D$ , characteristic function |   |

| endmo             | odule                                                                 |   |

| February 15, 2012 | ECE 152A - Digital Design Principles                                  | 7 |

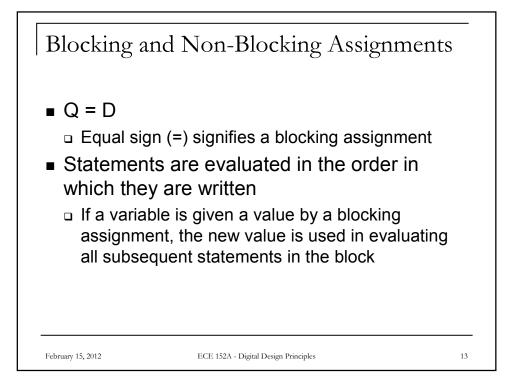

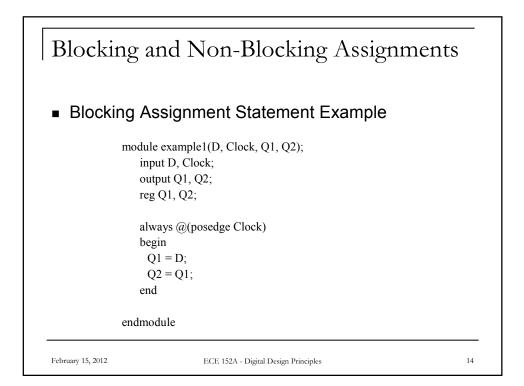

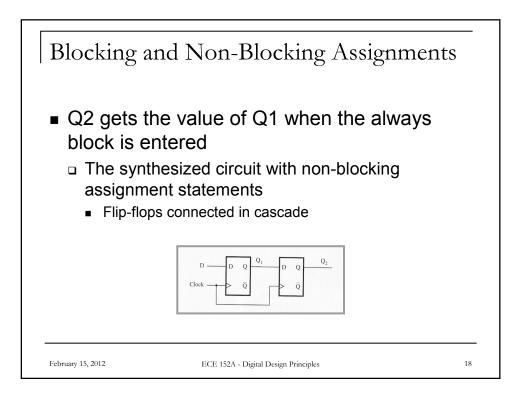

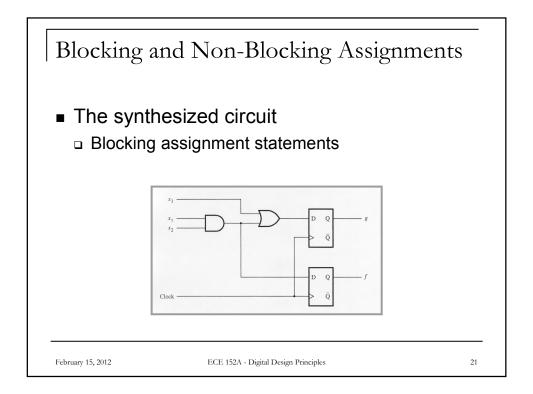

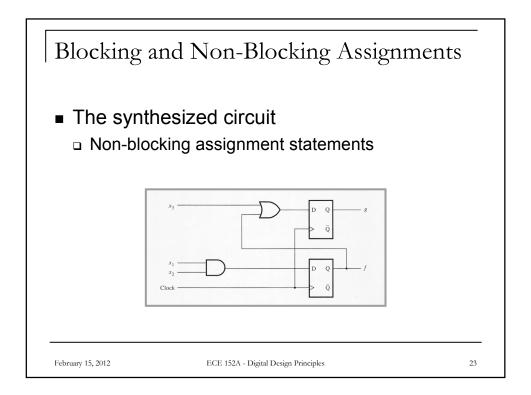

| Blocking and Non-Blocking Assignments |                                                                                                  |    |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------|----|--|--|

| <ul> <li>Blocking A</li> </ul>        | Assignment Statement Example                                                                     |    |  |  |

| i                                     | lule example3(x1, x2, x3, Clock, f, g);<br>input x1, x2, x3, Clock;<br>putput f, g;<br>reg f, g; |    |  |  |

| ł                                     | always @(posedge Clock)<br>begin<br>f = x1 & x2;<br>g = f   x3;<br>end                           |    |  |  |

| endr                                  | nodule                                                                                           |    |  |  |

| February 15, 2012                     | ECE 152A - Digital Design Principles                                                             | 19 |  |  |

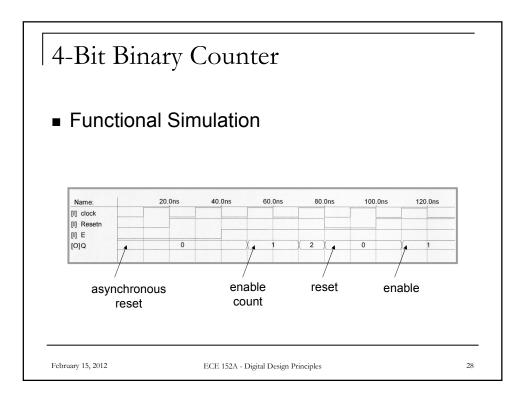

| Flip-Flops with Clear           |                                                                        |    |

|---------------------------------|------------------------------------------------------------------------|----|

| <ul> <li>Asynchronou</li> </ul> | us Clear                                                               |    |

| module flipfle                  | pp(D, Clock, Resetn, Q);                                               |    |

| input D, Clock, Resetn;         |                                                                        |    |

| output Q;                       |                                                                        |    |

| reg Q;                          |                                                                        |    |

| always @<br>if (!Res<br>else    | Q(negedge Resetn or posedge Clock)<br>etn)<br>$Q \le 0;$<br>$Q \le D;$ |    |

| endmodule                       |                                                                        |    |

| February 15, 2012               | ECE 152A - Digital Design Principles                                   | 25 |

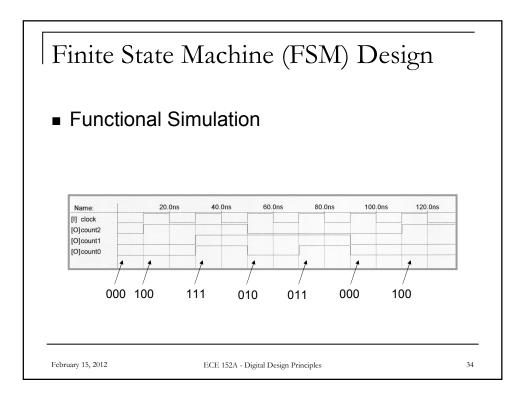

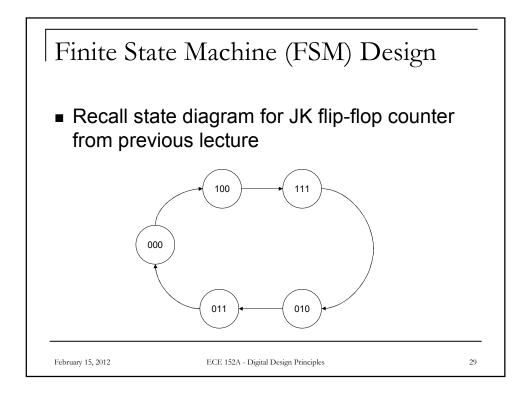

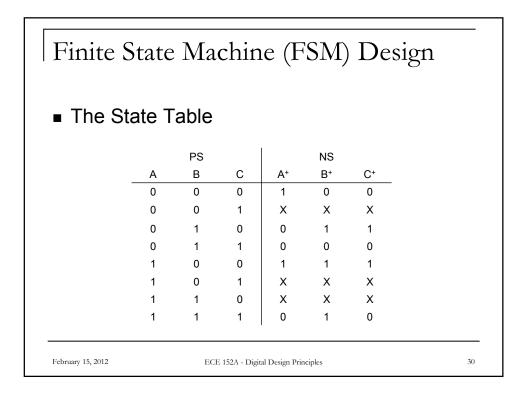

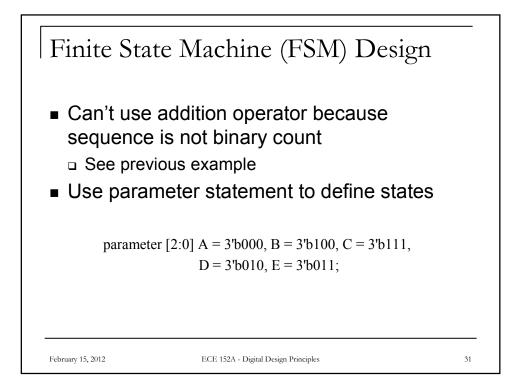

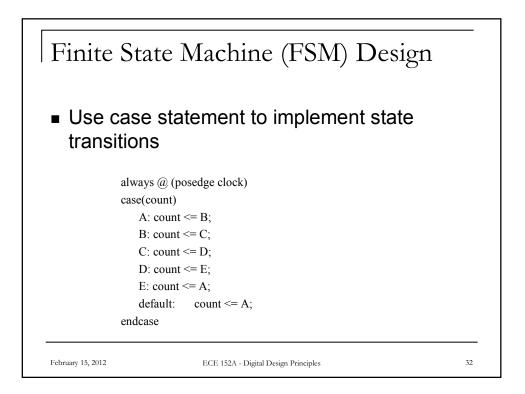

| Finite            | State Machine (FSM) Design                                                                                                                                           |    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| ■ The c           | omplete module                                                                                                                                                       |    |

|                   | module jk_counter(count, clock);                                                                                                                                     |    |

|                   | input clock;<br>output [2:0] count;                                                                                                                                  |    |

|                   | reg [2:0] count;<br>parameter [2:0] A = 3'b000, B = 3'b100, C = 3'b111,<br>D = 3'b010, E = 3'b011;                                                                   |    |

|                   | always @ (posedge clock)<br>case(count)<br>A: count <= B;<br>B: count <= C;<br>C: count <= D;<br>D: count <= E;<br>E: count <= A;<br>default: count <= A;<br>endcase |    |

|                   | endmodule                                                                                                                                                            |    |

| February 15, 2012 | ECE 152A - Digital Design Principles                                                                                                                                 | 33 |