Lab manual as of 11/2/2014. The manual is only complete through Lab C. I am working on introducing a new lab D and have put a fairly complete description of it in the manual. The software for schematic entry has separate on-line instructions. The simulation software operation is also a separate handout on the class website.

wrp

# Brown University School of Engineering

# Engineering 1630 - Digital Electronics System Design Semester I - 2014-15

The Student Lab Manual

Wm. R. Patterson

# **Table of Contents**

| 1. GENERAL INTRODUCTION                                                                                        | 5   |

|----------------------------------------------------------------------------------------------------------------|-----|

| 2. EVALUATION                                                                                                  | 8   |

| 2.1. Grades                                                                                                    | 9   |

| 2.2. Partial Credit                                                                                            |     |

| 2.3. INCOMPLETES                                                                                               | 10  |

| 2.4. THE FAULT TOLERANCE QUESTION (FTQ)                                                                        | 10  |

| 2.5. DOCUMENTATION                                                                                             |     |

| 2.6. Deadlines                                                                                                 |     |

| 2.7. THE ENGN1630 EXCLUSION PRINCIPLE                                                                          |     |

| 2.8. Lab Schedule                                                                                              |     |

| 2.9. TEACHER EVALUATION                                                                                        |     |

| 2.10. COLLABORATION                                                                                            |     |

| 3. GETTING STARTED                                                                                             | 16  |

| 4. CIRCUIT CONSTRUCTION GUIDELINES                                                                             | 17  |

| 4.1. General Hints                                                                                             | 17  |

| 4.2. The 163 Lab Environment                                                                                   | 18  |

| 4.3. LOGIC PROBES                                                                                              | 19  |

| 4.4. POWER SUPPLIES                                                                                            |     |

| 4.5. Bypassing                                                                                                 | 20  |

| 4.6. Debouncing                                                                                                | 20  |

| 5. DESIGN AND TROUBLESHOOTING                                                                                  | 22  |

| 5.1. Design                                                                                                    | 22  |

| 5.2. Troubleshooting                                                                                           |     |

| 6. HOMEWORK, LECTURES, AND TEXTBOOKS                                                                           |     |

| 6.1. Номеwork                                                                                                  |     |

| 6.2. Lectures                                                                                                  |     |

| 6.3. Textbooks                                                                                                 |     |

|                                                                                                                |     |

| 9. THE LAB CHALLENGES                                                                                          | 30  |

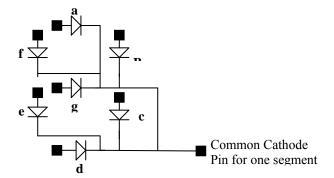

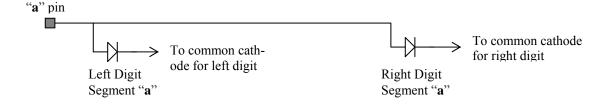

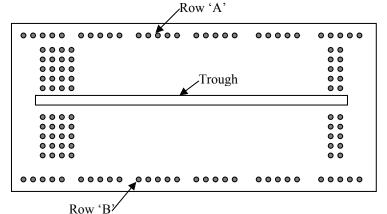

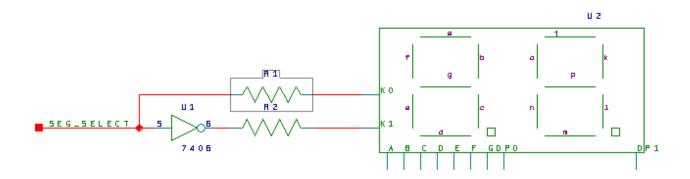

| 9.1. DISPLAYS AND LIGHT EMITTING DIODES                                                                        | 30  |

| 9.2. THE NUMBERED LABS                                                                                         | 34  |

| 9.2.1. Lab Zero                                                                                                | 2.1 |

| 9.2.1. LAB ZERO<br>9.2.2. LAB ONE                                                                              |     |

| 9.2.3. LAB TWO                                                                                                 |     |

| 9.2.4. LAB THREE                                                                                               |     |

| 9.2.5. LAB FOUR                                                                                                |     |

| 9.2.6. Lab Five                                                                                                |     |

| 9.2.6.1. Verilog Implementation of a Counter – An Example                                                      |     |

| 9.2.6.2. Assigning Pin Numbers to Programmable Devices                                                         |     |

| 9.2.6.3. Editing and Compiling Verilog Files for Xilinx Parts                                                  |     |

| 9.2.6.4. Alternative Tutorial for Xilinx CPLD Programming with Verilog                                         |     |

| STAGE 1, SETTING UP YOUR PROJECT                                                                               |     |

| STAGE 1, SETTING OF FOOR PROJECT                                                                               |     |

| STAGE 2, 1 ROGRAMMING VERILOG. THE VERT, VERT BASICS.  STAGE 3, COMPILING YOUR CODE AND LOADING IT ONTO A CPLD | 62  |

| 9.2.7. LAB SIX                                                                                                 |     |

| /.=-/. =: == == ============================                                                                   |     |

| 9.2.8. Lab Seven                                                                                                                 | 72             |

|----------------------------------------------------------------------------------------------------------------------------------|----------------|

| 9.2.9. Lab Eight                                                                                                                 |                |

| 9.2.10. Lab Nine                                                                                                                 |                |

| 9.3. THE LETTERED LABS                                                                                                           | 87             |

| 9.3.1. Lab A:                                                                                                                    | 87             |

| 9.3.3. LAB C:                                                                                                                    |                |

| 9.3.4. LAB D: THIS IS FIRST DRAFT OF A LAB STILL IN DEVELOPMENT. NOT INCLUDED IN INITIAL PROPERTY OF A LAB STILL IN DEVELOPMENT. | RINTING OF THE |

| MANUAL.                                                                                                                          | 100            |

| 9.3.5. Lab E:                                                                                                                    | 114            |

| 9.3.6. Lab F:                                                                                                                    | 115            |

| 9.4. THE LOGIC ANALYZER TOOL                                                                                                     | 116            |

|                                                                                                                                  |                |

| 9.5. REQUIREMENTS FOR A SCHEMATIC DRAWING                                                                                        | 117            |

| 10. THE ENGINEERING 163 CPLD-II BOARD                                                                                            | 121            |

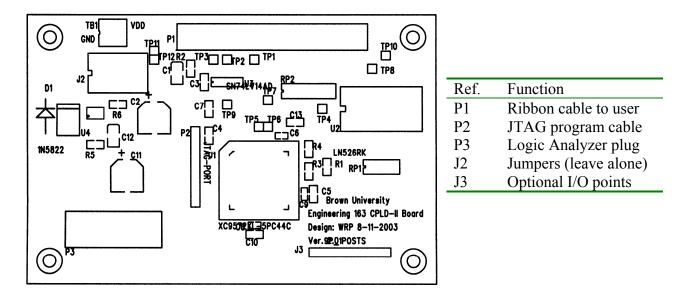

| FIGURE 10.3: SCHEMATIC DIAGRAM OF THE ENGINEERING 163 CPLD BOARD                                                                 | 128            |

| 11. SCHEMATICS AND TIMING DIAGRAMS                                                                                               | 130            |

| 11.1. GENERAL DOCUMENTATION                                                                                                      | 130            |

| 11.2. TIMING DIAGRAMS                                                                                                            |                |

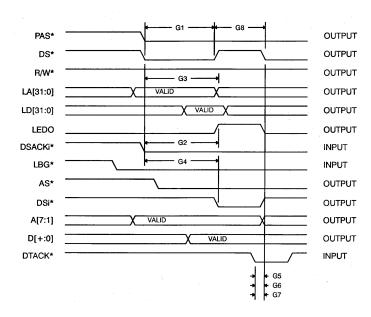

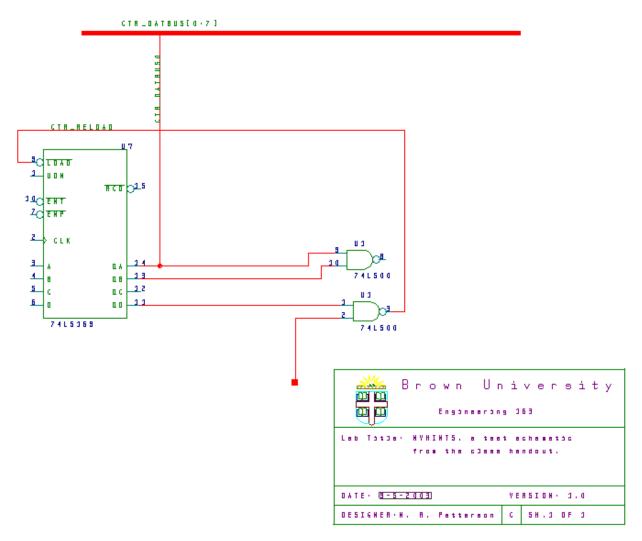

| FIGURE 11.2: TIMING DIAGRAM EXAMPLE.                                                                                             |                |

| 11.3. USING THE DXDESIGNER SCHEMATIC CAPTURE SOFTWARE                                                                            |                |

| 12. COMPONENT DATA INDEX                                                                                                         | 1/12           |

|                                                                                                                                  | ····· 174      |

#### 1. General Introduction

#### Course Overview:

This is primarily a lab-based course. It starts with a series of simple labs getting you acquainted with basic gates and flip-flops and how they are connected to do such tasks as single-bit addition, error correction, bus multiplexing, etc. Few real systems are assembled this way anymore but there are two virtues to these labs. First, they are a simple way to let you learn the basics through your fingers. Second, you learn something about the logic of debugging circuits including finding mechanical problems. (Real systems have lots of design and reliability issues from mechanical problems. There are always difficult design problems in building neat, compact packaging and unexpected reliability issues from lack of durability or from signal errors due to crosstalk, electromagnetic interference (EMI), etc.)

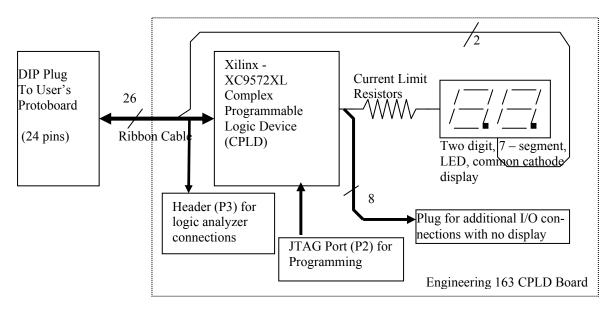

Somewhat more complex logic operations are feasible for you if you build the circuit using programmable logic, one example of which is the complex programmable logic device (CPLD). The one you will use for many of the labs is the Xilinx XC9572XL, which is roughly equivalent to a few hundred basic gates. We have prototyping boards that allow you to embed these devices into larger more practical systems that you must design. Finally in the last few labs, you use an even more powerful programmable device, a Xilinx Spartan  $3E^{TM}$  field programmable gate array (FPGA). While the device itself has been purchased embedded in an evaluation board with a lot of support components, I have built input-output add-on boards to simplify having you design real non-trivial logic systems. Please be patient with us as I revise and augment these labs as I try to do every year.

# Software, Debugging, and Simulation Tools:

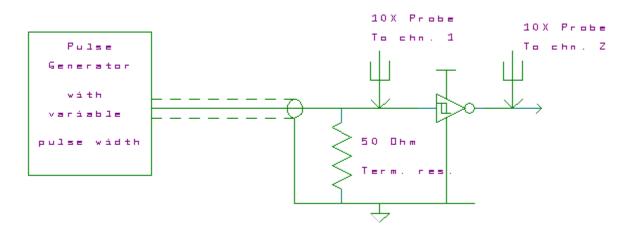

As part of learning the practice of the profession, we require you to use some *industrial* strength CAD software. You will learn schematic capture in DxDesigner, a design tool suite from Mentor Graphics Corp. This tool is a widely used starting point for printed circuit board design, the only feasible means of solving those pesky interconnection problems! On the other hand, we no longer use DxDesigner to do circuit simulation of discrete circuits because small scale logic is generally not complex enough to warrant logical simulation while the real issues in such designs are electrical not logical, e.g., transmission line reflections, propagation time effects, crosstalk, etc. These effects are not captured by logic simulators but require specialized simulators, one of which, Hyperlinx, is part of the DxDesigner tool suite.

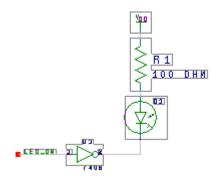

You will only do logic simulation for your programmable devices, the complexity of which requires sophisticated simulation capability. (Simulation based on the Verilog hardware description language is actually applicable to fairly complex board-level designs when Verilog descriptions of all the simulatable chips on the board are available from their vendors.) You do labs using Xilinx XC9572XL CPLDs and XC3S500E FPGAs. For their simulation, we will probably use a mix of Xilinx software to program the devices and Aldec Active-HDL software to simulate them. There are continuing changes to both the hardware and software for this latter part of the course, so I expect that this material will not be integrated without a certain amount of difficulty. I ask your indulgence.

It may seem peculiar to you that I do not recommend simulating the first couple of circuits that you build with discrete gates. My feeling is that these are sufficiently simple that you should have confidence in the logical functions you derive. For those of you who really want to do such simulation, there is a collection of free DIY software that includes a couple of very simple logic simulators at <a href="http://www.edn.com/design/diy/4430357/2/Top-free-DIY-tools-every-EE-needs">http://www.edn.com/design/diy/4430357/2/Top-free-DIY-tools-every-EE-needs</a>. Logisim is one of these and was used in CSCI0310 a couple of times.

What is usually more problematic in the first labs is not the logical design but the physical interconnection. Making a *DxDesigner* schematic is not mandatory at the beginning of the course, only being due near the end of the semester. However, I think you would find it quite useful to design using a schematic to capture the interconnections. Knowing from a permanent, visual record where the wires have to go can make the wiring a lot easier and require a lot less debugging.

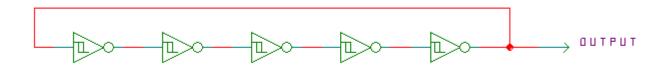

In the same vein, there is a requirement that you eventually use a logic simulator to show waveforms and time relationships in one of your labs. Again, the requirement only has to be fulfilled later in the course but you would get a lot more benefit from using that instrument on labs 5, 7, and 8 as you do the lab and find any need for debugging. Logic analyzers are great for that purpose because they expose both physical errors, that is, interconnection mistakes, and logical errors.

# **Through-Hole Hardware:**

In Engineering 1630, you start by designing small systems with TTL integrated circuits, building them, and then fiddling until they work. The fiddling can go from minor rewiring to complete redesign as one gets accustomed to the subtlety of the problem. This method can be very satisfying and great fun. (Please do not assume that "fiddling" alone is the right way to design. Care in analysis and simulation is the only route to larger systems. Fiddling is simply a necessary step in learning to ask the right questions.) This is not a practical way to build larger systems so the later parts of the course introduce hardware description languages as the first element of more modern approaches.

Your kits are largely made from "TTL" or Transistor Transistor Logic parts because these are the main commercial source of very small blocks of logic, they are still available in convenient packages, and they are quite inexpensive. But it is important to realize that TTL is not the only or even the dominant expression of logical systems even at the very small systems level. In fact, the main driver for my changing the simpler labs is that the components are so obsolete they are disappearing from the market altogether. (If you decide to keep your kit at the end of the course, you will have a pre-made antique collection.)

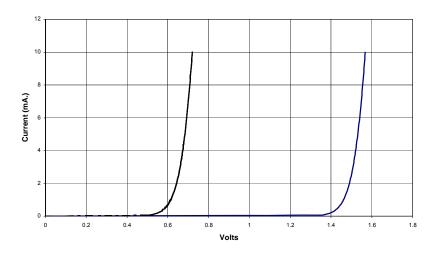

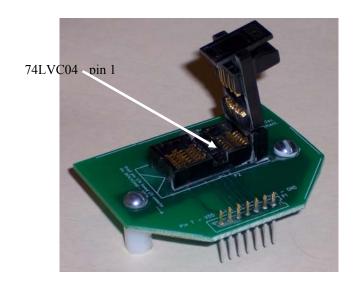

The dominant manufacturing technology for digital circuits is CMOS - the Complementary Metal Oxide Semiconductor process, which we will examine briefly in class in explaining how gates actually do their work. For labs two and six in which you measure gate properties we will supply some TTL-compatible, low voltage CMOS parts from Texas Instruments' SN74LVCxx series. Devices in this family are intended to supply small logic blocks for systems using power supply voltages less than the 5 volts that were standard for many years for TTL. (Most discrete logic today functions on 3.3 volts or lower.) Their working input signal range is 1.8 to 5.0 volts and they

will function with supply voltages over a similar range but are optimized for 3.3 volts supply or less. You will look at their speed and power performance over the full supply range.

#### **Programmable Hardware:**

Complex programmable logic devices (CPLDs in the trade jargon) are a competitive area of development. They are generally smaller and less flexible than FPGAs, but they are much less expensive, require many fewer support components, and have fast, well-controlled propagation delays. (FPGAs have benefited from the most advanced manufacturing processes. As a result their speeds are now faster. The basis of choice is usually the size of the logic - FPGAs implement larger systems, albeit at higher prices. CPLDs, however, do have the curious properties of more efficiently generating simple Boolean products of many inputs and of having propagation times more or less independent of logical function. They are also non-volatile, that is, you do not have to reprogram every time you turn the circuit on.)

You start to do labs with a CPLD at lab 3 and may use one again in Labs 4, 5, 7, A, and B with some restrictions. The ninth lab is on timing simulation, thus introducing the problem of verifying designs before they are built. Labs C through F are done with an FPGA.

You can program both CPLDs and FPGAs either using schematic entry or a hardware description language (HDL) or you can mix the two methods. In all cases you are just converting your thoughts into terms that software can convert to bit patterns for the switches and floating gate transistors in the devices. In this course you will use the Verilog HDL for design entry and will mix that with a schematic for the FPGA labs. In the early labs, labs 3, 4, and 5, you are limited in the syntax you are allowed to use because the point of the labs is the logic not the elegance of how well you can express intent in an HDL language. In the later labs, you are freer to exploit the full language flexibility. Dally and Harting have limited coverage of Verilog syntax and the older textbook by Wakerly (sects. 5.4, 7.13, and examples in chapter 6) has very good coverage of the basics of the Verilog language and there are many other tutorials on the web. I will put a copy of Wakerly on course reserve at the Sciences Library. Some TAs have found the site <a href="http://www.asic-world.com/verilog/index.html">http://www.asic-world.com/verilog/index.html</a> to be useful.

# Class Philosophy:

The emphasis throughout Engineering 1630 is on the design, construction, and verification of digital circuits. In class, we will discuss the conceptual and physical building blocks available to the designer, and show how these tools and techniques are used in various design situations. In the lab, you will take this design theory and put it to use by building actual hardware-based solutions. This may well be your only exposure to full responsibility for making a product work ever! (Engineering, like Computer Science, is a surprisingly social endeavor - most products come from development teams, not isolated geniuses. Most continuing education to keep one's skill set fresh is peer-to-peer.)

Reflecting the fact that this is primarily a hands-on laboratory course, many of the customary requirements of engineering courses have been scaled down. There are only two lab reports and one schematic to compose, and these will be graded on a satisfactory/must be redone basis. The computer simulation lab and the logic analyzer exercise will be at least partially selfdocumenting. There are only minimal fixed deadlines for individual assignments. While there will be a midterm and a final examination, they are intended to encourage you to think of the lab material in a more general framework. Your grade will be calculated as an average of your lab grade and the two exam grades. We expect the exams to test how well you respond to freshly posed problems of a similar nature to those found in the labs.

In the lab you design and build a particular circuit and then demonstrate that system to one of the TAs. You must be prepared to show a schematic of your system drawn with your own hand or through your own schematic entry and to explain it to the TA. The TA must be satisfied with the quality of that documentation before he/she will examine the rest of your work. After studying your approach, the TA will ask you a question about its performance or its design; if you answer the question correctly, the TA signs your scorecard, and you are free to move on to the next lab challenge.

In this course there are no specified times when you have to appear in the lab. You may design and build your circuit wherever you like. We will provide the necessary equipment to test and debug your circuit and will also provide a group of well-qualified teaching assistants to help you with any unusual problems. If you run into problems with malfunctioning equipment or software, please bring it to the attention of a TA or to me.

The liberalized format of ENGN1630 presents you with a number of challenges quite apart from actually building each lab assignment. By the time you take this course (typically in the junior or senior year) we expect that you have learned to think creatively, to work consistently, and to budget your time. The minimal deadlines established for completion of the labs force you to set goals for your own performance. While many design techniques are discussed in class, it is your responsibility to put broad concepts into practice. Making choices is part of the process.

Class will meet on Wednesdays and Fridays, from 3:00 PM until about 4:20. The lab will be open day and night most of the week with TA coverage for about 36 hours per week, with convenient evening hours at least twice a week. The lab will be in the Hewlett Electronics Laboratory, room 196 of the Giancarlo addition, affectionately known by most as "The Fishbowl".

#### 2. Evaluation

The evaluation policy used in ENGN1630 changes with the convictions and whims of the instructor in charge. Some take a rather liberal approach, allowing your circuits alone to represent the depth and breadth of your digital logic design knowledge. Some lower the number of labs and their weighting to make room for formal homework assignments. Others of us use points-oriented grading schemes of Baroque complexity that make your final grade dependent on how well you score on mid-term and final examinations, in addition to the number of design exercises you complete. Each of these approaches has its benefits, and each has its drawbacks.

I follow a grading policy based on a point system. There will probably be a total of 165 points available, 65 points from exams and 100 points allocated for completed lab work as tabulated below. To some extent the exact number of points will have to be adjusted based on how many of the later labs I can get functional in time. I reserve the right to change the total number and their weight depending on how much I get done. Passing performances on both exams and lab work

**separately** are required to pass the course, but a curve will be applied to your total grade to determine the letter grade reported to the Registrar. I find that determining the break points of that curve is sometimes difficult and I try to use criteria that call for above average performance on at least one of the two components of the grade is necessary for an A.

#### 2.1. Grades

Your lab grade is based on the number of lab challenges you complete. There is no partial credit on the lab grades. Instead you will receive points for each successfully completed lab challenge or piece of written lab work. There are 13 hexadecimally numbered labs now. I continue to hope that I will be able to add at least one and perhaps two more. With the points for using the schematic drawing software and the logic analyzer, there are a total of around 100 possible lab points. The distribution of points is:

Lab 0 through Lab 5: 5 points each

Lab 6 through Lab 8 and software simulation Lab 9: 6 points each

Lab A and B: 7 points each

Lab C: 8 points each

Labs D/E if I get that far: TBD

A schematic for either Lab 1, 5, 7, 8, or A: 6 points

Logic analyzer measurement challenge (see section 9.4): 5 points

To pass the course, however, you must have passing grades on **BOTH** the examination and lab parts of the course. A passing grade on the examination part of the course is 48% of the sum of the maximum number of points possible on the exams. A passing grade on the lab part of the course is **51 points**, which **must include credit** for Labs 1 and 2; for one lab from the set 7 and 8; for Lab 9 and for one lab from the B through F series; for the Logic Analyzer Challenge, and for a schematic of either lab 1, 7, 8, or A. **THERE WILL BE NO EXCEPTIONS TO THIS POLICY.** Please note that the use of a logic analyzer is mandatory. The laboratory has a superb collection of instruments and their use is to hardware what a debugger is to software. You don't know much about either discipline without knowing its fundamental test tools.

A word of advice: labs 7 and 8 involve systems with mixed analog and digital signals. Many students find these labs time consuming because they find it difficult to be systematic about dealing with the analog part. The letter series labs may also take significant amounts of time. However, they are purely digital. If you find that the first analog-to-digital converter lab that you do takes too long, then do the letter labs next. Only do the other A/D lab if you have time toward the end of the course.

Scuttlebutt variously suggests that either lab 7 or 8 is much easier than the other. I believe they are about equal difficulty. (I have changed some of the parts and requirements on both labs to make them easier to do than they used to be.) A careful and systematic approach is critical to success within reasonable time limits on either of them. It is not uncommon for some students to take 30 or more hours to do one of these labs, primarily because they do not think systematically about how to test what is going on in the prototype. The use of simulation for the digital section in advance can save enormous amounts of time on these labs and will provide a basis for logic analyzer measurements comparing expected and actual performance. Similarly, comparing the logic analyzer picture to your design intent can also make a big difference in the amount of time the lab takes. Analyzers save time despite their having a certain learning curve. Since you have to use an analyzer eventually, it makes sense to take the time to learn its use early enough to use it here.

Section 7 of this manual contains a scorecard for recording your performance on each of the labs; each time you successfully complete a lab, a TA will sign the line associated with that challenge and make an entry on our backup spreadsheet. I recommend you check that the TA makes this spreadsheet entry. To receive your grade, you must turn in your scorecard at the end of the semester, which is defined as no later than 5:00 PM of the day of the scheduled final examination. **Do not lose your scorecard!!!** I will give credit automatically for whatever is in the duplicate records spreadsheet, but this backup tends to be incomplete, and there are **NO guarantees without the signed scorecard.** People who arrive empty-handed at the end of the semester will receive No Credit for the course.

#### 2.2. Partial Credit

The nature of ENGN1630 precludes the assignment of partial credit for any of the Labs. If, for example, you are told to build a circuit that displays the digits 0, 1, 2, 3, 4, 5, 6, and 7 in a particular order, and you offer a circuit that displays all but the digit 3, you get no credit for the Lab until you troubleshoot the circuit and get it working as requested. This policy just reflects the nature of digital system design, and it is one from which no deviations will be made.

# 2.3. Incompletes

No grade of *Incomplete* for unfinished labs will be given unless you present evidence from a physician or a Dean of a serious and protracted medical problem. Because of the nature of the course, dealing with students after the end of the semester is difficult. The TAs are gone, the lab space is reorganized and used by other courses and other students, and all parts must be checked, cleaned, and inventoried. If you need to pass ENGN1630 to complete the requirements for a specific Brown degree, make sure you *at least* qualify for a grade of C. I have no sympathy for someone who shows up at the end of the semester with a nearly-blank scorecard in hand, and claims that he or she needs this course to graduate. The time to consider the relative importance of ENGN1630 to your educational experience is *now*.

# **2.4.** The Fault Tolerance Question (FTQ)

When you demonstrate a circuit for a TA, you and the TA will spend a couple of minutes verifying that the circuit meets all requirements. You must then show a schematic and explain the operation. (NOTE: This procedure is relatively recent change.) The schematic does not have to be machine generated although that would be preferable. It does have to be both neat and accurate. If you are asked where a particular connection point on the schematic is and reply that well you changed that, then you get to go away and do the documentation over again. The TAs get to decide whether the drawing is neat enough to understand. The TA will then check your breadboard serial number. Remember that you must do your own work with your own kit and substituting another person's breadboard for yours may lose you credit for the lab and risks academic penalties. Finally, the TA will ask a Fault Tolerance Question (FTQ). These questions may take one of three forms, at the option of the TA. For the first type of question, the TA will choose one wire in your circuit and ask what, if anything, will go wrong with your circuit after the wire is removed. For the second type of FTQ, the TA will introduce a problem into your circuit, leaving you the responsibility of finding and correcting the problem. The third type of FTQ will allow the TA to ask you general questions about the operation of your circuit, such as "What will happen to the output of the Q1 flip-flop if both inputs to this NAND gate are grounded?" It is a TA's prerogative to ask for documentation before an FTO.

These notions of an FTQ are based on TTL implementations of small systems. The labs based on programmable devices (CPLD or FPGA) pose special problems for framing good FTQs. In preparation for an FTQ or even for certification of compliance with specifications, **you must present full documentation of your design** including the wiring schematic and any programming file whether Verilog programming code, Xilinx schematic file or Aldec block diagram. The form of that documentation is at the discretion of the TA who may ask for it as a file in your computer account, a printed copy for easier reading, or even an electronic copy. Most likely the TA will prefer a paper schematic and an on-screen file. At the least, the TA will examine this and ask how you designed it. She may ask variants on the hardware FTQs based on changes to operation of the circuit that will be caused by a change to the schematic, Verilog, or Boolean description and may expect you to compile and demonstrate the expected result on the spot. Another possibility is that you will simply be asked to explain the logic of your system and answer questions (plural) about why you did it the way you did.

If you answer the FTQ correctly, the TA will sign your scorecard, congratulate you, and you can celebrate! (As a precautionary measure, you might want to be sure the TA enters your success on the backup sheets just in case you lose your scorecard.) If you do not answer the FTQ correctly, the TA will be obliged to ask you **two more** FTQ's. For every FTQ that you miss, two more must be asked. If several FTQ's are answered incorrectly, we will begin to wonder how you can know so little about a circuit that you designed, built, and tested yourself. We will begin to wonder about plagiarism. If you miss three FTQ's in a row, your circuit breadboard will be temporarily confiscated and you will be referred to the head TA for further consultation. If you are guilty of demonstrating a circuit that someone else designed, you will automatically lose credit for that lab. (If this is a required lab, you may not be able to pass the course.) If a second offense occurs, standard academic discipline procedures will be initiated.

We are aware that a certain amount of shopping around is done by students looking for a soft-hearted TA. To limit this behavior, no one can have more than five labs checked by any one

TA. All the TAs will have been told that we regard FTQ's as serious matters, and no TA has to be a patsy.

For most of the labs, once an FTQ (or a series of FTQ's) have been answered correctly, you have met all the requirements for that lab. There are a few exceptions to this rule. Labs 2 and 6 involve the measurement of important properties of your chips, such as power dissipation, logic levels, propagation delay, etc. They require data and the answers to some questions to be handed in as a report in lieu of an FTQ. These write-ups will be graded only on a *satisfactory/must-be-corrected* basis and will be handed back only after all reports for that lab were due. **You must both take the data and write the report individually!** It is perfectly okay to give each other advice and information, but you are responsible for doing your own work.

Similarly lab 9 on simulation and the schematic drawing by computer design entry require documentation in lieu of FTQs. All documentation is handed in through a box in room 196. We will mark that box with an appropriate sign but you can't miss it.

An FTQ can be fairly difficult sometimes. We will try not to choose bizarre wires or concoct impossible-to-analyze situations. In any event, you are responsible for giving a complete account of impending faults in your circuit before the wire is pulled or the software program modified. If you mention that X and Y will go wrong, but only X goes wrong when the wire is pulled, your answer is incorrect. On the other hand, if you mention that X and Y will go wrong, and X and Y and Z actually go wrong, then your answer is also incorrect. In some cases, you may want to list contingencies: "If the input goes HIGH, then X will occur, but if the input goes LOW, Y will occur." This may be particularly important for CMOS circuits for which an uncommitted input is not in a well-defined state. Vague answers, like "the circuit will not work" or "it would take a scientist to figure it out" are not acceptable. Neither is going to lunch; once an FTQ is asked, you must answer it during the same session. Any interruption in the FTQ process between a question and an answer will be recorded as a question failure. You may not break off a losing streak of questions without leaving your breadboard and a record of the missed questions with the TA for passing on to the next TA who takes up the questioning. You may only break off such a streak for good cause, and ignorance is not a good cause. Be sure you understand your system before you ask for an FTQ. The TA may pass you on to his or her successor if there is a shift change during your questioning.

It is the privilege of the TA to choose an appropriate FTQ. If you feel that you have been given an unfair question, first try to work out an answer. If you fail the question, you may bring your complaint to me. If I feel your complaint is justified, you will be asked a single replacement question; otherwise you will be referred back to the original TA who will ask the normal two-question FTQ follow-up.

Because an FTQ may be non-trivial, take a reasonable amount of time to answer a question. Allocate *at least* fifteen minutes to this process. Do not let the atmosphere of the lab make you anxious - getting the first question correct can save you a lot of time. We expect that over the course of the semester you will spend from 2 to 4 hours answering FTQs.

#### In Summary:

• Generally perform the following steps to have a standard lab recorded:

- 1. Show the TA a neat schematic of the lab, and explain its operation.

- a. For programmable labs, similarly share the code/block diagram.

- 2. Exhibit the operation of the circuit to show that it meets all requirements.

- 3. Have the TA check your board number.

- 4. Answer an FTQ of the TA's choosing.

- a. For each unsuccessful FTQ answer, you must answer two more FTQs.

- b. FTQs must be answered completely and correctly, and cannot be delayed without good cause.

- 5. Have the TA sign your scorecard, and record the completion in the excel sheet.

- A TA may check off only 5 of your labs.

- Academic honesty is taken very seriously, in both designing and building the circuits and in taking and reporting data.

#### 2.5. Documentation

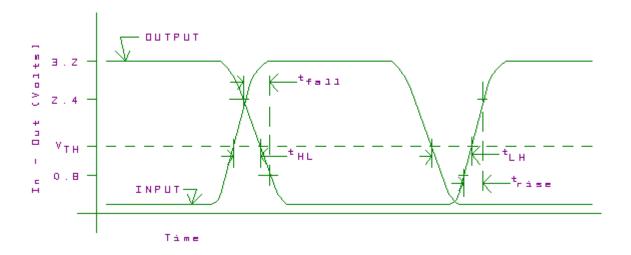

Proper documentation is an essential aspect of the design process; I expect you to get in the habit of specifying your circuit completely while you are devising and building it. Circuit diagrams, written circuit descriptions, timing diagrams, truth tables, etc., are the counterparts in hardware design to the documentation of computer programs which is so much a part of satisfactory programming. To encourage good habits in this area, we are requiring a carefully done schematic for one lab you have completed. (You may not hand in documentation for a lab that does not work! We may reject a schematic for a bad design even though you may have gotten it past a TA. For example, some people carefully adjust components to get a poor design to work for a while. That may fool a TA sometimes, but it may not fool the one - very likely me - who grades a stack of schematics.) The schematic must be done using the *DxDesigner* computer aided design (CAD) package. You must also use the same tool to generate a Bill of Materials for the circuit including adding information on the particular parts in the circuit at the level of commercial availability. See section 9.5 for the full set of requirements. We may even require redrawing if your schematic has a poor esthetic layout even if the interconnections are correctly expressed. Please see section 11.2 for information on timing diagrams for lab 9 and section 11.3 for further information on how *DxDesigner* works.

Also, you cannot expect much professorial or TA help with a non-working breadboard unless your working drawings are reasonably complete and legible. The TAs have been instructed *not* to answer questions about circuits unless they see a reasonable amount of documentation and to require a schematic as part of the evaluation process.

# 2.6. Deadlines

Many years ago, I experimented with deadlines for general groups of labs. As a result of its success in retaining the sanity of both students and TAs during the course, I continue the tradition. The lab groups, and associated completion dates, are:

Group one:

Labs 0 through 3 may be checked off only until October 8, 2014.

# Group two:

Labs 4 through 9 may be checked only until November 19, 2014.

# *Group three:*

Labs A and B and the schematic diagram requirement may be checked off only until December 5, 2014.

You may obtain credit for the labs within each group *only* up to the posted date. (Note that labs may be completed as soon as you wish, but they must be completed by the given enpumpkination date.) The last week before the final exam will be a grace period. During this week, you may have up to one additional lab from each group checked off.

Labs C through E may be checked off at any time until the last day of the semester, the day of the final exam. This year the ENGN1630 exam is on the morning of Thursday, Dec. 18, 2014. I will allow labs to be checked off until the Saturday after the exam since that is the latest that grades can be integrated before I have grades due. However, keep in mind that **TA assistance and availability for FTQ's decreases during exam period** for the obvious reason.

The completion groups were instituted for several reasons. First, ENGN1630 is allocated a fixed amount of lab space, a small number of TAs, and a finite amount of circuit testing, trouble-shooting, and demonstrating equipment. It has been our experience that most people (including me!) tend to procrastinate when not confronted with fixed deadlines. Without deadlines, some students fall hopelessly behind by the end of the semester.

A second compelling reason for the institution of the deadline approach, however, is that by concentrating on a group of labs in a given number of weeks, help sessions can be scheduled as necessary to assist those who appear to be having difficulty.

Note that students who thrive on the excitement generated by trying to complete the course at the last possible moment will especially appreciate and benefit from this deadline approach, since there are now four "last possible moments" to contend with instead of only one!

# 2.7. The ENGN1630 Exclusion Principle

For each day that the lab is open, **you may have only one lab signed off**. This will still allow ample time to complete as many labs as you wish - after all, the typical academic semester has at least 70 class days but only 15 or so labs have been defined for the entire course. The Exclusion Principle has two purposes: first, it prevents one individual from monopolizing TA time, and second, it provides more incentive for you to learn to work efficiently and steadily rather than in bursts. Deviations to this policy will not be considered. Please note that this has implications for how much you can hope to get done in the end-of-semester grace period.

#### 2.8. Lab Schedule

The ENGN1630 lab will be in Giancarlo room 196, the Hewlett Electronics Laboratory. It will be open every day except Saturday while the University is in session. Use the door nearest the ramp out of the building as its electric lock will be unlatched. Please do not leave the other door open or unlocked. TAs will be available for some 35 plus hours a week including at least two evenings during the week, probably Wednesday and Thursday.

We will try to keep TA schedules posted in the lab and on the web, telling when each TA will be available for troubleshooting help and for checking off labs. No TA will be assigned to work when class is in session. Also, although we will try to keep most lab slots staffed with at least one TA, there will undoubtedly be times when the lab has a TA scheduled but he or she does not turn up. The TAs have job interviews and other personal obligations and while I ask them to arrange for substitutes, this is not always practical. Do not schedule yourself so tightly that you miss getting a lab signed off because a TA overslept. The responsibility for getting labs checked off in a timely fashion is yours, not the TA's.

You are encouraged to come to the lab at times when the crowd is small (such as 9 AM) you will get more attention and have shorter waits for lab sign-offs.

#### 2.9. Teacher Evaluation

Besides my obligation to evaluate you, you will have an opportunity to evaluate me at the end of the semester. The School of Engineering arranges for web-based evaluations of teaching. The results are used for class assignment, salary adjustment, and (occasionally) tenure review. Some of the evaluation is designed to measure whether I have met the course goals for ABET. (Those goals are listed on the handout you receive the first day of class.) Finally, I distribute forms for the *Critical Review*. I take these reviews, both for the School and for the *Critical Review*, quite seriously, and would appreciate your doing the same. (By the way, I do not read any of them until after the final exam. The Dean's office retains all forms and tabulations until after exams are over and grades are submitted.)

#### 2.10. Collaboration

Unlike some courses, you are welcome to collaborate with your fellow students during the semester. Discussing problems with a friend is a good way to troubleshoot your circuit, and can be a source of self-improvement for both of you. Be sure that you completely understand any advice offered by anyone, however, since this advice may be wrong - providing even more frustration than the original problem that you yourself devised. Make sure that you will not be stumped on an FTQ and doing this will help with exams too.

In general, two kinds of collaboration can be distinguished: *soft collaboration* and *hard collaboration*. Soft collaboration is a perfectly acceptable process of seeking and offering advice on the design of a particular lab solution. We assume that you will understand any advice given, and hence will benefit from the information exchange. Note that while you may get design help from a

friend, you must use your own kit to construct the solution, you must generate your own documentation, you must be ready to explain your system with understanding, and you must answer your own FTQ.

Hard collaboration means the use of another person's circuit board, wiring or documentation during your FTQ. It also encompasses blind copying of another's design without sufficient understanding to pass the FTQ process. In labs requiring computer files, you must generate your own files individually, making your own choice of variable names, comment records, indentation, etc. All the data and reports for labs 2 and 6 and the schematic must be done individually. I will take a very dim view of nearly identical reports or duplicate data. If you copy something from another source as part of an explanation in your report, such as a figure or paragraph from Wikipedia, you must show explicit attribution in a footnote with appropriate bibliographic citation. (For the material in these labs, you really should be capable of writing the explanations yourself.) Copying is hard collaboration! None of the forms of hard collaboration will be tolerated. If you feel compelled to use a friend's design for a given lab challenge, you must at least go through the process of making your own schematic from scratch not by Xeroxing, wiring up the solution (including going through the computer entry process for CPLD or FPGA designs), and debugging it yourself! All the wiring and troubleshooting associated with lab challenges must be performed on the circuit boards issued to you at the beginning of the semester. TAs will be required to match the numbers found on your scorecard with those on the back of your boards. If you are found using someone else's board, you will automatically lose credit for the lab you are trying to demonstrate. (If this occurs during one of the labs required to pass, you cannot possibly pass the course.) You may also get your friend in trouble for loaning his or her boards. You may be referred to the appropriate Dean for action by the Academic Code Committee and will probably receive a grade of NC for the course. Penalties for tampering with someone else's board or kit will be dealt with even more stringently.

Improper collaboration, besides wasting the thousands of dollars you pay for taking this course, is a serious matter and will not be tolerated.

#### 3. Getting Started

You will receive your own chip set along with this lab manual. Look over Lab 0, work out a solution on paper and test it conceptually until you are convinced it will work. Then assemble and test it. Be especially careful about connections to the power supply. The easiest way to damage a chip is to get the power supply connections backwards. The +5 volt supply lead must go to the VCC lead of each device, and the ground or 5 volt return lead must go to the GND pin of each device. If you are using LVTTL parts, be careful not to apply an overvoltage. Failure to be careful may result in wholesale damage to your chips. We realize that some of your chips may be defective as a result of prior use (unusual but possible), but we will not replace components damaged by carelessness without some charge. Another point to be especially careful about is not to connect the output of a chip to +5 volts or even worse connect any pin of a logic chip to plus or minus 12 or minus five volts. These voltages are available on the supplies and may get used in labs 7 or 8. (Chips usually are more tolerant of outputs accidentally connected to ground.) In the labs that use the CPLDs, which is half the labs and most of the required one, you must program the device before you connect it to other wiring. We have special cables on the power supplies so

you can program the XC9572XL. Then turn off the power supply, wait a moment for the supply voltage to disappear, remove the power cable and substitute your cable.

**Hot-swapping cables can damage CPLDs too.** Always turn the power off and wait a few seconds before removing a cable to the CPLD board and never connect the cable with the power supply turned on.

**Nota Bene:** Massive destruction of chips or melted or burnt areas on protoboards or keypads will result in appropriate adjustments to the **price at which we will buy back your kit.** Your keypads are mechanically very robust, but they can be ruined easily by using them to short out the power supply, *i.e.*, to connect VCC to GND. This melts the plastic film under the buttons, causing them to stick. **You must use limiting or pull-up resistors** with the keypad. We are not sympathetic to damaged keypads.

When you are sure the circuit works properly, find a TA, demonstrate it, explain it, and answer an FTQ. With this signoff, you are well underway! Remember the deadline system, and remember that the lab gets busier and the challenges harder as the semester progresses.

If Lab 0 has you baffled, if you do not know who Herr Georg Ohm was (and why he is remembered -- his lab equipment is carefully and reverently preserved in the Deutsches Museum in Munich), if you do not know the difference between voltage and ground or capacitance and resistance, do not despair. The graduate TAs and I want to be helpful and can explain a lot if asked. Throughout the course you will have every opportunity to have your fears explained away; your responsibility is to take advantage of the help available.

#### 4. Circuit Construction Guidelines

#### 4.1. General Hints

Be a little compulsive. Organize the components in your chip set so that you do not waste time looking through the entire lot each time you need a particular chip. If you sort them in numerical order, you will easily find any part you need. The black foam that holds your kit chips is static resistant and a place of safe storage. If you want to store them in other materials, you should lay down a piece of aluminum foil to press onto the pins of the CMOS chips; this will short their pins together and prevent the chip from being destroyed by high-voltage static electricity. (CMOS parts including CPLDs are the most vulnerable parts, but TTL parts can be damaged too. The foam we use for kits is pretty good without aluminum foil, but be careful if you substitute other materials.)

Another suggestion is to make a set 3x5 index cards that summarize the pin connections and logical functions of each of the chips in your Kit. This may cost a bit of time now, but it will save time in the long run. These cards will serve as handy references on how each chip behaves, and will allow you to avoid leafing through your lab manual each time you need to know how the chip works (especially during the answering of FTQ's!). The automated form of this is to make use of the *DxDesigner* libraries and draw everything on-line. If you don't want to do index cards or look through the back of the manual, you can find the full data sheets on the class web site.

In general, you should start a lab challenge by working through the requirements of each subcircuit. Construct truth tables, if appropriate, showing the relationships among the various inputs and outputs of your system. Try to decompose one large problem into several smaller **problems**, keeping in mind the limitations of your chip selection and the need to integrate each of the pieces into a whole. Once you understand what needs to be done, work out a complete penciland-paper solution. Simulate the circuit by hand to see what happens during various combinations of inputs. Make sure that most of your logic errors are caught while you are still working in a pencil-and-paper mode; it is easier to erase a connection than to fix a circuit. You may wish to use DxDesigner to turn your hand sketch into a full schematic. This will help with accuracy of pin assignments, with finding missing signals, and with legibility. The DxDesigner software offers a design rule checker that finds outputs connected together, single pin nets, misnamed nets, etc. Further testing by simulation at the design stage is standard practice and is much recommended for the Xilinx-based designs. With practice, the time to draw and simulate a circuit is short enough that it is completely offset by the time saved in construction and debug. Remember that neat drawings help you work out ideas and build things with minimum errors. Per the comments above, this effort will also guarantee better help from TAs or from me.

After designing a solution, build your circuit gradually. Isolated sub-sections of the design can then be tested apart from the rest of the solution. If your circuit evolves in a step-wise manner, you will be able to understand its operation better, and you will be less likely to be baffled by a hard FTQ.

When you assemble your circuit, do it neatly with wires that are not so long that they rise above the breadboard in a confused mass. Make sure that only a minimum of bare wire is exposed throughout your circuit; this will cut down on intermittent problems that result from improper insulation. **Do not make wires so short** that they loop tightly over the top of individual chips, however, since this will prevent you from exchanging a chip if it fails. (This also prevents testing it or attaching a logic analyzer to it if you *suspect* it has failed. Logic analyzer connections are usually made with a clip that fits over the chip. Wires over the chip prevent doing this.) The CPLD board has a special connector to make connections to the logic analyzer. Assigning pins to make that connection give a proper analyzer display can help too. For example, if you have a bus, order the bits so they go high to low when displayed on the analyzer since that is the only format the analyzer will display.

When you wire a circuit, use a consistent color-coding scheme. For example, make all +5v lines red, all ground lines brown (or any other Earth tone, for that matter), etc. To aid in trouble-shooting, use a variety of wire colors throughout your circuit so that co-located wires can be easily distinguished. For parallel lines of information (busses) you may want to use wire colors corresponding to the resistor color code.<sup>1</sup>

# 4.2. The 163 Lab Environment

Besides being the place where your circuits will be tested by TA's, room 196 is where you can go to use a power supply, scope and logic analyzer for troubleshooting, to talk with fellow students about the lab challenges, and generally to bask in a high-tech atmosphere. Do not, however,

<sup>&</sup>lt;sup>1</sup> The resistor color code is a series of color and digit assignments. See the back of the data sheet section of this manual for the code's definition.

make a nuisance of yourself! No loud social gatherings; no smoking; no drugs; no food fights or practical jokes. Observe normal lab courtesy. Turn off equipment when you are done. Return all wires and cables to their normal places. Clean up little wires or scraps of paper. Do not remove anything from the lab (except your lab kit) without permission. If you break something, or notice something is broken, notify a TA.

Check the whiteboards for the latest news concerning the course. If there is a change in the lecture schedule, or if some particularly useful lab information is discovered (such as the opening or closing of the lab at non-standard times), it will be posted there and on the class web-site.

For some labs, you will want to use an oscilloscope to monitor rapidly changing voltages. If you do not know how to use one, please ask a TA. He or she can explain time bases, vertical calibration, triggering, dual trace operation and other features. Because TAs are only a year ahead of you, they may not know all the details. The manuals for scopes are on the class website -- be persistent. Please be careful when using the scopes – be especially cautious with the probes. These probes are easy to damage. Similarly the logic analyzers have delicate probes that need care in handling. There are a number of manuals in the lab for the analyzers that discuss the instruments in detail. Check the drawers in the back of the room. We do have a good supply of leads and clips, and you shouldn't have to jury rig everything. Ask the TAs to get more leads from me if the supply is getting low.

There are 16 PCs on the workbenches in the lab to support the labs and they run from the same server and SAN that the Computing Facility uses. There is software on the computers that will remove anything that you leave on the C:\ drive and some directories on the D:\ drive. Use the space allocated for you on the U:\ drive.

If you are unfamiliar with any other pieces of equipment in the lab, ask a TA for assistance.

# 4.3. Logic Probes

Most of the power supplies are equipped with logic probes that can quickly tell you the voltage levels of any point in your circuit. The LOW LED is on for voltages less than 0.8v; the HIGH LED is on the voltages greater than 2.4v. If the logic probe measures voltages between 1.0v and 2.2v (or if it is unconnected) no lights will glow. A third LED will light if the probe detects a pulse train.

# 4.4. Power Supplies

Room 196 has approximately twelve digital test stations. The heart of each of these stations is the power supply. To activate your circuit, connect a wire from the +5v terminal or from the -5v or +3.3v terminal as appropriate to the appropriate slot on your breadboard and a wire from the ground terminal to your ground pins. Always double check that you have the proper polarity of power *before* turning on your circuit. **Reversing the power supply leads could damage all of the chips on your breadboard!**

For your own reasons, you may wish to avoid the bustling atmosphere of the 163 lab and instead test your circuits in the privacy of your own room. The advantages of this approach are that you will be able to control the noise level around you, and you will also (presumably) be able to control the size of the crowd waiting in line for you to finish. The disadvantages of this approach are that there will typically be no TA to offer advice, and that an alternate source of 5 volt power is necessary. There are a number of solutions to this latter problem.

Because supply voltage fluctuations cause circuits to malfunction and because TTL circuits draw large currents, any approach based on batteries is a marginal solution to your problem. The parts for a simple power supply can be purchased from Radio Shack for about \$20. If you are interested in building one, I can give you a circuit diagram and some guidance on how to do it. For more money, it is possible to purchase a fully assembled 5v power supply that will deliver 1 or more amps of current. For example, a 5v/5A supply with auxiliary +-12-15v outputs costs under \$40.

# 4.5. Bypassing

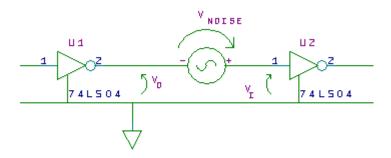

No power supply is perfect in the sense that a constant potential difference of exactly +5v is present between every pair of connections to VCC and GND on every extension of every wire of the power-to-ground system. The relative immunity of digital systems to extraneous potential variations (noise!) is a major reason for the ubiquity and power of digital logic, but that immunity is not infinite. Because of small series resistances and inductances associated with the power supply and its wiring, noise, that is, transient current spikes generated by pulse circuits or by TTL gates changing state, can cause voltage changes on the power wiring and make your logic circuits malfunction. Sequential circuits -- counters, flip-flops, etc. -- are especially sensitive. Other noise may come from equipment turned off and on somewhere else in the lab or from the 60 cycle magnetic field noise generated by fluorescent lights, or from *reflections* of signals sent over long wires in your circuit. (In fact, a major subdiscipline has grown up around designing out problems with power and signal distribution. It goes by the name of signal integrity analysis and design.)

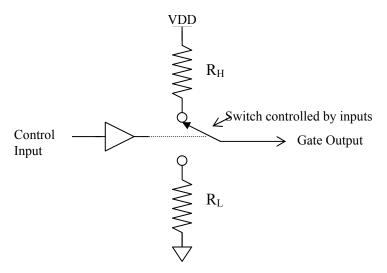

To protect your circuit from transient voltage spikes on the power supply lines, you can "bypass" or "decouple" the power supply by placing capacitors directly from power to ground at key places in your circuit. Key places are typically clock pulse generating or clock pulse receiving chips, such as oscillators, multivibrators, counters, flip flops or other state machines. You have several 0.1μF capacitors among your parts that can be used for bypass. More are available if necessary. Because it takes an appreciable amount of charge to change the voltage across such a capacitor, these will divert some of the current causing voltage transients. **Be aware of the possibility of bypass problems when troubleshooting your circuits!** If a counter seems to skips values or a flip-flop changes state for no logical reason, a bypass capacitor from VCC to GND at that chip may be necessary. Please be aware too that the 74ACT04 chip may be a source of extra noise and may require its own bypass capacitor. All except the simplest labs require at least a couple of bypass capacitors. One other possibility to check when troubleshooting an erratic circuit is that the supply voltage **at the chips** may be less that the 4.75 volts required for proper operation. Measure it directly at the chip with a multimeter.

# 4.6. Debouncing

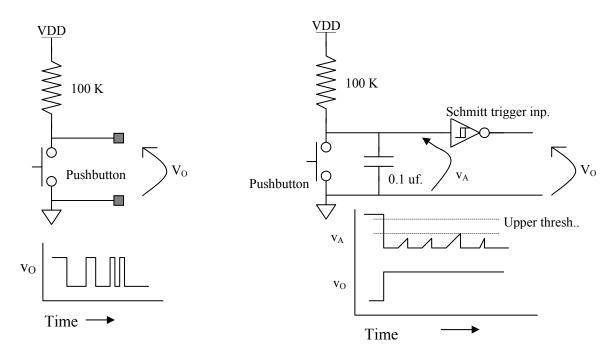

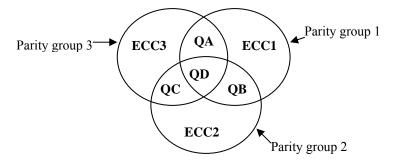

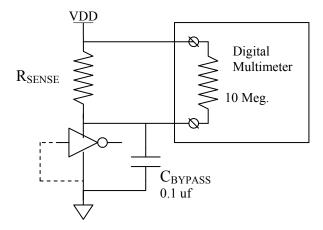

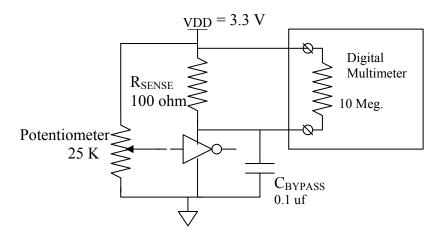

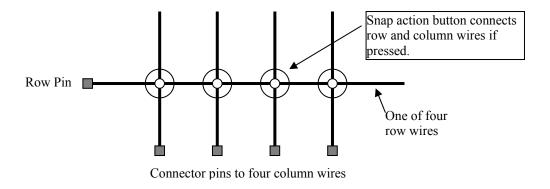

Mechanical switches, such as those on your keyboard, are another source of unwanted pulses. Suppose you press one of your keyboard buttons. Initially, the two internal wires are separated (or form an "open circuit"). Pressing the button will close the circuit, and cause contact between the two wires. Instead of making a single continuous contact, however, the two wires actually make several bouncing contacts on a microscopic scale of millisecond duration. Looking at the event with an oscilloscope you may see a series of pulses instead of the single pulse you desire. Figure I illustrates this problem and shows a method of *debouncing* a 2 wire push button.

Figure I: Debouncing a single-contact mechanical switch or button.

The solution idea here is similar to the solution of the bypass problem. Use a capacitor to absorb some of the current associated with the unwanted pulse activity. In Fig. I, we have a large resistance connected from the power supply to the gate of an inverter. If there is no other current at that logic gate input, the capacitor will remain charged to the power supply voltage. If the gate input is grounded, as it can be with the push of a button, the gate voltage will change immediately. If mechanical bounce occurs, and the contacts momentarily part, the capacitor will recharge with a time constant of about  $R \cdot C$ . The actual time this circuit takes from the opening of the switch contacts until the signal  $V_A$  crosses the inverter threshold depends on the type of inverter. In lab 2 you will find that TTL gates have substantial current flowing thru input terminals. These currents charge the capacitor faster than the resistor alone would. With 74LSxx series gates, C must be several microfarads to get a 10 ms. hold time. If the gate is a CMOS gate, then it usually has no steady input current. In that case, an RC time constant of 10 ms as in Fig Eq II would result in a hold time of 3 milliseconds. [The exact result is  $\Delta t = -R \cdot C \ln[(V_{CC} - V_{THG})/(V_{CC})]$ .] If, well before the 3 milliseconds elapse, mechanical contact is made again, the gate voltage will again drop to 0v and be kept below the threshold that causes a change of state for the gate. Thus, the output of the gate will remain low in spite of small changes going on at the input due to mechanical bounce. You may first encounter the need to put this theory into practice in Lab 4.

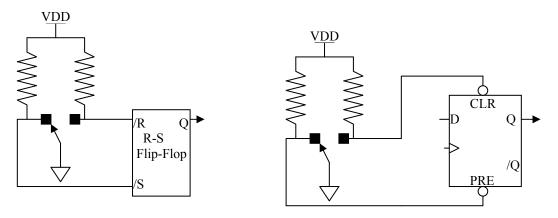

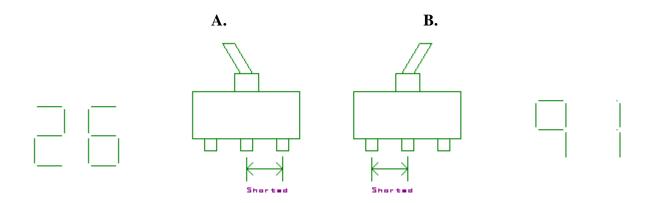

When the mechanical signal source is a switch instead of a pushbutton, an alternative method of debouncing the switch signal is available. Figure II shows two variants on the technique, one using the preset/clear lines on a flip-flop and the other using two NAND gates connected as an RS flip-flop. The idea is that the single pull double throw (SPDT) switch bounces on the make or break of the moving contact with either of the two stationary ones but does not bounce back and forth from the one to the other. The flip-flop responds to the first time each contact is made and ignores subsequent bounces until the other contact is closed again.

From your point of view, what we hope you will notice about the devices in your kit are the input currents, and the power versus frequency relations. One of the important results of the difference in input currents is that TTL devices have uncommitted inputs which are always high, while CMOS devices have undetermined values for uncommitted inputs. Also, this behavior and the high power supply noise of the newer CMOS parts can make them not interchangeable with TTL despite having nominally identical interface specifications. It is good construction practice never to leave an input floating; connect it to either VDD or GND. Good design tools will flag such open pins as errors during design checks. Also with your CMOS parts, as with the TTL parts, it is very important to bypass power connections.

Figure II: Using flip-flops to debounce an SPDT switch.

# 5. Design and Troubleshooting

# 5.1. Design

You may find that inspiration is not enough to keep you working on lab challenge designs. Develop a moderate weekly schedule for steady progress. Your goal could initially be to design or build a lab solution during each session, although later labs may require considerably more time and effort. Do not find out the hard way that necessity is not always the mother of invention, especially at 4:30 pm on the last day you can get a certain lab checked off. However well you organize your time, you may still be frustrated by problems. The problems will come from incomplete circuit design, sloppy construction, or unsystematic troubleshooting.

Design problems can be approached in one of two ways. First, you can wait for inspiration to strike. This may involve re-reading a lab challenge, and then taking a walk in the rain. (A

shower may be substituted on those occasions that the sun shines for several successive days in Providence.) At the end of your walk, you may have subconsciously thought about the problem enough to have a good first approximation for a solution. A second approach may be to sit down somewhere and think very hard about the nature of the problem and how it might be solved. You can read the recommended texts for the course. You could talk to friends. You might even pay attention during lecture! Another good approach might be to study the actions of various chips in your kit, and see if this provides a clue to how a problem may be solved.

Try to break the problem into several smaller ones. For example, if part of your assignment calls for a display, design and build the display portion of your circuit (being careful not to design yourself into a corner!). Seeing a portion of your assignment work may provide the incentive to explore other aspects of the challenge. Suppose you have tried to think of *some* solution for a couple of hours, and still are getting nowhere. Try (in the following order) these steps:

- 1) dreaming,

- 2) asking another student for help soft collaboration,

- 3) consulting a TA for a hint,

- 4) seeking an appointment with the professor,

- 5) going to the Emerald City for an appointment with the Wizard of Oz.

Help from step 4 is guaranteed to provide you with a basis for hope.

# 5.2. Troubleshooting

Suppose you have a design that, on paper, looks as if it should work and yet does not give proper outputs after you have hooked it up and tested it. Recheck your wiring. Are the power supply connections made properly? Are all the inputs to each gate accounted for? Do all of the outputs go somewhere? Next, check the power supply. Are you getting the proper voltage? Is the polarity correct? If the power supply has been reversed, all the chips in the circuit may be damaged. Is there an adequate number of bypass capacitors? Does one chip seem like the culprit? Take it out and test it by itself; you may have a defective chip that you should exchange for a good one. The CPLDs are very easy to damage! While we try to keep on top of replacing them, sometimes the class destroys them faster than we can keep up. Are you having problems with clock signals? Sometimes with a heavy load and poor wiring, the NE555 will give two clock edges at one nominal low to high or high to low transition. If there is a switch in the system, you may need to bypass or debounce its signal as described in the Construction Guidelines.

Use the logic analyzer to test activity at multiple pins simultaneously. (The analyzer is really not that hard to use and is very powerful in displaying the action of a system. Use it early and often rather than leaving the Logic Analyzer Challenge to the last possible moment.) There are clips in the lab that go over DIP integrated circuits and make it easy to connect the logic analyzer to all the pins at once. The CPLD and FPGA boards have logic analyzer plugs that connect 16 pins to the analyzer in one push. As of the start of labs, every logic analyzer has a plug that fits the ones on these boards and a second cable that has individual wires that can go on the DIP clips. In assigning pins of the CPLD to signals, lay them out to simplify the use of the analyzer, *e.g.*, if there is a bus, get the pin order correct for the order of bus signals to be correct on the analyzer display. If you have timing signals, sketch what you expect the timing waveforms to be and make sure that the

proper events happen in the correct sequence. (Remember that simulation can be part of your paper design and the comparison of what is predicted and what is measured is a wonderful diagnostic method.) You may want to single step through the states of your circuit. Examining timing waveforms with an oscilloscope, you may discover noise on a clock signal or discover a signal that does not meet the specifications for a HIGH or LOW. Particularly in labs that use sequential circuits, you should use the analyzer to see if one event is happening before or after it ought to according to your design. You may have to introduce or remove delays from your circuits. Don't be afraid to use the right tool even if it takes a little while to get used to it. You designed the circuit and ought to know the sequence of events it should display. Developing the ability to compare design to reality is the chief reason to require labs rather than doing everything in simulation.

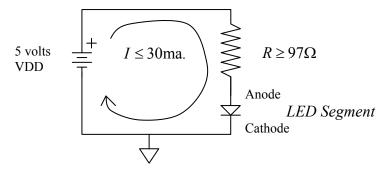

You may want to double-check interfaces between one kind of chip and another. For example, if you have an output from a gate driving an LED, the voltage across the LED in the HIGH state may be clamped lower than the HIGH logic levels required for other connections to that output. You need a resistor in series with that LED. Or, you may have a CMOS chip fanning out to too many TTL chips. Or, you may have a TTL chip unable to reach threshold voltage on a CMOS input. Is your problem intermittent? You may want to make sure that the wiring has been done in a neat manner. Wiggle the wires in their breadboard socket holes to make sure there are no inadvertent open circuits. Bare wires may cause unwanted short circuits. Do not hesitate to trim the ends of wires and strip them again as worn tin plate can lead to bad connections.

Let us suppose, however, that you have checked all these possibilities and your circuit still does not work. What should you do? The next thing to do is sleep on it. We are not talking about a Rip Van Winkle solution here - just overnight, or at most forget it for the weekend. You hope that a subconscious integration of the paradoxes and dilemmas of your case will lead to an intuitive insight - dream therapy, if you like!

Now suppose it is the next day, and the consolation of sleep did not help. Seek out the help of another student or a TA. You may know someone who has already done the lab or know a student from last year's 1630 course, or you may have a sympathetic friend to whom you can explain your situation out loud. Often giving such an explanation helps you realize the problem or the friend or TA may be able to spot an oversight. Of course, you will want to restrict your give-and-take with other students to "soft collaboration." Remember that any advice you get from anyone may be tested by the Fault Tolerance Question when you finally demonstrate your circuit!

One important requirement in talking to a TA (and probably to a friend too) is you must **be prepared with legible documentation**. (Sloppy documentation is very frustrating for both TAs and me. Do not try to transfer your frustration to one of us!) A TA may also set up some test, the results of which you both will study. She may want to swap a couple of replacement chips in and out. If she finds you have made a trivial error, she will point it out to you and you will be home free. If you are way off base though, the TA's are instructed not to give you a complete answer to your problem. The TA will suggest ideas that should help you do the design yourself. During this time you must keep in mind that the lab challenges are not simply homework problems that you are doing as practice for exams; the challenges are the primary basis of your grade itself, and as such, we and the TA's constrain ourselves not to spoon-feed solutions to you.

Suppose you take the ideas of the TA and attempt to implement them. You may modify your circuit; you may start over and build another one. But it is possible you will continue to fail. You are convinced the TA is a bozo. Things are worse now. You will have slipped to stage five frustration. Why might this be? The TA may not have understood your design, or may not have been willing to give you enough information for you to navigate out of your particular maze, or you may have simply been too depressed or anxious to appreciate the advice, or the TA may really be a bozo! You will now want to seek out a Professor for troubleshooting advice. I am always available after class. Also I am glad to answer questions if you find me in my office (Room 449) or labs (Rooms 195, 325 or 703). For more extended advice, make an appointment. When you do come, however, make sure that you come prepared with legible documentation of your design and have your circuit wired neatly. Be willing to describe your problem and the attempts you have made to solve it. I will try to understand your circuit enough to make a judgment about it. Be willing to endure a Socratic dialogue. I will tell you whether I think your design can work, and if I think it cannot, I will suggest some sort of redesign. Ask as many questions as you like. Do not leave until you feel at least a little optimistic that further work will be profitable. Remember that I cannot tell whether you understand something unless you tell me honestly if you do or don't. Don't try to hide your confusion when I say something mysterious. Make your feelings known if you think your progress has been halted entirely!

A final word on frustration: if the results of tests on your circuit indicate it, don't be afraid to acknowledge that you may have designed yourself into a dead end and that the best strategy may be to pull out all your wires and chips and start with a fresh idea. Engineers, who have become too enamored of a particular design that will never work, tend to become pretty bitter. They drift from anger to cynicism to apathy. They become blind to the faults of the circuit at hand. They view it as possessed by supernatural forces beyond the understanding of student logic. They kill time by watching movies like "The Exorcist" when all they really need is a good EXOR gate. In professional life such tendencies are a devastating handicap.

This advice about frustration may seem silly as you proceed with the early labs. We hope the advice will still seem silly as you continue on, but experience indicates that this may not be the case. You should be aware that the later labs, particularly 7, 8, A, B, and C, may require much more attention to detail and knowledge of chips.

#### 6. Homework, Lectures, and Textbooks

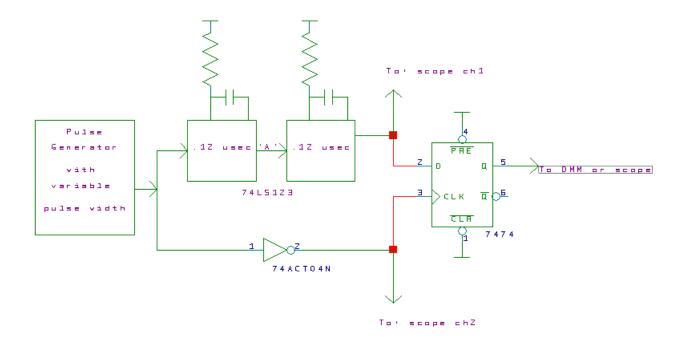

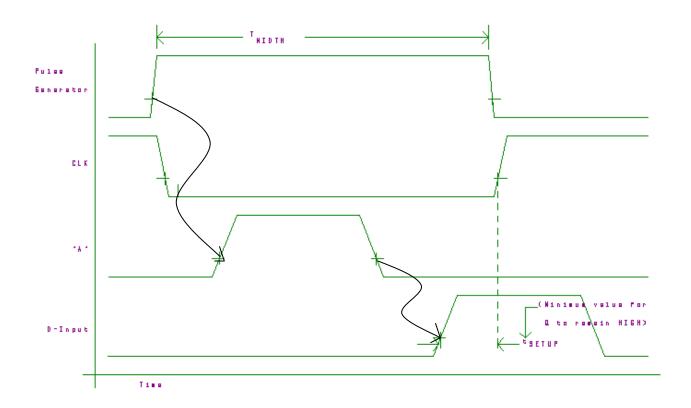

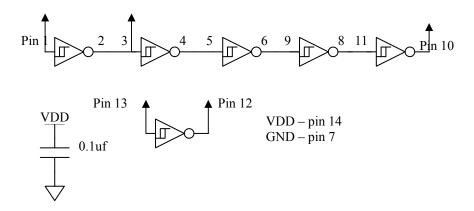

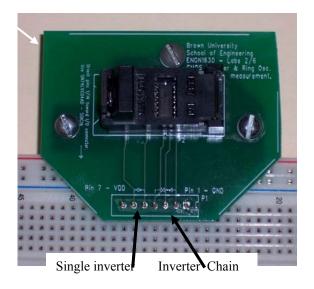

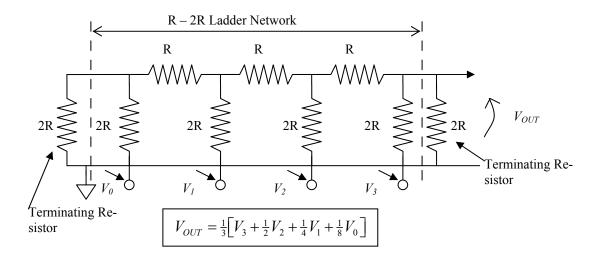

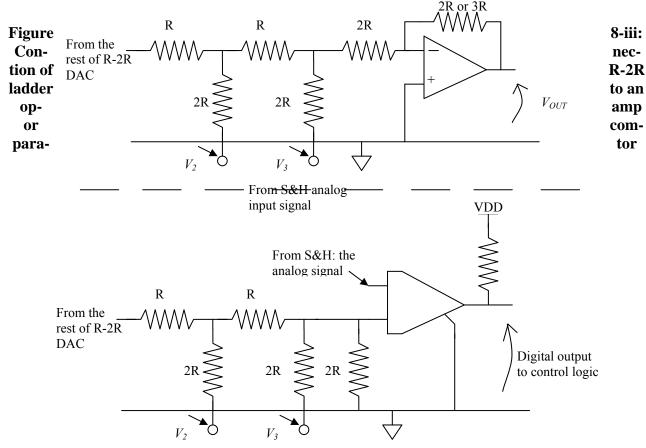

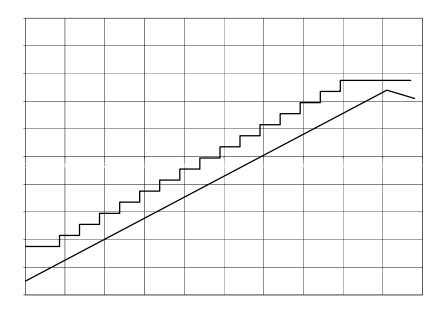

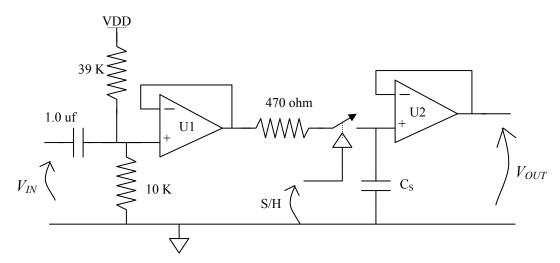

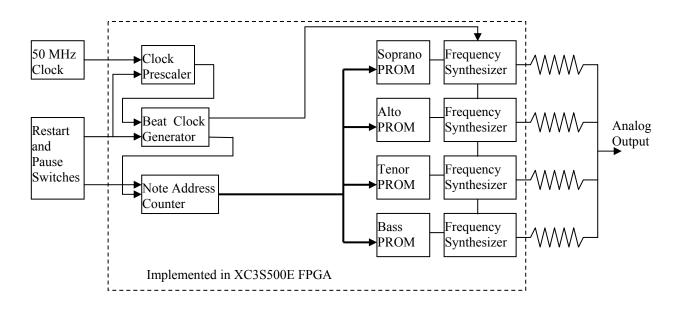

#### 6.1. Homework