# Latches, the D Flip-Flop & Counter Design

ECE 152A – Winter 2012

#### Brown and Vranesic

- 7 Flip-Flops, Registers, Counters and a Simple Processor

- 7.1 Basic Latch

- 7.2 Gated SR Latch

- 7.2.1 Gated SR Latch with NAND Gates

- 7.3 Gated D Latch

- □ 7.3.1 Effects of Propagation Delays

#### Brown and Vranesic (cont)

- 7 Flip-Flops, Registers, Counters and a Simple Processor (cont)

- 7.4 Master-Slave and Edge-Triggered D Flip-Flops

- □ 7.4.1 Master-Slave D Flip-Flop

- □ 7.4.2 Edge-Triggered D Flip-Flop

- □ 7.4.3 D Flip-Flop with Clear and Preset

- □ 7.4.4 Flip-Flop Timing Parameters (2<sup>nd</sup> edition)

#### Roth

11 Latches and Flip-Flops

- 11.1 Introduction

- 11.2 Set-Reset Latch

- 11.3 Gated D Latch

- 11.4 Edge-Triggered D Flip-Flop

#### Roth (cont)

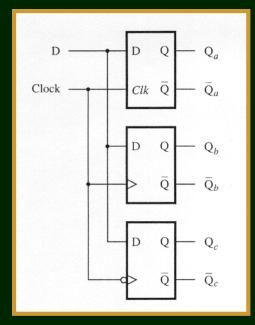

12 Registers and Counters

- 12.1 Registers and Register Transfers

- 12.2 Shift Registers

- 12.3 Design of Binary Counters

- 12.4 Counters for Other Sequences

## Combinational vs. Sequential Logic

#### Combinational logic

- Function of present inputs only

- Output is known if inputs (some or all) are known

#### Sequential logic

#### Function of past and present inputs

- Memory or "state"

- Output known if present input and present state are known

- Initial conditions often unknown (or undefined)

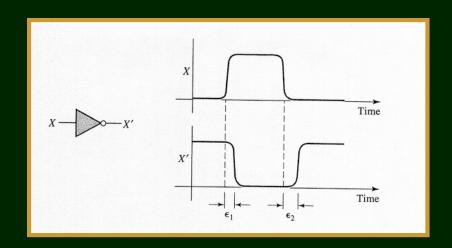

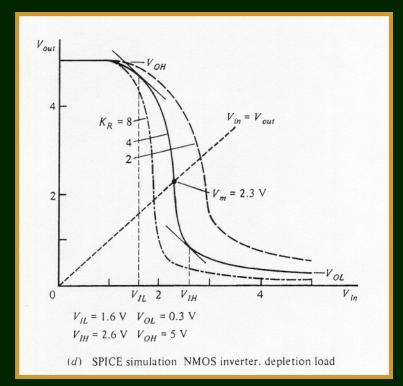

## Gate Delays

#### Recall from earlier lecture

When gate inputs change, outputs don't change instantaneously

#### Outputs connected to inputs

- Single inverter feedback

- If propagation delay is long enough, output will oscillate

If the propagation delay is not long enough, the output will settle somewhere in the middle

•

$$V_{in} = V_{out}$$

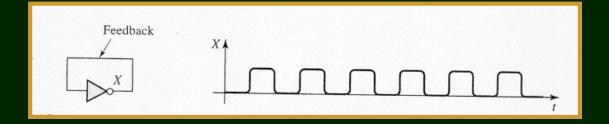

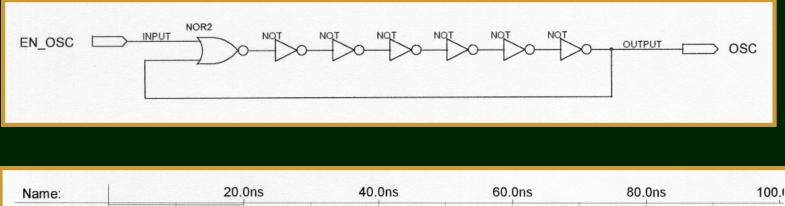

#### Ring Oscillator

- Any odd number of inverters will oscillate

- $\frac{1}{2}$  period = total prop delay of chain

| Name:                | 20.0115 | 40.0115 | 80.0HS | 80.005 | 100.1 |

|----------------------|---------|---------|--------|--------|-------|

| [I] EN_OSC<br>[O]OSC |         |         |        |        |       |

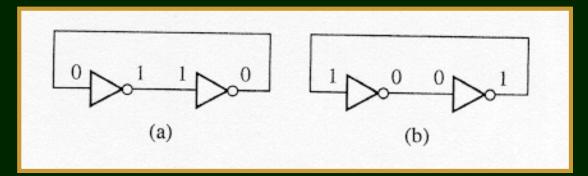

#### What about an even number of inversions?

- Two inverter feedback

- Memory (or State)

- Static 1 or 0 "stored" in memory

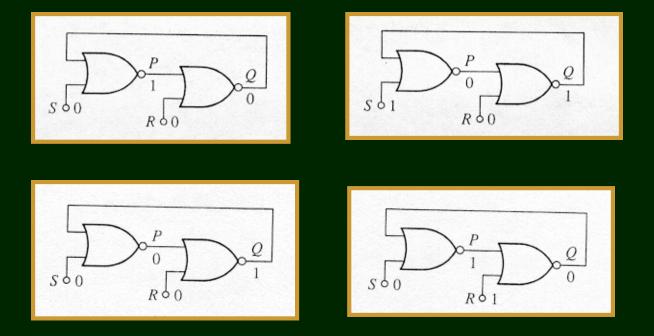

#### The Latch

#### Replace inverters with NOR gates

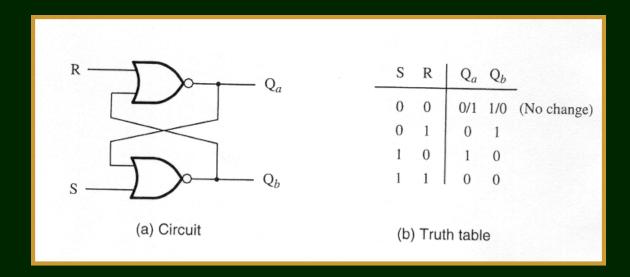

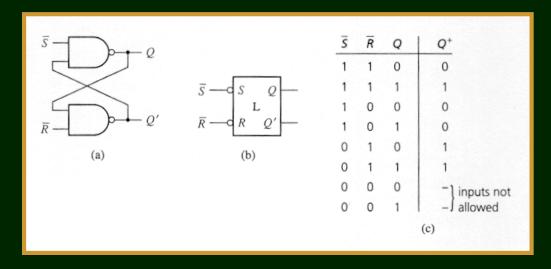

### The Set-Reset (SR) Latch

NOR implementationInverted feedback

February 6, 2012

#### The SR Latch

R = Reset (clear)

Q → 0, Q\* → 1

S = Set (preset)

Q → 1, Q\* → 0

NOR gate implementation

Either input = 1 forces an output to 0

Terminology

- Present state, Q

- Current value of Q and Q\*

- Next state, Q<sup>+</sup>

- Final value of Q and Q\* after input changes

#### Operation

- □ S=1, R=0 : set to 1, Q<sup>+</sup> = 1

- □ S=0, R=1 : reset to 0, Q<sup>+</sup> = 0

- □ S=0, R=0 : hold state,  $Q^+ = Q$

- □ S=1, R=1 : not allowed

- Q<sup>+</sup> = Q<sup>\*+</sup> = 0, lose state

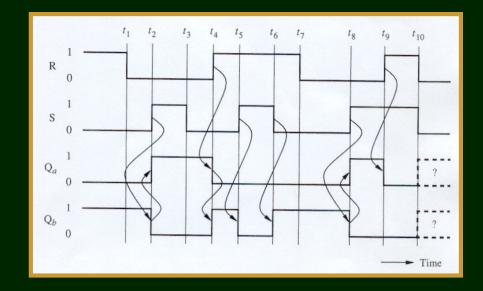

#### Timing Diagram

- RS inputs are "pulses"

- Temporarily high, but normally low

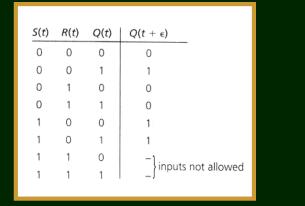

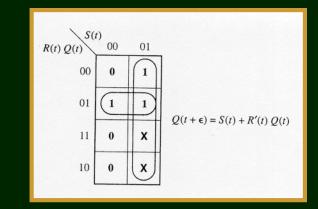

#### Characteristic Equation

- Algebraic expression of flip-flop behavior

- Plot characteristic table on map, find Q<sup>+</sup>

- $Q^+ = S + R'Q$  (S = R = 1 not allowed)

#### Characteristic Equation

- $\square$  Q<sup>+</sup> = S + R'Q (S = R = 1 not allowed)

- Q becomes 1 when S = 1, R = 0

- Stays Q when S = R = 0

- Q becomes 0 when S = 0, R = 1

#### State Table

NS (Q+) PS (Q) SR=00 01 10 11 Х 0 0 0 1 1 1 1 0 Х

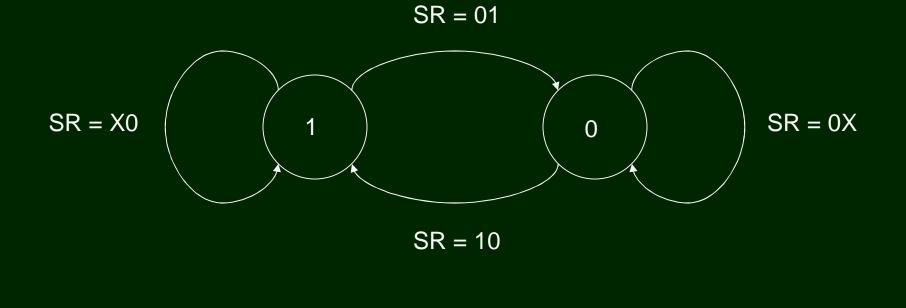

#### State Diagram

#### The SR Latch with NANDS

# NAND Based S'R' Latch S' = R' = 0 not allowed Either input = 0 forces output to 1

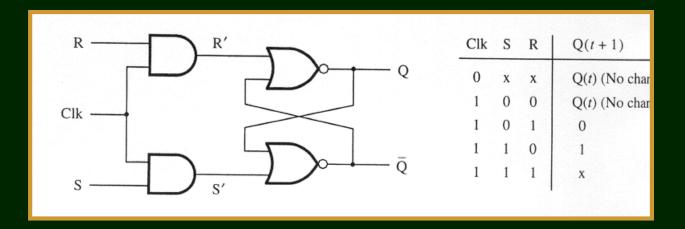

#### The Gated SR Latch

## Also known as "transparent" latch Output follows input (transparent) when enabled

## The Gated SR Latch (cont)

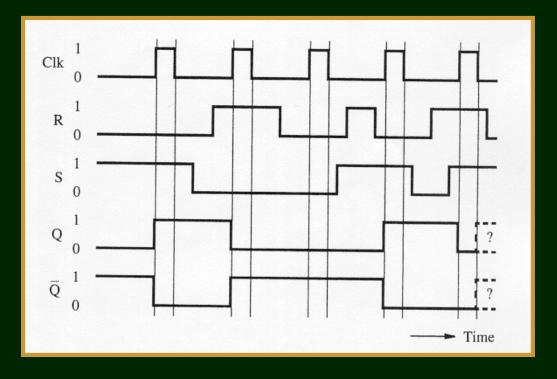

#### Timing Diagram

February 6, 2012

## The Gated SR Latch (cont)

#### NAND Implementation

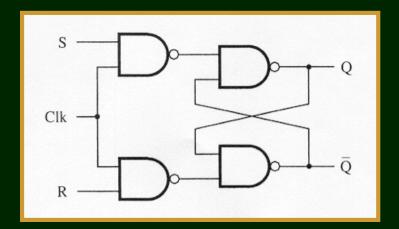

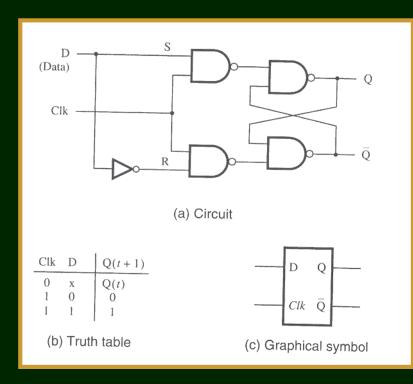

## The Gated Data (D) Latch

#### NAND Implementation of transparent D latch

## The Gated D Latch

#### Timing Diagram

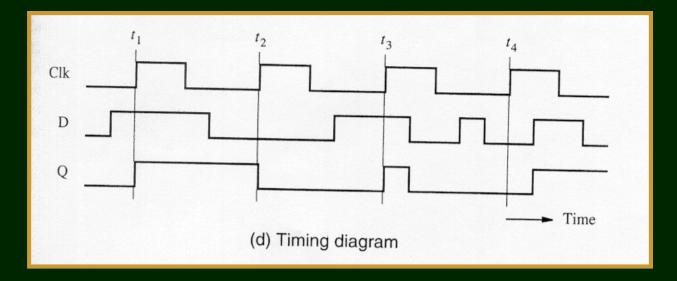

## The Edge Triggered D Flip-Flop

#### The D Flip-Flop

- Input D, latched and passed to Q on clock edge

- Rising edge triggered or falling edge triggered

- Characteristic table and function

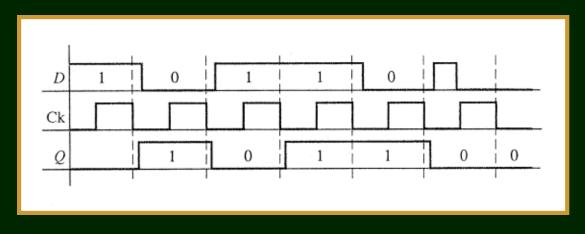

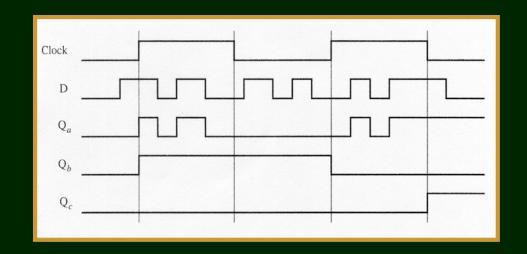

## The Edge Triggered D Flip-Flop

#### Most commonly used flip-flop

- Output follows input after clock edge

- Q and Q\* change only on clock edge

- Timing diagram for negative edge triggered flip-flop

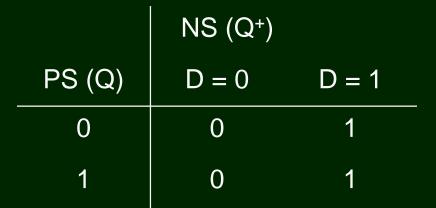

## The D Flip-Flop

#### State Table

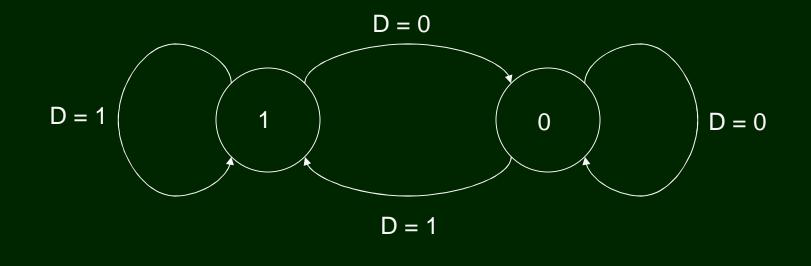

## The D Flip-Flop (cont)

#### State Diagram

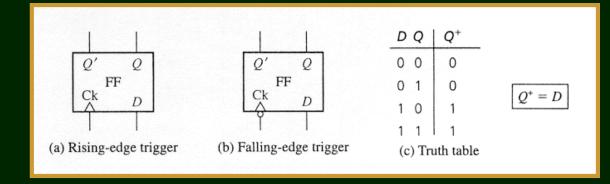

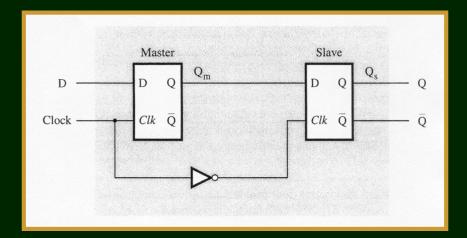

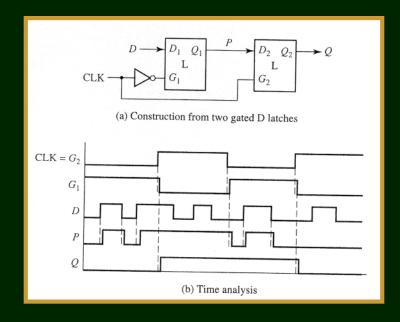

### The Master-Slave D Flip-Flop

- Construct edge triggered flip-flop from 2 transparent latches

Many other topologies for edge triggered flip-flops

- Falling edge triggered (below)

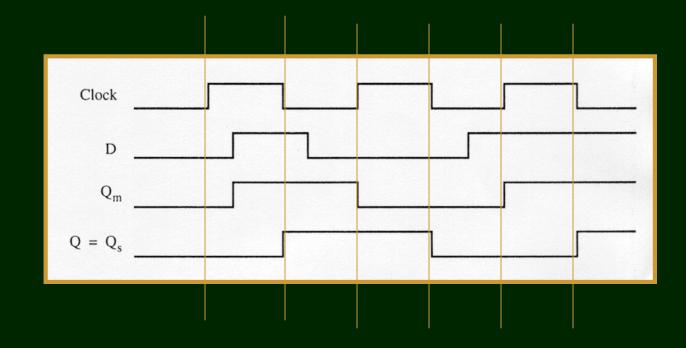

## The Master-Slave D Flip-Flop (cont)

# Timing Diagram Falling edge triggered

## The Master-Slave D Flip-Flop (cont)

# A Second Timing Diagram Rising edge triggered

February 6, 2012

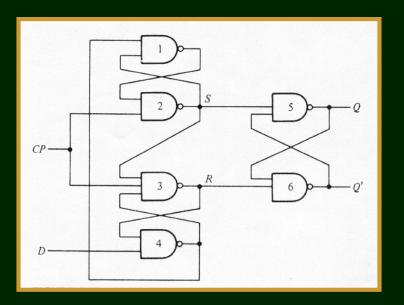

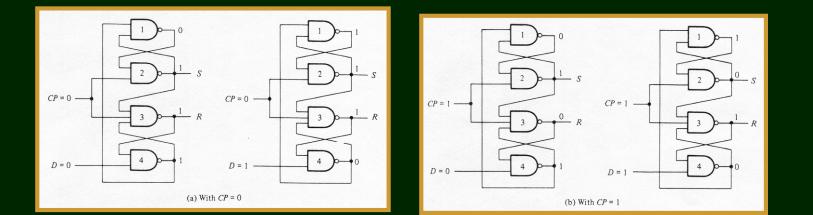

## The Edge Triggered D Flip-Flop

## "True" Edge Triggered D Flip-Flop Never transparent (unlike Master Slave)

## The Edge Triggered D Flip-Flop

#### Operation of Flip-Flop

## Types of D Flip-Flops

### Gated, Positive Edge and Negative Edge

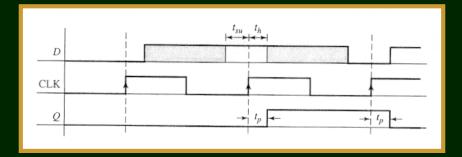

### **Timing Parameters**

#### $\Box \ \mathsf{CLK} \to \mathsf{Q}$

Delay from clock edge (CLK) to valid (Q, Q\*) output

#### • Setup time $t_{su}$

Stable, valid data (D) before clock edge (CLK)

#### $\Box$ Hold time $t_{hold}$

Stable, valid data (D) after clock edge (CLK)

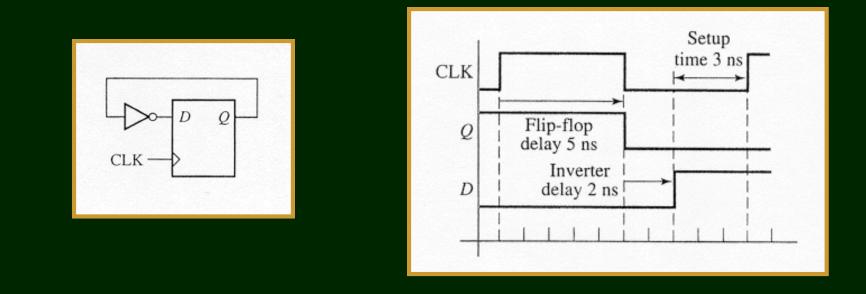

### Maximum Frequency

Maximum frequency (minimum clock period) for a digital system

CLK → Q + propagation delay + t<sub>su</sub>

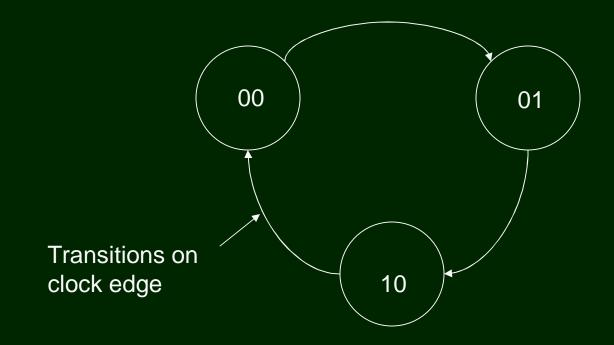

Design Example #1: Modulo 3 counter

00 → 01 → 10 ↓

↑ ← ← ← ← ←

Requires 2 flip-flops

One for each "state variable"

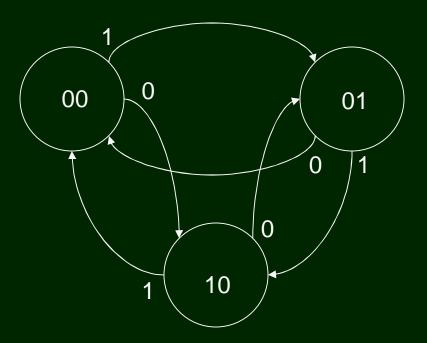

### State Diagram

### State Table

| PS |   | NS |    |

|----|---|----|----|

| А  | В | A+ | B+ |

| 0  | 0 | 0  | 1  |

| 0  | 1 | 1  | 0  |

| 1  | 0 | 0  | 0  |

| 1  | 1 | X  | Х  |

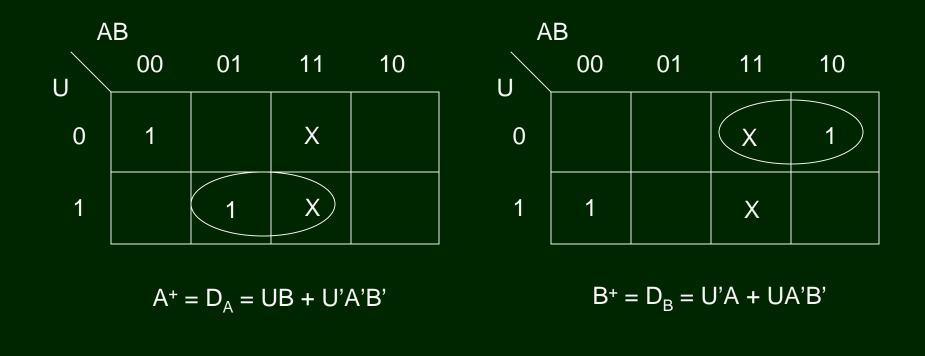

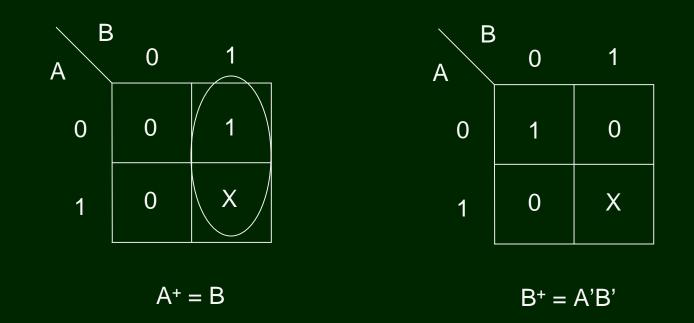

### Next State Maps

Implementation with D Flip-Flops

What are the D inputs to flip-flops A and B?

Recall characteristic equation for D flip-flop

- Q<sup>+</sup> = D

- Therefore,  $A^+ = B \longrightarrow D_A = B$

- and...  $B^+ = A'B' \rightarrow D_B = A'B'$

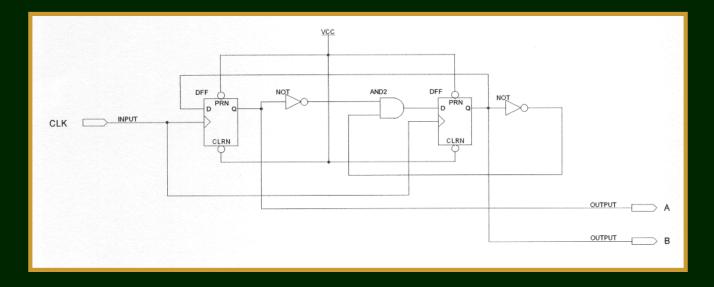

### Implementation with positive edge triggered flip-flops

February 6, 2012

Implementation with positive edge triggered flip-flops

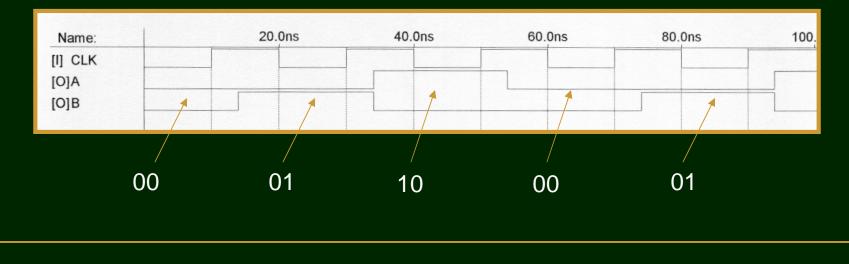

Timing diagram

### Design Example #2:

Modulo 3 counter with up/down\* input

- Counter counts up with input = 1 and down with input = 0

- Implement with D flip-flops

### State diagram

### State table

| U | А | В | A+ | B+ |

|---|---|---|----|----|

| 0 | 0 | 0 | 1  | 0  |

| 0 | 0 | 1 | 0  | 0  |

| 0 | 1 | 0 | 0  | 1  |

| 0 | 1 | 1 | Х  | Х  |

| 1 | 0 | 0 | 0  | 1  |

| 1 | 0 | 1 | 1  | 0  |

| 1 | 1 | 0 | 0  | 0  |

| 1 | 1 | 1 | Х  | Х  |

### Next state maps and flip-flop inputs