## Lecture 1 Overview of ASIC and FPGA Design

Alex Jones ECE 2120 Hardware Design Methodologies Fall 2007

1

| Grades                                                                                                                                                                                                                                                                                                                                                                      |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>Tentative Grading Schedule         <ul> <li>35% Homeworks and Labs</li> <li>35% Exams</li> <li>30% Project</li> </ul> </li> <li>Structure         <ul> <li>First Half of Class</li> <li>Homeworks/Mini Projects each week</li> <li>Individual Work</li> <li>Second Half</li> <li>Single Larger Project</li> <li>Teams of at least 2 depends</li> </ul> </li> </ul> |   |

| <ul> <li>Late Work will have minimum of 10% Penalty per day late.</li> <li>Not guaranteed to accept late work at all</li> </ul>                                                                                                                                                                                                                                             | 6 |

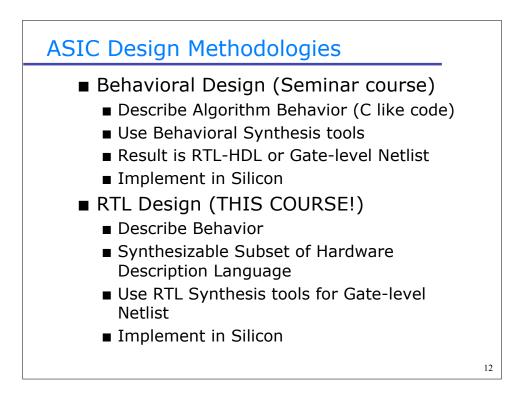

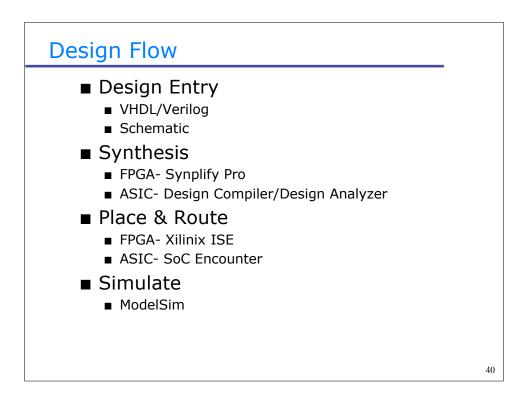

## ASIC Design Methodologies

- Gate Level Design (ECE 132/501)

- Implement Logic at Gate Level

- Schematic Editor (Mentor Graphics)

- Hardware Description Language (Gates)

- Logic Synthesis to Netlist

- Implement in Silicon

- Full Custom Layout (ECE 1192/2192)

- Design Logic at the Transistor Level

- Hierarchical Design

- Build Design from Bottom Up

- Connect Components Manually

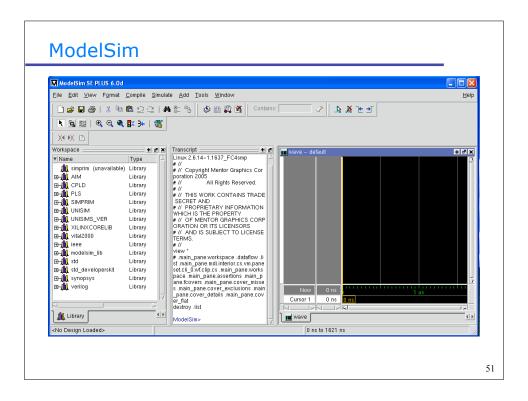

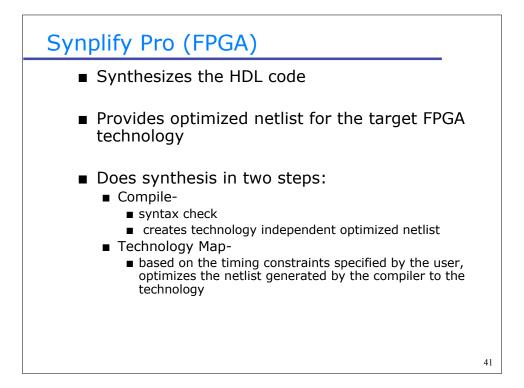

| Synplify Pr                                                                                                        | 0                                                                                                                           |                                                   |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                                                    | o <mark>jects koaded&gt;]</mark><br>ect Bun HIL Bralyst Options Bindow Web Help<br>Ø X Pa R ⊇ C   AA D   0 D   1 → F M    1 | X ⊂ .<br>× • :<br>♦ : : : : : : : : : : : : : : : |

| Open Project                                                                                                       | Run Synplify Pro®                                                                                                           |                                                   |

| Add File<br>Change File<br>New Impl<br>Impl Options<br>New P&R<br>View Log<br>- Frequency (Mhz)-<br>\$100<br>\$100 | <li>cload project&gt;</li>                                                                                                  | Run Directory: T                                  |

| Type ID                                                                                                            | Find: Find: Source                                                                                                          |                                                   |