## Lecture 12

- Process-induced Variations II: Systematic

- Lithographic Proximity Effect

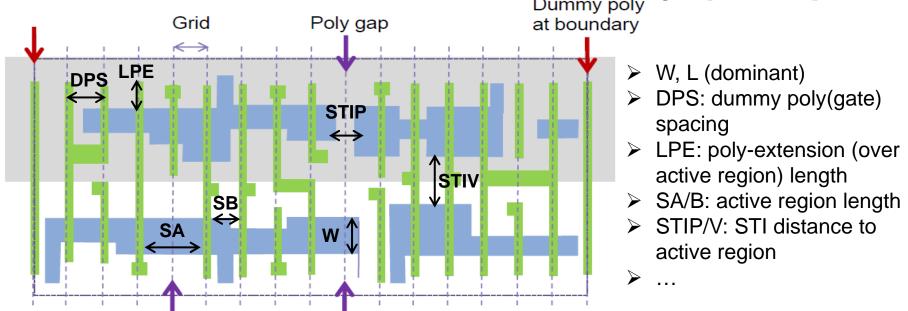

- Layout Dependent Strain

- Well Proximity Effect

**Reading**: multiple research articles (reference list at the end of this lecture)

# **Lithography Proximity Effect (LPE)**

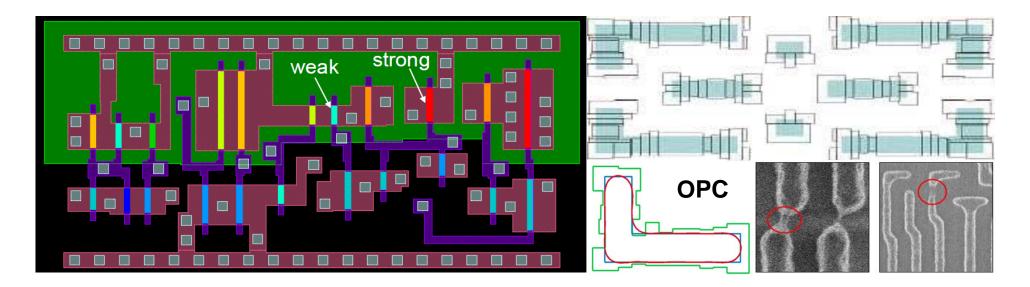

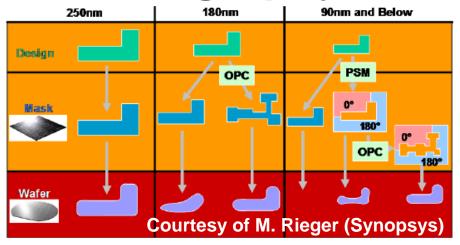

- Optical Proximity Correction (OPC) used to compensate for image errors due to diffraction effects by adding extra polygons to the pattern on the photomask

- Phase Shift Mask (PSM)

used to reduce the light interference by

changing the thickness of transmitting patterns

on the photomask (i.e. creating a phase shift

light)

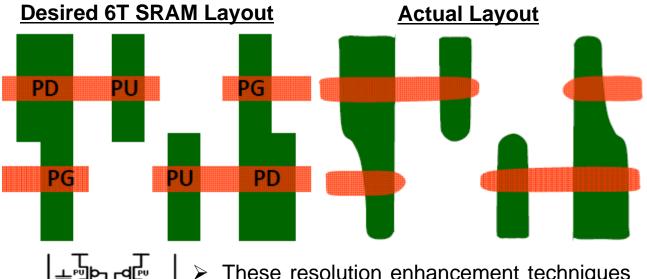

These resolution enhancement techniques help to reduce the pattern distortions, yet still end with round corners.

# Impact of Poly Corner Rounding: Gate-Extension Dependence

> Threshold voltage 0.35 0.30 SCE RSCE 0.25 STI ∑ 0.20 ∯ 0.15 0.10 → Vtlin 0.05 0.00 0.02 0.04 0.06 -0.02Poly gate PY0 [um] Average channel length increasing.

1.E-05

1.E-06

1.E-07

1.E-08

1.E-09

1.E-05

1.E-09

1.E-10

2.E-05

3.E-05

Ion [A]

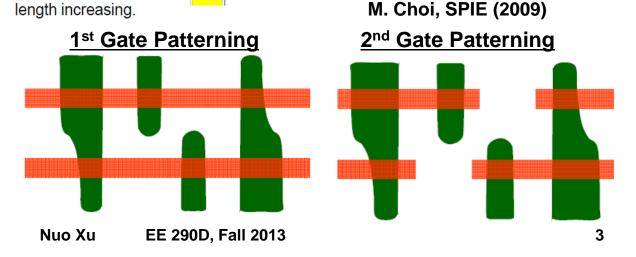

Poly corner rounding can be improved by using multiple patterning/exposure techniques.

11/6/2013

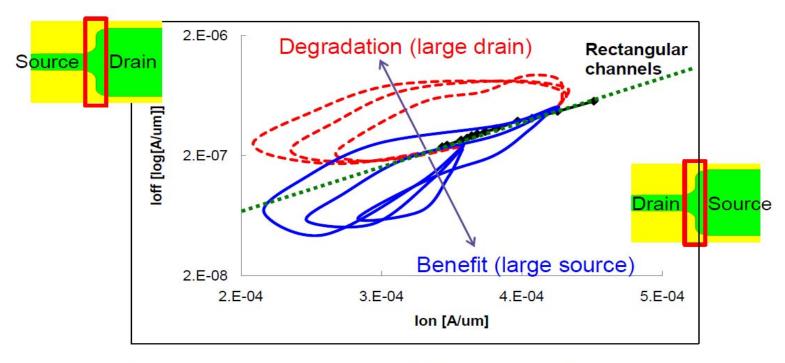

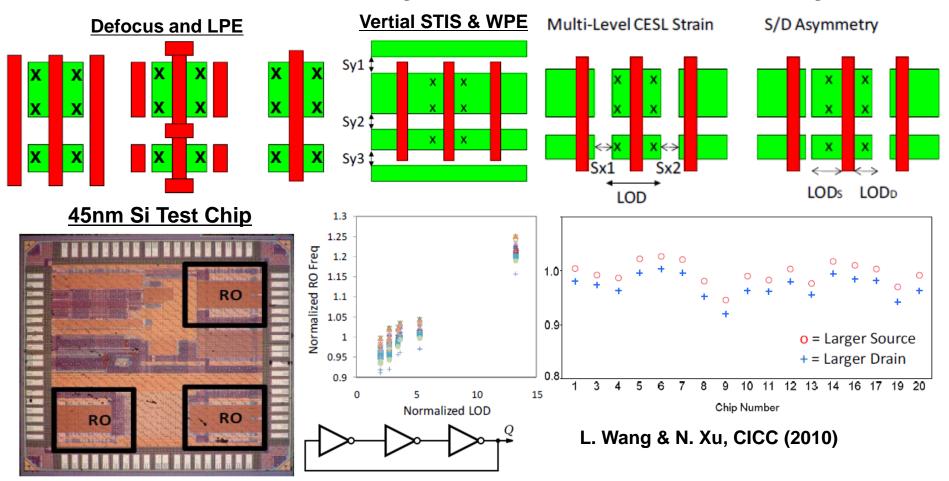

# Impact of Active Region Rounding: Asymmetric Source/Drain

- Large source structure provides better performance

- 10% Ion gain or 3x Ioff reduction

- Large drain structure degrades performance

- 50% Ion degradation or 3x Ioff leakage

M. Choi, SPIE (2009)

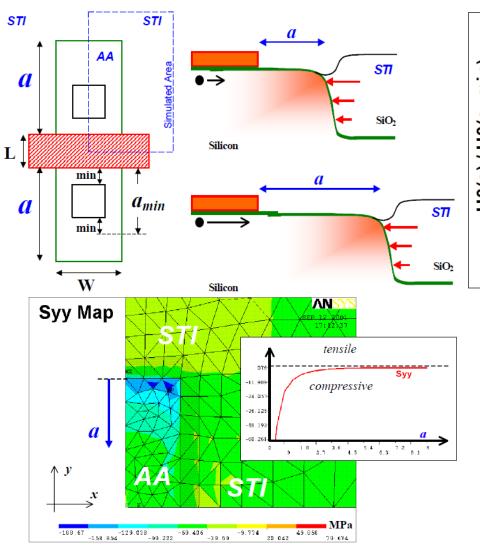

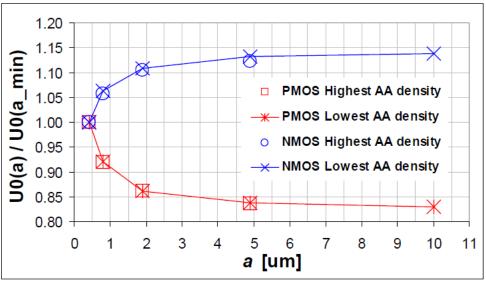

# **STI Proximity Effect**

- Due to the different thermal expansion coefficients between Si and STI, there exists <u>biaxial compressive</u> residual stress in the active region after processing.

- STI-stress generally increases PMOS current and decreases NMOS current.

- Stress relaxes exponentially with increased distance from Si/STI boundary.

R. A. Bianchi, IEDM (2002)

5

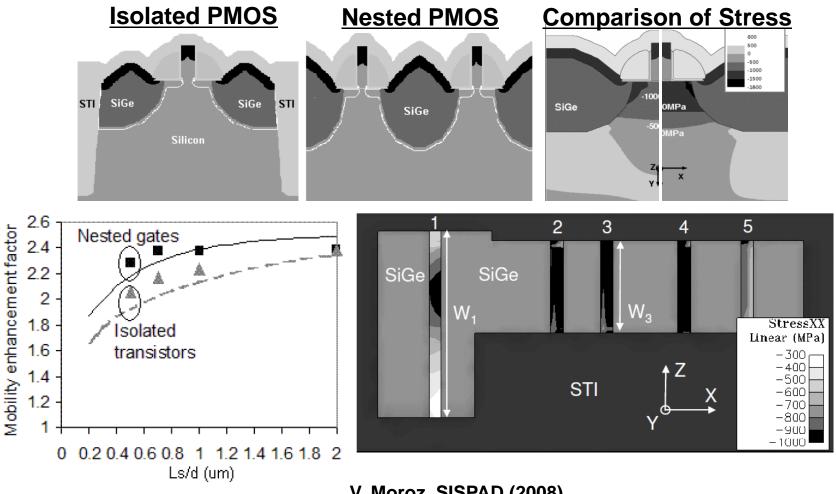

# **Layout Dependent Strain:** eSiGe Source/Drain

V. Moroz, SISPAD (2008)

11/6/2013 Nuo Xu EE 290D, Fall 2013 6

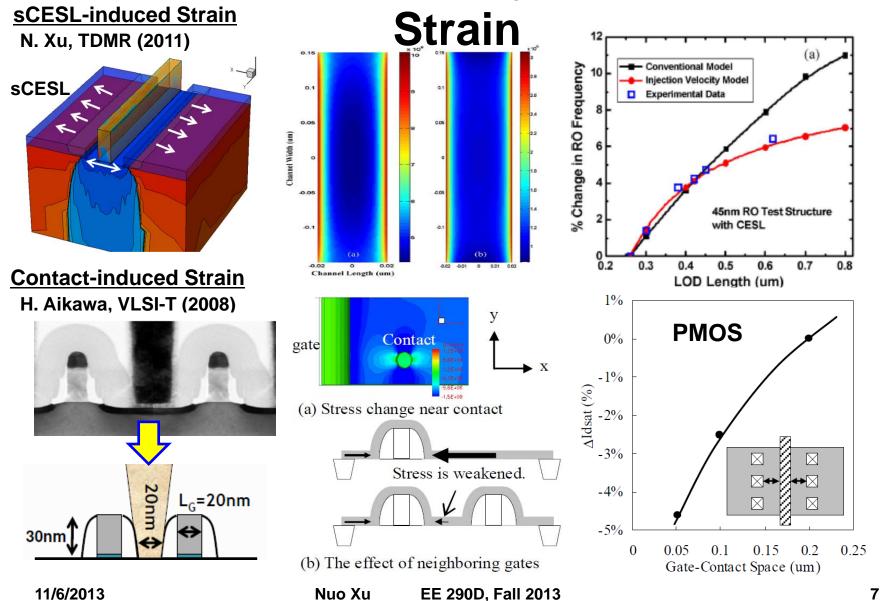

# Other Sources for Layout Dependent

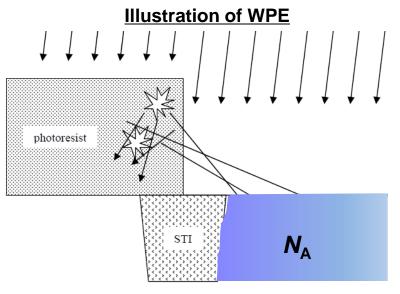

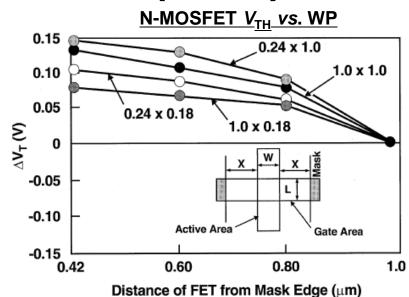

# Well Proximity Effect (WPE)

2-D WPE T.B. Hook, T-ED (2003)

- During ion implantation, kinetic ions scatter back out of PR and become embedded in the Si near PR edge, causing V<sub>TH</sub> shift.

- The affected distance is ~ 1um.

- Small angle II helps, but never avoids WPE.

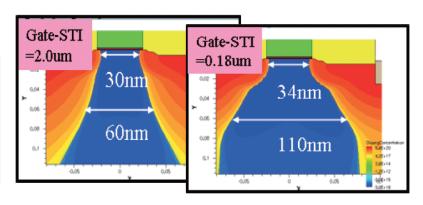

# **Another WPE: Stress-induced Enhanced/Retarded Diffusion**

H. Tsuno, VLSI-T (2007)

| Layout parameters | NFET |      |      | PFET |      |

|-------------------|------|------|------|------|------|

| shrinkage         | В    | As   | P    | В    | As   |

| Gate-STI          | -9%  | -17% | -34% | -23% | -43% |

| Gate space        | 1%   | 1%   | 3%   | 2%   | 4%   |

| STI width         | 4%   | 8%   | 15%  | 11%  | 18%  |

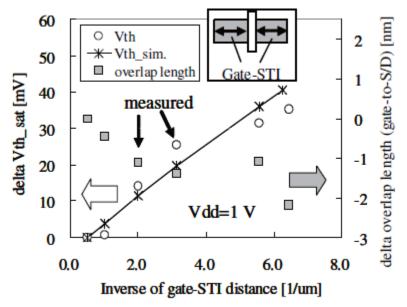

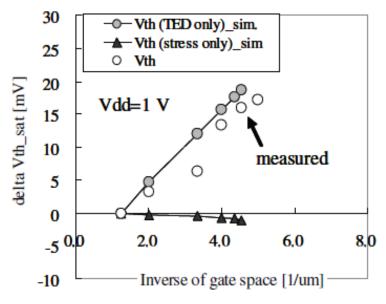

### N-MOSFET V<sub>TH</sub> Shift vs. Inverse of (1) STI-Gate Distance and (r)Gate Spacing

EE 290D, Fall 2013

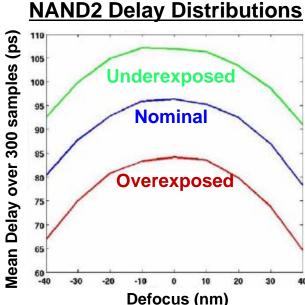

# Design for Manufacturability (DFM)

$$\mu = \mu_{ref} \frac{1 + K_{\mu} \left(\frac{1}{SA + L/2} + \frac{1}{SB + L/2}\right)}{1 + K_{\mu} \left(\frac{1}{SA_{ref} + L/2} + \frac{1}{SB_{ref} + L/2}\right)}$$

where

$$K_{V} = \frac{K_{VTO}}{1 + \frac{L_{KVTO}}{L^{LLODKVTO}} + \frac{W_{KVTO}}{W^{WLODKVTO}} + \frac{P_{KVTO}}{L^{LLODKVTO}W^{WLODKVTO}}$$

$$V_{TO} = V_{TO\,ref} + K_V \left( \frac{1}{SA + L/2} + \frac{1}{SB + L/2} - \frac{1}{SA_{ref} + L/2} - \frac{1}{SB_{ref} + L/2} \right)$$

where

$$K_V = \frac{K_{VTO}}{1 + \frac{L_{KVTO}}{L^{LLODKVTO}} + \frac{W_{KVTO}}{W^{WLODKVO}} + + \frac{P_{KVTO}}{L^{LLODKVTO}W^{WLODKVTO}}}$$

Compact modeling is the best solution to leverage between the accuracy and design complexity.

# **Monitors for Systematic Variability**

Ring oscillators (RO) and OFF-state transistors are often used to characterize transistors' performance and leakage.

11/6/2013 Nuo Xu EE 290D, Fall 2013 11

# Summary of Systematic Variability on Planar Bulk MOSFETs

| Layout Variation                             | Typical I <sub>on</sub><br>variation range | Typical V <sub>th</sub><br>variation range |

|----------------------------------------------|--------------------------------------------|--------------------------------------------|

| Length of diffusion (LOD) (SiGe or STI)      | ~30%                                       | ~50mV                                      |

| Spacing to adjacent diffusion                | ~5%                                        | $\sim \! \! 15 mV$                         |

| Active diffusion corners                     | ~5%                                        | ~15mV                                      |

| Poly spacing                                 | ~15%                                       | ~30mV                                      |

| Poly corner rounding                         | ~5%                                        | $\sim 20 \text{mV}$                        |

| Well boundary (WPE)/ Dual stress liner (DSL) | ~15%                                       | ~90mV                                      |

| Contact to gate distance                     | ~3%                                        | $\sim 10 mV$                               |

| delay(ps)<br>leakage power(nW) |           | no well prox | ximity model | using well proximity model |       |  |

|--------------------------------|-----------|--------------|--------------|----------------------------|-------|--|

| 25C/1.0V                       |           | value        | ratio        | value                      | ratio |  |

| inverter                       | cell rise | 27.98        | 1            | 30.12                      | 1.08  |  |

|                                | cell fall | 19.34        | 1            | 21.19                      | 1.10  |  |

|                                | leakage   | 4.654        | 1            | 2.448                      | 0.53  |  |

| NAND                           | cell rise | 31.18        | 1            | 33.34                      | 1.07  |  |

|                                | cell fall | 28.83        | 1            | 31.55                      | 1.09  |  |

|                                | leakage   | 5.095        | 1            | 3.007                      | 0.59  |  |

| NOR                            | cell rise | 55.67        | 1            | 59.88                      | 1.08  |  |

|                                | cell fall | 20.52        | 1            | 22.38                      | 1.09  |  |

|                                | leakage   | 10.107       | 1            | 6.222                      | 0.62  |  |

# impacts of different systematic variability sources Courtesy of X.-W. Lin (Synopsys)

Layout-dependent strain and WPE play the dominant role on transistor performance's drift.

# standard logic circuit performance shift w/ WPE Y.-M. Sheu, CICC (2005)

Small active-region area cells suffer more from systematic variability.

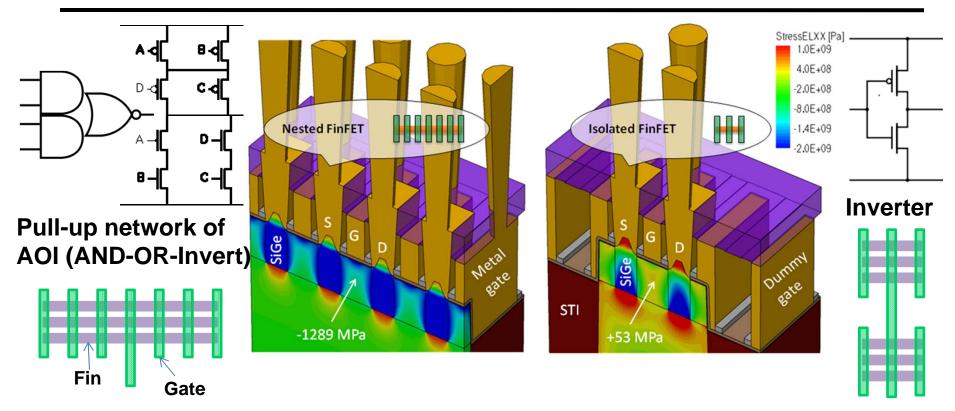

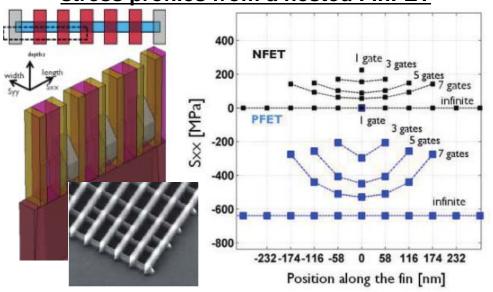

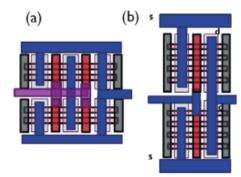

# Impact of Layout Dependent Strain on FinFETs

- Topologies of nested and isolated FinFET are unavoidable.

- Mobility of nested FinFET will be enhanced by ~80%.

- Stress of isolated FinFET is almost relaxed.

M. Choi, ISTDM (2012)

### **Strained FinFET Inverter Performance**

## stress profiles from a nested FinFET

### **CMOS** Inverter performance benchmark

| Inverter Layout |                | STI comp.<br>– I GPa | STI tensile<br>I GPa |  |

|-----------------|----------------|----------------------|----------------------|--|

| (a)             | 2 gates 2 fins | reference            | +6.15 %              |  |

| (b)             | I gate 4 fins  | - 4.69 %             | - 5.14 %             |  |

- PMOS stress (induced by eSiGe) boosts with fin length and # of gates per fin and degrades with increasing fin pitch.

- NMOS stress (induced by tensile STI) boosts with increasing fin pitch, and degrades with increasing # of gates per fin.

- For a CMOS invertor, the best configuration comes from a multiple-gate yet moderate fin-pitch design.

M. G. Bardon, VLSI-T (2013)

### References

- 1. T. B. Hook *et al.*, "Lateral Ion Implant Straggle and Mask Proximity Effect," *IEEE Transactions on Electron Devices*, vol.50, no.9, pp. 1946-1951, 2003.

- 2. R.A. Bianchi *et al.*, "Accurate Modeling of Trench Isolation Induced Mechanical Stress Effects on MOSFET Electrical Performance," *IEEE IEDM Tech. Dig.*, pp.117-120, 2002.

- 3. V. Moroz *et al.*, "The Impact of Layout on Stress-Enhanced Transistor Performance," *SISPAD Tech. Dig.*, pp.143-146, 2005.

- 4. N. Xu et al., "Physically based Modeling of Stress Induced Variation in Nanoscale Transistor Performance," *IEEE Transactions on Device and Material Reliability*, vol.11, no.3, pp. 378-386, 2011.

- 5. H. Aikawa *et al.*, "Variability Aware Modeling and Characterization in Standard Cell in 45nm CMOS with Stress Enhancement Technique," *Symp. VLSI Tech.*, pp.90-91, 2008.

- 6. H. Tsuno *et al.*, "Advanced Analysis and Modeling of MOSFET Characteristics Fluctuation Caused by Layout Variation," *Symp. VLSI Tech.*, pp.204-205, 2007.

- 7. L. T.-N. Wang *et al.*, "Parameter-Specific Ring Oscillator for Process Monitoring at the 45nm Node," *IEEE CICC Tech. Dig.*, 2010.

- 8. Y.-M. Sheu *et al.*, "Modeling Well Edge Proximity Effect on Highly-Scaled MOSFETs," *IEEE CICC Tech. Dig.*, 2005.

- 9. M. Choi et al., "14nm FinFET Stress Engineering with Epitaxial SiGe Source/Drain," International SiGe Technology and Device Meeting, Berkeley, CA, 2012.

- 10. M. G. Bardon *et al.*, "Layout induced Stress Effects in 14nm and 10nm FinFETs and their Impact on Performance," *Symp. VLSI Tech.Dig.*, pp. 114-115, 2013.