LMX2571

SNAS654A - MARCH 2015-REVISED JULY 2016

# LMX2571 Low-Power, High-Performance PLLatinum™ RF Synthesizer with FSK Modulation

#### **Features**

- Any Frequency from 10 MHz to 1344 MHz

- Low Phase Noise and Spurs

- 123 dBc/Hz at 12.5 kHz Offset at 480 MHz

- -145 dBc/Hz at 1 MHz Offset at 480 MHz

- Normalized PLL Noise Floor of –231 dBc/Hz

- Spurious Better Than –75 dBc/Hz

- New FastLock to Reduce Lock Time

- A Novel Technique to Remove Integer Boundary Spurs

- Integrated 5-V Charge Pump and Output Divider for External VCO Operation

- 2-, 4- and 8-Level or Arbitrary Level Direct Digital **FSK Modulation**

- One TX/RX Output or Two Fanout Outputs

- Crystal, XO or Differential Reference Clock Input

- Low Current Consumption

- 39-mA Typical Synthesizer Mode (Internal VCO)

- 9-mA Typical PLL Mode (External VCO)

- 24-Bit Fractional-N Delta Sigma Modulator

# 2 Applications

- Duplex Mode Digital Professional 2-Way Radio

- dPMR, DMR, PDT, P25 Phase I

- Low Power Radio Communication Systems

- Satcom Modem

- Wireless Microphone

- Propriety Wireless Connectivity

- Handheld Test and Measurement Equipment

# 3 Description

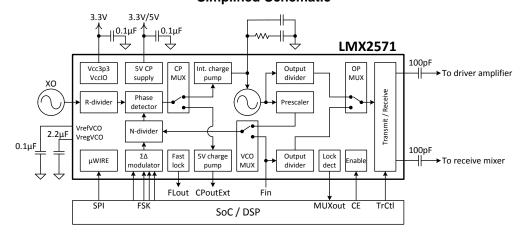

The LMX2571 is a low-power, high-performance, wideband PLLatinum™ RF synthesizer integrates a delta-sigma fractional N PLL, multiple core voltage-controlled oscillator (VCO), programmable output dividers and two output buffers. The VCO cores work up to 5.376 GHz resulting in continuous output frequency range of 10 MHz to 1344 MHz.

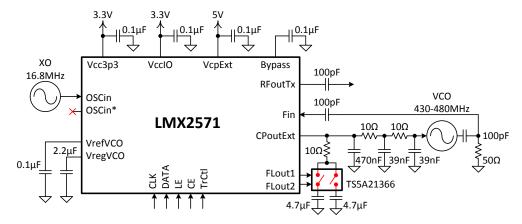

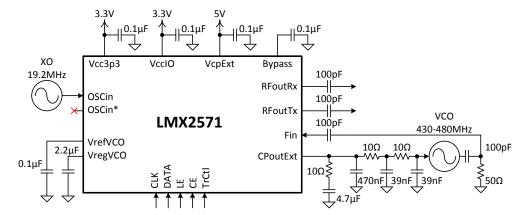

This synthesizer can also be used with an external VCO. To that end, a dedicated 5-V charge pump and an output divider are available for this configuration.

programmable multiplier incorporated to help improve spurs, allowing the system to use every channel even if it falls on an integer boundary.

The output has an integrated SPDT switch that can be used as a transmit/receive switch in FDD radio application. Both outputs can also be turned on to provide 2 outputs at the same time.

The LMX2571 supports direct digital FSK modulation through programming or pins. Discrete level FSK, pulse shaping FSK, and analog FM modulation are supported.

A new FastLock technique can be used allowing the user to step from one frequency to the next in less than 1.5 ms even when an external VCO is used with a narrow band loop filter.

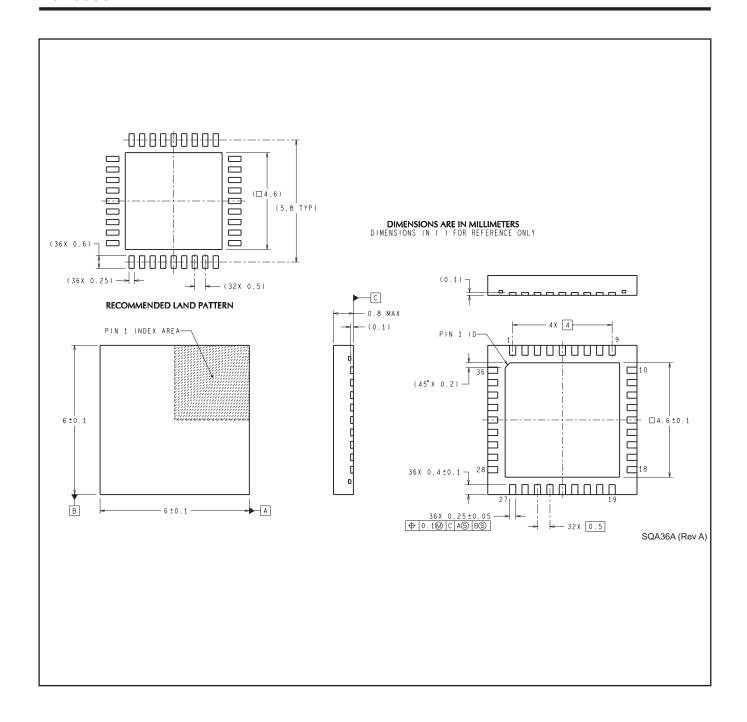

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LMX2571     | WQFN (36) | 6.00 mm × 6.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

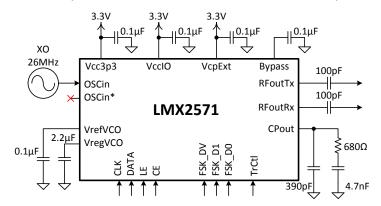

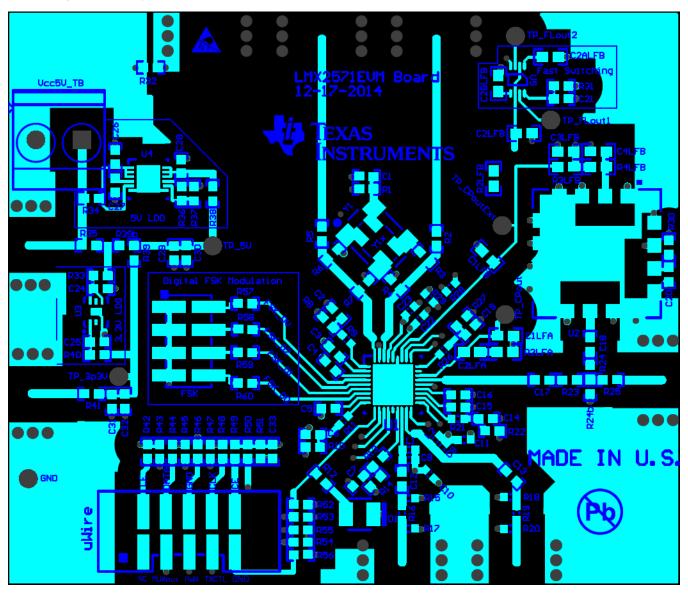

### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                             |    | 7.5 Programming                      |           |

|---|----------------------------------------|----|--------------------------------------|-----------|

| 2 | Applications 1                         |    | 7.6 Register Maps                    |           |

| 3 | Description 1                          | 8  | Application and Implementation       | 35        |

| 4 | Revision History2                      |    | 8.1 Application Information          | 35        |

| 5 | Pin Configuration and Functions        |    | 8.2 Typical Applications             | 44        |

| 6 | Specifications4                        |    | 8.3 Do's and Don'ts                  | 53        |

| ٠ | 6.1 Absolute Maximum Ratings           | 9  | Power Supply Recommendations         | 54        |

|   | 6.2 ESD Ratings                        | 10 | Layout                               | 55        |

|   | 6.3 Recommended Operating Conditions 4 |    | 10.1 Layout Guidelines               | 55        |

|   | 6.4 Thermal Information                |    | 10.2 Layout Example                  | 55        |

|   | 6.5 Electrical Characteristics         | 11 | Device and Documentation Support     | 56        |

|   | 6.6 Timing Requirements                |    | 11.1 Device Support                  | 56        |

|   | 6.7 Typical Characteristics            |    | 11.2 Documentation Support           | <u>56</u> |

| 7 | Detailed Description 10                |    | 11.3 Trademarks                      | 56        |

| - | 7.1 Overview 10                        |    | 11.4 Electrostatic Discharge Caution | 56        |

|   | 7.2 Functional Block Diagram           |    | 11.5 Glossary                        | 56        |

|   | 7.3 Feature Description                | 12 | Mechanical, Packaging, and Orderable |           |

|   | 7.4 Device Functional Modes            |    | Information                          | 56        |

# 4 Revision History

| Changes from Original (March 2015) to Revision A             |   |  |

|--------------------------------------------------------------|---|--|

| <ul> <li>Updated frequency for external VCO Mode.</li> </ul> | 5 |  |

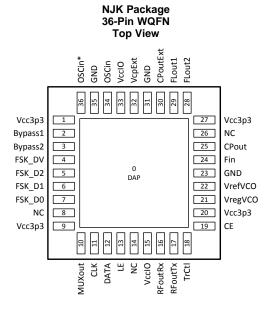

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN      |          |        |                                                                                                                |  |

|----------|----------|--------|----------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.      | TYPE   | DESCRIPTION                                                                                                    |  |

| Bypass1  | 2        | Bypass | Place a 100-nF capacitor to GND.                                                                               |  |

| Bypass2  | 3        | Bypass | Place a 100-nF capacitor to GND.                                                                               |  |

| CE       | 19       | Input  | Chip Enable input. Active HIGH powers on the device.                                                           |  |

| CLK      | 11       | Input  | MICROWIRE clock input.                                                                                         |  |

| CPout    | 25       | Output | Internal VCO charge pump access point to connect to a 2 <sup>nd</sup> order loop filter.                       |  |

| CPoutExt | 30       | Output | 5-V charge pump output used in PLL mode (external VCO).                                                        |  |

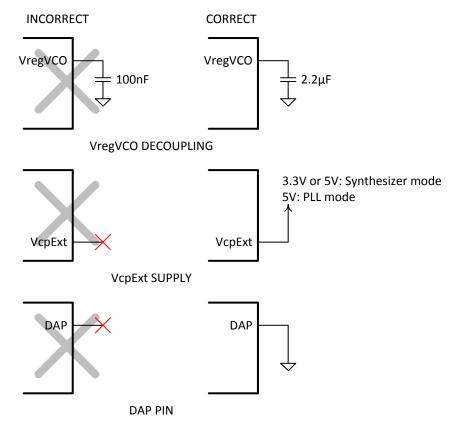

| DAP      | 0        | GND    | The DAP should be grounded.                                                                                    |  |

| DATA     | 12       | Input  | MICROWIRE serial data input.                                                                                   |  |

| Fin      | 24       | Input  | High frequency AC coupled input pin for an external VCO. Leave it open or AC coupled to GND if not being used. |  |

| FSK_D0   | 7        | Input  | SK data bit 0 (FSK PIN mode) / I2S FS input (FSK I2S mode).                                                    |  |

| FSK_D1   | 6        | Input  | K data bit 1 (FSK PIN mode) / I2S DATA input (FSK I2S mode).                                                   |  |

| FSK_D2   | 5        | Input  | FSK data bit 2 (FSK PIN mode).                                                                                 |  |

| FSK_DV   | 4        | Input  | FSK data valid input (FSK PIN mode) / I2S CLK input (FSK I2S mode).                                            |  |

| FLout1   | 29       | Output | FastLock output control 1 for external switch. Output is HIGH when F1 is selected.                             |  |

| FLout2   | 28       | Output | FastLock output control 2 for external switch. Output is HIGH when F2 is selected.                             |  |

| GND      | 23       | GND    | VCO ground.                                                                                                    |  |

| GND      | 31       | GND    | Charge pump ground.                                                                                            |  |

| GND      | 35       | GND    | OSCin ground.                                                                                                  |  |

| LE       | 13       | Input  | MICROWIRE latch enable input.                                                                                  |  |

| MUXout   | 10       | Output | Multiplexed output that can be assigned to lock detect or readback serial data output.                         |  |

| NC       | 8,14, 26 | NC     | Do not connect these pins.                                                                                     |  |

| OSCin    | 34       | Input  | Reference clock input.                                                                                         |  |

| OSCin*   | 36       | Input  | Complementary reference clock input.                                                                           |  |

| RFoutRx  | 16       | Output | RF output used to drive receive mixer. Selectable open drain or push-pull output.                              |  |

| RFoutTx  | 17       | Output | RF output used to drive transmit signal. Selectable open drain or push-pull output.                            |  |

| TrCtl    | 18       | Input  | Transmit/Receive control. This pin controls the RF output port and the output frequency selection.             |  |

#### Pin Functions (continued)

| PIN     | PIN             |        | DESCRIPTION                                                                                                               |

|---------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.             | ITPE   | DESCRIPTION                                                                                                               |

| Vcc3p3  | 1, 9, 20,<br>27 | Supply | Connect to 3.3-V supply.                                                                                                  |

| VccIO   | 15, 33          | Supply | Supply for digital logic interface. Connect to 3.3-V supply.                                                              |

| VcpExt  | 32              | Supply | Supply for 5-V charge pump. Connect to 5-V supply in PLL mode. Connect to either 3.3-V or 5-V supply in synthesizer mode. |

| VrefVCO | CO 22 Bypass    |        | LDO output. Place a 100-nF capacitor to GND.                                                                              |

| VregVCO | 21              | Bypass | Bias circuitry for the VCO. Place a 2.2-µF capacitor to GND.                                                              |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                            | MIN  | MAX                   | UNIT |

|------------------|----------------------------|------|-----------------------|------|

| $V_{CC}$         | Power supply voltage       | -0.3 | 3.6                   | V    |

| V <sub>IO</sub>  | IO supply voltage          | -0.3 | 3.6                   | V    |

| V <sub>IN</sub>  | IO input voltage           |      | V <sub>CC</sub> + 0.3 | V    |

| $V_{CP}$         | Charge pump supply voltage |      | 5.25                  | V    |

| TJ               | Junction temperature       |      | 150                   | °C   |

| T <sub>STG</sub> | Storage temperature        | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                           |                                                                     | VALUE | UNIT |

|--------------------|---------------------------|---------------------------------------------------------------------|-------|------|

|                    |                           | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1500 |      |

| V <sub>(ESD)</sub> | ) Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                            |                                 | MIN             | NOM MAX         | UNIT |

|-----------------|----------------------------|---------------------------------|-----------------|-----------------|------|

| $V_{CC}$        |                            |                                 | 3.15            | 3.45            | V    |

| $V_{IO}$        | IO supply voltage          |                                 |                 | V <sub>CC</sub> | V    |

| \/              | Charge pump supply voltage | PLL mode (external VCO)         |                 | 5               | V    |

| V <sub>CP</sub> |                            | Synthesizer mode (internal VCO) | V <sub>CC</sub> | 5               |      |

| T <sub>A</sub>  | Ambient temperature        |                                 | -40             | 85              | °C   |

| $T_{J}$         | Junction temperature       |                                 |                 | 125             | °C   |

#### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>             | LMX2571<br>WQFN (NJK) | UNIT |

|----------------------|-------------------------------------------|-----------------------|------|

|                      |                                           | 36 PINS               |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance    | 32.9                  | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance | 14.5                  | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Product Folder Links: LMX2571

#### Thermal Information (continued)

|                      |                                              | LMX2571    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | WQFN (NJK) | UNIT |

|                      |                                              | 36 PINS    |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.3        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.3        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.0        | °C/W |

#### 6.5 Electrical Characteristics

$3.15~V \le V_{CC} \le 3.45~V,~V_{IO} = V_{CC},~-40~^{\circ}C \le T_{A} \le 85~^{\circ}C,~except~as~specified.$  Typical values are at  $V_{CC} = V_{IO} = 3.3~V,~V_{CP} = 3.3~$

|                      | PARAMETER                                   | TEST CO                                | ONDITIONS                                                          | MIN    | TYP    | MAX | UNIT |  |

|----------------------|---------------------------------------------|----------------------------------------|--------------------------------------------------------------------|--------|--------|-----|------|--|

| CURREN               | T CONSUMPTION                               | '                                      |                                                                    |        |        |     |      |  |

|                      |                                             |                                        | Configuration A <sup>(1)</sup>                                     | 39     |        |     |      |  |

|                      | Total current in synthesizer mode (internal |                                        | Configuration B <sup>(2)</sup>                                     |        | 44     |     |      |  |

| I <sub>CC</sub>      | VCO)                                        |                                        | Configuration C <sup>(3)</sup>                                     |        | 46     |     |      |  |

|                      |                                             | f <sub>OUT</sub> = 480 MHz<br>SE OSCin | Configuration D <sup>(4)</sup>                                     |        | 51     |     |      |  |

|                      |                                             | 3L 030III                              | Configuration E <sup>(5)</sup>                                     |        | 9      |     | mA   |  |

| I <sub>PLL</sub>     | Total current in PLL mode (external VCO)    |                                        | Configuration F <sup>(6)</sup>                                     |        | 15     |     |      |  |

|                      |                                             |                                        | Configuration G <sup>(7)</sup>                                     |        | 21     |     |      |  |

| I <sub>CC</sub> PD   | Power down current                          |                                        | CE = 0V or POWERDOWN bit = 1<br>$V_{CC}$ = 3.3 V, Push-pull output |        | 0.9    |     |      |  |

| OSCIN R              | REFERENCE INPUT                             |                                        |                                                                    |        |        |     |      |  |

| f <sub>OSCin</sub>   | OSCin frequency range                       | Single-ended or differentia            | l input                                                            | 10 150 |        | 150 | MHz  |  |

|                      | OSCin input voltage (8)                     | Single-ended input                     |                                                                    | 1.4    |        | 3.3 | V    |  |

| $V_{OSCin}$          | OSCIn input voltage (7)                     | Differential input                     |                                                                    | 0.15   |        | 1.5 | V    |  |

| CRYSTA               | L REFERENCE INPUT                           |                                        |                                                                    |        |        |     |      |  |

| f <sub>XTAL</sub>    | Crystal frequency range                     | Fundamental model, ESR                 | < 200 Ω                                                            | 10     |        | 40  | MHz  |  |

| C <sub>IN</sub>      | OSCin input capacitance                     |                                        |                                                                    |        | 1      |     | pF   |  |

| MULT                 |                                             | ·                                      |                                                                    |        |        |     |      |  |

| f <sub>MULTin</sub>  | MULT input frequency                        | MULT > Pre-divider                     |                                                                    | 10     |        | 30  | MHz  |  |

| f <sub>MULTout</sub> | MULT output frequency                       | Not supported with crystal             | reference input                                                    | 60     |        | 130 | MHz  |  |

| PLL                  |                                             | ·                                      |                                                                    |        |        |     |      |  |

| f <sub>PD</sub>      | Phase detector frequency                    |                                        |                                                                    |        |        | 130 | MHz  |  |

|                      |                                             | Programmable minimum                   | Internal charge pump                                               |        | 312.5  |     |      |  |

|                      |                                             | value                                  | 5-V charge pump                                                    |        | 625    |     | μА   |  |

| V                    | Charge pump current <sup>(9)</sup>          | Der programmable eten                  | Internal charge pump                                               |        | 312.5  |     |      |  |

| K <sub>PD</sub>      | Charge pump current                         | Per programmable step                  | 5-V charge pump                                                    |        | 625    |     |      |  |

|                      |                                             | Programmable maximum                   | Internal charge pump                                               |        | 7187.5 |     | 1    |  |

|                      |                                             | value                                  | 5-V charge pump                                                    |        | 6875   |     |      |  |

<sup>(1)</sup>  $f_{OSCin} = 19.44 \text{ MHz}$ , MULT = 1, Prescaler = 4,  $f_{PD} = 19.44 \text{ MHz}$ , one RF output, output type = push pull, output power = -3 dBm

$f_{OSCin}$  = 19.44 MHz, MULT = 1, Prescaler = 2,  $f_{PD}$  = 19.44 MHz, one RF output, output type = push pull, output power = -3 dBm  $f_{OSCin}$  = 19.44 MHz, MULT = 5, Prescaler = 2,  $f_{PD}$  = 19.44 MHz, one RF output, output type = push pull, output power = -3 dBm

f<sub>OSCin</sub> = 19.44 MHz, MULT = 5, Prescaler = 2, f<sub>PD</sub> = 97.2 MHz, one RF output, output type = push pull, output power = −3 dBm

$f_{OSCin} = 19.44$  MHz, MULT = 1,  $f_{PD} = 19.44$  MHz, output from VCO (5)

$f_{OSCin} = 19.44$  MHz, MULT = 1,  $f_{PD} = 19.44$  MHz, one RF output, output type = push pull, output power = -3 dBm

$f_{OSCin} = 19.44 \text{ MHz}$ , MULT = 1,  $f_{PD} = 19.44 \text{ MHz}$ , two RF outputs, output type = push pull, output power = -3 dBm See OSCin Configuration for definition of OSCin input voltage.

This is referring to the total base charge pump current. In PLL mode, this is equal to EXTVCO\_CP\_IDN + EXTVCO\_CP\_IUP. In synthesizer mode, this is equal to CP\_IDN + CP\_IUP. See Table 6, Table 7 and Table 8 for details.

# **Electrical Characteristics (continued)**

$3.15~V \le V_{CC} \le 3.45~V,~V_{IO} = V_{CC},~-40~^{\circ}C \le T_{A} \le 85~^{\circ}C,~except~as~specified.$  Typical values are at  $V_{CC} = V_{IO} = 3.3~V,~V_{CP} = 3.3~$

|                                   | PARAMETER                                    | TEST CO                                | NDITIONS                                                     | MIN  | TYP    | MAX             | UNIT   |

|-----------------------------------|----------------------------------------------|----------------------------------------|--------------------------------------------------------------|------|--------|-----------------|--------|

| DNI                               | N (10)                                       |                                        | Internal charge pump                                         |      | -124   |                 | ID #1  |

| PN <sub>PLL_1/f</sub>             | Normalized PLL 1/f noise <sup>(10)</sup>     | At maximum charge pump                 | 5-V charge pump                                              |      | -120   |                 | dBc/Hz |

| 5                                 |                                              | current                                | Internal charge pump                                         |      | -231   |                 |        |

| PN <sub>PLL_Flat</sub>            | Normalized PLL noise floor <sup>(10)</sup>   |                                        | 5-V charge pump                                              |      | -226   |                 | dBc/Hz |

|                                   | External VCO input frequency <sup>(11)</sup> | EXTVCO_CHDIV=1                         | EXTVCO CHDIV=1                                               |      |        | 2000            |        |

| f <sub>RFin</sub>                 |                                              | EXTVCO_CHDIV=8,10                      |                                                              | 100  |        | 1900            | MHz    |

|                                   |                                              | EXTVCO_CHDIV=2,3,4,5,6                 | 5,7,9                                                        | 100  |        | 1400            | Ī      |

|                                   |                                              | 0.1 GHz ≤ f <sub>RFin</sub> < 1 GHz    |                                                              | -10  |        |                 |        |

| $P_{RFin}$                        | External VCO input power                     | 1 GHz ≤ f <sub>RFin</sub> ≤ 1.4 GHz    |                                                              | -5   |        |                 | dBm    |

|                                   |                                              | 1.4 GHz < f <sub>RFin</sub> ≤ 2 GHz    |                                                              | 0    |        |                 | Ī      |

| vco                               |                                              |                                        |                                                              | - 11 |        |                 |        |

| f <sub>VCO</sub>                  | VCO frequency                                |                                        |                                                              | 4300 |        | 5376            | MHz    |

| K <sub>VCO</sub>                  | VCO gain <sup>(12)</sup>                     | f <sub>VCO</sub> = 4800 MHz            |                                                              |      | 56     |                 | MHz/V  |

| ΔT <sub>CL</sub>                  | Allowable temperature drift <sup>(13)</sup>  | VCO not being re-calibrated            | VCO not being re-calibrated, –40 °C ≤ T <sub>A</sub> ≤ 85 °C |      |        | 125             | °C     |

| t <sub>VCOCal</sub>               | VCO calibration time                         | $f_{OSCin} = f_{PD} = 100 \text{ MHz}$ |                                                              |      | 140    |                 | μs     |

|                                   | Open loop VCO phase noise                    |                                        | 100 Hz offset                                                |      | -32.4  |                 |        |

|                                   |                                              |                                        | 1 kHz offset                                                 |      | -62.3  |                 | Ī      |

| <b>D.</b> 1                       |                                              |                                        | 10 kHz offset                                                |      | -92.1  |                 | dBc/Hz |

| $PN_{VCO}$                        |                                              | $f_{OUT} = 480 \text{ MHz}$            | 100 kHz offset                                               | -    | -121.1 |                 |        |

|                                   |                                              |                                        | 1 MHz offset                                                 | -    | -144.5 |                 |        |

|                                   |                                              |                                        | 10 MHz offset                                                | -    | -156.8 |                 |        |

| RF OUTPU                          | JT                                           |                                        |                                                              |      |        |                 | 1      |

|                                   | DE suits at few suits and                    | Synthesizer mode                       |                                                              | 10   |        | 1344            | N41.1- |

| f <sub>OUT</sub>                  | RF output frequency                          | PLL mode, RF output from               | buffer                                                       | 10   |        | 1400            | MHz    |

| P <sub>TX</sub> , P <sub>RX</sub> | RF output power                              | f 400 MH-                              | Danier and hit C                                             |      | 0      |                 | dBm    |

| H2 <sub>RFout</sub>               | Second harmonic                              | f <sub>OUT</sub> = 480 MHz             | Power control bit = 6                                        |      | -25    |                 | dBc    |

| DIGITAL F                         | SK MODULATION                                |                                        |                                                              | -    |        |                 | ·<br>I |

| FSK <sub>Level</sub>              | FSK level <sup>(14)</sup>                    | FSK PIN mode                           |                                                              | 2    |        | 8               |        |

| FSK <sub>Baud</sub>               | FSK baud rate <sup>(15)</sup>                | Loop bandwidth = 200 kHz               | Loop bandwidth = 200 kHz                                     |      | 100    |                 | kSPs   |

| FSK <sub>Dev</sub>                | FSK deviation                                | Configuration H <sup>(16)</sup>        | Configuration H <sup>(16)</sup>                              |      | ±39    |                 | kHz    |

|                                   | NTERFACE                                     | 1                                      |                                                              |      |        |                 |        |

| V <sub>IH</sub>                   | High level input voltage                     |                                        |                                                              | 1.4  |        | V <sub>IO</sub> | V      |

| V <sub>IL</sub>                   | Low level input voltage                      |                                        |                                                              |      |        | 0.4             | V      |

| I <sub>IH</sub>                   | High level input current                     | V <sub>IH</sub> = 1.75 V               |                                                              | -25  |        | 25              | μΑ     |

- (10) Measured with a clean OSCin signal with a high slew rate using a wide loop bandwidth. The noise metrics model the PLL noise for an infinite loop bandwidth as:

- PLL\_Total = 10 \* log[10<sup>(PLL\_Flat / 10)</sup> + 10<sup>(PLL\_Flicker / 10)</sup>]

- $PLL\_Flat = PN1Hz + 20 * log(N) + 10 * log(f_{PD})$

- PLL\_Flicker = PN10kHz 10 \* log(Offset / 10 kHz) + 20 \* log(f<sub>OUT</sub> / 1 GHz)

- (11) For external VCO frequencies above 1.4 GHz, there are restrictions on the output divider and register R70 needs to be programmed to 0x046110.

- (12) The VCO gain changes as a function of the VCO core and frequency. See Integrated VCO for details.

- (13) Not tested in production. Ensured by characterization. Allowable temperature drift refers to programming the device at an initial temperature and allowing this temperature to drift WITHOUT reprogramming the device, and still have the device stay in lock. This change could be up or down in temperature and the specification does not apply to temperatures that go outside the recommended operating temperatures of the device.

- (14) The data showed here simply specifies the range of discrete FSK level that is supported in PIN mode. PIN mode supports 2-, 4- and 8-level of FSK modulation. If arbitrary level of FSK modulation is desired, use FSK SPI™ FAST mode or FSK I2S mode. See *Direct Digital FSK Modulation* for details.

- (15) The baud rate is limited by the loop bandwidth of the PLL loop. As a general rule of thumb, it is desirable to have the loop bandwidth at least twice the baud rate.

- (16) f<sub>PD</sub> = 100 MHz, DEN = 2<sup>24</sup>, CHDIV1 = 5, CHDIV2 = 2, Prescaler = 2, FSK step value = 32716, 32819. The maximum achievable frequency deviation depends on the configuration, see *Direct Digital FSK Modulation* for details.

#### **Electrical Characteristics (continued)**

$3.15~V \le V_{CC} \le 3.45~V,~V_{IO} = V_{CC},~-40~^{\circ}C \le T_{A} \le 85~^{\circ}C,~except~as~specified.~Typical~values~are~at~V_{CC} = V_{IO} = 3.3~V,~V_{CP} = 3.3~V,$

|                 | PARAMETER                 | TEST CONDITIONS           | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------|---------------------------|-----|-----|-----|------|

| I <sub>IL</sub> | Low level input current   | V <sub>IL</sub> = 0 V     | -25 |     | 25  | μΑ   |

| V <sub>OH</sub> | High level output voltage | $I_{OH} = 500 \ \mu A$    | 2   |     |     | V    |

| V <sub>OL</sub> | Low level output voltage  | I <sub>OL</sub> = -500 μA |     | 0   | 0.4 | V    |

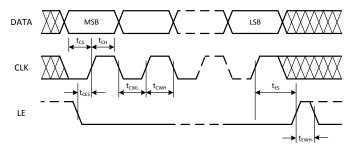

#### 6.6 Timing Requirements

3.15 V  $\leq$  V<sub>CC</sub>  $\leq$  3.45 V, V<sub>IO</sub> = V<sub>CC</sub>, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, except as specified. Typical values are at V<sub>CC</sub> = V<sub>IO</sub> = 3.3 V, T<sub>A</sub> = 25 °C.

|                  |                            |              | MIN | NOM | MAX | UNIT |

|------------------|----------------------------|--------------|-----|-----|-----|------|

| MICRO            | WIRE TIMING                |              |     |     |     |      |

| t <sub>ES</sub>  | Clock to enable low time   |              | 5   |     |     | ns   |

| t <sub>CS</sub>  | Data to clock setup time   |              | 2   |     |     | ns   |

| t <sub>CH</sub>  | Data to clock hold time    |              | 2   |     |     | ns   |

| t <sub>CWH</sub> | Clock pulse width high     | See Figure 1 | 5   |     |     | ns   |

| t <sub>CWL</sub> | Clock pulse width low      |              | 5   |     |     | ns   |

| t <sub>CES</sub> | Enable to clock setup time |              | 5   |     |     | ns   |

| t <sub>EWH</sub> | Enable pulse width high    |              | 2   |     |     | ns   |

Figure 1. MICROWIRE Timing Diagram

There are several other considerations for programming:

- A slew rate of at least 30 V/µs is recommended for the CLK, DATA and LE. The same apply for other digital control signals such as FSK\_D[0:2] and FSK\_DV signals.

- The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the LE signal, the data is sent from the shift register to an active register.

- The LE pin may be held high after programming, causing the LMX2571 to ignore clock pulses.

- When CLK or DATA lines are shared between devices, it is recommended to divide down the voltage to the CLK, DATA, and LE pins closer to the minimum voltage. This provides better noise immunity.

- If the CLK and DATA lines are toggled while the VCO is in lock, as is sometimes the case when these lines

are shared with other parts, the phase noise may be degraded during the time of this programming.

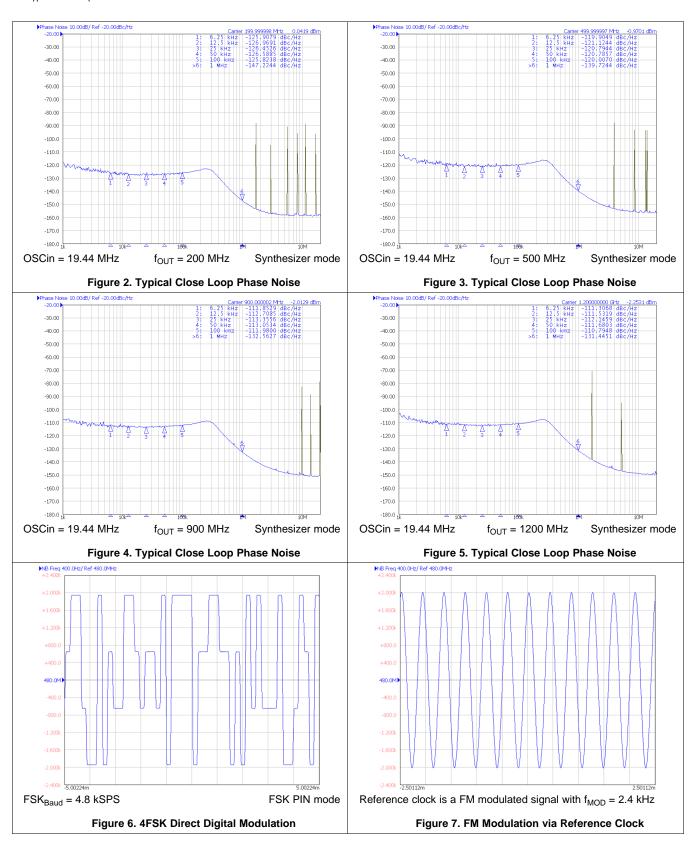

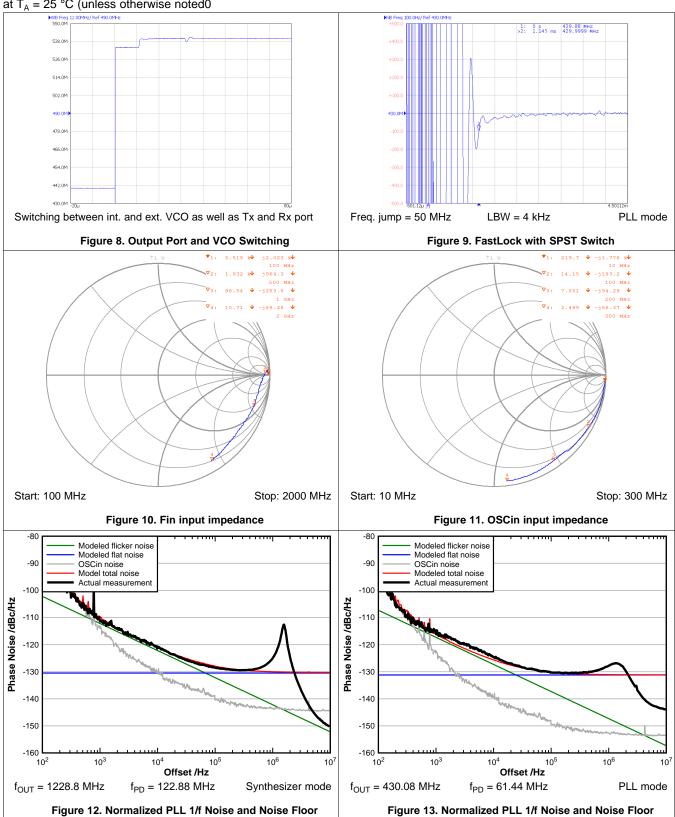

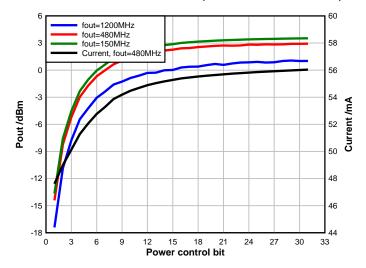

# 6.7 Typical Characteristics

at  $T_A = 25$  °C (unless otherwise noted0

Submit Documentation Feedback

Copyright © 2015–2016, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

at  $T_A = 25$  °C (unless otherwise noted0

# 7 Detailed Description

#### 7.1 Overview

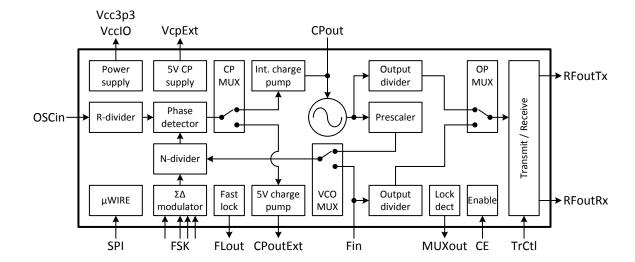

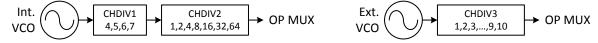

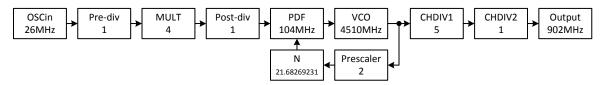

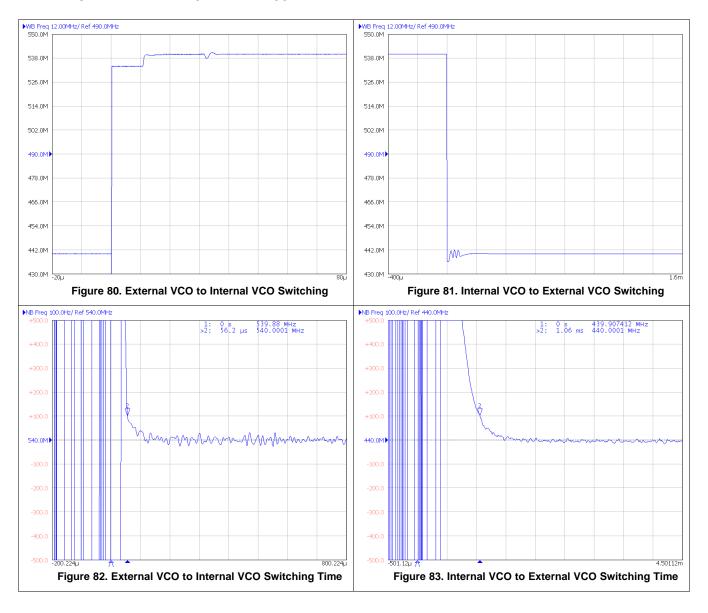

The LMX2571 is a frequency synthesizer with low-noise, high-performance integrated VCOs. The 5-GHz VCO cores, together with the output channel dividers, can produce frequencies from 10 MHz to 1344 MHz. The LMX2571 supports two operation modes, synthesizer mode and PLL mode. In synthesizer mode, the entire device is utilized; in PLL mode the internal VCO is bypassed, and an external VCO is required to implement a complete synthesizer.

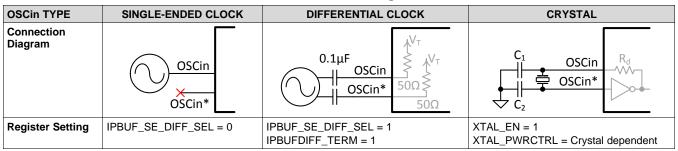

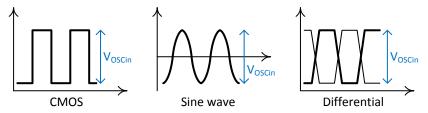

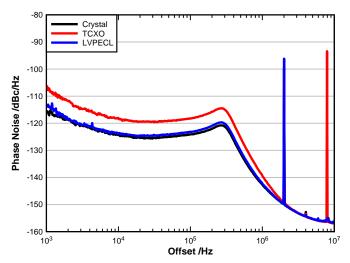

The reference clock input supports a crystal used for the on-chip oscillator, AC-coupled differential clock signals, and DC-coupled single-ended clock signals such as XO or CMOS clock devices.

The PLL is a fractional-N PLL with programmable Delta Sigma modulator (first order to fourth order). The fractional denominator is of variable length and up to 24-bits long, providing a frequency step with very fine resolution.

The internal VCO can be bypassed, allowing the use of an external VCO. A separate 5-V charge pump is dedicated for the external VCO, eliminating the need for an op-amp to support 5-V VCOs. A new advanced FastLock technique is developed to shorten the lock time to less than 1.5 ms, even there is a very narrow loop bandwidth.

A unique programmable multiplier is incorporated in the R-divider. The multiplier is used to avoid and reduce integer boundary spurs or to increase the phase detector frequency for higher performance.

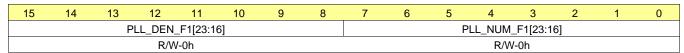

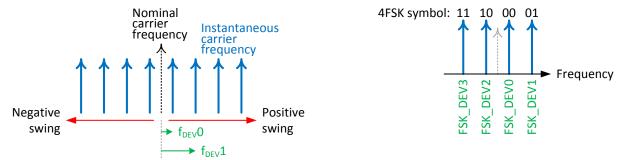

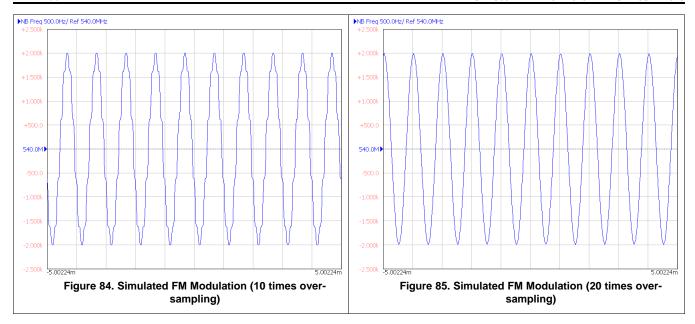

The LMX2571 supports direct digital FSK modulation, thus allowing a change in the output frequency by changing the N-divider value. The N-divider value can be programmed through MICROWIRE interface or through pins. Discrete 2-, 4- and 8-level FSK, as well as arbitrary-level FSK, are supported. Arbitrary-level FSK can be used to construct pulse-shaping FSK or analog-FM modulation.

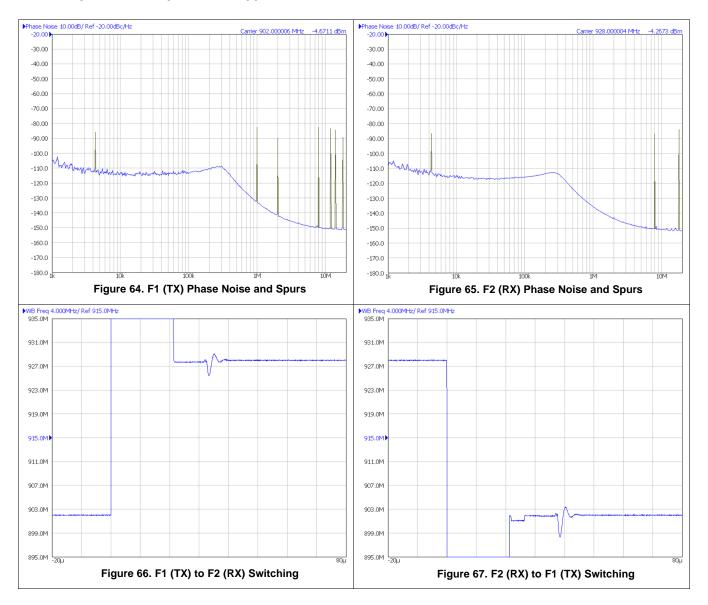

The output has an integrated T/R switch, and the divided-down internal or external VCO signal can be output to either the TX port or the RX port. The switch can also be configured as a 1:2 fanout buffer, providing the signal on both outputs at the same time. In addition to port switching, the output frequency can be switched between two pre-defined frequencies, F1 and F2, simultaneously. This feature is ideal for use in FDD duplex system where the TX frequency is different from RX (LO) frequency.

The LMX2571 requires only a single 3.3-V power supply. Digital logic interface is 1.8-V input compatible. The analog blocks power supplies use integrated LDOs, eliminating the need for high performance external LDOs.

Programming of the device is achieved through the MICROWIRE interface. The device can be powered down through a register programming or toggling the Chip Enable (CE) pin.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Reference Oscillator Input

The OSCin and OSCin\* pins are used as frequency reference inputs to the device. The OSCin pin can be driven single-ended with a CMOS clock or a crystal oscillator. The on-chip crystal oscillator can also be used with an external crystal as the reference clock. Differential clock input is also supported, making it easily to interface with high performance system clock devices such as Tl's LMK series clock devices.

Because the OSCin or OSCin\* signal is used as a clock for VCO calibration, a proper signal needs to be applied at the OSCin and/or OSCin\* pin at the time of programming the R0 register. A higher slew rate tends to yield the best fractional spurs and phase noise, so a square wave signal is best for the OSCin and/or OSCin\*pins. If using a sine wave, higher frequencies tend to yield better phase noise and fractional spurs due to their higher slew rates.

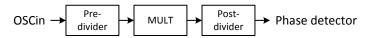

#### 7.3.2 R-Dividers and Multiplier

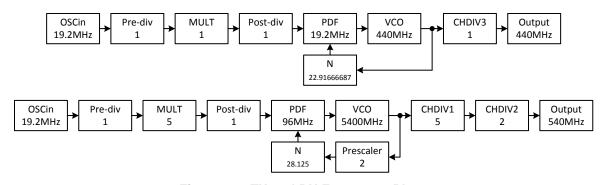

The R-divider consists of a Pre-divider, a Multiplier (MULT), and a Post-divider.

Figure 14. R-Divider

Both the Pre- and Post-dividers divide frequency down while the MULT multiplies frequency up. The purpose of adding a multiplier is to avoid and reduce integer boundary spurs or to increase the phase-detector frequency for higher performance. See *MULT Multiplier* for details. The phase detector frequency, f<sub>PD</sub>, is therefore equal to

$$f_{PD} = (f_{OSCin} / Pre-divider) * (MULT / Post-divider)$$

(1)

When using the Multiplier (MULT > 1), there are some points to remember:

- The Multiplier must be greater than the Pre-divider.

- Crystal mode must be disabled (XTAL\_EN=0).

- Using the multiplier may add noise, especially for multiplier values greater than 6.

#### 7.3.3 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the Post-divider and N-divider and generates a correction current corresponding to the phase error. This charge pump current is programmable to different strengths.

#### 7.3.4 PLL N-Divider and Fractional Circuitry

The total N-divider value is determined by  $N_{integer}$  + NUM / DEN. The N-divider includes fractional compensation and can achieve any fractional denominator (DEN) from 1 to 16,777,215 ( $2^{24}$  – 1). The integer portion,  $N_{integer}$ , is the whole part of the N-divider value and the fractional portion,  $N_{frac}$  = NUM / DEN, is the remaining fraction.  $N_{integer}$ , NUM and DEN are programmable.

The order of the delta sigma modulator is also programmable from integer mode to fourth order. There are several dithering modes that are also programmable. Dithering is used to reduce fractional spurs. In order to make the fractional spurs consistent, the modulator is reset any time that the R0 register is programmed.

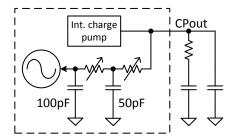

#### 7.3.5 Partially Integrated Loop Filter

The LMX2571 integrates the third and fourth pole of the loop filter. The values for the resistors can be programmed independently through the MICROWIRE interface. The larger the values of the resistors, the stronger the attenuation of the internal loop filter. This partially integrated loop filter can only be used in synthesizer mode.

#### **Feature Description (continued)**

Figure 15. Integrated Loop Filter

#### 7.3.6 Low-Noise, Fully Integrated VCO

The LMX2571 includes a fully integrated VCO. The VCO generates a frequency which varies with the tuning voltage from the loop filter. Output of the VCO is fed to a prescaler before going to the N-divider. The prescaler value is selectable between 2 and 4. In general, prescaler equals 2 will result in better phase noise especially when the PLL is operated in fractional-N mode. If the prescaler equals 4, however, the device will consume less current. The VCO frequency is related to the other frequencies and Prescaler as follows:

$$f_{VCO} = f_{PD} * N$$

-divider \* Prescaler (2)

In order to reduce the VCO tuning gain, thus improving the VCO phase noise performance, the VCO frequency range is divided into several different frequency bands. This creates the need for frequency calibration in order to determine the correct frequency band given a desired output frequency. The VCO is also calibrated for amplitude to optimize phase noise. These calibration routines are activated any time that the R0 register is programmed with the FCAL\_EN bit equals one. It is important that a valid OSCin signal must present before VCO calibration begins.

This device will support a full sweep of the valid temperature range of 125°C (-40°C to 85°C) without having to re-calibrate the VCO. This is important for continuous operation of the synthesizer under the most extreme temperature variation.

#### 7.3.7 External VCO Support

The LMX2571 supports an external VCO in PLL mode. In PLL mode, the internal VCO and its associated charge pump are powered down, and a 5-V charge pump is switched in to support external VCO. No extra external low noise op-amp is required to support 5-V tuning range VCO. The external VCO output can be obtained directly from the VCO or from the device's RF output buffer.

# 7.3.8 Programmable RF Output Divider

The internal VCO RF output divider consists of two sub-dividers; the total division value is equal to the multiplication of them. As a result, the minimum division is 4 while the maximum division is 448.

Figure 16. VCO Output Divider

There is only one output divider when external VCO is being used. This divider supports even and odd division, and its values are programmable between 1 and 10.

#### 7.3.9 Programmable RF Output Buffer

The RF output buffer type is selectable between push-pull and open drain. If open drain buffer is selected, external pullup to VcclO is required. Regardless of output type, output power can be programmed to various levels. The RF output buffer can be disabled while still keeping the PLL in lock. See RF Output Buffer Type for details.

#### Feature Description (continued)

#### 7.3.10 Integrated TX, RX Switch

The LMX2571 integrates a T/R switch which is controlled by the TrCtl pin. The output from the internal VCO or external VCO divider will be routed to either the RFoutTx or RFoutRx ports, depending on the state of the TrCtl pin. The TrCtl pin not only controls the output port, but may also switch the output frequency simultaneously. For example, if TrCtl = 1, the active port is RFoutTx with an output frequency of F1. When TrCtl changes from 1 to 0, the active port could be RFoutRx with an output frequency of F2. LMX2571 has two sets of register to store the configurations for F1 and F2.

The T/R switch could also be configured as a fanout buffer to output the same signal at both RFoutTx and RFoutRx ports at the same time. All of these features are also programmable, see *Programming* and *Frequency and Output Port Switching with TrCtl Pin* for details.

#### 7.3.11 Powerdown

The LMX2571 can be powered up and down using the CE pin or the POWERDOWN bit. All registers are preserved in memory while it is powered down. When the device comes out of the powered down state, either by resuming the POWERDOWN bit to zero or by pulling back CE pin HIGH (if it was powered down by CE pin), it is required that register R0 with FCAL EN=1 be programmed again to re-calibrate the device.

#### 7.3.12 Lock Detect

The MUXout pin of the LMX2571 can be configured to output a signal that indicates when the PLL is being locked. If lock detect is enabled while the MUXout pin is configured as a lock-detect output, when the device is locked the MUXout pin output is a logic HIGH voltage. When the device is unlocked, MUXout output is a logic LOW voltage.

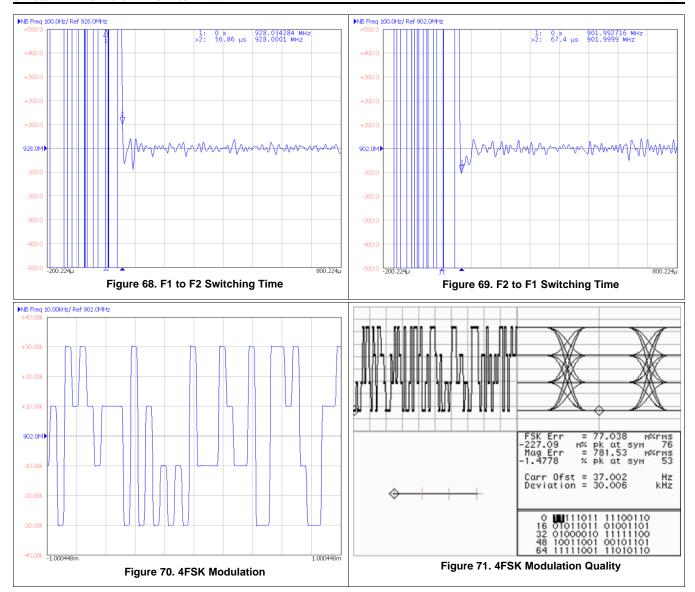

#### 7.3.13 FSK Modulation

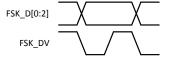

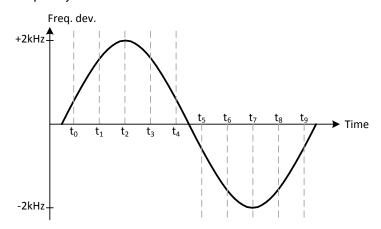

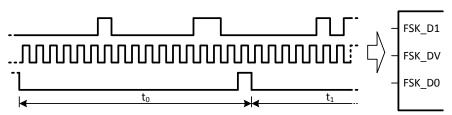

Direct digital FSK modulation is supported in LMX2571. FSK modulation is achieved by changing the output frequency by changing the N-divider value. The LMX2571 supports four different types of FSK operation.

- 1. FSK PIN mode. LMX2571 supports 2-, 4- and 8-level FSK modulation in PIN mode. In this mode, symbols are directly fed to the FSK\_D0, FSK\_D1, and FSK\_D2 pins. Symbol clock is fed to the FSK\_DV pin. Symbols are latched into the device on the rising edge of the symbol clock. The maximum supported symbol clock rate is 1 MHz. The device has eight dedicated registers to pre-store the desired FSK frequency deviations, with each register corresponding to one of the FSK symbols. The LMX2571 will change its output frequency according to the states on the FSK pins; no extra register programming is required.

- 2. FSK SPI mode. This mode is identical to the FSK PIN mode with the exception that the control for the selected FSK level is not performed with external pins but with register R34. Each time when register R34 is programmed, change only the FSK\_DEV\_SEL field to select the desired FSK frequency deviation as stored in the dedicated registers.

- 3. FSK SPI FAST mode. In this mode, instead of selecting one of the pre-stored FSK level, change the FSK deviation directly by writing to the register R33, FSK\_DEV\_SPI\_FAST field. As a result, this mode supports arbitrary-FSK level, which is useful to construct pulse-shaping or analog-FM modulation.

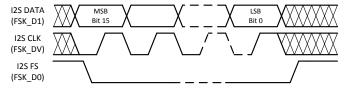

- 4. FSK I2S mode. This mode is similar to the FSK SPI FAST mode, but the programming format is an I2S format on dedicated pins instead of SPI. The benefit of using I2S is that this interface could be shared and synchronous to other digital audio interfaces. The same FSK data input pins that are used in FSK PIN mode are re-used to support I2S programming. In this mode only the 16 bits of DATA field is required to program. The data is transmitted on the high or low side of the frame sync (programmable in register R34, FSK\_I2S\_FS\_POL). The unused side of the frame sync needs to be at least one clock cycle. In other words, 17 (16 + 1) CLK cycles are required at a minimum for one I2S frame. Maximum I2S clock rate is 100 MHz.

Figure 17. FSK PIN Mode Timing

Figure 18. FSK I2S Mode Timing

Submit Documentation Feedback

#### **Feature Description (continued)**

See Direct Digital FSK Modulation for FSK operation details.

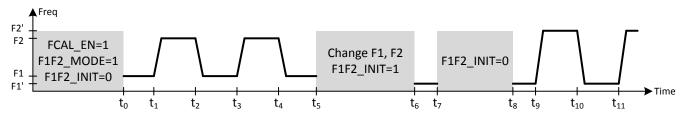

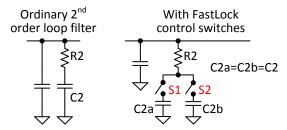

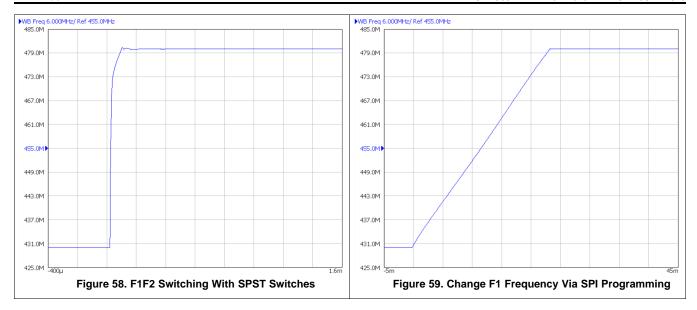

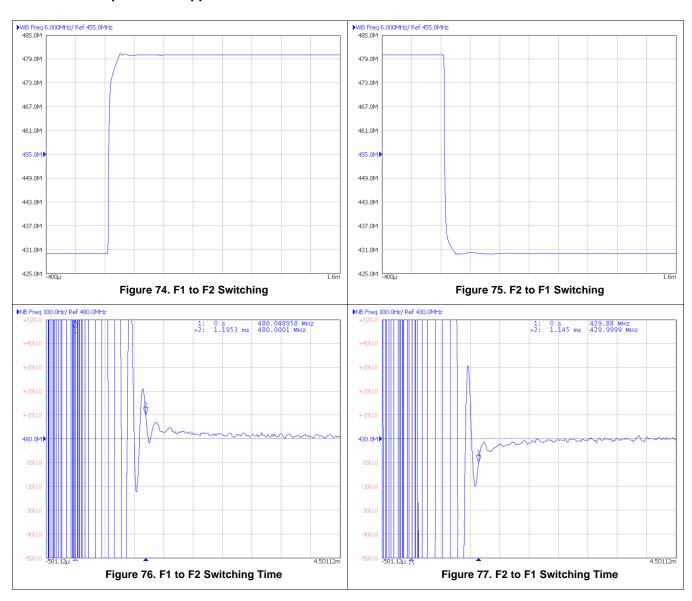

#### 7.3.14 FastLock

The LMX2571 includes a FastLock feature that can be used to improve the lock times in PLL mode when the loop bandwidth is small. In general, the lock time is approximately equal to 4 divided by the loop bandwidth. If the loop bandwidth is 1 kHz, then the lock time would be 4 ms. However, if the f<sub>PD</sub> is much higher than the loop bandwidth, cycle slipping may occur, and the actual lock time will be much longer. Traditional fastlock usually reduces lock time by increasing loop bandwidth during frequency switching. However, there is a limitation on the achievable maximum loop bandwidth due to limitation on charge-pump current and loop filter component values. In some cases, this kind of fastlock technique will make cycle slip even worse.

The LMX2571 adopts a new FastLock approach that eliminates the cycle slip problem. With an external analog SPST switch in conjunction with LMX2571's FastLock control, the lock time for a 100-MHz frequency switch could be settled in less than 1.5 ms. See *FastLock with External VCO* for details.

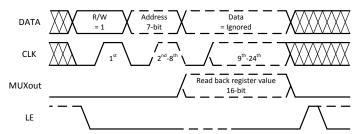

#### 7.3.15 Register Readback

The LMX2571 allows any of its registers to be read back. The MUXout pin can be programmed to support either lock-detect output or register-readback serial-data output. To read back a certain register value, follow the following steps:

- 1. Set the R/W bit to 1; the data field contents are ignored.

- 2. Send the register to the device; readback serial data will be output starting at the 9<sup>th</sup> clock cycle.

Figure 19. Register Readback Timing Diagram

### 7.4 Device Functional Modes

#### 7.4.1 Operation Mode

The device can be operated in synthesizer mode or PLL mode.

- 1. Synthesizer mode. The internal VCO will be adopted.

- 2. PLL mode. The device is operated as a standalone PLL; an external VCO is required to complete the loop.

#### 7.4.2 Duplex Mode

LMX2571 supports fast frequency switching between two pre-defined register sets, F1 and F2. This feature is good for duplex operation. The device supports three duplex modes:

- 1. Synthesizer duplex mode. Both F1 and F2 are operated in synthesizer mode.

- 2. PLL duplex mode. Both F1 and F2 are operated in PLL mode.

- 3. Synthesizer/PLL duplex mode. In this mode, F1 and F2 will be operated in different operation mode.

#### 7.4.3 FSK Mode

LMX2571 supports four direct digital FSK modulation modes.

- 1. FSK PIN mode. 2-, 4- and 8-level FSK modulation. Modulation data is fed to the device through dedicated pins.

- 2. FSK SPI mode. 2-, 4- and 8-level FSK modulation. Pre-defined FSK deviation is selected through SPI programming.

#### **Device Functional Modes (continued)**

- 3. FSK SPI FAST mode. This mode supports arbitrary-level FSK modulation. Desired FSK deviation is written to the device through SPI programming.

- 4. FSK I2S mode. Arbitrary-level FSK modulation is supported. Desired FSK deviation is fed to the device through dedicated pins.

#### 7.5 Programming

The LMX2571 is programmed using several 24-bit registers. A 24-bit shift register is used as a temporary register to indirectly program the on-chip registers. The shift register consists of a data field, an address field, and a R/W bit. The MSB is the R/W bit. 0 means register write while 1 means register read. The following 7 bits, ADDR[6:0], form the address field which is used to decode the internal register address. The remaining 16 bits form the data field DATA[15:0]. While LE is low, serial data is clocked into the shift register upon the rising edge of clock. Serial data is shifted MSB first into the shift register when programming. When LE goes high, data is transferred from the data field into the selected active register bank. See Figure 1 for timing diagram details.

#### 7.5.1 Recommended Initial Power on Programming Sequence

When the device is first powered up, it needs to be initialized, and the ordering of this programming is important. The sequence is listed below. After this sequence is completed, the device should be running and locked to the proper frequency.

- 1. Apply power to the device and ensure the Vcc pins are at the proper levels.

- 2. If CE is LOW, pull it HIGH.

- 3. Wait 100 µs for the internal LDOs to become stable.

- 4. Ensure that a valid reference is applied to the OSCin pin.

- 5. Program register R0 with RESET=1. This will ensure all the registers are reset to their default values.

- 6. Program in sequence registers R60, R58, R53, ..., R1 and then R0.

#### 7.5.2 Recommended Sequence for Changing Frequencies

The recommended sequence for changing frequencies in different scenarios is as follows:

- 1. If the N-divider is changing, program the relevant registers, then program R0 with FCAL\_EN = 1.

- 2. In FSK SPI mode, FSK SPI FAST mode, and FSK I2S mode, the fractional numerator is changing; program the relevant registers only.

- 3. If switching frequency between F1 and F2, program the relevant control registers only or toggle the TrCtl pin. See *Frequency and Output Port Switching with TrCtl Pin* for details.

Copyright © 2015–2016, Texas Instruments Incorporated

Product Folder Links: LMX2571

# TEXAS INSTRUMENTS

# 7.6 Register Maps

| REG | 23  | 22 | 21 | 20   | 19 | 18 | 17 | 16 | 15                     | 14                                                                                              | 13     | 12       | 11       | 10            | 9      | 8       | 7           | 6         | 5                     | 4       | 3          | 2                    | 1        | 0     | POR     |

|-----|-----|----|----|------|----|----|----|----|------------------------|-------------------------------------------------------------------------------------------------|--------|----------|----------|---------------|--------|---------|-------------|-----------|-----------------------|---------|------------|----------------------|----------|-------|---------|

|     | R/W |    |    | ADDF |    |    |    |    |                        |                                                                                                 |        |          |          |               |        |         | DATA[15     | :0]       |                       | -       |            | 1                    |          |       |         |

| R60 | R/W | 0  | 1  | 1    | 1  | 1  | 0  | 0  | 1                      | 0                                                                                               | 1      | 0        | 0        | 0             | 0      | 0       | 0           | 0         | 0                     | 0       | 0          | 0                    | 0        | 0     | 3C4000h |

| R58 | R/W | 0  | 1  | 1    | 1  | 0  | 1  | 0  | 1                      | 0                                                                                               | 0      | 0        | 1        | 1             | 0      | 0       | 0           | 0         | 0                     | 0       | 0          | 0                    | 0        | 0     | 3A0C00h |

| R53 | R/W | 0  | 1  | 1    | 0  | 1  | 0  | 1  | 0                      | 1                                                                                               | 1      | 1        | 1        | 0             | 0      | 0       | 0           | 0         | 0                     | 0       | 0          | 1                    | 1        | 0     | 352802h |

| R47 | R/W | 0  | 1  | 0    | 1  | 1  | 1  | 1  | 0                      | DITHER                                                                                          | RING   | 0        | 0        | 0             | 0      | 0       | 0           | 0         | 0                     | 0       | 0          | 0                    | 0        | 0     | 2F0000h |

| R46 | R/W | 0  | 1  | 0    | 1  | 1  | 1  | 0  | 0                      | 0                                                                                               | 0      | 0        | 0        | 0             | 0      | 0       | 0           | 0         | 0                     | 1       | 1          | VCO_<br>SEL_<br>STRT | VCC      | D_SEL | 2E001Ah |

| R42 | R/W | 0  | 1  | 0    | 1  | 0  | 1  | 0  | 0                      | 0                                                                                               | 0      | 0        | 0        | 0             | 1      | 0       | 0           | 0         | EXTVCO<br>_CP<br>_POL |         |            | EXTVCO_              | _CP_IDN  |       | 2A0210h |

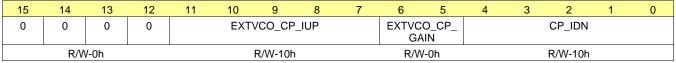

| R41 | R/W | 0  | 1  | 0    | 1  | 0  | 0  | 1  | 0                      | 0                                                                                               | 0      | 0        |          | EX            | TVCO_C | P_IUP   |             | EXTVCO    | _CP_GAIN              |         |            | CP_I                 | DN       |       | 290810h |

| R40 | R/W | 0  | 1  | 0    | 1  | 0  | 0  | 0  | 0                      | 0                                                                                               | 0      |          |          | CP_IUP        |        |         | CP_         | GAIN      | 0                     | 1       | 1          | 1                    | 0        | 0     | 28101Ch |

| R39 | R/W | 0  | 1  | 0    | 0  | 1  | 1  | 1  | 0                      | 0                                                                                               | SEL -  |          |          |               |        |         |             |           | 2711F0h               |         |            |                      |          |       |         |

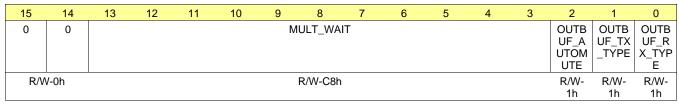

| R35 | R/W | 0  | 1  | 0    | 0  | 0  | 1  | 1  | 0                      | 0 MULT_WAIT OUTBUF OUTBUF OUTBUF OUTBUF AUTO _TX _RX MUTE _TYPE _TYPE                           |        |          |          |               |        |         |             |           |                       | 230647h |            |                      |          |       |         |

| R34 | R/W | 0  | 1  | 0    | 0  | 0  | 1  | 0  | IPBUF<br>DIFF_<br>TERM | F. SE_DIFF XTAL_PWRCTRL XTAL_EN 0 FSK_12S_ FSK_12S_ FSK_LEVEL FSK_DEV_SEL MODE_ MODE_ SEL0 SEL1 |        |          |          |               |        |         |             |           |                       | 221000h |            |                      |          |       |         |

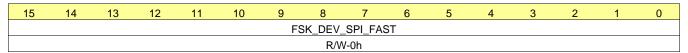

| R33 | R/W | 0  | 1  | 0    | 0  | 0  | 0  | 1  |                        | FSK_DEV_SPI_FAST                                                                                |        |          |          |               |        |         |             |           |                       |         | 210000h    |                      |          |       |         |

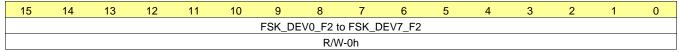

| R32 | R/W | 0  | 1  | 0    | 0  | 0  | 0  | 0  |                        |                                                                                                 |        |          |          |               |        | FSK_    | DEV7_F2     |           |                       |         |            |                      |          |       | 200000h |

| R31 | R/W | 0  | 0  | 1    | 1  | 1  | 1  | 1  |                        |                                                                                                 |        |          |          |               |        | FSK_    | DEV6_F2     |           |                       |         |            |                      |          |       | 1F0000h |

| R30 | R/W | 0  | 0  | 1    | 1  | 1  | 1  | 0  |                        |                                                                                                 |        |          |          |               |        | FSK_    | DEV5_F2     |           |                       |         |            |                      |          |       | 1E0000h |

| R29 | R/W | 0  | 0  | 1    | 1  | 1  | 0  | 1  |                        |                                                                                                 |        |          |          |               |        |         | DEV4_F2     |           |                       |         |            |                      |          |       | 1D0000h |

| R28 | R/W | 0  | 0  | 1    | 1  | 1  | 0  | 0  |                        |                                                                                                 |        |          |          |               |        |         | DEV3_F2     |           |                       |         |            |                      |          |       | 1C0000h |

| R27 | R/W | 0  | 0  | 1    | 1  | 0  | 1  | 1  |                        |                                                                                                 |        |          |          |               |        |         | DEV2_F2     |           |                       |         |            |                      |          |       | 1B0000h |

| R26 | R/W | 0  | 0  | 1    | 1  | 0  | 1  | 0  |                        |                                                                                                 |        |          |          |               |        |         | DEV1_F2     |           |                       |         |            |                      |          |       | 1A0000h |

| R25 | R/W | 0  | 0  | 1    | 1  | 0  | 0  | 1  |                        |                                                                                                 |        |          |          |               |        | FSK_    | DEV0_F2     |           |                       |         |            |                      |          |       | 190000h |

| R24 | R/W | 0  | 0  | 1    | 1  | 0  | 0  | 0  | 0                      | 0                                                                                               | 0      | 0        | 0        | FSK_EN_<br>F2 |        | EXTVCC  | _CHDIV_F2   |           | EXTVCO<br>_SEL<br>_F2 |         |            | OUTBUF_T>            | C_PWR_F2 |       | 180010h |

| R23 | R/W | 0  | 0  | 1    | 0  | 1  | 1  | 1  | 0                      | 0 0 OUTBUF_RX_PWR_F2 OUTBUF                                                                     |        |          |          |               |        |         |             | 1710A4h   |                       |         |            |                      |          |       |         |

| R22 | R/W | 0  | 0  | 1    | 0  | 1  | 1  | 0  |                        | LF_R3_F2                                                                                        |        | (        | CHDIV2_  | F2            | СН     | DIV1_F2 | Р           | FD_DELAY_ | F2                    |         |            | MULT                 | _F2      |       | 168584h |

| R21 | R/W | 0  | 0  | 1    | 0  | 1  | 0  | 1  |                        |                                                                                                 |        | PLL_F    | R_F2     |               |        |         |             |           |                       | PL      | L_R_PRE_F  | 2                    |          |       | 150101h |

| R20 | R/W | 0  | 0  | 1    | 0  | 1  | 0  | 0  | PLL_N_<br>PRE_F2       | FRAG                                                                                            | C_ORDE | R_F2     |          |               |        |         |             | PLL_      | _N_F2                 |         |            |                      |          |       | 140028h |

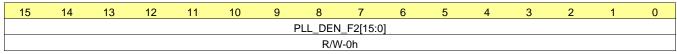

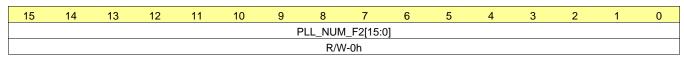

| R19 | R/W | 0  | 0  | 1    | 0  | 0  | 1  | 1  |                        | 1                                                                                               |        |          |          |               |        | PLL_DE  | N_F2[15:0]  |           |                       |         |            |                      |          |       | 130000h |

| R18 | R/W | 0  | 0  | 1    | 0  | 0  | 1  | 0  |                        |                                                                                                 |        |          |          |               |        | PLL_NU  | JM_F2[15:0] |           |                       |         |            |                      |          |       | 120000h |

| R17 | R/W | 0  | 0  | 1    | 0  | 0  | 0  | 1  |                        |                                                                                                 |        | PLL_DEN_ | F2[23:16 | ]             |        |         |             |           |                       | PLL_    | NUM_F2[23: | 16]                  |          |       | 110000h |

Submit Documentation Feedback

Copyright © 2015–2016, Texas Instruments Incorporated

# **Register Maps (continued)**

| REG | 23  | 22 | 21 2 | 20 1 | 9 1  | 18   | 17 | 16 | 15               | 14       | 13               | 12               | 11            | 10           | 9             | 8             | 7                       | 6                       | 5  | 4     | 3          | 2    | 1       | 0       | POR     |

|-----|-----|----|------|------|------|------|----|----|------------------|----------|------------------|------------------|---------------|--------------|---------------|---------------|-------------------------|-------------------------|----|-------|------------|------|---------|---------|---------|

| -   | R/W |    | AI   | DDRE | SS[6 | 6:0] |    |    |                  |          |                  |                  |               |              |               |               | DATA[15                 | :0]                     |    |       |            |      |         |         |         |

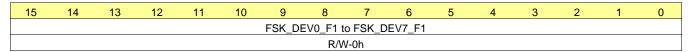

| R16 | R/W | 0  | 0    | 1    | 0    | 0    | 0  | 0  |                  |          |                  |                  |               |              |               | FSK_I         | DEV7_F1                 |                         |    |       |            |      |         |         | 100000h |

| R15 | R/W | 0  | 0    | 0    | 1    | 1    | 1  | 1  |                  |          |                  |                  |               |              |               | FSK_I         | DEV6_F1                 |                         |    |       |            |      |         |         | F0000h  |

| R14 | R/W | 0  | 0    | 0    | 1    | 1    | 1  | 0  |                  |          |                  |                  |               |              |               | FSK_I         | DEV5_F1                 |                         |    |       |            |      |         |         | E0000h  |

| R13 | R/W | 0  | 0    | 0    | 1    | 1    | 0  | 1  |                  |          |                  |                  |               |              |               | FSK_I         | DEV4_F1                 |                         |    |       |            |      |         |         | D0000h  |

| R12 | R/W | 0  | 0    | 0    | 1    | 1    | 0  | 0  |                  |          |                  |                  |               |              |               | FSK_I         | DEV3_F1                 |                         |    |       |            |      |         |         | C0000h  |

| R11 | R/W | 0  | 0    | 0    | 1    | 0    | 1  | 1  |                  |          |                  |                  |               |              |               | FSK_I         | DEV2_F1                 |                         |    |       |            |      |         |         | B0000h  |

| R10 | R/W | 0  | 0    | 0    | 1    | 0    | 1  | 0  |                  |          |                  |                  |               |              |               | FSK_I         | DEV1_F1                 |                         |    |       |            |      |         |         | A0000h  |

| R9  | R/W | 0  | 0    | 0    | 1    | 0    | 0  | 1  |                  |          |                  |                  |               |              |               | FSK_I         | DEV0_F1                 |                         |    |       |            |      |         |         | 90000h  |

| R8  | R/W | 0  | 0    | 0    | 1    | 0    | 0  | 0  | 0                | 0        | 0                | 0                | F1            |              |               |               |                         | 80010h                  |    |       |            |      |         |         |         |

| R7  | R/W | 0  | 0    | 0    | 0    | 1    | 1  | 1  | 0                | 0        | 0                |                  | OUTB          | BUF_RX_PV    | /R_F1         |               | OUTBUF<br>_TX_EN<br>_F1 | OUTBUF<br>_RX_EN<br>_F1 | 0  | 0     | 0          |      | LF_R4_F | 1       | 710A4h  |

| R6  | R/W | 0  | 0    | 0    | 0    | 1    | 1  | 0  |                  | LF_R3_F1 |                  |                  | CHDIV2_F      | 1            | CHD           | IV1_F1        | PI                      | FD_DELAY_               | F1 |       |            | MULT | Γ_F1    |         | 68584h  |

| R5  | R/W | 0  | 0    | 0    | 0    | 1    | 0  | 1  |                  |          |                  | PLL_F            | R_F1          |              |               |               |                         |                         |    | PLL   | _R_PRE_F   | 1    |         |         | 50101h  |

| R4  | R/W | 0  | 0    | 0    | 0    | 1    | 0  | 0  | PLL_N_<br>PRE_F1 | FRA      | C_ORDEF          |                  |               |              |               |               | 40028h                  |                         |    |       |            |      |         |         |         |

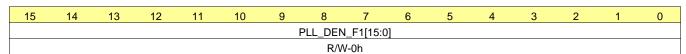

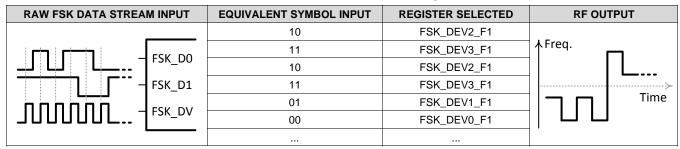

| R3  | R/W | 0  | 0    | 0    | 0    | 0    | 1  | 1  |                  |          | PLL_DEN_F1[15:0] |                  |               |              |               |               | 30000h                  |                         |    |       |            |      |         |         |         |

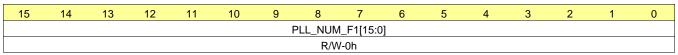

| R2  | R/W | 0  | 0    | 0    | 0    | 0    | 1  | 0  |                  |          |                  | PLL_NUM_F1[15:0] |               |              |               |               | 20000h                  |                         |    |       |            |      |         |         |         |

| R1  | R/W | 0  | 0    | 0    | 0    | 0    | 0  | 1  |                  |          |                  | PLL_DEN_         | F1[23:16]     |              |               |               |                         |                         |    | PLL_N | NUM_F1[23: | 16]  |         |         | 10000h  |

| R0  | R/W | 0  | 0    | 0    | 0    | 0    | 0  | 0  | 0                | 0        | RESET            | POWER<br>DOWN    | RXTX_<br>CTRL | RXTX_<br>POL | F1F2_<br>INIT | F1F2_<br>CTRL | F1F2_<br>MODE           | F1F2_<br>SEL            | 0  | 0     | 0          | 0    | 1       | FCAL_EN | 3h      |

The POR value is the power-on reset value that is assigned when the device is powered up or the RESET bit is asserted. POR is not a default working mode, all registers are required to program properly in order to make the device works as desired.

#### 7.6.1 R60 Register (offset = 3Ch) [reset = 4000h]

### Figure 20. R60 Register

| 15 | 14        | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 1  | 0         | 1  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|    | R/W-4000h |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 1. R60 Register Field Descriptions

| Bit  | Field | Туре | Reset | Description                  |

|------|-------|------|-------|------------------------------|

| 15-0 |       | R/W  | 4000h | Program A000h to this field. |

#### 7.6.2 R58 Register (offset = 3Ah) [reset = C00h]

#### Figure 21. R58 Register

| 15 | 14       | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 1  | 0        | 0  | 0  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|    | R/W-C00h |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# **Table 2. R58 Register Field Descriptions**

| Bit  | Field | Туре | Reset | Description                  |

|------|-------|------|-------|------------------------------|

| 15-0 |       | R/W  | C00h  | Program 8C00h to this field. |

### 7.6.3 R53 Register (offset = 35h) [reset = 2802h]

#### Figure 22. R53 Register

| 15 | 14        | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 1         | 1  | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

|    | R/W-2802h |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 3. R53 Register Field Descriptions

| Bit  | Field | Туре | Reset | Description                  |

|------|-------|------|-------|------------------------------|

| 15-0 |       | R/W  | 2802h | Program 7806h to this field. |

### 7.6.4 R47 Register (offset = 2Fh) [reset = 0h]

### Figure 23. R47 Register

| 15   | 14 13     | 12 | 11 | 10 | 9 | 8 | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|------|-----------|----|----|----|---|---|---|--------|---|---|---|---|---|---|

| 0    | DITHERING | 0  | 0  | 0  | 0 | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W- | R/W-0h    |    |    |    |   |   |   | R/W-0h |   |   |   |   |   |   |

| 0h   |           |    |    |    |   |   |   |        |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### **Table 4. R47 Register Field Descriptions**

| Bit   | Field     | Туре | Reset | Description                                                                                                                                                                                                                                                             |

|-------|-----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    |           | R/W  | 0h    | Program 0h to this field.                                                                                                                                                                                                                                               |

| 14-13 | DITHERING | R/W  | Oh    | Set the level of dithering. This feature is used to mitigate spurs level in certain use case by increasing the level of randomness in the Delta Sigma modulator, typically done at the expense of noise at certain offset.  0 = Disabled 1 = Weak 2 = Medium 3 = Strong |

| 12-0  |           | R/W  | 0h    | Program 0h to this field.                                                                                                                                                                                                                                               |

# 7.6.5 R46 Register (offset = 2Eh) [reset = 1Ah]

### Figure 24. R46 Register

| 15 | 14      | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2                    | 1    | 0    |

|----|---------|----|----|----|----|---|---|---|---|---|---|---|----------------------|------|------|

| 0  | 0       | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 1 | 1 | VCO_<br>SEL_S<br>TRT | VCO. | _SEL |

|    | R/W-1Ah |    |    |    |    |   |   |   |   |   |   |   |                      |      |      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# **Table 5. R46 Register Field Descriptions**

| Bit  | Field        | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                       |