NTD-25333 CR/02491:

Contract No. NAS8-24900

M&S Computing Report No. 69-0002

Prepared for the

NASA MSFC Astrionics Laboratory Technology Division Marshall Space Flight Center, Alabama

FINAL REPORT

"FEASIBILITY STUDY AND ANALYSIS OF THE USE OF COMPUTERS

TO PREPARE MONOLITHIC INTEGRATED CIRCUITS FOR CSE"

CASE FILE COPY

Prepared by:

Approved by:

M&S Computing, Inc. Huntsville, Alabama

July 3, 1969

# ABSTRACT

7

At the request of NASA MSFC, M&S Computing, Inc. has conducted a study on a conceptual approach for performing computer assisted MOS FET Circuit Design; the objective of the study being to develop the functional design of a baseline package which will provide for the computer assisted design of the photographic masks necessary for circuit fabrication. This report presents the software functional design and the system configuration required to implement this software. Both the software and system configuration are evaluated in terms of performance capabilities and future growth potential.

# TABLE OF CONTENTS

. \*

| Part |      |                                                         | Page No. |

|------|------|---------------------------------------------------------|----------|

|      | ABST | RACT                                                    | i        |

|      | TABI | LE OF CONTENTS                                          | ii       |

| ·.   | REFE | ERENCES                                                 | v        |

| I    | PROE | BLEM DEFINITION                                         | I-1      |

|      | 1.1  | Introduction                                            | I-1      |

|      | 1.2  | Computer Task Study                                     | I-1      |

|      | 1.3  | Industrial Survey                                       | I-3      |

|      | 1,4  | System Configuration Study                              | I-3      |

| п    | INDU | STRIAL SURVEY                                           | II-1     |

|      | 2.1  | Introduction                                            | II - 1   |

|      | 2.2  | Graphics Oriented Systems                               | II-1     |

|      | 2.3  | Banning                                                 | II-3     |

|      |      | 2.3.1 Functional Description                            | II-3     |

|      |      | 2.3.1.1 Placement-Routing-Folding<br>PRF Program        | II-3     |

|      |      | 2.3.1.2 Artwork Program                                 | II-4     |

|      |      | 2.3.1.3 MOS Logic Block Simulator                       | II-4     |

|      |      | 2.3.1.4 Signal Trace and Transient<br>Analysis Programs | II-5     |

|      |      | 2.3.2 Advantages and Disadvantages                      | II-5     |

| Part        |                                                                               | Page No.    |  |  |

|-------------|-------------------------------------------------------------------------------|-------------|--|--|

| III         | SYSTEM CONFIGURATION STUDY                                                    | III-1       |  |  |

|             | 3.1 Introduction                                                              | III-1       |  |  |

|             | 3.2 Dedicated System (SDS 930)                                                | III-1       |  |  |

|             | 3.3 Large Scale System (Univac 1108)                                          | III-3       |  |  |

| IV          | STUDY CONCLUSIONS                                                             | ÍV-1        |  |  |

|             | 4.1 NASA Operation                                                            | IV-1        |  |  |

|             | 4.1.1 Current Intentions                                                      | IV-1        |  |  |

|             | 4.1.2 Potential Problem Areas                                                 | IV-1        |  |  |

|             | 4.2 Importance of Graphics                                                    | IV-3        |  |  |

|             | 4.3 Recommendations                                                           | IV-3        |  |  |

|             | APPENDIX                                                                      |             |  |  |

|             | A DESIGN CONCEPT FOR COMPUTER CONTROLLE<br>MOS FET CIRCUIT ARTWORK GENERATION | D           |  |  |

| <b>A.</b> 1 | INTRÓDUCTION                                                                  | <b>A-1</b>  |  |  |

| A. 2        | CURRENT OPERATION                                                             | A-2         |  |  |

| A. 3        | MOS DESIGN FUNDAMENTALS                                                       | A-4         |  |  |

|             | A.3.1 MOS Cell Specification                                                  | A-5         |  |  |

|             | A.3.2 Chip Circuit Specification                                              | <b>A-13</b> |  |  |

| <b>A.</b> 4 | MAN/COMPUTER INTERFACE                                                        | <b>A-16</b> |  |  |

| A. 5        | PROCESSOR REQUIREMENTS                                                        | <b>A-31</b> |  |  |

|             | A.5.1 Introduction                                                            | <b>A-31</b> |  |  |

|             | A. 5.2 Circuit Data Set                                                       | A-35        |  |  |

|             | A.5.2.1 The Cell/Pad Table      | · A-35       |

|-------------|---------------------------------|--------------|

|             | A.5.2.2 The Node Working Table  | <b>A-3</b> 6 |

|             | A.5.2.3 Circuit Schematic File  | <b>A-4</b> 0 |

|             | A. 5. 3 Mask Data Set           | A-40         |

|             | A. 5. 4 Element Dictionary      | A-42         |

|             | A.5.5 Element Library           | A-42         |

|             | A.5.6 Circuit Library           | A-42         |

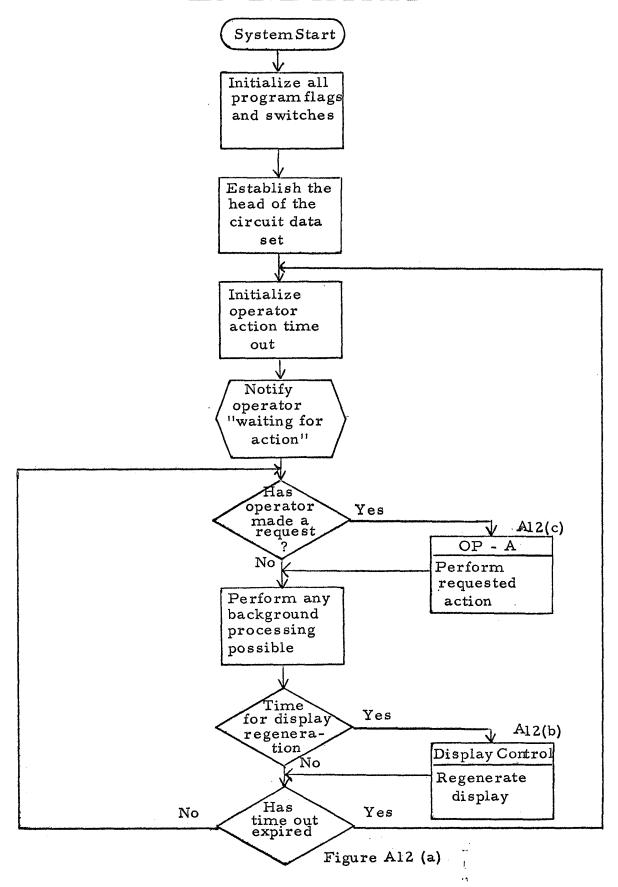

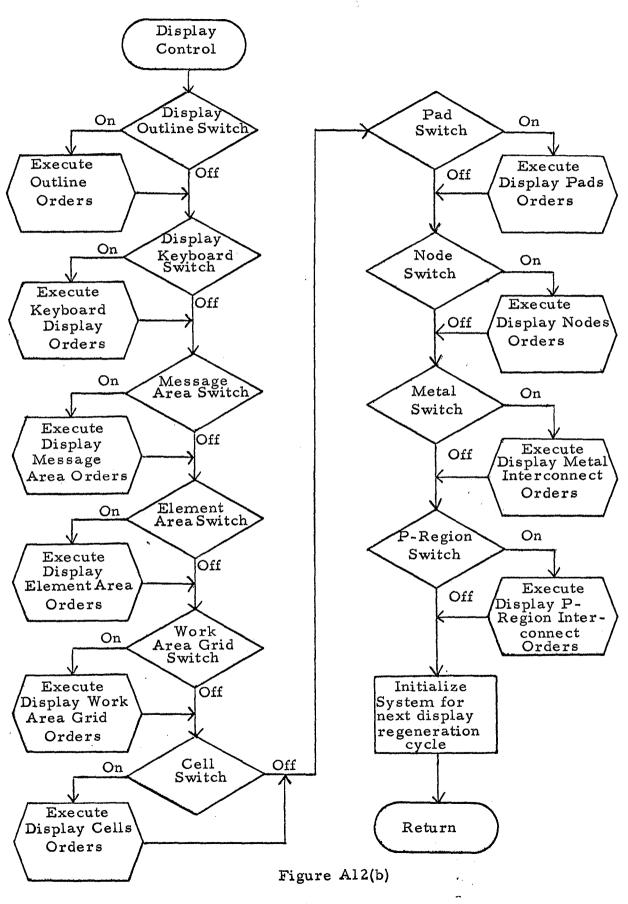

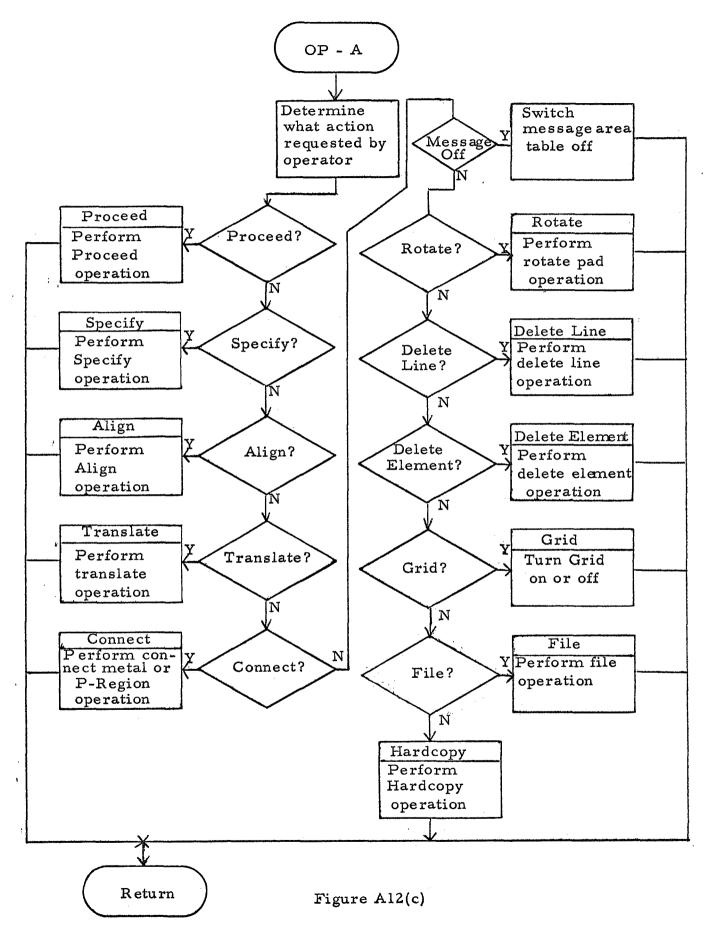

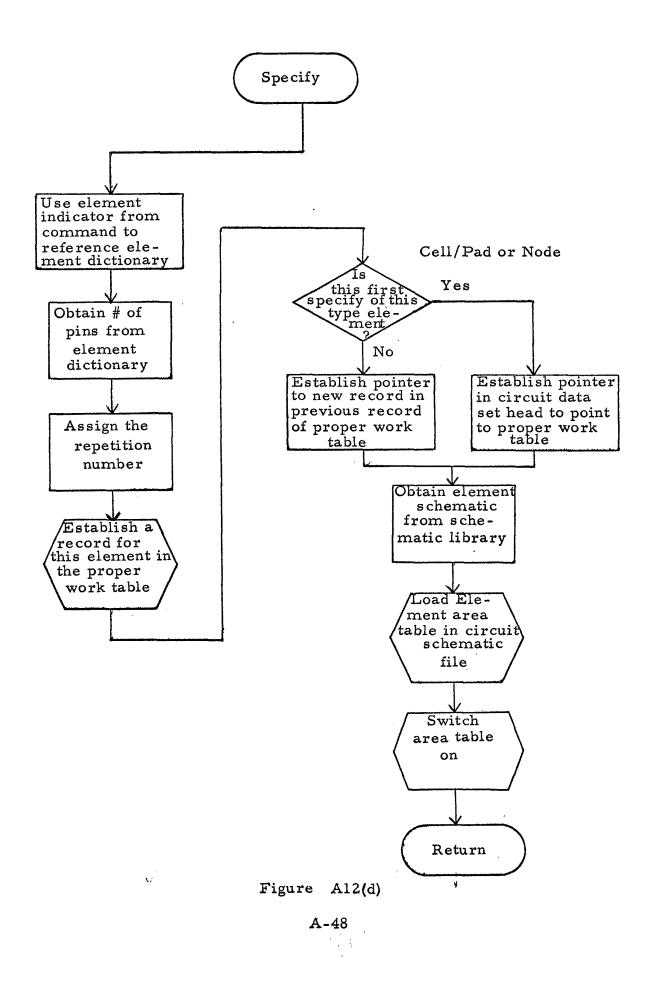

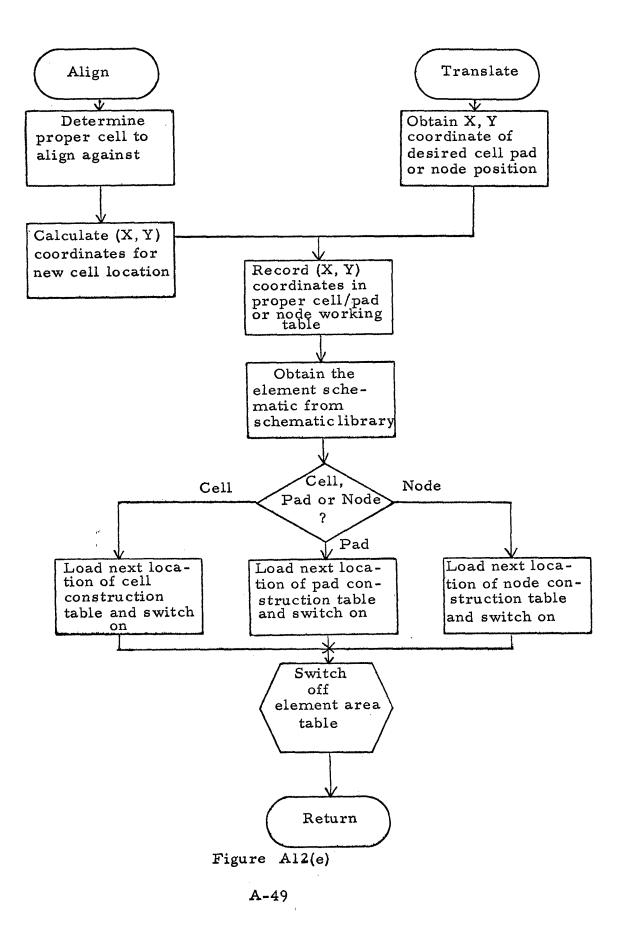

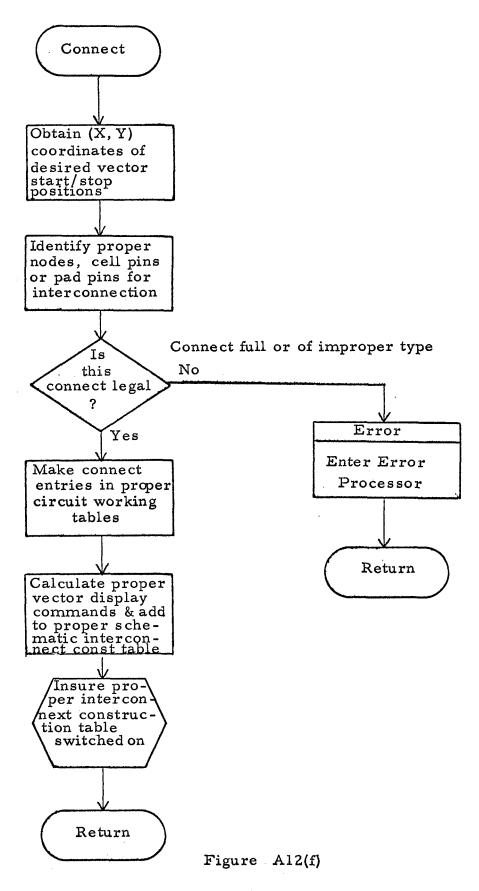

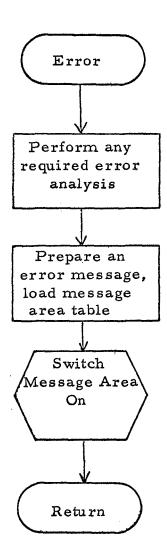

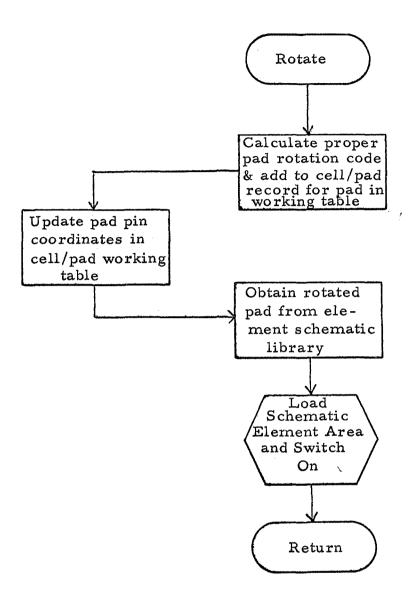

|             | A.5.7 Functional Flow Charts    | <b>A-4</b> 4 |

|             | A.5.8 Software Statistics       | <b>A-4</b> 4 |

| <b>A.</b> 6 | OUTPUT REQUIREMENTS             | A-69         |

| A.7         | COMPUTER TASK STUDY CONCLUSIONS | A-70         |

#### REFERENCES

- H. B. Baskin and S. P. Morse, "A Multilevel Modeling Structure for Interactive Graphic Design", IBM Systems Journal, Vol. 7 Numbers 3 and 4, 1968.

- 2. Philco-Ford, "MOS Design Fundamentals Handbook."

- 3. Philco-Ford Corporation, "MOS Monolithic Subsystems: A Revolution in Microelectronics", 1966.

- 4. General Instrument, "MOS LSI Design Manual."

- 5. Scientific Data Systems, "SDS 930 Computer Reference Manual," 90-00-64E, February 1967.

- 6. Scientific Data Systems, "SDS CRT Display System," Production Bulletin 64-27-01B (Rev 1), 9/15/65.

- 7. Scientific Data Systems, "SDS 925/930/9300 Input-Output Interface Design Manual," SDS 900561A, December 1965.

- 8. Scientific Data Systems, "SDS Symbol and Meta-Symbol," Reference Manual 90-05-06F, August 1967.

- 9. Sperry Rand Corporation, "Univac 1108 Multi-Processor System," System Description, 1968.

- 10. Dertouzou, "Circal: On-Line Circuit Design," IEEE Proceedings, Vol. 55, No. 5, May 1967, pp. 637-654.

- Bryden, Joseph E., "Design Considerations for Computer Driven CRT Displays," Computer Design Magazine, March 1969, pp. 38-46.

- Lee, C. Y., "An Algorithm for Path Connections and Its Applications", IEEE Proceedings, Volume EC-10, Number 3, September 1961.

- 13. IBM, "ECAP: Electronic Circuit Analysis Program," April 1967.

- A. Spitalny and M. J. Goldberg, "CADIC: Computer Aided Design of Integrated Circuits", IEEE Proceedings, Volume 55, Number 11, November 1967, pp. 1982-1988.

- Fairchild-Semiconductor, "Micromosaic Arrays...

An MOS Approach to Custom LSI".

- 16. C. M. Oualline, L. F. McCalla, P. Englebretson, and S. P. Rhodes, "Glad: A System Approach to Artwork Generation", Proceedings of the SHARE-ACM-IEEE Design Automation Workshop, June 1969, pp. 403-414.

- Hightower, David W., "A Solution to Line Routing Problems on the Continuous Plane", Proceedings of the SHARE-ACM-IEEE Design Automation Workshop, June 1969, pages 1 24.

- National Security Agency, "Standard Cell Engineering Note Book", February 1969.

- Applied Research Defense Electronic Products, Radio Corporation of America, Contract: DA-18-119-AMC-03460(X), "BANNING: User's Guide for Placement --Routing -- Folding Program", September 1967.

- 20. Applied Research Defense Electronic Products, Radio Corporation of America, Contract: DA-18-119-AMC-03460(X), "BANNING: Programmer's Manual for Artwork Program", August 1967.

- Applied Research Defense Electronic Products, Radio Corporation of America, Contract: DA-18-119-AMC-03460(X), "BANNING: User's Guide for Signal-Trace Program", August 1967.

- 22. Applied Research Defense Electronic Products, Radio Corporation of America, Contract: DA-18-119-AMC-03460(X), "BANNING: User's Manual for Artwork Program", August 1967.

# PART I

### PROBLEM DEFINITION

### 1.1 INTRODUCTION

M&S Computing, Inc. has been conducting a study for the NASA MSFC Astrionics Laboratory, Technology Division, on a conceptual approach for performing computer assisted MOS FET Circuit Design. The study effort was conducted to satisfy the following primary objectives:

- (1) To confirm the feasibility of performing computer assisted MOS FET Circuit Design on a system available to NASA MSFC, and

- (2) To develop the functional design of a baseline package which will provide for the computer assisted design of the photographic masks necessary for circuit fabrication.

To meet these objectives it was necessary to develop, during the course of this study, the standardization groundrules and the man/computer communication interface applicable to this application. Realistic system constraints were established by orienting the baseline approach towards the SDS 930 computer, which NASA MSFC had indicated was a potential small system candidate for performing this task.

The study effort was broken into the following three logically sequential study phases.

# 1.2 COMPUTER TASK STUDY

The first phase consisted of a definition and evaluation of the explicit functions that the computer would be required to perform during the circuit design task. This phase was relatively machine independent and consisted primarily of a determination of the desired man/computer interface, a functional definition of the application software, and a formalization of the necessary output requirements. Since NASA MSFC had expressed an explicit interest in a system oriented about a graphics terminal which would provide the designer/engineer with a real time circuit design tool, M&S Computing placed special emphasis on defining a concept which provided for a graphics terminal to establish efficient two-way communication between the designer and the system.

To effectively estimate the graphics software requirements, a study was made of the current design and manufacturing procedure employed by NASA MSFC to produce MOS FET circuits. Particular attention was payed to the average chip device densities. Since the complexity of the graphics problem is directly related to the circuit complexity, it was necessary to define a "worst case" circuit in order to realistically bound the graphics requirement. A standard "worst case" or most complex circuit was defined by NASA MSFC which consisted of the following elements:

> 30 standard cells with up to 100 devices total 18 bonding pads 100 contact nodes 210 normal nodes

The computer task study resulted in the functional definition of a baseline software system, oriented around a graphics terminal, and designed to provide computer assisted MOS FET circuit design on a small dedicated system. The conclusions arrived at during this phase of the study are presented in detail in the attached Appendix, "A Design Concept for Computer Controlled MOS FET Circuit Artwork Generation." This Appendix should serve as a valuable reference and guidance document if such a system is implemented.

In particular, the Appendix presents a detailed discussion of:

- 1. The current NASA MSFC operations.

- 2. The standardized placement and interconnect groundrules established during the study phase.

- 3. The designer/computer communication interface both with and without a graphics terminal.

- 4. The functional design of the baseline software, including flowcharts, and

- 5. The processor requirements which include initial storage estimates and input/output requirements.

All of the storage estimates contained within the Appendix have been based on the "worst case" circuit described above.

# 1.3 INDUSTRIAL SURVEY

The second phase of the study effort consisted of a limited industrial survey which was conducted in order to evaluate the work that has been done in the field of computer aided circuit design and analysis. As a result of an expressed NASA MSFC interest, the survey was concentrated in two distinct areas. First, a review was conducted of a selected set of industrial packages which utilize a graphics terminal to support various phases of the automated circuit design and analysis process. Secondly, the BANNING Program, which is available from the National Security Agency, was evaluated in relation to NASA MSFC requirements.

The results of the Industrial Survey are discussed in Section II of this report.

### 1.4 SYSTEM CONFIGURATION STUDY

The third and final phase of this study effort consisted of the development of a recommended system hardware configuration and an analysis of the operational efficiency and limitation of the baseline software, presented in the Appendix, on the designated system. The UNIVAC 1108 Computer was evaluated to provide a comparison between the simple baseline approach used in defining the SDS 930 System configuration and the typical large scale approach used in industry. The UNIVAC 1108 is a large scale general purpose system which is currently being utilized by the NASA MSFC Computation Laboratory. Since this system is available to the Astrionics Laboratory Technology Division, it is a logical candidate for this task.

The results of the System Configuration Study are presented in Section III of this document.

Section IV of this document contains a concise summation of the conclusions arrived at during the course of this study effort and the recommendations being made by M&S Computing, Inc.

# PART II

#### INDUSTRIAL SURVEY

# 2.1 INTRODUCTION

In order to determine the "state-of-the-art" and to be able to isolate trends within the field of computer aided circuit design and analysis, M&S Computing conducted a limited survey of industrial software systems. Some of the system reviewed required more than 200K of on-line storage in which to operate. These software packages may seem unduly large and complex, but as the engineer begins working with more complex circuits, he requires all the support capability available to solve interconnection problems and perform detailed circuit analysis.

Since NASA is considering implementing the BANNING Program developed by the National Security Agency, special emphasis was placed on developing a functional knowledge of this program in order to be able to evaluate the program in terms of applicability to current NASA requirements.

Due to the increased interest in real time circuit design capabilities and the additional program control provided by interactive graphics, the graphics terminal is playing an important role in industrial applications. During this survey special emphasis was placed on reviewing large industrial applications that provide graphics capabilities in order to determine the present and future role of graphics within the field of integrated circuits.

#### 2.2 GRAPHICS ORIENTED SYSTEMS

The primary advantage of an on-line graphic display is that the user is able to quickly and easily interact with the program. It is apparent that there is a definite trend toward providing interactive graphics to facilitate circuit design, improve circuit development time, and optimize circuit performance. The software systems listed below have been developed by industry due to user demands for increased use of computer graphics to enhance the man-machine inter face.

- CIRCAL: On-Line Circuit Design (Massachusetts Institute of Technology)

- CADIC: Computer Aided Design of Integrated Circuits (United Aircraft Corporation)

- EACP: Electronic Circuit Analysis Program (International Business Machines Corporation)

MICROMOSAIC (Fairchild Semiconductor)

Each of these programs was investigated during the course of this study effort because of their use of computer graphics to provide a real time graphics capability. Since detailed information on each of these systems is readily available to the reader, they have not been described in detail.

As software systems grow in size and complexity to provide the utmost capabilities in circuit design, analysis, routing, and artwork generation, they require larger computer resources than can be economically and realistically provided by a dedicated computer. However, large computer facilities must maintain a relatively free general computing capability and must remain available to many users for various applications. The graphics terminal which interfaces with a time-shared computer system allows the man-machine communication demanded by the designer/engineer without restricting the computer's capability of servicing other user requests.

The amount of software required to support interactive graphics depends on the complexity of the circuits being developed. As the circuits grow in complexity, the circuit schematic and mask graphic data may increase to such an extent that the display hardware is unable to present the entire circuit effectively. When this situation occurs, errors begin to increase due to free-hand handling of the light pen when specifying component locations and interconnections. This problem is common among users utilizing computer graphics as a circuit design tool, and software capabilities have been developed to correct the problem by using a "window", "zoom", or "scroll" concept for displaying only the section of the circuit in which the designer is interested. While the actual technique of implementation is different for each of these three concepts, they each effectively scale the graphic image on an imaginary surface far larger than that provided by the terminal screen. The software required to provide a preliminary graphic design capability and a basic user oriented design language needed for effective designer/machine communication are presented in the Appendix of this report. This software was functionally defined as part of a baseline system designed to solve the immediate requirements of the NASA MSFC Astrionics Laboratory Technology Division, but is capable of being expanded to serve as the basic software requirement for a large scale system accessed from a remote graphics terminal.

### 2.3 BANNING

The Banning Design Automation System consists of five major programs and a standardized cell pattern library which provides for the design of MOS-FET circuits using standardized thick-oxide P-MOS building blocks or "cells." The five major Banning Programs are briefly described below.

### 2.3.1 Functional Description

The first two of the five programs are required to translate the detailed logic design into the precision MOS-FET photographic masks required to manufacture the desired circuits. The remaining three programs provide the analytical capability necessary to evaluate the performance of basic circuit and logic nets.

# 2.3.1.1 Placement-Routing-Folding (PRF) Program

The PRF Program is responsible for performing final cell placement on the chips and component signal interconnection routing. The final placement of the individual cells on the chips is governed by the computer which is responsible for establishing a placement which results in suitable minimum total wire lengths for interconnecting the array. Once cell placement has been completed, the signal interconnections are routed using both metal pathways and P-region tunnels.

The input data cards for the PRF Program are in the same format as those utilized by the logic block simulator. The PRF Program pre-processes the input data and converts it for its own needs. The common input format reduces the possibility of errors being introduced when proceeding from the circuit analysis phase to the placement, routing, and artwork generation phase. The PRF Program capability is a function of the computer's memory size. For example, the GE 625 System appears to be able to handle arrays of more than 150 cells. (A bonding pad is counted as a cell.)

£

The output available from the PRF Program consists of the following four items:

- (1) Two types of capacitance loading data (before and after routing).

- (2) A folded array printout showing chip size, cell locations, cell orientation, and type.

- (3) A printout of the predicted speed performance of the array as determined by the Signal-Trace Program.

- (4) A listing of the PRF Program output specifications, cell locations; orientations, signal interconnects, and parallel bus and bonding pad locations.

### 2.3.1.2 Artwork Program

The Artwork Program generates the commands required by the Gerber Plotter to draw the desired artwork. The program output is a magnetic tape which contains the light aperture and motion commands which control the operation of the plotter. The topology data for the standard cells required by the program are available from the Banning cell pattern library.

The Artwork Program also performs certain housekeeping functions such as updating the library tape and formulating Gerber instructions for drawing standard cell composites from digitized cell data.

#### 2.3.1.3 MOS Logic Block Simulator

The Logic Block Simulator is a self-contained program designed to simulate the binary logic system of interconnected MOS-FET standard cells. The program is driven from card inputs which describe the cell types comprising the circuit along with cell characteristics and interconnection information. The primary output consists of columnized 0's and 1's which represent the outputs of specific cells as they exist at the end of Phase I or Phase II clock times. The run limitation is a function of the number of output columns available on the line printer.

## 2.3.1.4 Signal Trace and Transient Analysis Programs

The Signal Trace Program operates as a subroutine of the PRF Program and provides a highly accurate time analysis prediction for the desired array.

The Transient Analysis Program is used to evaluate the response times of the basic Banning cells.

Since this report is not concerned with circuit analysis, the above descriptions are deliberately sketchy. If additional information on these programs is desired, the reader is directed to the detailed Banning Software Documentation.

### 2.3.2 Advantages and Disadvantages

The Banning package is a sophisticated, large scale, batch processing oriented, design automation system which contains extensive capabilities for performing automated circuit design, analysis, and artwork generation. The capabilities are ideally suited for the design engineer who wishes to develop large scale MOS FET arrays with an emphasis on circuit analysis. A large pattern library of standardized cells simplified the design task, and a set of well standardized operating definitions allow the computer to relieve the designer of much of the tedium associated with the design process. In particular, the computer will perform for the designer automatic component placement, signal interconnection routing, and array interconnection. In addition, Banning supplies a number of analytical tools which allow the engineer to effectively analyze the predicted performance of his design.

In spite of the extensive capabilities of the Banning System, a number of limitations do exist which restrict the usefulness of the system in the highly R&D oriented atmosphere of the NASA MSFC Astrionics Laboratory, Technology Division operation.

The major limitation is the lack of a graphics terminal capability which would allow the designer to control, on line, the design and analysis processes, and to actively participate in the design, placement, and routing operations with the computer. As stated earlier, the current trend in industry is to develop real time design automation systems in which the man and the computer complete the design process during an interactive on-line dialogue. The use of such graphics terminal systems allows the engineer to monitor his design through the entire development cycle and to make modifications or corrections as desired.

Two other limitations exist which are only minor in nature and could be easily corrected:

- (1) No punched tape output currently exists from the Artwork Generation Program. Such a tape must be generated in order to drive the NASA Gerber Plotter.

- (2) No preliminary plotter output of the circuit masks is provided prior to using the Gerber. Such an output on an inexpensive plotting device, such as one of the smaller Cal Comp machines, would prove valuable in verifying the mask design prior to actual generation, and could considerably reduce wasted Gerber operation.

# PART III

### SYSTEM CONFIGURATION STUDY

#### 3.1 INTRODUCTION

The System Configuration Study was designed to identify the minimum realistic definition of the system hardware configuration required to perform the designated task while allowing for a reasonable growth potential. In defining a system configuration for computer aided circuit design, all systems from the large multi-processor time sharing system to the small "in house" dedicated computer must be considered.

The final system configuration must be chosen on the basis of the task requirements, the desired level of growth potential, and the user's availability requirements. There are advantages in developing an "in house" system that is closely monitored by the engineer responsible for its application; however, if the future expectations of the system require extensive circuit design and analysis capabilities, care must be taken to provide a system configuration that will permit the necessary growth required. If such growth is to be extensive, a large scale system may be necessary from the start.

# 3.2 DEDICATED SYSTEM (SDS 930)

The baseline software requirements presented in the Appendix of this report are developed around a small "in house" system configuration. However, care has been taken to insure that a large scale development could be implemented as a logical extension of this baseline package.

The small dedicated system can provide many advantages to both the programmer and user. Some of the more obvious advantages are listed below:

- o Implementation is easier.

- o Closer programmer/engineer communication.

- o Engineers work directly with the computer.

#### o Immediate turnaround time.

Fast turnaround time, on-line debugging, and fewer system constraints facilitate and accelerate the development of software packages for a small dedicated computer. Such a system will establish and enhance a close communication between the engineers and programmers, resulting in a better system performance and confidence. Since turnaround time has been identified as a major problem with the current operation, the availability of a small system is a key advantage of a computer dedicated to the support of one project.

The basic system configuration presented in this section is small enough to be readily available as a design tool, and is also capable of significant expansion in order to handle the future requirements of the designer/engineer.

The minimum SDS 930 hardware configuration needed to effectively provide a real time circuit design tool should consist of the following elements:

- o SDS 930 Central Processing Unit

- o 16,000 Word Memory

- o Graphic Display Terminal

- o Disc

- o Card Reader

- o Magnetic Tape Unit

The SDS 930 is a high speed, low cost, general purpose digital computer, ideally suitable for use in a system dedicated to the support of one project. The computer is fast enough to provide the necessary response time needed to drive a real time circuit design system, and large enough to support significant growth potential. With an extensive overlay structure, the baseline software system could be implemented in an 8K memory; however, this would considerably complicate software implementation and would severely restrict the system growth potential and versatility. A 16K storage capability will result in the best overall systems performance and will simplify implementation. The high speed direct access capabilities of the disc are necessary due to the fast response time demanded by the display terminal. The entire task of computer aided circuit design is primarily concerned with data manipulation and organization. The major percentage of the off-line storage provided by a disc will be devoted to the data tables needed for circuit schematics and mask definition. As the circuit development passes from the real time design phase into the mask creation phase, I/O response time becomes less important permitting the use of magnetic tape as both intermediate storage and as the final output medium for the circuit masks.

The card reader provides the necessary input device to communicate with the system assembler and to handle the large amount of data required to create and update the data tables on disk. If the system does not contain an interactive graphics display, the circuit design commands may also be entered by cards.

The basic design language developed in the Appendix of this report is compatible with both standard batch type job input and control, as well as with an interactive graphics capability. The developed system should be highly user oriented and should provide efficient designer/computer communication. A graphics capability simplifies the communication between the engineer and the computer, and places the designer in direct control of the development of his circuit. Without the graphics capability, the designer loses a powerful design tool and the system reverts to batch oriented operation.

### 3.3 LARGE SCALE SYSTEM (UNIVAC 1108)

The software available today that can be used for automated circuit design, analysis, routing, and artwork generation exceeds by far the capability of a small computer. These capabilities are natural extensions of a small scale circuit design system and should be carefully considered as possible future applications before committing to the development of a less sophisticated system.

The UNIVAC 1108 System presently in use at Marshall's NASA Computational Laboratory is capable of supporting the most sophisticated circuit design software currently available in industry for the preparation of monolithic integrated circuits. The UNIVAC 1108 System is a large-scale data processing system that features multiprogramming and multi-processing capabilities for high performance. The cost, performance, and availability of the 1108 system prohibits its use as a dedicated computer to a project of this size. However, by incorporating a remote graphics terminal capability within the system, the designer/engineer would have both the capabilities of a large scale system and the availability of a dedicated computer. This arrangement would provide an unquestionable "best system" as future growth potential would be practically unlimited and turnaround time would be near optimum.

The cost of both the hardware and software required to provide graphic terminals has previously prohibited the large scale use of interactive graphics as the solution to the man/machine communication problem. A graphics terminal which provides sufficient capability for permitting computer assisted MOS FET circuit design and system software of the magnitude needed to support such terminals in a time shared environment is costly and would have to be developed in a general package to support many terminal users. Large scale systems which service many users invariably operate in a multiprogramming environment in order to effectively use central processor time during the delays inherent in servicing I/O requests. If the same system is to support terminals, additional software must be developed to provide a "demand" (priority) processing mode to establish productive "conversation" between the terminal and the computer.

The UNIVAC 1108 System currently in use at the NASA MSFC Computational Laboratory provides a graphics terminal capability. Several UNIVAC 1558/1557 Graphics Terminals have been placed in various locations within the NASA MSFC Facility, and are presently supported for on-line user applications. The UNIVAC 1108 system software is oriented toward maximizing the throughput of batch operations, while providing the capability for handling useful amounts of real time and demand processing. The system software, however, is of a general nature and must be supplemented by user software to be able to interpret the operator action and determine the required response. As explained in Section II of this report, the user-oriented graphic software required to provide an interactive graphics capability is proportional to the complexity of the circuits being designed. The generation of the additional application software required to utilize the existing graphics terminal will not be a minor problem. Graphics packages

**III-4**

can become extremely complex, especially if extensive operator flexibility and control must be provided. However, the advantages of such a graphics package, when considered in the light of the benefits provided by terminal operations, make it essential that such a system be seriously considered. Without the remote graphics terminal, the UNIVAC 1108 becomes unavailable for on-line, realtime circuit design, but retains the capability of employing the most up-to-date developments in the preparation of integrated circuit masks.

### PART IV

# STUDY CONCLUSIONS

The final system configuration must be chosen on the basis of the task requirements, the desired level of growth potential, and the user's availability requirements. The baseline software developed during this study is well suited for the SDS 930 system configuration presented in Part III. If a small dedicated system is desired, the SDS 930 configuration is large enough to perform the specified task and to provide a reasonable growth potential. However, if a graphics terminal is available for the 1108, it is unquestionably the more desirable system for performing automated artwork generation. This is especially true if future plans for the system require an extensive circuit design and analysis capability.

# 4.1 NASA OPERATION

## 4.1.1 Current Intentions

NASA MSFC is currently actively engaged with the evaluation and preliminary implementation of the Banning System. Tentative plans call for initially implementing the Artwork Program in order to establish a minimum production oriented capability to be followed later by the addition of the other Banning System components in a building block sequence. The overall objective appears to be to provide the full capabilities of the Banning System to NASA MSFC but in a sequence which allows the artwork generation capability to be available for use as quickly as possible.

Preliminary estimates indicate that approximately 1 - 3 months of effort will be required to make the Artwork Program operational at the Huntsville Facility if no serious complications are encountered. Inputs for the initial artwork system will probably have to be hand generated since the PRF Program will not be operational initially.

#### 4.1.2 Potential Problem Areas

A number of potential problems exist with the current NASA proposal for the implementation of the Banning System. In presenting these points, it is not M&S Computing's intention to discourage the use of the Banning System. The system is basically sound and contains extensive desirable capabilities. However, it is imperative that potential problem areas be quickly identified so that the responsible NASA personnel can assess their impact and develop appropriate corrections.

- (1) The original NASA intention was to develop a system to support the designer/engineer during the placement and routine operations of MOS FET circuit design and to eliminate the tedious and time consuming manual operations involved in generating chip artwork. The current operation and its inherent problems are described in Section A. 2 of the Appendix. The current proposal to make the Banning Artwork Program operational will require 1 3 months of effort and will not substantially alleviate the problems associated with the current operation for the following reasons:

- (a) Placement and routing will still have to be done by hand without the PRF Program. In order to digitize the necessary input data for the Artwork Program, the designer will still have to provide a scaled mask drawing which a programmer must then convert to the proper input format. While the full drafting steps of the current operation should not be necessary, significant manual preparation will still be required.

- (b) The Artwork Program cannot directly provide the control paper tape needed to drive the Gerber Plotter. The magnetic tape output of the Artwork Program must be processed by essentially the same program currently used to punch the Gerber paper tape.

- (c) It is unclear yet that the output from the Artwork Program is fully compatible with the Gerber Plotter at MSFC. As long as the deviations are not major, this problem should not be critical.

(2) Since the Banning System does not support a graphics terminal, the system is unavailable for on-line, real time circuit/mask design. Efficient two-way communication between the engineer and the system during the design phase will not be realized.

### 4.2 IMPORTANCE OF GRAPHICS

The NASA MSFC Computational Laboratory and many industrial computer facilities have realized the growing demand to supplement batch processing abilities with the remote terminal capability to provide effective man/machine communication. To allow the computer to completely replace the circuit designer, a multitude of design rules for the design of individual devices and for their interconnection into complete circuits must be established to generalize circuit designing and present the problem in terms applicable to the computer. Experience and subjective reasoning of the experienced designer is lost, freedom of design is greatly restricted, and considerable circuit design efficiency is eliminated in order to restrict designer interaction requirements. If the experienced circuit designer, whose primary interest is experimental design with a maximum emphasis on optimization, is to be provided computer assistance, an interactive graphics capability is highly desirable.

Interactive graphics provides a real time circuit design tool and allows the designer/engineer to specify components and control placement and interconnection modifications. The designer/engineer is able to "review" completed circuits and incorporate late design changes or modifications prior to generating the final artwork.

M&S Computing feels that interactive graphics is essential to the type of research and development work that is performed at the NASA MSFC Facility. Since both the hardware and software are available to provide graphic terminal support on the UNIVAC 1108 system, the amount of effort and expense required to provide the circuit designer with an interactive graphics capability is well worth while in light of the advantages of such a system.

### 4.3 RECOMMENDATIONS

ŧ

In particular, M&S Computing feels that there are a number of distinct recommendations to be made as a result of this study effort:

- (1) A UNIVAC 1558/1557 Graphics Terminal is located in the B Wing of the Astrionics Laboratory. If this system can be made available for this application, the UNIVAC 1108 will provide an unquestionable "best system" for this task since future growth potential would be practically unlimited and turnaround time would be near optimum.

- (2) Immediate emphasis should be placed on developing the complete design of an application, user oriented graphic design language for this task. This language should be capable of supporting both job control and circuit design, analysis, routing, and artwork generation.

- (3) The required graphics application software should be developed in parallel with the implementation of the Banning Artwork Program.

- (4) The Banning Artwork Program will, if coupled to a display terminal, provide a significant improvement in the design and generation of circuit masks. However, the desirability of implementing the full Banning Program should be seriously reviewed. It is not at all clear that the benefits provided by the total Banning System are worth the cost of implementation to the NASA MSFC Facility.

#### APPENDIX

# A DESIGN CONCEPT FOR COMPUTER CONTROLLED MOS FET CIRCUIT ARTWORK GENERATION

# A.1 INTRODUCTION

The Computer Task Study was dedicated to developing a logically consistent and realistic software approach for performing computer assisted MOS FET circuit design. It was conducted with a systems approach in that all aspects of the design sequence were acrutinized and modified if necessary to form an overall approach with mutually compatible components. A considerable amount of effort was spent developing standardization groundrules for:

- (a) Component Designation

- (b) Cell Architecture

- (c) Circuit Architecture, and

- (d) Circuit Component Interconnection

A basic design language was developed which is compatible with both standard batch type job input and control, as well as with an interactive graphics capability. The man/computer communication interface is discussed in detail in Section A. 4.

The software package which was designed as a result of this study effort has been functionally flowcharted and is presented in Section A.5.7. The output capabilities of the proposed system are presented in Section A. 6, along with a discussion of desirable documentation and hard copy requirements.

# A.2 CURRENT OPERATION

The following discussion of current MOS FET design fundamentals is provided to establish a common baseline knowledge and to eliminate any possible confusion caused by the terminology utilized during the subsequent sections of this report. Those individuals fully versed in MOS FET design techniques need not concern themselves with this section.

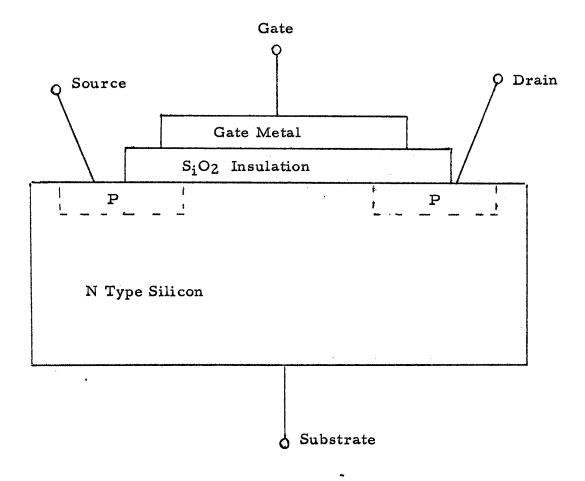

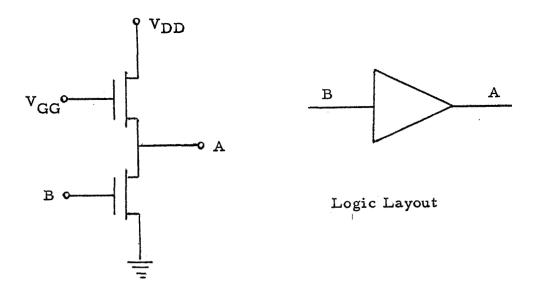

The MOS FET (Metal-Oxide-Silicon Field Effect Transistor) is a solid state device which differs from the ordinary transistor in that it is a voltage amplifier with a very high input impedance and a transfer characteristic similar to that of a pentode vacuum tube. The simplest form of this device is shown in Figure Al, however, the actual layout may vary considerably, depending upon desired device characteristics and the circuit configuration into which the device is designed.

The device considered during this study was a P channel enhancement mode device and consists of a block of N type silicon called the Substrate into which  $P^+$  impurities are diffused in two parallel strips called "the source" and "the drain". The area of N type silicon between the two P area strips is called the channel and becomes an induced P region during operation. The entire surface of the chip is covered by silicon dioxide which is etched down over the P regions and the channel area. A metal gate is deposited over the channel area, separated from it by the oxide. Metal supply lines contact the source and drain through contact cutouts in the oxide.

For a MOS FET circuit in which all devices are made by the same process, the characteristics of each transistor will be controlled primarily by the gate length and width. This feature is of the utmost importance in designing MOS FET devices.

As a first step in actual device fabrication, a thin layer of silicon dioxide is grown on the surface of the silicon wafer. This is followed by four photographic etch steps intermixed with other steps such as impurity diffusion, vacuum metalization, and intermediate layerings with silicon dioxide. The masks for these photographic operations are prepared by the same large scale layout and photo reduction techniques common to the integrated circuit industry.

Figure Al

In the MOS FET circuit (CHIP) fabrication operations used by NASA MSFC, the process of generating the four masks from a given input circuit schematic is a tedious and time consuming manual task. The individual steps in this procedure are listed below:

- (1) A final circuit schematic is defined based on design requirements and breadboard results.

- (2) From the schematic a topological layout is developed. This shows the location and approximate sizes of each device in the circuit along with the interconnections, crossover points, and metal to P-region contacts.

- (3) Next a complete set of scaled mask layouts is developed by a draftsman.

- (4) The scaled mask layouts are used to either manually cut the rubylith which is then photographically reduced to create the actual mask, or to generate an input tape for a gerber plotter which draws the mask to be photographically reduced.

The entire sequence of events listed above, including repetitions required to correct or modify the original design, can take months to complete. It is this design and mask development sequence which can be considerably improved and speeded up by utilizing a general purpose digital computer, preferably with interactive graphics capability, to support the circuit designer and to eliminate the need for an extensive drafting step.

# A.3 MOS DESIGN FUNDAMENTALS

During the course of this study effort, M&S Computing studied two distinct MOS FET design techniques.

The General Instrument's MOS LSI Design Manual describes a free form technique in which a multitude of design rules are established for the design of individual devices and for their interconnection into complete circuits. The rules, in effect, allow the design engineer to custom tailor each device and circuit component to optimize the desired circuit parameters. The GI approach allows a complete freedom of design and is ideally suited for the individual, experienced circuit designer whose primary interest is experimental design with a maximum emphasis on optimization. However, the GI method, because of its total free form approach, is extremely difficult to implement on a computer. Far too many of the design steps in this method are based on intuition, experience, and subjective reasoning.

The second method investigated was a method described by Philco-Ford which allows for the design of large scale arrays with standardized cells. The procedure is similar to breadboarding conventional integrated circuits. The complete circuit is laid out using the standard circuit cells and well defined rules govern component interconnection and circuit geometry. The major concern of the designer with this approach is on optimizing cell interconnects. A functioning circuit can be laid out without considering the order in which blocks feed into each other. However, the number of crossovers and often the chip area as well can be minimized by grouping together, insofar as possible, cells that interconnect. The method described by Philco-Ford is ideally suited to computer assistance.

The primary disadvantage of this technique is that the circuit designer must work with standardized cells, the arrangement and interconnection of which is governed by rigid and formalized rules. This, of course, prevents the designer from completely optimizing all circuit devices and forces him to work with a circuit format somewhat less convenient than his normal schematic.

# A. 3.1 MOS Cell Specification

As stated previously, the Philco-Ford concept of utilizing "building blocks" or standardized cells as circuit components defines a circuit design technique which lends itself well to automation. The techniques presented in this study are based on that concept in an expanded form which liberalizes some of the design rules.

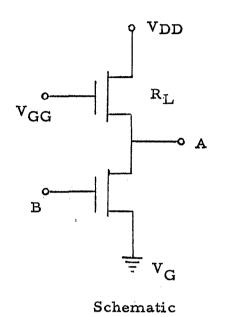

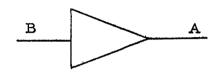

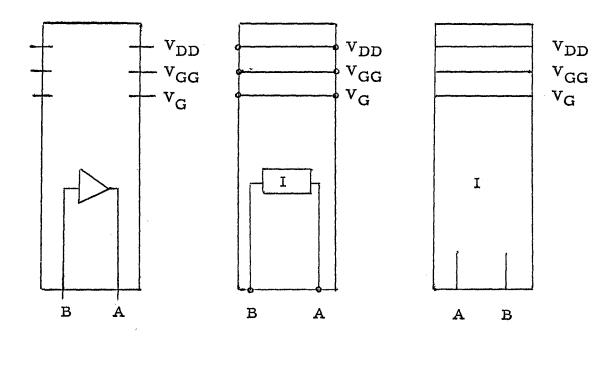

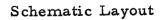

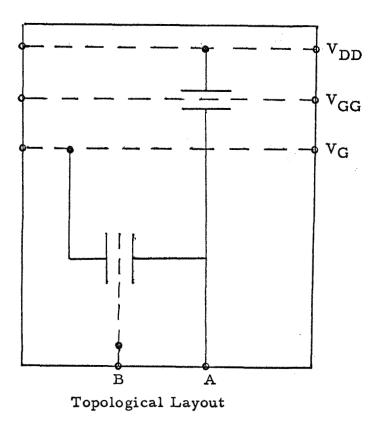

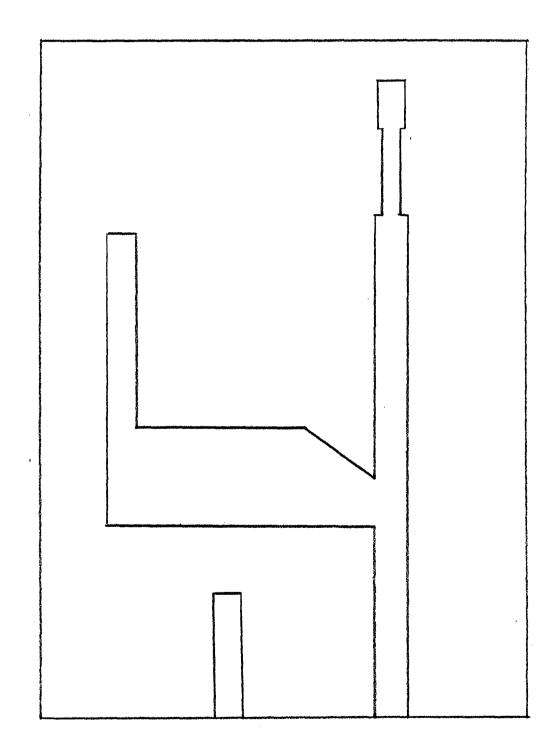

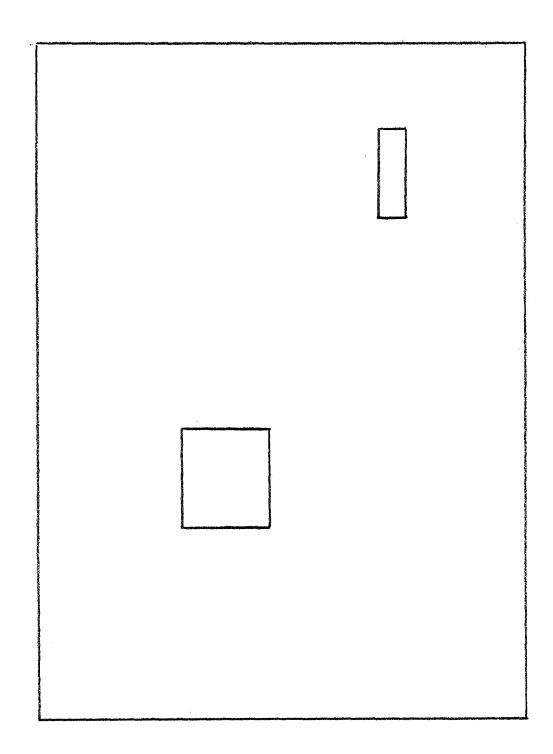

The cell, as defined for this study, is a circuit device or group of devices, including component interconnects which has been established as a standardized circuit element. Examples of cells are inverters, NOR gates, output buffers, one bit shift registers, etc. From the designers viewpoint, a cell consists only of a circuit component with well defined inputs and outputs, operating characteristics, and a symbolic representation. To the computer a cell is considerably different. This can best be demonstrated by an illustration. Figure A2 shows the schematic and logical representation of a MOS FET inverter cell constructed of two devices where  $V_{DD}$  is the drain voltage,  $V_{GG}$  is the gate voltage,  $V_G$  is ground, and A and B are respectively the logical input and output for the cell. Three symbolic layouts for the inverter cell are shown in Figure A3. The primary difference between the various forms is their acceptability for computer representation and the number of data words required to construct each graphically. The particular symbolic layout most compatible with efficient computer storage techniques is shown in Figure A3(c) and will be discussed in detail later.

To construct circuits the designer only needs to know the symbolic representation of the available cells and the rules for component interconnection and circuit geometry. The computer needs to know considerably more.

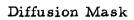

Since the primary objective of the computer is to construct the output tapes required for manufacturing the four fabrication masks, the definition of a cell to the computer consists not only of the cell's symbolic representation but also of its mask representations. A complete cell representation for the basic inverter is presented in Figures A4 through A6. On the topological layout of Figure A4, dashed lines are used to represent metal circuit paths, solid lines represent diffused P-regions except for the cell border, solid dots show connections of metal to P-regions, and small circles indicate cell contact nodes for circuit interconnection. As can be seen by examining Figures A5 and A6, there is an almost direct correspondence between the solid lines on the topological layout and the diffusion mask, the dashed lines and the metalization mask, and the solid dots and the contact mask.

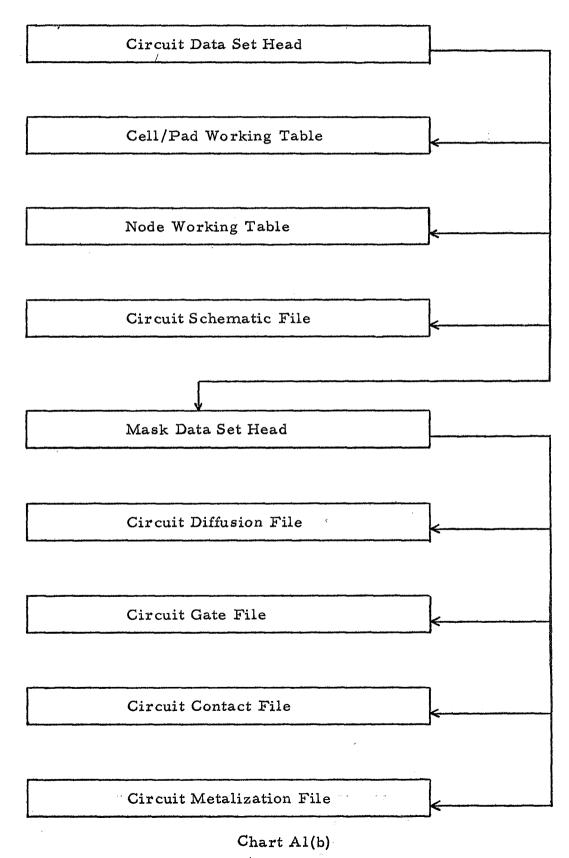

The cell representation is maintained in the computer storage area as a data set of points and vectors. Each of the four masks and the symbolic representation of the cell is stored independently and computer cell definition is synonymous with the five data tables that make up the cell's data set. A detailed description of these data tables and their use is presented in Section A. 5.

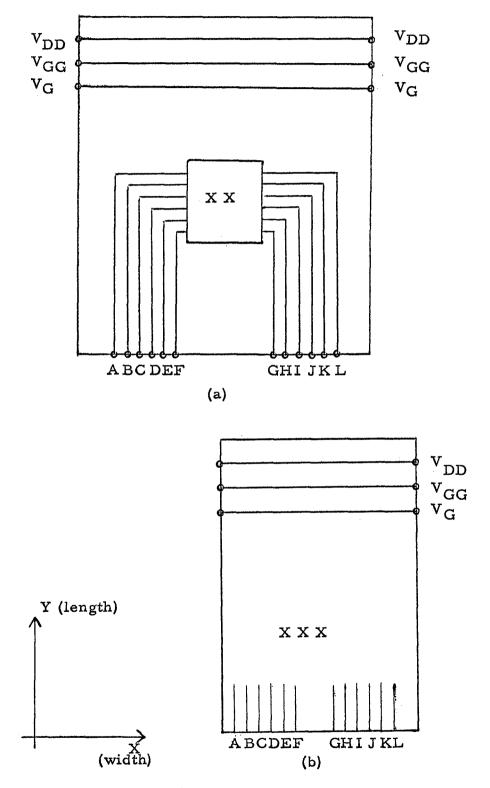

Two symbolic representations of an arbitrary cell are shown in Figure A7 and certain standardization rules have been established concerning its organization:

£

# INVERTER

Figure A2

.

(a)

(b)

(c)

.

Figure A3

# INVERTER CELL

.

Figure A5(a)

Gate Mask

,

Figure A5(b)

Contact Mask

°

۲.

Figure A6(a)

# Metalization Mask

Figure A6(b)

•

BASIC CELL

Figure A7

- (1) Power supply lines ( $V_{DD}$ ,  $V_{GG}$ , and  $V_G$ ) run through each cell horizontally at fixed locations and are metal.

- (2) All cells have a standard length (Y-dimension) and a variable width (X-dimension) dependent upon cell function.

- (3) All cell logical inputs and outputs enter or leave the cell from the bottom. In rare instances a logical I/O line may be routed to the top of a cell but never to the side.

- (4) In general, all cell logical inputs and outputs will be Pregion signal lines. (In the future it may be necessary to define a metal I/O but such a need will complicate computer cell definition and should be avoided if at all possible.)

#### A.3.2 Chip Circuit Specification

The term circuit in this study report refers to a collection of cells, cell interconnections, and bonding pads all located on a single silicon chip. With the building block approach, the circuit designer is primarily concerned with cell and bonding pad alignment, component interconnection, and circuit geometry.

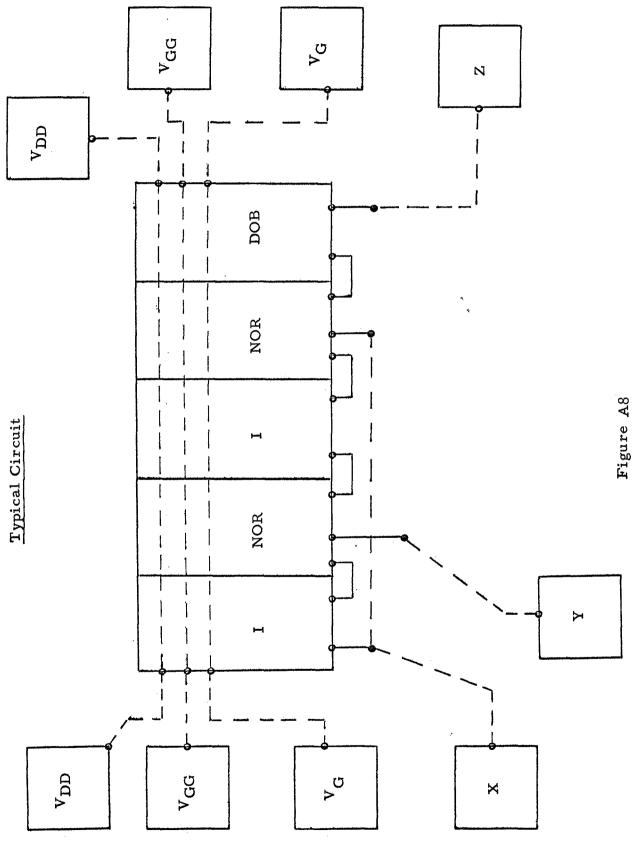

Figure A8 shows the symbolic representation of a typical MOS FET circuit constructed with standardized cells of the type described in Section A. 3. 1. The boxes around the perimeter of the figure represent circuit bonding pads. The other symbolic conventions used are identical to those described in Section A. 3. 1 for the topological layout.

As stated earlier, to construct circuits the designer only needs to know the symbolic representation of the available cells and the rules for establishing component interconnection. The circuit information needed by the computer is analogous to the information that is required to define a cell.

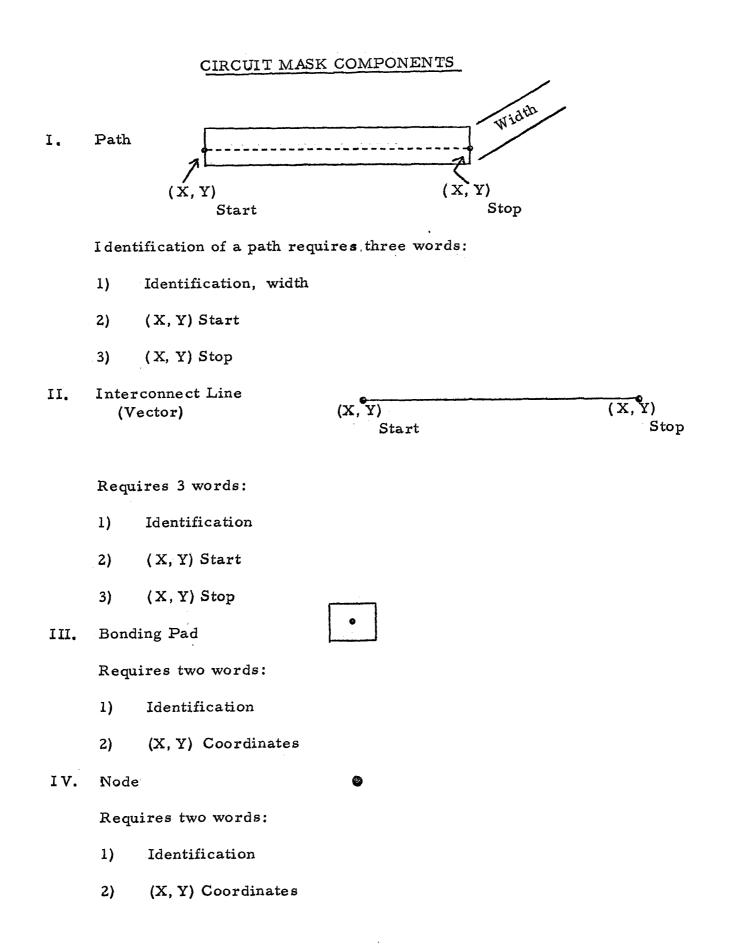

The definition of a circuit to the computer consists of the symbolic representation of the components used to represent the circuit. This includes cells, bonding pads, nodes, contacts, and contact nodes. A node differs from a contact node in that it only allows two or more straight line interconnection paths of the same material to join. A contact node joins two or more interconnections of mixed materials (metal and P-region).

ł

A-14

As with the individual cell, the computer is responsible for maintaining the circuit symbolic representation as well as the four mask layouts. In this case, the mask layouts are an overlapped composite consisting of the individual cell masks for those cells specified for this circuit and the individual masks for each specified bonding pad, metal or P-region interconnect, and contact.

The circuit representation is maintained in the computer storage area as a data set similar to those necessary to represent cells. The only difference is that the circuit data set's component coordinates are oriented to a chip grid system whereas individual cell definition data sets use a relocatable grid coordinate system with the origin located at the cell's lower left hand corner.

Circuit definition and construction is also governed by the following standardization rules necessary to permit computer participation in the design steps:  $\mathbf{1}^{i}$

- (1) Cells will be arranged in a horizontal fashion with vertical boundaries aligned.

- (2) Multiple rows of cells may be employed if proper care is taken to protect against crossover shorts.

- (3) In general, metal lines will run horizontally and P-region lines will run vertically to reduce the possibility of crossover problems.

- (4) Metal lines should be used whenever possible to minimize line resistance and capacitance.

- (5) Metal lines must be used for  $V_{DD}$ ,  $V_{GG}$ , and  $V_G$ ; and for all bonding pad connections.

- (6) Each pin on a block will have only a single path attached to it. Multiple connects will be through an external node.

- (7) Each bonding pad will have only a single path attached to it. Multiple connects will be through external nodes.

A-15

É

î.

The above rules constitute a baseline set and may be revised if appropriate care is taken in analyzing the impact on computer operation.

Both the Philco-Ford manual and the GI manual list a voluminous number of specific design rules which have not been discussed in this section. One of the primary advantages of computer assisted design is that the computer will assume responsibility for properly implementing the detailed device design procedures if the circuit is constructed from defined cells properly linked. The designer's primary responsibility will be for establishing the desired circuit geometry.

#### A.4 MAN/COMPUTER INTERFACE

Since the primary user of this system will be a designer/ engineer rather than a computer specialist, it is extremely important that the man/computer interface be user rather than programmer oriented. The ideal system would provide a graphics terminal to establish efficient two-way communication between the designer and the system, and a communication language which allows the designer to define his inputs in a familiar terminology suited to his particular problem.

Many of the problems encountered in the creation of a proper support system in which interactive graphics systems may operate are not unique to graphics applications. Rather, these problems are common to all interactive (conversational) systems. They are, however, accentuated by the graphic display console which, because of its ability to display much information rapidly, causes the user to become impatient with any system that cannot provide a response commensurate with its speed.

For this reason the man/computer interface was developed in two phases. The first phase assumed the existence of a graphics terminal and defines the basic conversational interface with the terminal as an essential component.

The second phase extrapolated the basic man/computer interface defined in phase one to a system which does not contain a graphics terminal. The primary objective was to establish an interface which, while not initially requiring a graphics display, could be easily expanded to include one with no major design modifications.

3

The minimum graphics terminal configuration required for this task would consist of a CRT display unit, a typewriter keyboard, and a light pen or gun. The typewriter keyboard will allow the user to transmit alphanumeric characters and special symbols to the system and to the graphic display. The light gun allows the user to identify particular display (X, Y) coordinates of which he wishes the system to be aware.

The system which has been developed for this application should be readily applicable to any display terminal which has a control light pen or gun and is capable of displaying vectors and alphanumeric characters.

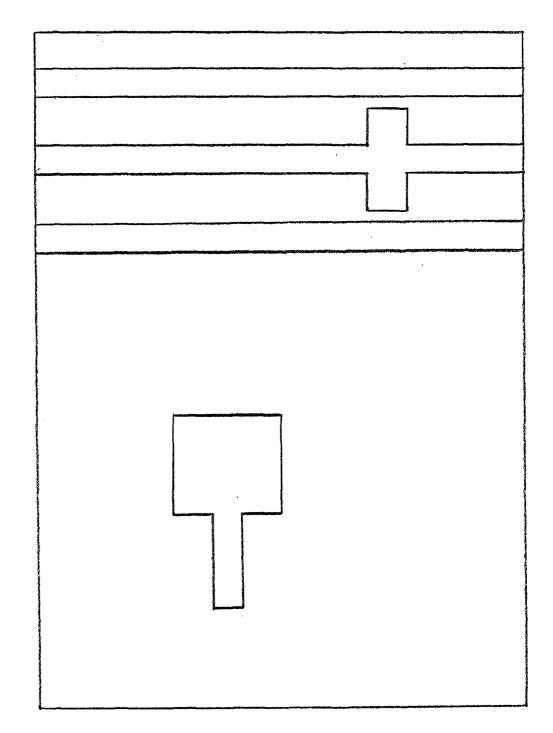

Figure A9 presents a representation of the CRT screen layout for this application. It should be noted that the screen has been partitioned into four distinct areas.

The working area represents the silicon chip area upon which the desired circuit will be constructed. As the design task proceeds, this area will contain the symbolic representation of the circuit under consideration.

The element area portion of the CRT is used to provide an immediate response to the operation action of specifying a circuit element. Legitimate circuit elements are: defined circuit cells, bonding pads, contact nodes, and nodes. When an element is specified, its symbolic representation is immediately displayed in the element display area. It may be rotated, if necessary, and then transferred to the working area of the screen by either the "translate" or the "align" instructions.

The message area provides a display area on the screen which the system may use to communicate with the user. Possible uses are error messages to notify the user of illegal operations, system status messages, etc.

5

The command keyboard is a portion of the display which is sensitive to light gun activity. It is further subdivided as shown in Figure Al0. Each small block, when touched by the light gun, will implement the command specified by that block. Blank blocks are current spares. Table Al presents a detailed definition of the current instruction list and relates the instructions to the symbols used on Figure Al0.

|              | ELEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MESSAGE AREA | AREA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | COMMAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | KEYBOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WORKING AREA |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | <u>un un constant</u> i della de |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NOR          | SP | SNC                                                                                                            | AR | H.      | СР               | RPR     | DE |         |                                        | GOF | MOF     | Н | ceed    |

|--------------|----|----------------------------------------------------------------------------------------------------------------|----|---------|------------------|---------|----|---------|----------------------------------------|-----|---------|---|---------|

| UN NO N      | SB | SN                                                                                                             | AL | RT      | CM               | RPL     | DL |         |                                        | GON |         | ы | Proceed |

|              |    | 5                                                                                                              |    | <u></u> |                  | <u></u> | L  | <u></u> | •••••••••••••••••••••••••••••••••••••• |     |         |   | · · ·   |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

| CA           |    |                                                                                                                |    |         | A                |         |    |         |                                        |     |         |   |         |

| MESSAGE AREA |    |                                                                                                                |    |         | WORKING AREA     |         |    |         |                                        |     |         |   |         |

| SSAG         |    |                                                                                                                |    |         | KING             |         |    |         |                                        |     |         |   |         |

| ME           |    |                                                                                                                |    |         | WOR              |         |    |         |                                        |     |         |   |         |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

|              |    |                                                                                                                |    |         |                  |         |    |         |                                        |     |         |   |         |

|              |    | والمراجع وا |    |         | چنان معربین مادی |         |    |         |                                        |     | <b></b> |   |         |

•

# OPERATION CODES

| Symbol | Definition                                                                                                                                                                                                                       |                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| SB     | Specify a Circuit Block (defined cell)                                                                                                                                                                                           |                                                                          |

| SPC    | Specify a Corner Pad                                                                                                                                                                                                             | As a result of any<br>specify operation, the<br>specified element        |

| SP     | Specify a Side Pad                                                                                                                                                                                                               | appears in the element<br>area of the display.                           |

| SN     | Specify a Node                                                                                                                                                                                                                   | area or me display.                                                      |

| SCN    | Specify a Contact Node                                                                                                                                                                                                           |                                                                          |

| AL     | <u>Align Block Left</u> - This instruction will<br>fied by the previous operation and curre<br>area with the left hand boundary of a cur<br>of cells in the working area. The user<br>light gun the left hand border of the dest | ently in the element<br>rrently existing chain<br>must indicate with the |

| AR     | Align Block Right - Same as AL except<br>the right boundary of an existing chain.                                                                                                                                                | system will align on                                                     |

| RT     | <u>Reset</u> - This instruction will reset the s designer to restart his circuit.                                                                                                                                                | creen and allow the                                                      |

| СМ     | <u>Connect Metal</u> - If the user next indicat<br>tact nodes) in the working area, the sys<br>them with a metal path (dashed line).                                                                                             |                                                                          |

| СР     | <u>Connect P-Region</u> - Same as CM above<br>will connect the indicated nodes with a l<br>line).                                                                                                                                |                                                                          |

| Т      | <u>Translate</u> - This instruction will allow<br>an element area to the working area by<br>(X, Y) coordinates in the working area v                                                                                             | touching the desired                                                     |

| RPL    | <u>Rotate Pad Left</u> - Every time this instr<br>pad in the element area will be rotated                                                                                                                                        |                                                                          |

Table Al

A-20

1

| Symbol  | Definition                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

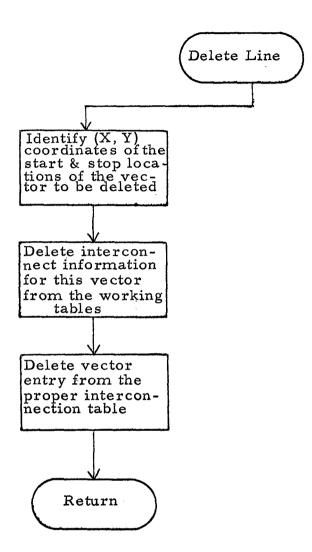

| DL      | Delete Line - Allows the operator to eliminate the intercon-<br>nection line touched by the light gun.                                                                                       |

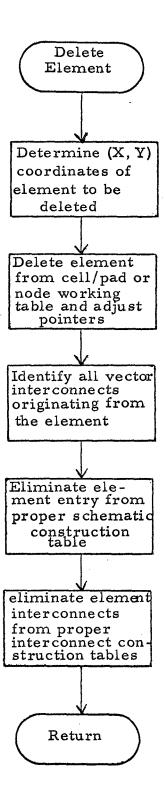

| DE      | <u>Delete Element</u> - Allows the operator to eliminate the ele-<br>ment touched by the light gun and all of its interconnections.                                                          |

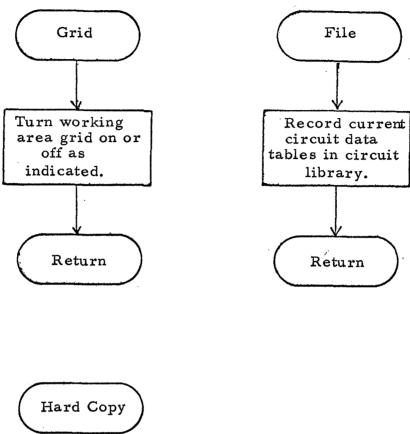

| GON     | <u>Grid On</u> - This instruction allows the operator to grid the working area.                                                                                                              |

| GOF     | <u>Grid Off</u> - Allows the operator to turn the grid off.                                                                                                                                  |

| F       | <u>File</u> - This instruction allows the operator to record in a library for later reference the data sets describing the circuit currently in the working area.                            |

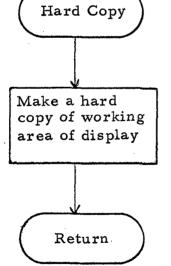

| н       | <u>Hardcopy</u> - This instruction allows the operator to obtain a hard copy of the working area.                                                                                            |

| MOF     | Message Off - This command will blank the message area of the display.                                                                                                                       |

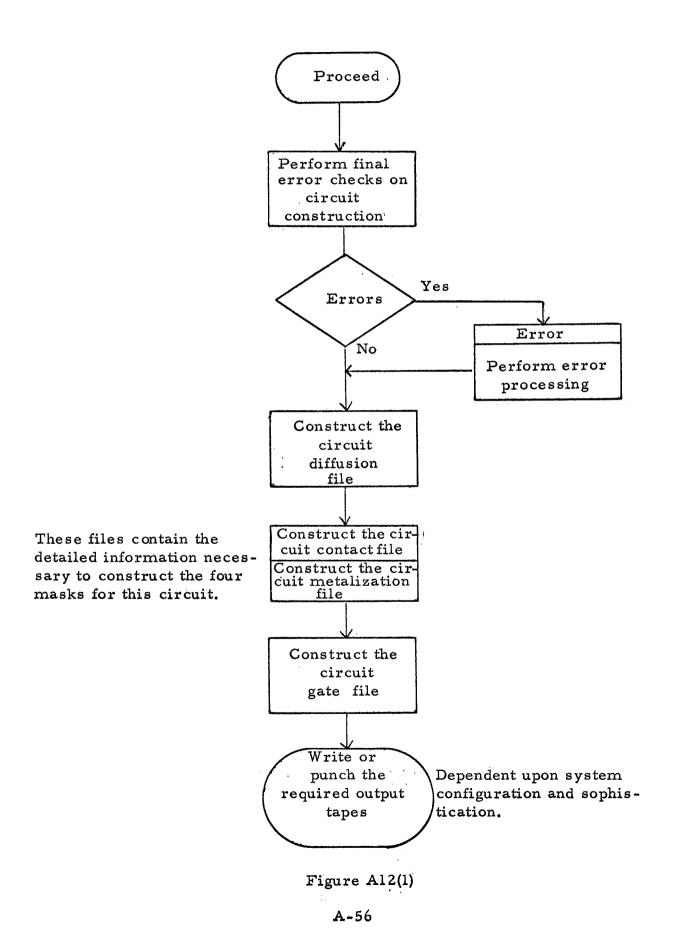

| Proceed | <u>Proceed</u> - Indicates to the system that the design in the work-<br>ing area is complete and that the system should begin deriv-<br>ing the required output to generate the four masks. |

Table A1. (continued)

A-21

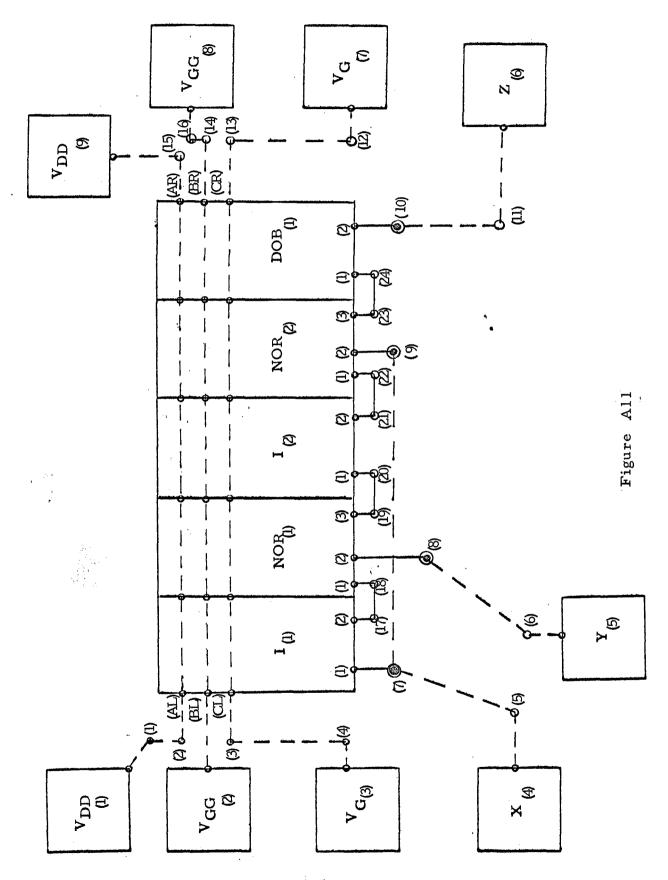

To illustrate how this system is to be used, the circuit of Figure A8 will be constructed in the working area using the defined instructions. Figure All is identical to Figure A8 except that nodes, blocks, and pads are numbered to simplify the illustration. Pads are numbered from 1 to 9 starting at  $V_{DD}$  in the upper left and proceeding in a counter-clockwise manner. Cells are identified by their symbol and a repetition number which is assigned by the computer as the cell is specified. The repetition number is indicative of the number of times the same standard cell has been used in the circuit. In order to uniquely identify a particular cell or pad in a circuit, both its code number and repetition number must be known.

Nodes have been arbitrarily numbered as specified. The number and letters in parenthesis would not be visible on the screen but are analogous to the numbering scheme used by the system to keep track of circuit elements.

A detailed instruction list for the circuit of Figure All has been developed in Table A2. The nomenclature used is oriented about the numbering convention utilized in Figure All. For the sake of simplicity, the following conventions have been used in Table A2:

- (1) "SB-I(1)" This is the specification of Block I, Repetition Number (1).

- (2) "N(4)" is Node # 4.

- (3) "CM-(P1)(N1)" is read "Connect Metal from Pad 1 to Node #1".

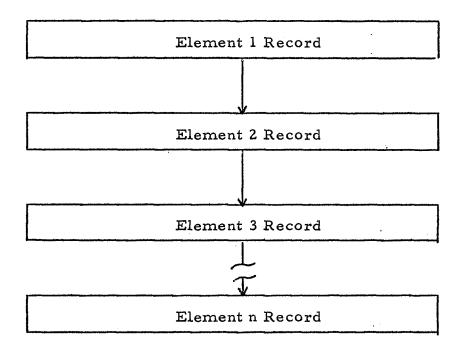

- (4) "CP-(N9)(NOR2, 2)" is read "Connect P-Region from Node #9 to NOR Cell Repetition #2, Pin #2."