# Machine Learning in Compiler Optimization

By Zheng Wang and Michael O'Boyle

ABSTRACT | In the last decade, machine-learning-based compilation has moved from an obscure research niche to a mainstream activity. In this paper, we describe the relationship between machine learning and compiler optimization and introduce the main concepts of features, models, training, and deployment. We then provide a comprehensive survey and provide a road map for the wide variety of different research areas. We conclude with a discussion on open issues in the area and potential research directions. This paper provides both an accessible introduction to the fast moving area of machine-learning-based compilation and a detailed bibliography of its main achievements.

**KEYWORDS** | Code optimization; compiler; machine learning; program tuning

# I. INTRODUCTION

"Why would anyone want to use machine learning to build a compiler?" It is a view expressed by many colleagues over the last decade. Compilers translate programming languages written by humans into binary executable by computer hardware. It is a serious subject studied since the 1950s [1]–[3] where correctness is critical and caution is a by-word. Machine learning, on the other hand, is an area of artificial intelligence (AI) aimed at detecting and predicting patterns. It is a dynamic field looking at subjects as diverse as galaxy classification [4] to predicting elections based on Tweeter feeds [5]. When an open-source machine learning compiler was announced by IBM in 2009 [6], some wry slashdot commentators picked up on the AI aspect, predicting the start of sentient computers, global net, and the war with machines from the *Terminator* film series.

In fact, as we will see, in this paper, that compilers and machine learning are a natural fit and have developed into an established research domain.

Manuscript received October 30, 2017; accepted January 23, 2018. (Corresponding author: Michael O'Boyle.)

**Z. Wang** is with the MetaLab, School of Computing and Communications, Lancaster University, Lancaster LAI 4WA, U.K. (e-mail: z.wang@lancaster.ac.uk).

**M. O'Boyle** is with the School of Informatics, University of Edinburgh, Edinburgh EH8 9AB, U.K. (e-mail: mob@inf.ed.ac.uk).

# Digital Object Identifier: 10.1109/JPROC.2018.2817118

# A. It Is All About Optimization

Compilers have two jobs—translation and optimization. First, they must translate programs into binary correctly. Second, they have to find the most efficient translation possible. There are many different correct translations whose performance varies significantly. The vast majority of research and engineering practices is focused on this second goal of performance, traditionally misnamed optimization. The goal was misnamed because in most cases, until recently, finding an optimal translation was dismissed as being too hard to find and an unrealistic endeavor. Instead it focused on developing compiler heuristics to transform the code in the hope of improving performance but could in some instances damage it.

Machine learning predicts an outcome for a new data point based on prior data. In its simplest guise, it can be considered a form of interpolation. This ability to predict based on prior information can be used to find the data point with the best outcome and is closely tied to the area of optimization. It is at this overlap of looking at code improvement as an optimization problem and machine learning as a predictor of the optima where we find machine learning compilation.

Optimization as an area, machine learning based or otherwise, has been studied since the 1800s [8], [9]. An interesting question is therefore why has the convergence of these two areas taken so long? There are two fundamental reasons. First, despite the year-on-year increasing potential performance of hardware, software is increasingly unable to realize it leading to a software gap. This gap has yawned right open with the advent of multicores (see also Section VI-B). Compiler writers are looking for new ways to bridge this gap.

Second, computer architecture evolves so quickly that it is difficult to keep up. Each generation has new quirks and compiler writers are always trying to play catchup. Machine learning has the desirable property of being automatic. Rather than relying on expert compiler writers to develop clever heuristics to optimize the code, we can let the machine learn how to optimize a compiler to make the machine run faster, an approach

<sup>1</sup>In fact, the term superoptimizer [7] was coined to describe systems that tried to find the optimum.

sometimes referred to as autotuning [10]–[13]. Machine learning is, therefore, ideally suited to making any code optimization decision where the performance impact depends on the underlying platform. As described later in this paper, it can be used for topics ranging from selecting the best compiler flags to determining how to map parallelism to processors.

Machine learning is part of a tradition in computer science and compilation in increasing automation The 1950s to 1970s were spent trying to automate compiler translation, e.g., lex for lexical analysis [14] and yacc for parsing [15]; the last decade by contrast has focused on trying to automate compiler optimization. As we will see, it is not "magic" or a panacea for compiler writers, rather it is another tool allowing automation of tedious aspects of compilation providing new opportunities for innovation. It also brings compilation nearer to the standards of evidence-based science. It introduces an experimental methodology where we separate out evaluation from design and considers the robustness of solutions. Machine-learning-based schemes, in general, have the problem of relying on black boxes whose working we do not understand and hence trust. This problem is just as true for machine-learning-based compilers. In this paper, we aim to demystify machine-learning-based compilation and show it is a trustworthy and exciting direction for compiler research.

The remainder of this paper is structured as follows. First, we give an intuitive overview for machine learning in compilers in Section II. Then, we describe how machine learning can be used to search for or to directly predict good compiler optimizations in Section III. This is followed by a comprehensive discussion in Section IV for a wide range of machine learning models that have been employed in prior work. Next, in Section V, we review how previous work chooses quantifiable properties, or features, to represent programs. We discuss the challenges and limitations for applying machine learning to compilation, as well as open research directions in Section VII before we summarize and conclude in Section VIII.

# II. OVERVIEW OF MACHINE LEARNING IN COMPILERS

Given a program, compiler writers would like to know what compiler heuristic or optimization to apply in order to make the code better. Better often means execute faster, but can also mean smaller code footprint or reduced power. Machine learning can be used to build a model used within the compiler that makes such decisions for any given program.

There are two main stages involved: learning and deployment. The first stage learns the model based on training data, while the second uses the model on new unseen programs. Within the learning stage, we need a way of representing programs in a systematic way. This representation is known as the program features [16].

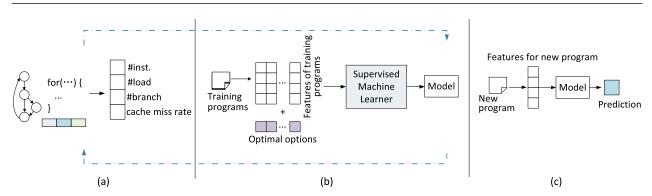

Fig. 1 gives an intuitive view on how machine learning can be applied to compilers. This process, which includes feature engineering, learning a model, and deployment, is described in the following sections.

# A. Feature Engineering

Before we can learn anything useful about programs, we first need to be able to characterize them. Machine learning relies on a set of quantifiable properties, or features, to characterize the programs [Fig. 1(a)]. There are many different features that can be used. These include the static data structures extracted from the program source code or the compiler intermediate representation (such as the number of instructions or branches), dynamic profiling information (such as performance counter values) obtained through runtime profiling, or a combination of the both.

Standard machine learning algorithms typically work on fixed length inputs, so the selected properties will be summarized into a fixed length feature vector. Each element of the vector can be an integer, real or Boolean value. The process of feature selection and tuning is referred to as feature engineering. This process may need to iteratively perform multiple times to find a set of high-quality features to build

Fig. 1. A generic view of supervised machine learning in compilers. (a) Feature engineering. (b) Leaning a model. (c) Deployment.

an accurate machine learning model. In Section V, we provide a comprehensive review of feature engineering for the topic of program optimization.

# B. Learning a Model

The second step is to use training data to derive a model using a learning algorithm. This process is depicted in Fig. 1(b). Unlike other applications of machine learning, we typically generate our own training data using existing applications or benchmarks. The compiler developer will select training programs which are typical of the application domain. For each training program, we calculate the feature values, compiling the program with different optimization options, and running and timing the compiled binaries to discover the best performing option. This process produces, for each training program, a training instance that consists of the feature values and the optimal compiler option for the program.

The compiler developer then feeds these examples to a machine learning algorithm to automatically build a model. The learning algorithm's job is to find from the training examples a correlation between the feature values and the optimal optimization decision. The learned model can then be used to predict, for a new set of features, what the optimal optimization option should be.

Because the performance of the learned model strongly depends on how well the features and training programs are chosen, the processes of featuring engineering and training data generation often need to repeat multiple times.

# C. Deployment

In the final step, the learned model is inserted into the compiler to predict the best optimization decisions for new programs. This is demonstrated in Fig. 1(c). To make a prediction, the compiler first extracts the features of the input program, and then feeds the extracted feature values to the learned model to make a prediction.

The advantage of the machine-learning-based approach is that the entire process of building the model can be easily repeated whenever the compiler needs to target a new hardware architecture, operating system, or application domain. The model built is entirely derived from experimental results and is hence evidence based.

#### D. Example

As an example to illustrate these steps, consider thread coarsening [18] for GPU programs. This code transformation technique works by giving multiple work items (or work elements) to one single thread. It is similar to loop unrolling, but applied across parallel work items rather than across serial loop iterations.

Fig. 2(a) shows a simple OpenCL kernel where a thread operates on a work item of the 1-D input array, in, at a time. The work item to be operated on is specified by the value

```

kernel void square(global float* in, global float* out){

int gid = get_global_id(0)

3

out[gid] = in[gid] * in[gid];

(a)

kernel void square(global float* in, global float* out){

int gid = get_global_id(0);

int tid0 = 2*gid + 0;

int tid1 = 2*gid + 1;

out[tid0] = in[tid0] * in[tid0];

out[tid1] = in[tid1] * in[tid1];

```

Fig. 2. An OpenCL thread coarsening example reproduced from [17]. The original OpenCL code is shown in (a) where each thread takes the square of one element of the input array. When coarsened by a factor of two, as shown in (b), each thread now processes two elements of the input array.

returned from the OpenCL get\_global\_id() API. Fig. 2(b) shows the transformed code after applying a thread coarsen factor of two, where each thread processes two elements of the input array.

Thread coarsening can improve performance through increasing instruction-level parallelism [19], reducing the number of memory-access operations [20] and eliminating redundant computation when the same value is computed in every work item. However, it can also have several negative side effects, such as reducing the total amount of parallelism and increasing the register pressure, which can lead to slowdown performance. Determining when and how to apply thread coarsening is nontrivial, because the best coarsening factor depends on the target program and the hardware architecture that the program runs on [17], [19].

Magni et al. show that machine learning techniques can be used to automatically construct effective threadcoarsening heuristics across GPU architectures [17]. Their approach considers six coarsening factors (1, 2, 4, 8, 16, 32). The goal is to develop a machine-learning-based model to decide whether an OpenCL kernel should be coarsened on a specific GPU architecture and, if so, what is the best coarsening factor. Among many machine learning algorithms, they chose to use an artificial neural network to model<sup>2</sup> the problem. Construing such a model follows the classical three-step supervised learning process, which is depicted in Fig. 1 and described in more details as follows.

1) Feature Engineering: To describe the input OpenCL kernel, Magni et al. use static code features extracted from the compiler's intermediate representation. Specifically, they developed a compiler-based tool to obtain the feature values from the program's LLVM bitcode [21]. They started from 17 candidate features. These include things like the number of

<sup>&</sup>lt;sup>2</sup>In fact, Magni et al. employed a hierarchical approach consisting of multiple artificial neural networks [17]. However, these networks are trained using the same process.

and types of instructions and memory level parallelism (MLP) within an OpenCL kernel. Table 1 gives the list of candidate features used in [17]. Typically, candidate features can be chosen based on developers' intuitions, suggestions from prior works, or a combination of both. After choosing the candidate features, a statistical method called principal component analysis (PCA; see also Section IV-B) is applied to map the 17 candidate features into seven aggregated features, so that each aggregated feature is a linear combination of the original features. This technique is known as "feature dimension reduction," which is discussed in Section V-D2. Dimension reduction helps eliminating redundant information among candidate features, allowing the learning algorithm to perform more effectively.

- 2) Learning the Model: For the work presented in [17], 16 OpenCL benchmarks were used to generate training data. To find out which of the six coarsening factors performs best for a given OpenCL kernel on a specific GPU architecture, we can apply each of the six factors to an OpenCL kernel and record its execution time. Since the optimal thread-coarsening factor varies across hardware architectures, this process needs to repeat for each target architecture. In addition to finding the best performing coarsening factor, Magni et al. also extracted the aggregated feature values for each kernel. Applying these two steps on the training benchmarks results in a training data set where each training example is composed of the optimal coarsening factor and feature values for a training kernel. The training examples are then fed into a learning algorithm which tries to find a set of model parameters (or weights) so that overall prediction error on the training examples can be minimized. The output of the learning algorithm is an artificial neural network model where its weights are determined from the training data.

- 3) Deployment: The learned model can then be used to predict the optimal coarsening factor for unseen OpenCL programs. To do so, static source code features are first extracted from the target OpenCL kernel; the extracted feature values are then fed into the model which decides whether to coarsen or not and which coarsening factor should be used. The technique proposed in [17] achieves an average speedup between 1.11x and 1.33x across four GPU architectures and does not lead to degraded performance on a single benchmark.

Table 1 Candidate Code Features Used in [17]

| Feature Description                              | Feature Description                                      |

|--------------------------------------------------|----------------------------------------------------------|

| # Basic Blocks                                   | # Branches                                               |

| # Divergent Instr.                               | # Instrs. in Divergent Regions                           |

| (# instr. in Divergent regions)/(# total instr.) | # Divergent regions                                      |

| # Instrs                                         | # Floating point instr.                                  |

| Avg. ILP per basic block                         | (# integer instr.) / (# floating point instr.)           |

| # integer instr.                                 | # Math built-in func.                                    |

| Avg. MLP per basic block                         | # loads                                                  |

| # stores                                         | # loads that are independent of the coarsening direction |

| # barriers                                       |                                                          |

# III. METHODOLOGY

One of the key challenges for compilation is to select the right code transformation, or sequence of transformations for a given program. This requires effectively evaluating the quality of a possible compilation option, e.g., how a code transformation will affect eventual performance.

A naive approach is to exhaustively apply each legal transformation option and then profile the program to collect the relevant performance metric. Given that many compiler problems have a massive number of options, exhaustive search and profiling is infeasible, prohibiting the use of this approach at scale. This search-based approach to compiler optimization is known as iterative compilation [22], [23] or autotuning [10], [24]. Many techniques have been proposed to reduce the cost of searching a large space [25], [26]. In certain cases, the overhead is justifiable if the program in question is to be used many times, e.g., in a deeply embedded device. However, its main limitation remains: it only finds a good optimization for one program and does not generalize into a compiler heuristic.

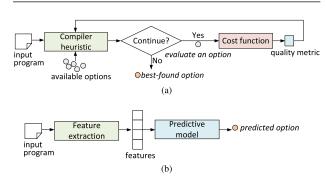

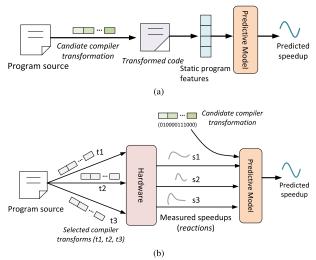

There are two main approaches for solving the problem of scalably selecting compiler options that work across programs. A high level comparison of both approaches is given in Fig. 3. The first strategy attempts to develop a cost (or priority) function to be used as a proxy to estimate the quality of a potential compiler decision, without relying on extensive profiling. The second strategy is to directly predict the best performing option.

# A. Building a Cost Function

Many compiler heuristics rely on a cost function to estimate the quality of a compiler option. Depending on the optimization goal, the quality metric can be execution time, the code size, or energy consumption, etc. Using a cost function, a compiler can evaluate a range of possible options to choose the best one, without needing to compile and profile the program with each option.

Fig. 3. There are, in general, two approaches to determine the optimal compiler decision using machine learning. The first one is to learn a cost or priority function to be used as a proxy to select the best performing option (a). The second one is to learn a predictive model to directly predict the best option (b).

1) The Problem of Handcrafted Heuristics: Traditionally, a compiler cost function is manually crafted. For example, a heuristic of function inlining adds up a number of relevant metrics, such as the number of instructions of the target function to be inlined, the callee and stack size after inlining, and compare the resulted value against a predefined threshold to determine if it is profitable to inline a function [27]. Here, the importance or weights for metrics and the threshold are determined by compiler developers based on their experience or via "trail-and-error." Because the efforts involved in tuning the cost function are so expensive, many compilers simply use "one-size-fits-all" cost function for inlining. However, such a strategy is ineffective. For examples, Cooper et al. show that a "one-size-fits-all" strategy for inlining often delivers poor performance [28]; other studies also show that the optimal thresholds to use to determine when to inline change from one program to the other [29], [30].

Handcrafted cost functions are widely used in compilers. Other examples include the work conducted by Wagner et al. [31] and Tiwari et al. [32]. The former combines a Markov model and a human-derived heuristic to statically estimate the execution frequency of code regions (such as function innovation counts). The latter calculates the energy consumption of an application by assigning a weight to each instruction type. The efficiency of these approaches highly depends on the accuracy of the estimations given by the manually tuned heuristic.

The problem of relying on a hand-tuned heuristic is that the cost and benefit of a compiler optimization often depend on the underlying hardware; while handcrafted cost functions could be effective, manually developing one can take months or years on a single architecture. This means that tuning the compiler for each newly released processor is hard and is often infeasible due to the drastic efforts involved. Because cost functions are important and manually tuning a good function is difficult for each individual architecture, researchers have investigated ways to use machine learning to automate this process.

In Section III-A2, we review a range of previous studies on using machine learning to tune cost functions for performance and energy consumption—many of which can be applied to other optimization targets such as the code size [33] or a tradeoff between energy and runtime.

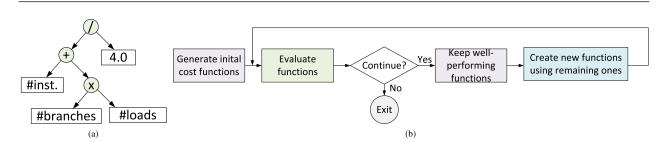

2) Cost Functions for Performance: The Meta Optimization framework [34] uses genetic programming (GP) to search for a cost function  $y \leftarrow f(x)$ , which takes in a feature vector x and produces a real-valued priority y. Fig. 4 depicts the workflow of the framework. This approach is evaluated on a number of compiler problems, including hyperblock formation, register allocation, and data prefetching, showing that machine learned cost functions outperform human-crafted ones. A similar approach is employed by Cavazos et al. who find cost functions for performance and compilation overhead for a Java just-in-time compiler [35]. The COLE compiler [36] uses a variance of the GP algorithm called strength Pareto evolutionary algorithm 2 (SPEA2) [37] to learn cost functions to balance multiple objectives (such as program runtime, compilation overhead, and code size). In Section IV-C, we describe the working mechanism of GP-like search algorithms.

Another approach to tune the cost functions is to predict the execution time or speedup of the target program. The Qilin compiler [38] follows such an approach. It uses curve fitting algorithms to estimate the runtime for executing the target program of a given input size on the CPU and the GPU. The compiler then uses this information to determine the optimal loop iteration partition across the CPU and the GPU. The Qilin compiler relies on an application-specific function which is built on a per program base using reference inputs. The curve fitting (or regression; see, also, Section IV) model employed by the Qilin compiler can model with continuous values, making it suitable for estimating runtime and speedup. In [39], this approach is extended, which developed a relative predictor that predicts whether an unseen predictor will improve significantly on a GPU relative to a CPU. This is used for runtime scheduling of OpenCL jobs.

The early work conduced by Brewer proposed a regression-based model to predict the execution of a data layout scheme for parallelization, by considering three parameters [40]. Using the model, his approach can select the optimal

<sup>3</sup>Hyperblock formation combines basic blocks from multiple control paths to form a predicated, larger code block to expose instruction level

Fig. 4. A simple view of the GP approach presented in [34] for tuning compiler cost functions. Each candidate cost function is represented as an expression tree (a). The workflow of the GP algorithm is presented in (b).

layout for over 99% of the time for a partial differential equation (PDE) solver across four evaluation platforms. Other previous works also use curve fitting algorithms to build a cost function to estimate the speedup or runtime of sequential [41]–[43], OpenMP [44]–[46], and, more recently, deep learning applications [47].

3) Cost Functions for Energy Consumption: In addition to performance, there is an extensive body of work that investigates ways to build energy models for software optimization and hardware architecture design. As power or energy readings are continuous real values, most of the prior work on power modeling uses regression-based approaches.

Linear regression is a widely used technique for energy modeling. Benini et al. developed a linear-regression-based model to estimate power consumption at the instruction level [48]. The framework presented by Rethinagiri et al. [49] uses parameterized formulas to estimate power consumption of embedded systems. The parameters of the formulas are determined by applying a regression-based algorithm to reference data obtained with handcrafted assembly code and power measurements. In a more recent work, Schürmans et al. also adopt a regression-based method for power modeling [50], but the weights of the regression model are determined using standard benchmarks instead of handwritten assembly programs.

Other works employ the artificial neural network (ANN) to automatically construct power models. Curtis-Maury et al. develop an ANN-based model to predict the power consumption of OpenMP programs on multicore systems [51]. The inputs to the model are hardware performance counter values such as the cache miss rate, and the output is the estimated power consumption. Su et al. adopt a similar approach by developing an ANN predictor to estimate the runtime and power consumption for mapping OpenMP programs on nonuniform memory access (NUMA) multicores. This approach is also based on runtime profiling of the target program, but it explicitly considers NUMA-specific information like local and remote memory accesses per cycle.

# **B.** Directly Predicting the Best Option

While a cost function is useful for evaluating the quality of compiler options, the overhead involved in searching for the optimal option may still be prohibitive. For this reason, researchers have investigated ways to directly predict the best compiler decision using machine learning for relatively small compilation problems.

Monsifrot et al. pioneered the use of machine learning to predict the optimal compiler decision [16]. This work developed a decision-tree-based approach to determine whether it is beneficial to unroll a loop based on information such as the number of statements and arithmetic operations of the loop. Their approach makes a binary decision on whether to unroll a loop but not how many times the loop should be unrolled. Later, Stephenson and Amarasinghe advanced [16] by directly

predicting the loop unroll factor [52] by considering eight unroll factors (1, 2, ..., 8). They formulated the problem as a multiclass classification problem (i.e., each loop unroll factor is a class). They used over 2500 loops from 72 benchmarks to train two machine learning models [a nearest neighbor and a support vector machine (SVM) model] to predict the loop unroll factor for unseen loops. Using a richer set of features than [16], their techniques correctly predict the unroll factor for 65% of the testing loops, leading to, on average, a 5% improvement for the SPEC 2000 benchmark suite.

For sequential programs, there is extensive work in predicting the best compiler flags [53], [54], code transformation options [55], or tile size for loops [56], [57]. This level of interest is possibly due to the restricted nature of the problem, allowing easy experimentation and comparison against prior work.

Directly predicting the optimal option for parallel programs is harder than doing it for sequential programs, due to the complex interactions between the parallel programs and the underlying parallel architectures. Nonetheless, there are works on predicting the optimal number of threads to be used to run an OpenMP program [46], [58], the best parameters to be used to compile a CUDA programs for a given input [59], and the thread coarsening parameters for OpenCL programs for GPUs [17]. These papers show that supervised machine learning can be a powerful tool for modeling problems with a relatively small number of optimization options.

## IV. MACHINE LEARNING MODELS

In this section, we review the wide range of machine learning models used for compiler optimization. Table 2 summarizes the set machine learning models discussed in this section.

There are two major subdivisions of machine learning techniques that have previously been used in compiler optimizations: supervised and unsupervised learning. Using supervised machine learning, a predictive model is trained on empirical performance data (labeled outputs) and important quantifiable properties (features) of representative programs. The model learns the correlation between these feature values and the optimization decision that delivers the optimal (or near-optimal) performance. The learned correlations are used to predict the best optimization decisions for new programs. Depending on the nature of the outputs, the predictive model can be either a regression model for continuous outputs or a classification model for discrete outputs.

In the other subdivision of machine learning, termed unsupervised learning, the input to the learning algorithm is a set of input values merely—there is no labeled output. One form of unsupervised learning is clustering which groups the input data items into several subsets. For example, SimPoint [60], a simulation technique, uses clustering to pick represent program execution points for program simulation. It does so by first dividing a set of program runtime information

| Approach                  | Problem                  | Application Domains                                                                                                                                          | Models                                                                                                                              |

|---------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 6 '                       | Regression               | Useful for modelling continuous values, such as estimating execution time, speedup, power consumption, latency etc.                                          | Linear/non-linear regression, artificial neural networks (ANNs), support vector machines (SVMs).                                    |

| Supervised learning Class | Classification           | Useful for predicting discrete values, such as choosing compiler flags, #threads, loop unroll factors, algorithmic implementations etc.                      | K-nearest neighbour (KNN), decision trees, random forests, logical regression, SVM, Kernel Canonical Correlation Analysis, Bayesian |

| Unsupervised learning     | Clustering               | Data analysis, such as grouping profiling traces into clusters of similar behaviour                                                                          | K-means, Fast Newman clustering                                                                                                     |

|                           | Feature engineering      | Feature dimension reduction, finding useful feature representations                                                                                          | Principal component analysis (PCA), autoencoders                                                                                    |

| Online learning           | Search and self-learning | Useful for exploring a large optimisation space, runtime adaption, dynamic task scheduling where the optimal outcome is achieved through a series of actions | Genetic algorithm (GA), genetic programming (GP), reinforcement learning (RL)                                                       |

Table 2 Machine Learning Methods Discussed in Section IV

into groups (or clusters), such that points within each cluster are similar to each other in terms of program structures (loops, memory usages, etc.); it then chooses a few points of each cluster to represent all the simulation points within that group without losing much information.

There are also techniques that sit at the boundary of supervised and unsupervised learning. These techniques refine the knowledge gathered during offline learning or previous runs using empirical observations obtained during deployment. We review such techniques in Section IV-C. This sections concludes with a discussion of the relative merits of different modeling approaches for compiler optimization.

# A. Supervised Learning

1) Regression: A widely used supervised learning technique is called regression. This technique has been used in various tasks, such as predicting the program execution time input [38] or speedup [39] for a given input, or estimating the tail latency for parallel workloads [61].

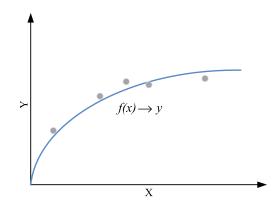

Regression is essentially curve fitting. As an example, consider Fig. 5 where a regression model is learned from five data points. The model takes in a program input size *X* and predicts the execution time of the program Y. Adhering to supervised learning nomenclature, the set of five known data points is the training data set and each of the five points that comprise the training data is called a training example. Each training example  $(x_i, y_i)$  is defined by a feature vector (i.e., the input size in our case)  $x_i$  and a desired output (i.e., the program execution time in our case)  $y_i$ . Learning in this context is understood as discovering the relation between the inputs  $(x_i)$  and the outputs  $(y_i)$  so that the predictive model can be used to make predictions for any new, unseen input features in the problem domain. Once the function *f* is in place, one can use it to make a prediction by taking in a new input feature vector x. The prediction y is the value of the curve that the new input feature vector x corresponds to.

There are a range of machine learning techniques that can be used for regression. These include the simple linear regression model and more advanced models like SVMs and ANNs. Linear regression is effective when the input (i.e.,

feature vectors) and output (i.e., labels) have a strong linear relation. SVM and ANNs can model both linear and nonlinear relations, but typically require more training examples to learn an effective model when compared with simple linear regression models.

Table 3 gives some examples of regression techniques that have been used in prior work for code optimization and the problem to be modeled.

2) Classification: Supervised classification is another technique that has been widely used in prior work of machinelearning-based code optimization. This technique takes in a feature vector and predicts which of a set of classes the feature vector is associated with. For example, classification can be used to predict which of a set of unroll factors should be used for a given loop, by taking in a feature vector that describes the characteristics of the target loop (see also Section II-D).

The k-nearest neighbur (KNN) algorithm is a simple yet effective classification technique. It finds the k closet training examples to the input instance (or program) on the feature space. The closeness (or distance) is often evaluated using the Euclidean distance, but other metrics can also be used. This technique has been used to predict the optimal optimization parameters in prior works [52], [66], [67]. It

Fig. 5. A simple regression-based curve-fitting example. There are five training examples in this case. A function f is trained with the training data, which maps the input x to the output y. The trained function can predict the output of an unseen x.

Table 3 Regression Techniques Used in Prior Works

| Modelling Technique        | Application              | References       |

|----------------------------|--------------------------|------------------|

| Linear Regression          | Exec. Time Estimation    | [62], [38], [43] |

| Linear Regression          | Perf. & Power Prediction | [63], [64], [65] |

| Artificial Neural Networks | Exec. Time Estimation    | [62], [46], [39] |

works by first predicting which of the training programs are closet (i.e., nearest neighbors) to the incoming program on the feature space; it then uses the optimal parameters (which are found during training time) of the nearest neighbors as the prediction output. While it is effective on small problems, KNN also has two main drawbacks. First, it must compute the distance between the input and all training data at each prediction. This can be slow if there is a large number of training programs to be considered. Second, the algorithm itself does not learn from the training data; instead, it simply selects the k nearest neighbors. This means that the algorithm is not robust to noisy training data and could choose an ill-suited training program as the prediction.

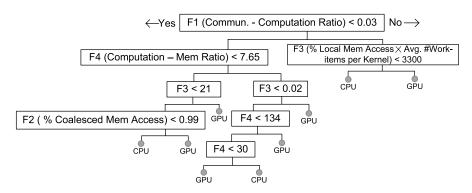

As an alternative, the decision tree has been used in prior works for a range of optimization problems. These include choosing the parallel strategy for loop parallelization [69], determining the loop unroll factor [16], [70], deciding the profitability of using GPU acceleration [68], [71], and selecting the optimal algorithm implementation [72]. The advantage of a decision tree is that the learned model is interpretable and can be easily visualized. This enables users to understand why a particular decision is made by following the path from the root node to a leaf decision node. For example, Fig. 6 depicts the decision tree model developed in [68] for selecting the best performing device (CPU or GPU) to run an OpenCL program. To make a prediction, we start from the root of the tree; we compare a feature value (e.g., the communication-computation ratio) of the target program against a threshold to determine which branch of the tree to follow; and we repeat this process until we reach a leaf node where a decision will be made. It is to note that the structure and thresholds of the tree are automatically determined by the machine learning algorithm, which may change when we target a different architecture or application domain.

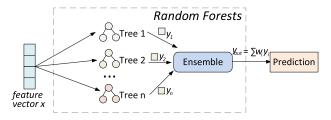

Decision trees make the assumption that the feature space is convex, i.e., it can be divided up using hyperplanes into different regions, each of which belongs to a different category. This restriction is often appropriate in practice. However, a significant drawback of using a single decision tree is that the model can overfit due to outliers in the training data (see also Section IV-D). Random forests [73] have, therefore, been proposed to alleviate the problem of overfitting. Random forests are an ensemble learning method [74]. As illustrated in Fig. 7, it works by constructing multiple decision trees at training time. The prediction of each tree depends on the values of a random vector sampled independently on the feature value. In this way, each tree is randomly forced to be insensitive to some feature dimensions. To make a prediction, random forests then aggregate the outcomes of individual trees to form an overall prediction. It has been employed to determine whether to inline a function or not [75], delivering better performance than a single-modelbased approach. We want to highlight that random forests can also be used for regression tasks. For instances, it has been used to model energy consumption of OpenMP [76] and CUDA [77] programs.

Logical regression is a variation of linear regression but is often used for classification. It takes in the feature vector and calculates the probability of some outcome. For example, Cavazos and O'Boyle used logical regression to determine the optimization level of Jike RVM. Like decision trees, logical regression also assumes that the feature values and the prediction has a linear relation.

More advanced models, such as SVM classification, have been used for various compiler optimization tasks [46], [79]–[81]. SVMs use kernel functions to compute the similarity of feature vectors. The radial basis function (RBF) is commonly used in prior works [46], [82] because it can model both linear and nonlinear problems. It works by mapping the input feature vector to a higher dimensional space where it may be easier to find a linear hyperplane to well separate the labeled data (or classes).

Other machine learning techniques, such as kernel canonical correlation analysis and naive Bayes, have also

Fig. 6. A decision tree for determining which device (CPU or GPU) to use to run an OpenCL program. This diagram is reproduced from [68].

Fig. 7. Random forests are an ensemble learning algorithm. It aggregates the outputs of multiple decision trees to form a final prediction. The idea is to combine the predictions from multiple individual models together to make a more robust, accurate prediction than any individual model.

been used in prior works to predict stencil program configurations [83] or detect parallel patterns [84].

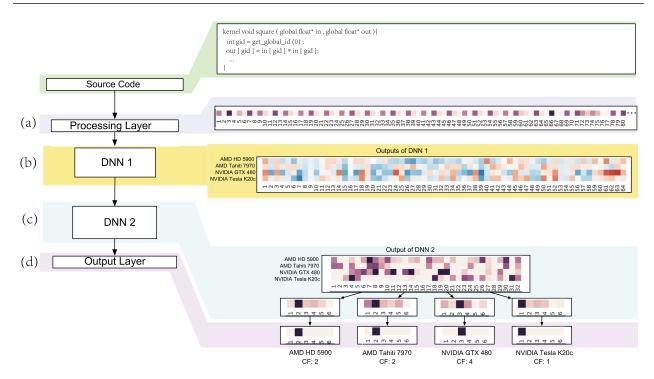

3) Deep Neural Networks: In recent years, deep neural networks [85] have been shown to be a powerful tool for tackling a range of machine learning tasks such as image recognition [86], [87] and audio processing [88]. Deep neural networks (DNNs) have recently been used to model program source code [89] for various software engineering tasks (see also Section VI-C), but so far there is little work of applying DNNs to compiler optimization. A recent attempt in this direction is the DeepTune framework [78], which uses DNNs to extract source code features (see also Section V-C).

The advantage of DNNs is that they can compactly represent a significantly larger set of functions than a shallow network, where each function is specialized at processing part of the input. This capability allows DNNs to model the complex relationship between the input and the output (i.e., the prediction). As an example, consider Fig. 8 that visualizes the internal state of DeepTune [78] when predicting the optimal thread coarsening factor for an OpenCL kernel (see Section II-D). Fig. 8(a) shows the first 80 elements of the input source code tokens as a heatmap in which each cell's color reflects an integer value assigned to a specific token. Fig. 8(b) shows the neurons of the first DNN for each of the four GPU platforms, using a red-blue heatmap to visualize the intensity of each activation. If we have a close look at the heatmap, we can find a number of neurons in the layer with different responses across platforms. This indicates that the DNN is partly specialized to the target platform. As information flows through the network [layers (c) and (d) in Fig. 8], the layers become progressively more specialized to the specific platform.

# **B.** Unsupervised Learning

Unlike supervised learning models which learn a correlation from the input feature values to the corresponding outputs, unsupervised learning models only take it from the input data (e.g., the feature values). This technique is often used to model the underlying structure of distribution of the data.

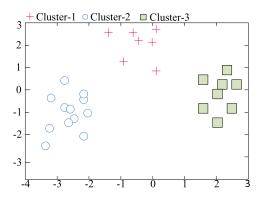

Clustering is a classical unsupervised learning problem. The k-means clustering algorithm [90] groups the input data into k clusters. For example, in Fig. 9, a k-means algorithm is used to group data points into three clusters on a 2-D

Fig. 8. A simplified view of the internal state for the DeepTune DNN framework [78] when it predicts the optimal OpenCL thread coarsening factor. Here, a DNN is learned for each of the four target GPU architectures. The activations in each layer of the four models increasingly diverge (or specialize) toward the lower layers of the model. It is to note that some of the DeepTune layers are omitted to aid presentation.

Fig. 9. Using k-means to group data points into three clusters. In this example, we group the data points into three clusters on a 2-D feature space.

feature space. The algorithm works by grouping data points that are close to each other on the feature space into a cluster. K-means is used to characterize program behavior [60], [91]. It does so by clustering program execution into phase groups, so that we can use a few samples of a group to represent the entire program phases within a group. K-means is also used in the work presented in [92] to summarize the code structures of parallel programs that benefit from similar optimization strategies. In addition to k-means, Martins *et al.* employed the fast Newman clustering algorithm [93] which works on network structures to group functions that may benefit from similar compiler optimizations [94].

PCA is a statistical method for unsupervised learning. This method has been heavily used in prior work to reduce the feature dimension [17], [25], [95]–[97]. Doing so allows us to model a high-dimensional feature space with a smaller number of representative variables which, in combination, describe most of the variability found in the original feature space. PCA is often used to discover the common pattern in the data sets in order to help clustering exercises. It is used to select representative programs from a benchmark suite [95], [98]. In Section V-D, we discuss PCA in further details.

Autoencoders are a recently proposed artificial neural network architecture for discovering the efficient codings of input data in an unsupervised fashion [99]. This technique can be used in combination of a natural language model to first extract features from program source code and then find a compact representation of the source code features [100]. We discuss autoencoders in Section V-D when reviewing feature dimensionality reduction techniques.

# C. Online Learning

1) Evolutionary Search: Evolutionary algorithms (EAs) or evolutionary computation such as genetic algorithms (GAs), GP, <sup>4</sup> and stochastic-based search have been employed

to find a good optimization solution from a large search space. An EA applies principles inspired by biological evolution to find an optimal or near-optimal solution for the target problem. For instance, the SPIRAL autotuning framework uses a stochastic evolutionary search algorithm to choose a fast formula (or transformation) for signal processing applications [101]. Li *et al.* use GAs to search for the optimal configuration to determine which sorting algorithm to use based on the unsorted data size [102]. The Petabricks compiler offers a more general solution by using EAs to search for the best performing configurations for a set of algorithms specified by the programmer [103]. In addition to code optimization, EAs have also been used to create Pareto optimal program benchmarks under various criteria [104].

As an example, consider how an EA can be employed in the context of iterative compilation to find the best compiler flags for a program [25], [36], [105]. Fig. 10 depicts how an EA can be used for this purpose. The algorithm starts from several populations of randomly chosen compiler flag settings. It compiles the program using each individual compiler flag sequence, and uses a fitness function to evaluate how well a compiler flag sequence performs. In our case, a fitness function can simply return the reciprocal of a program runtime measurement, so that compiler settings that give faster execution time will have a higher fitness score. In the next epoch, the EA algorithm generates

Fig. 10. Using an EA to perform iterative compilation. The algorithm starts from several initial populations of randomly chosen compiler flag sequences. It evaluates the performance of individual sequences to remove poorly performing sequences in each population. It then applies crossover and mutation to create a new generation of populations. The algorithm returns the best performing program binary when it terminates.

<sup>&</sup>lt;sup>4</sup>A GA is represented as a list of actions and values, often a string, while a GP is represented as a tree structure of actions and values. For example, GP is applied to the abstract syntax tree of a program to search for useful features in [70].

the next populations of compiler settings via mechanisms such as reproduction (crossover) and mutation among compiler flag settings. This results in a new generation of compiler flag settings and the quality of each setting will be evaluated again. In a mechanism analogous to natural selection, a certain number of poorly performing compiler flags within a population are chosen to die in each generation. This process terminates when no further improvement is observed or the maximum number of generations is reached, and the algorithm will return the best found program binary as a result.

There are three key operations in an EA algorithm: selection, crossover, and mutation. The probability of an optimization option being selected for dying is often inversely proportional to its fitness score. In other words, options that are relatively fitter (e.g., give faster program runtime) are more likely to survive and remain a part of the population after selection. In crossover, a certain number of offsprings are produced by mixing some existing optimization options (e.g., compiler flags). The likelihood of an existing option being chosen for crossover is again proportional to its fitness. This strategy ensures that good optimizations will be preserved over generations, while poorly performing optimizations will gradually die out. Finally, mutation randomly changes a preserved optimization, e.g., by turning on/off an option or replacing a threshold value in a compiler flag sequence. Mutation reduces the chance that the algorithm gets stuck with a locally optimal optimization.

EAs are useful for exploring a large optimization space where it is infeasible to just enumerate all possible solutions. This is because an EA can often converge to the most promising area in the optimization space quicker than a general search heuristic. The EA is also shown to be faster than a dynamic-programming-based search [24] in finding the optimal transformation for the fast Fourier transformation (FFT) [101]. When compared to supervised learning, EAs have the advantage of requiring little problem-specific knowledge, and hence they can be applied on a broad range of problems. However, because an EA typically relies on the empirical evidences (e.g., running time) for fitness evaluation, the search time can still be prohibitively expensive. This overhead can be reduced by using a machine-learningbased cost model [43] to estimate the potential gain (e.g., speedup) of a configuration (see also Section III-A). Another approach is to combine supervised learning and EAs [25], [106] by first using an offline learned model to predict the most promising areas of the design space (i.e., to narrow down the search areas), and then searching over the predicted areas to refine the solutions. Moreover, instead of predicting where in the search space to focus on, one can also first prune the search space to reduce the number of options to search over. For example, Jantz and Kulkarni show that the search space of phase ordering<sup>5</sup> can be greatly

<sup>5</sup>Compiler phase ordering determines at which order a set of compiler optimization passes should be applied to a given program.

Fig. 11. The working mechanism of reinforcement learning.

reduced if we can first remove phases whose application order is irrelevant to the produced code [107]. Their techniques are claimed to prune the exhaustive phase order search space size by 89% on average.

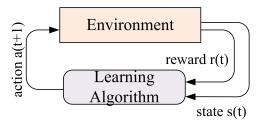

2) Reinforcement Learning: Another class of online learning algorithms is reinforcement learning (RL) which is sometimes called "learning from interactions." The algorithm tries to learn how to maximize the rewards (or performance) itself. In other words, the algorithm needs to learn, for a given input, what the correct output or decision to take is. This is different from supervised learning where the correct input/output pairs are presented in the training data.

Fig. 11 illustrates the working mechanism of RL. Here the learning algorithm interacts with its environment over a discrete set of time steps. At each step, the algorithm evaluates the current state of its environment, and executes an action. The action leads to a change in the state of the environment (which the algorithm can evaluate in the next time step), and produces an immediate reward. For example, in a multitasking environment, a state could be the CPU contention; when processor cores are idle, an action could be where to place a process, and a reward could be the overall system throughput. The goal of RL is to maximize the longterm cumulative reward by learning an optimal strategy to map states to actions.

RL is particularly suitable for modeling problems that have an evolving natural, such as dynamic task scheduling, where the optimal outcome is achieved through a series of actions. RL has been used in prior research to schedule RAM memory traffics [108], select software component configurations at runtime [109], and configure virtual machines [110]. An early work of using RL for program optimization was conduced by Lagoudakis and Littman [111]. They use RL to find the cutoff point to switch between two sorting algorithms: quickSort and insertionSort. CALOREE combines machine learning and control theories to schedule CPU resources on heterogeneous multicores [112]. For a given application, CALOREE uses control-theoretic methods to dynamically adjust the resource allocation, and machine learning to estimate the application's latency and power for a given resource allocation plan (to offer decision supports).

An interesting RL-based approach for scheduling parallel OpenMP programs is presented in [113]. This approach predicts the best number of threads for a target OpenMP

program when it runs with other competing workloads, aiming to make the target program run faster. This approach first learns a reward function offline based on static code features and runtime system information. The reward function is used to estimate the reward of a runtime scheduling action, i.e., the expected speedup when assigning a certain number of processor cores to an OpenMP program. In the next scheduling epoch, this approach uses the empirical observation of the application speedup to check if the reward function was accurate and the decision was good, and update the reward function if the model is found to be inaccurate.

In general, RL is an intuitive and comprehensive solution for autonomous decision making. But its performance depends on the effectiveness of the value function, which estimates the immediate reward. An optimal value function should lead to the greatest cumulative reward in the longer term. For many problems, it is difficult to design an effective value function or policy, because the function needs to foresee the impact of an action in the future. The effectiveness of RL also depends on the environment; if the number of possible actions is large, it can take RL a long time to converge to a good solution. RL also requires the environment to be fully observed, i.e., all the possible states of the environment can be anticipated ahead of time. However, this assumption may not hold in a dynamic computing environment due to unpredictable disturbances, e.g., changes in application inputs or application mixes. In recent years, deep learning techniques have been used in conjunction with RL to learn a value function. The combined technique is able to solve some problems that were deemed impossible in the past [114]. However, how to combine deep learning with RL to solve compilation and code optimization problems remains an open question.

#### D. Discussion

What model is best is the \$64000 question. The answer is: it depends. More sophisticated techniques may provide greater accuracy but they require large amounts of labeled training data—a real problem in compiler optimization. Techniques such as linear regression and decision trees require less training data compared to more advanced models such as SVMs and ANNs. Simple models typically work well when the prediction problem can be described using a feature vector that has a small number of dimensions, and when the feature vector and the prediction are linearly correlated. More advanced techniques such as SVMs and ANNs can model both linear and nonlinear problems on a higher dimensional feature space, but they often require more training data to learn an effective model. Furthermore, the performance of an SVM and an ANN also highly depends on the hyperparameters used to train the model. The optimal hyperparameter values can be chosen by performing cross validation on the training data. However, how to select

parameters to avoid overfitting while achieving a good prediction accuracy remains an outstanding challenge.

Choosing which modeling technique to use is nontrivial. This is because the choice of model depends on a number of factors: the prediction problem (e.g., regression or classification), the set of features to use, the available training examples, the training and prediction overhead, etc. In prior works, the choice of modeling technique largely relied on developer experience and empirical results. Many of the studies in the field of machine-learning-based code optimization do not fully justify the choice of the model, although some do compare the performance of alternate techniques. The OpenTuner framework addresses the problem by employing multiple techniques for program tuning [115]. OpenTuner runs multiple search techniques at the same time. Techniques which perform well will be given more candidate tuning options to examine, while poorly performed algorithms will be given fewer choices or disabled entirely. In this way, OpenTuner can discover which algorithm works best for a given problem during search.

One technique that has seen little investigation is the use of Gaussian processes [116]. Before the recent widespread interest in DNNs, these were a highly popular method in many areas of machine learning [117]. They are particularly powerful when the amount of training data is sparse and expensive to collect. They also automatically give a confidence interval with any decision. This allows the compiler writer to trade off risk versus reward depending on the application scenario.

Using a single model has a significant drawback in practice. This is because a one-size-fits-all model is unlikely to precisely capture behaviors of diverse applications, and no matter how parameterized the model is, it is highly unlikely that a model developed today will always be suited for tomorrow. To allow the model to adapt to the change of the computing environment and workloads, ensemble learning was exploited in prior works [73], [118], [119]. The idea of ensemble learning is to use multiple learning algorithms, where each algorithm is effective for particular problems, to obtain better predictive performance than could be obtained from any of the constituent learning algorithm alone [120], [121]. Making a prediction using an ensemble typically requires more computational time than doing that using a single model, so ensembles can be seen as a way to compensate for poor learning algorithms by performing extra computation. To reduce the overhead, fast algorithms such as decision trees are commonly used in ensemble methods (e.g., random forests), although slower algorithms can benefit from ensemble techniques as well.

#### V. FEATURE ENGINEERING

Machine-learning-based code optimization relies on having a set of high-quality features that capture the important characteristics of the target program. Given that there is an

Table 4 Summary of Features Discussed in Section V

| Feature                       | Description                                                                                                                               |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Static code features          | Features gathered from source code<br>or the compiler intermediate rep-<br>resentations, such as instruction<br>counts. See Section V-A1. |

| Tree and graph based features | Features extracted from the program graph, such as the number of nodes of different types. See Section V-A2.                              |

| Dynamic features              | Features obtained through dynamic profiling or during runtime execution, such as performance counter values. See Section V-A3.            |

| Reaction-based features       | Speedups or execution time obtained by profiling the target program under specific compiler settings. See Section V-B.                    |

unbounded number of potential features, finding the right set is a nontrivial task. In this section, we review how previous work chooses features, a task known as feature engineering. Tables 4 and 5 summarize the range of program features and feature engineering techniques discussed in this section, respectively.

# A. Feature Representation

Various forms of program features have been used in compiler-based machine learning. These include static code structures [122] and runtime information such as system load [118], [123] and performance counters [53].

- 1) Static Code Features: Static program features such as the number and type of instructions are often used to describe a program. These features are typically extracted from the compiler intermediate representations [29], [46], [52], [80] in order to avoid using information extracted from dead code. Table 6 gives some of the static code features that were used in previous studies. Raw code features are often used together to create a combined feature. For example, one can divide the number of load instructions by the number of total instructions to get the memory load ratio. An advantage of using static code features is that the features are readily available from the compiler intermediate representation.

- 2) Tree- and Graph-Based Features: Singer and Veloso represent the FFT in a split tree [124]. They extract from the tree a set of features, by counting the number of nodes of various types and quantifying the shape of the tree. These treebased features are then used to build a neural-network-based

Table 5 Feature Engineering Techniques Discussed in Section V.

| Problem                          | Techniques                                                                                                        |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Feature selection                | Pearson correlation coefficient, mu-<br>tual information, regression analy-<br>sis. See Section V-D1.             |

| Feature dimensionality reduction | Principal component analysis (PCA), factor analysis, linear discriminant analysis, autoencoder. See Section V-D2. |

Table 6 Example Code Features Used in Prior Works

| Description             | Examples                                                        |

|-------------------------|-----------------------------------------------------------------|

| Arithmetic instructions | #floating point instr., #integer instr.,<br>#method call instr. |

| Memory operations       | #load instr, #store instr.                                      |

| Branch instructions     | #conditional branch instr, #uncon-<br>ditional branch instr     |

| loop information        | #loops, loop depth                                              |

| parallel information    | #work threads, work group size                                  |

cost function that predicts which of the two FFT formulas runs faster. The cost function is used to search for the best performing transformation.

Park et al. present a unique graph-based approach for feature representations [125]. They use an SVM where the kernel is based on a graph similarity metric. Their technique requires hand-coded features at the basic block level, but thereafter, graph similarity against each of the training programs takes the place of global features. Mailike shows that spatial-based information, i.e., how instructions are distributed within a program, extracted from the program's data flow graph could be a useful feature for machine-learningbased compiler optimization [126]. Nobre et al. also exploit graph structures for code generation [26]. Their approach targets the phase ordering problem. The order of compiler optimization passes is represented as a graph. Each node of the graph is an optimization pass and connections between nodes are weighted in a way that subsequences with higher aggregated weights are more likely to lead to faster runtime. The graph is automatically constructed and updated using iterative compilation (where the target program is complied using different compiler passes with different orders). A design space exploration algorithm is employed to drive the iterative compilation process.

3) Dynamic Features: While static code features are useful and can be extracted at static compile time (hence feature extraction has no runtime overhead), they have drawbacks. For examples, static code features may contain information of code segments that rarely get executed, and such information can confuse the machine learning model; some program information such as the loop bound depends on the program input, which can only be obtained during execution time; and static code features often may not precisely capture the application behavior in the runtime environment [such as resource contention and input/ output (I/O) behavior] as such behavior highly depends on the computing environment such as the number of available processors and corunning workloads.

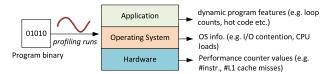

As illustrated in Fig. 12, dynamic features can be extracted from multiple layers of the runtime environment. At the application layer, we can obtain information such as loop iteration counts that cannot be decided at compile time, dynamic control flows, frequently executed code regions, etc. At the operating system level, we can observe the memory and I/O behavior of the application as well as CPU load and thread contention, etc. At the hardware

Fig. 12. Dynamic features can be extracted from multiple layers of the computing environment.

level, we can use performance counters to track information such as how many instructions have been executed and of what types, and the number of cache loads/stores as well as branch misses, etc.

Hardware performance counter values, such as executed instruction counts and cache miss rate, are therefore used to understand the application's dynamic behaviors [53], [127], [128]. These counters can capture low-level program information such as data access patterns, branches, and computational instructions. One of the advantages of performance counters is that they capture how the target program behaves on a specific hardware and avoid the irrelevant information that static code features may bring in. In addition to hardware performance counters, operating system level metrics, such as system load and I/O contention, are also used to model an application's behavior [39], [123]. Such information can be externally observed without instrumenting the code, and can be obtain during offline profiling or program execution time.

While effective, collecting dynamic information could incur prohibitively overhead and the collected information can be noisy due to competing workloads and operating system scheduling [129] or even subtle settings of the execution environment [130]. Another drawback of performance counters and dynamic features is that they can only capture the application's past behavior. Therefore, if the application behaves significantly different in the future due to the change of program phases or inputs, then the prediction will be drawn on an unreliable observation. As such, dynamic and static features are often used in combination in prior works in order to build a robust model.

# **B.** Reaction-Based Features

Cavazos et al. present a reaction-based predictive model for software—hardware codesign [131]. Their approach profiles the target program using several carefully selected compiler options to see how program runtime changes under these options for a given microarchitecture setting. They then use the program "reactions" to predict the best available application speedup. Fig. 13 illustrates the difference between a reaction-based model and a standard program feature-based model. A similar reaction-based approach is used in [132] to predict speedup and energy efficiency for an application that is parallelized thread-level speculation (TLS) under a given microarchitectural configuration. Note that while a reaction-based approach does not use static

Fig. 13. Standard feature-based modeling (a) versus reaction-based modeling (b). Both models try to predict the speedup for a given compiler transformation sequence. The program feature-based predictor takes in static program features extracted from the transformed program, while the reaction-based model takes in the target transformation sequence and the measured speedups of the target program, obtained by applying a number of carefully selected transformation sequences. Diagrams are reproduced from [131].

code features, developers must carefully select a few settings from a large number of candidate options for profiling, because poorly chosen options can significantly affect the quality of the model.

#### C. Automatic Feature Generation

As deriving good features is a time-consuming task, a few methods have been proposed to automatically generate features from the compiler's intermediate representation (IR) [70], [133]. The work of [70] uses GP to search for features, but required a huge grammar to be written, some 160 kB in length. Although much of this can be created from templates, selecting the right range of capabilities and search space bias is nontrivial and up to the expert. The work of [133] expresses the space of features via logic programming over relations that represent information from the IRs. It greedily searches for expressions that represent good features. However, their approach relies on expert selected relations, combinators, and constraints to work. Both approaches closely tie the implementation of the predictive model to the compiler IR, which means changes to the IR will require modifications to the model. Furthermore, the time spent in searching features could be significant for these approaches.

The first work to employ neural network to extract features from program source code for compiler optimization was conducted by Cummins *et al.* [78]. Their system, namely DeepTune, automatically abstracts and selects appropriate features from the raw source code. Unlike prior work

where the predictive model takes in a set of human-crafted features, program code is used directly in the training data. Programs are fed through a series of neural-network-based language models which learn how the code correlates with the desired optimization options (see also Fig. 8). Their work also shows that the properties of the raw code that are abstracted by the top layers of the neural networks are mostly independent of the optimization problem. While promising, it is worth mentioning that dynamic information such as the program input size and performance counter values are often essential for characterizing the behavior of the target program. Therefore, DeepTune does not completely remove human involvement for feature engineering when static code features are insufficient for the optimization problem.

#### D. Feature Selection and Dimension Reduction

Machine learning uses features to capture the essential characteristics of a training example. Sometimes we have too many features. As the number of features increases, so does the number of training examples needed to build an accurate model [134]. Hence, we need to limit the dimension of the feature space. In compiler research, commonly, an initial large, high-dimensional candidate feature space is pruned via feature selection [52], or projected into a lower dimensional space [17]. In this section, we review a number of feature selection and dimension reduction methods.

1) Feature Selection: Feature selection requires understanding how a particular feature affects the prediction accuracy. One of the simplest methods for doing this is applying the Pearson correlation coefficient. This metric measures the linear correlation between two variables and is used in numerous works [55], [92], [122], [135] to filter out redundant features by removing features that have a strong correlation with an already selected feature. It has also been used to quantify the relation of the select features in regression. One obvious drawback of using Pearson correlation as a feature ranking mechanism is that it is only sensitive to a linear relationship.

Another approach for correlation estimation is mutual information [131], [136], which quantifies how much information of one variable (or feature) can be obtained through another variable (feature). Like correlation coefficient, mutual information can be used to remove redundant features. For example, if the information of feature x can be largely obtained through another existing feature y, feature *x* can then be taken out from the feature set without losing much information on the reduced feature set.

Both correlation coefficient and mutual information evaluate each feature independently with respect to the prediction. A different approach is to utilize regression analysis for feature ranking. The underlying principal of regression analysis is that if the prediction is the outcome of regression model based on the features, then the most important features should have the highest weights (or coefficients) in the model, while features uncorrelated with the output variables should have weights close to zero. For example, least absolute shrinkage and selection operator (LASSO) regression analysis is used in [137] to remove less useful features to build a compiler-based model to predict performance. LASSO has also been used for feature selection to tune the compiler heuristics for the TRIPS processor [138].

In general, feature selection remains an open problem for machine learning, and researchers often follow a "trailand-error" approach to test a range of methods and feature candidates. This makes automatic feature selection framework like FEAST [139] and HERCULES [140] attractive. The former framework employs a range of existing feature selection methods to select useful candidate features, while the latter searches for the most important static code features from a set of predefined patterns for loops.

2) Feature Dimensionality Reduction: While feature selection allows us to select the most important features, the resulted feature set can still be too large to train a good model, especially when we only have a small number of training examples. By reducing the number of dimensions, the learning algorithm can often perform more efficiently on a limited training data set. Dimension reduction is also important for some machine learning algorithms such as KNN to avoid the effect of the curse of dimensionality [141].

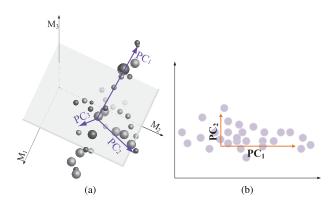

PCA is a well-established feature reduction technique [142]. It uses orthogonal linear transformations to reduce the dimensionality of a set of variables, i.e., features in our case.

Fig. 14 demonstrates the use of PCA to reduce the number of dimensions. The input in this example is a 3-D space defined by  $M_1$ ,  $M_2$ , and  $M_3$ , as shown in Fig. 14(a). Three components,  $PC_1$ ,  $PC_2$ , and  $PC_3$ , which account for the variance of the data, are first calculated. Here,  $PC_1$  and  $PC_2$  contribute most to the variance of the data and PC3 accounts for the least variance. Using only  $PC_1$  and  $PC_2$ , one can transform the original, 3-D space into a new, 2-D coordinate

Fig. 14. Using PCA to reduce dimensionality of a 3-D feature space. The principal components are first computed (a). Then, the first two principal components (PC1 and PC2) are selected to represent the original 3-D feature space on a new 2-D space (b).

system [as illustrated in Fig. 14(b)] while preserving much of the variance of the original data.

PCA has been used in many prior compiler research works for feature reduction [17], [25], [55], [92], [95]–[97], [143]. It has also been used in prior works to visualize the working mechanism of a machine learning model, e.g., to show how benchmarks can be grouped in the feature space [123], by projecting features from a high-dimensional space into a 2-D space.