#### **Project: IEEE P802.15 Working Group for Wireless Personal Area Networks (WPANs)**

Submission Title: H2020 EPIC Project: Next Generation FEC for Tb/s and THz Systems Date Submitted: 7 May, 2018 Source: Onur Sahin, InterDigital Europe Address: 64 Great Eastern St, InterDigital Europe, London, UK, EC2A 3QR Voice:+447459205055, FAX:+442077494196, E-Mail:onur.sahin@interdigital.com

**Re:** n/a

**Abstract:** This talk will give an introduction and overview of H2020 EPIC project. The project content and objectives, with the ultimate target of design and implementation of practical ultra-high speed FEC technology for B5G systems, will be detailed. The FEC design framework of the EPIC project which holistically unifies the information theoretic code design principles with advanced VLSI techniques will be discussed. Based on the inherent trade-offs between the coding theory and efficient FEC architecture design, e.g. in terms randomness, parallel/serial operations, locality, the design space exploration (DSE) figures of all three major code-class, e.g. Turbo codes, LDPC, and Polar codes, will be provided.

Purpose: Information of IEEE 802.15 IG THz

**Notice:** This document has been prepared to assist the IEEE P802.15. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein.

**Release:** The contributor acknowledges and accepts that this contribution becomes the property of IEEE and may be made publicly available by P802.15.

The EPIC project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 760150.

# H2020 EPIC Project: Next Generation FEC for Tb/s and THz Systems

Enabling Practical Wireless Tb/s Communications with Next Generation Channel Coding

# What is EPIC?

- EPIC project designs and implements next generation FEC technology for a number of 5G and beyond (B5G) use cases, primarily within ultra-high speed (>100Gbps) wireless systems (THz).

- 3-year (Sept 2017-Sept 2020) project is executed by 8 partners with in-depth expertise in coding theory&algorithm development, FEC implementation, and system-level design.

# **Partners:**

ເງງອ

TECHNISCHE UNIVERSITÄT KAISERSLAUTERN

ΤΕCΗΝΙΚ**ΌΝ**

Technikon Forschungs- und Planungsgesellschaft mbH (Coordinator) Villach, Austria

InterDigital Europe Ltd. London, United Kingdom

Interur Leuve

Interuniversitair Micro-Electronica Centrum (imec) Leuven, Belgium

Polaran Ltd. Ankara, Turkey

Technische Universität Kaiserslautern (Technical Lead) Kaiserslautern, Germany

Ericsson AB Stockholm, Sweden

Institut Mines-Télécom, IMT Atlantique Brest, France

IMT Atlantique Bretagne-Pays de la Loire École Mines-Télécom

ERICSSON

Creonic GMBH Kaiserslautern, Germany

6 May, 2018

Enabling Practical Wireless Tb/s Communications with Next Generation Channel Coding

# **EPIC Project Objectives**

- Design and implement next generation Forward Error Correction (FEC) for wireless Tb/s technology and Beyond-5G (B5G) systems.

- Advance state-of-the-art Turbo, Low Density Parity Check (LDPC), and Polar Codes and develop the principal channel coding technology for wireless Tb/s technology.

- Devise a disruptive FEC design framework to unify algorithmic and implementation domains.

- Validate and demonstrate the developed FEC technology in virtual silicon tape-out and provide first-in-class wireless Tb/s FEC chipset architecture block.

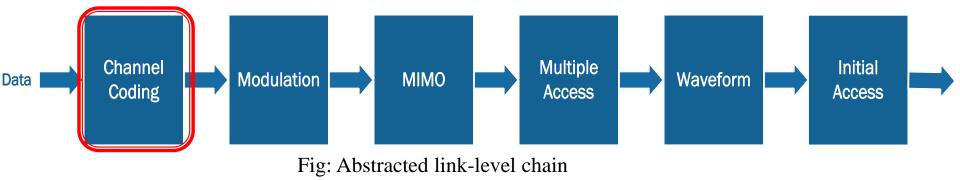

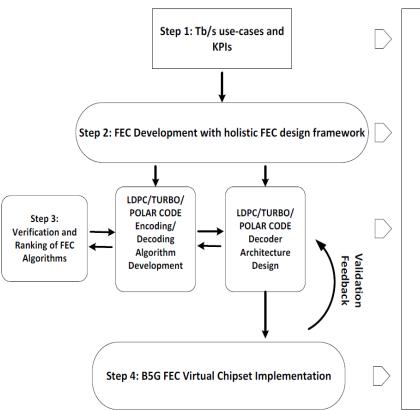

# EPIC Methodology for B5G FEC Technology Design

- Identify B5G use-cases, link level, and FEC requirements in terms of communication and implementation performances

- Execute on EPIC design framework to develop FEC technology according to the FEC requirement guidelines

- Develop LDPC/Turbo/Polar Encoding/Decoding Algorithms

- Implement selected B5G FEC candidates in virtual chipset

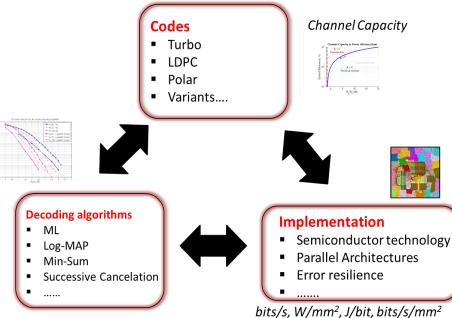

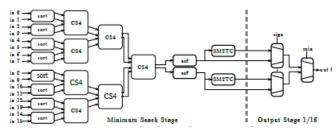

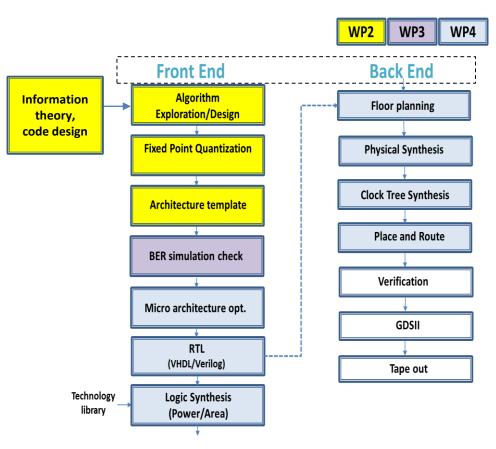

# **EPIC Design Framework**

- Holistic approach that combines information-theoretic code design principles with advanced VLSI techniques

- Objective: To develop highly-optimized dedicated architectures in advanced semiconductor technology nodes

- The framework is driven by key performance trade-offs such as:

- Code, algorithm and implementation level parameters (code randomness/locality/regularity, decoding algorithm complexity, bit/word/sub-block level parallel vs. sequential architectures, optimality vs. approximation)

- Communication performance and implementation efficiency KPIs (BER/FER, throughput, energy/power/area efficiency)

bit/frame error rates

EPIC

EPIC

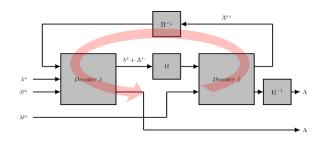

# **Information Theory/Implementation Gap**

Energy efficient high throughput architectures require

- Large parallelism

- Large regularity

- Large locality

- LDPC: Tanner Graph

- Turbo Code: Interleaver

Some decoding algorithms are inherently serial

- Turbo-Code decoding

- Polar Code successive cancelation

8

#### Processing Block 1 Network Processing Block 2 Softdecoder 1 (MAP) Softdecoder 2 (MAP) Variable\_n1 Check\_n1 Variable\_nN

# **Strong link with Silicon technology**

- Information theory, algorithms, architecture and implementation in Silicon are mapped on the technical workpackages

- Selected designs will go all the way through the ASIC implementation (front-end and back-end) in deeply-scaled CMOS

- Target technology node: 7nm CMOS

- Better area efficiency, better energy efficiency

# **B5G use-cases and system-level&FEC requirements**

- Explored potential wireless ultra-high throughput use-cases for B5G.

- System requirements and KPIs (bit and frame error rate, throughput, latency, power, cost, flexibility)

- FEC level-KPIs utilizing system requirements (bit and frame error rate, throughput, latency, energy efficiency, area efficiency, and power density)

|                       | BER             | Flexibility | Latency   | Throughput |

|-----------------------|-----------------|-------------|-----------|------------|

|                       |                 |             |           | [Gbps]     |

| Virtual reality       | 10^-6           | high        | 0.5ms     | 500,00     |

| Data kiosk            | 10^-12          | low         | 0.5ms     | 1000,00    |

| Backhaul              | 10^-8           | medium      | 100ns     | 250,00     |

| Intra-device com.     | 10^-12          | low         | 100ns     | 500,00     |

| Fronthaul             | 10^-12          | medium      | 25ns      | 1000,00    |

| Data center           | 10^-12 ~ 10^-15 | medium      | 100ns     | 1000,00    |

| Hybrid wireless fiber | 10^-12          | medium      | 200ns     | 1000,00    |

| High speed satellite  | 10^-10          | medium      | max ~10ms | 100-1000   |

EPIC

# **EPIC FEC Implementation KPI Bounds – Broad strokes**

- Practical FEC chip **area constraint** on a SoC: ~10 mm<sup>2</sup>

- FEC chip **power budget** to avoid heat removal issues: ~1 W

- FEC decoder throughput: 1 Tbps

- Detailed FEC KPI requirements in public report: D1.2 B5G Wireless Tb/s FEC KPI Requirements and Technology Gap Analysis (available at <u>https://epic-h2020.eu/</u>)

| EPIC FEC KPI bounds     |               |  |  |  |

|-------------------------|---------------|--|--|--|

| Area limit              | 10 mm²        |  |  |  |

| Area efficiency limit   | 100 Gb/s/ mm² |  |  |  |

| Energy efficiency limit | ~1 pJ/bit     |  |  |  |

| Power density limit     | 0.1 W/mm²     |  |  |  |

EPIC

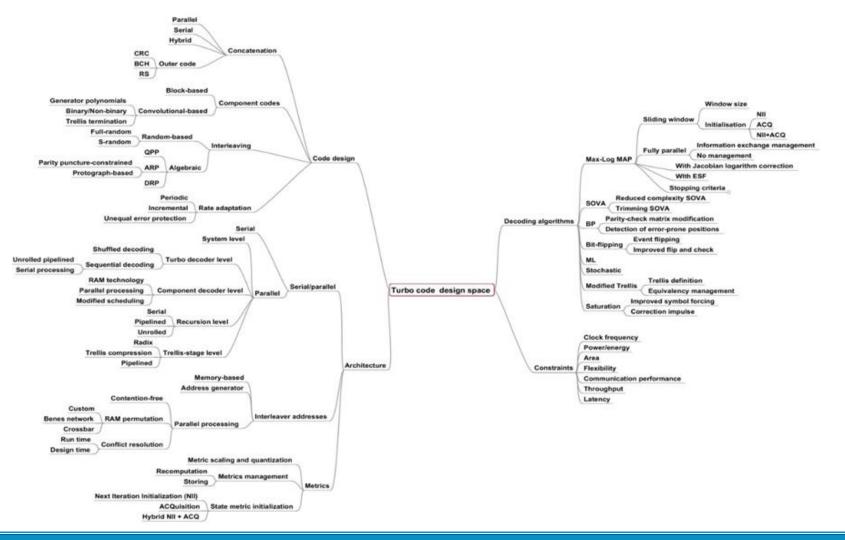

#### **Design Space Turbo-Codes**

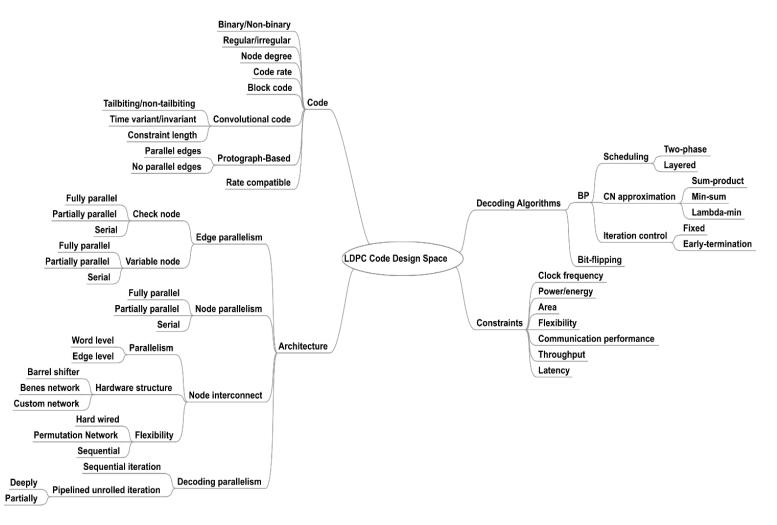

#### **Design Space LDPC Codes**

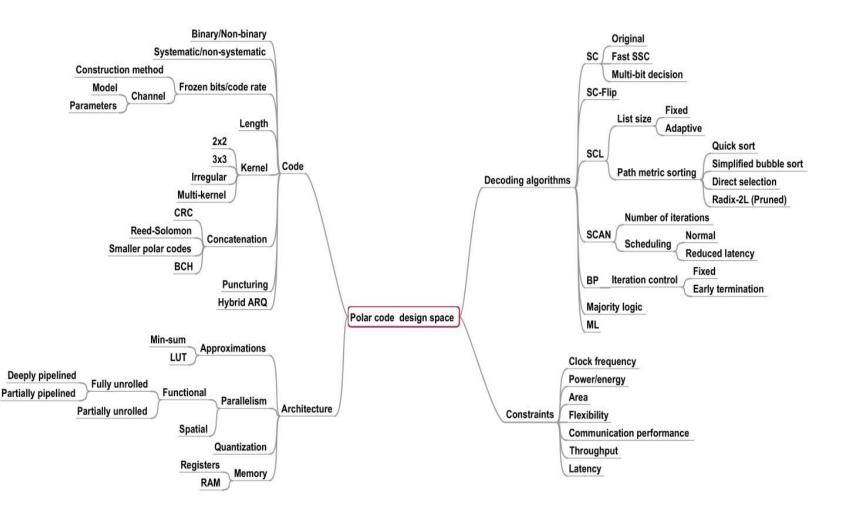

#### **Design Space Polar Codes**

#### **Current Status and Future Work**

- EPIC project has explored various THz/Tbps B5G use-cases, and derived their system&FEC-level KPIs.

- EPIC architecture-aware FEC design framework is developed.

- Active design and implementation study of B5G FEC technology.

- Project progress and reports are available at: <u>https://epic-h2020.eu/</u>.

# **General Project Information**

- Project reference: **760150**

- Project start: 1<sup>st</sup> September 2017

- Duration: **3 years**

- Total costs/EC contribution: EUR 2.966.268,75

- Eight partners from seven different European countries:

- Creonic Gmbh , Ericsson AB, IMEC, Institut Mines-Telecom, InterDigital Europe, Polaran, Technikon, Technische Universitaet Kaiserslautern

- Mission: EPIC aims to develop a new generation of Forward-Error-Correction (FEC) codes in a manner that will serve as a fundamental enabler of practicable beyond 5G wireless Tb/s solutions and also to develop and utilize a disruptive FEC design framework allowing to advance state-of-the-art FEC schemes.

- Website: <u>www.epic-h2020.eu</u>

- Twitter: <u>Epic760150</u>; Linkedin: <u>https://www.linkedin.com/in/epic-project-184362150</u>

# **EPIC Grant Agreement No. 760150**

"The EPIC project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 760150."

If you need further information, please contact the coordinator: TECHNIKON Forschungs- und Planungsgesellschaft mbH Burgplatz 3a, 9500 Villach, AUSTRIA Tel: +43 4242 233 55 Fax: +43 4242 233 55 77 E-Mail: coordination@epic-h2020.eu

The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author's view – the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability.

Enabling Practical Wireless Tb/s Communications with Next Generation Channel Coding

6 May, 2018

Enabling Practical Wireless Tb/s Communications with Next Generation Channel Coding