|  |                  | Men                                   | nory                         |                                        |

|--|------------------|---------------------------------------|------------------------------|----------------------------------------|

|  |                  | RWM                                   | NVRWM                        | ROM                                    |

|  | Random<br>Access | Non-Random<br>Access                  | EPROM<br>E <sup>2</sup> PROM | Mask-Programmed<br>Programmable (PROM) |

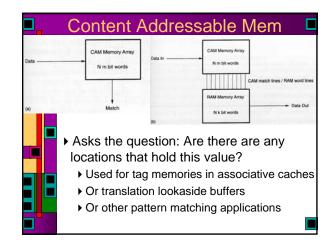

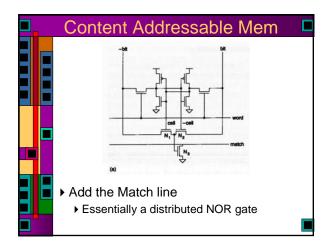

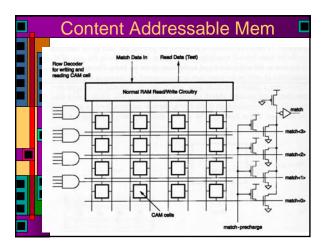

|  | SRAM<br>DRAM     | FIFO<br>LIFO<br>Shift Register<br>CAM | FLASH                        |                                        |

|  |                  |                                       |                              |                                        |

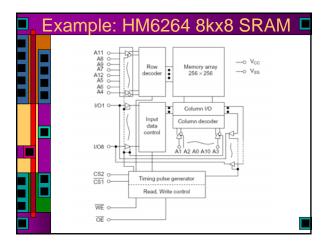

| l h             | HM6264                                                                                                                                                              | Interfa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ce            |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                 | HM6264BLP                                                                                                                                                           | BLSP/BLFP Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

|                 | NC []<br>A12 [] 2<br>A6 [] 4<br>A6 [] 4<br>A6 [] 6<br>A4 [] 6<br>A3 [] 7<br>A2 [] 8<br>A0 [] 10<br>II 11<br>II 002 [] 12<br>U03 [] 14<br>V <sub>65</sub> [] 4<br>II | 28         V <sub>CC</sub> 27         WE           28         WE           22         AB           24         AB           22         AE           21         AE           22         AE           21         AE           21         AE           21         DE           21         DE           21         DE           21         DE           21         DE           21         DE           20         CS1           100         IOS           100         IOS           100         IOS           100         IOS |               |

| Pin Description | n                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| Pin name        | Function                                                                                                                                                            | Pin name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Function      |

| A0 to A12       | Address input                                                                                                                                                       | WE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Write enable  |

| I/O1 to I/O8    | Data input/output                                                                                                                                                   | ŌE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output enable |

| CS1             | Chip select 1                                                                                                                                                       | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No connection |

| CS2             | Chip select 2                                                                                                                                                       | Voc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power supply  |

|                 |                                                                                                                                                                     | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ground        |

|          |         |      |          | Functior                  | n Tab                              | le      | l                  |

|----------|---------|------|----------|---------------------------|------------------------------------|---------|--------------------|

|          | ction ' |      |          |                           |                                    |         |                    |

| WE       | CS1     | CS2  | OE       | Mode                      | V <sub>cc</sub> current            | I/O pin | Ref. cycle         |

| ×        | н       | ×    | ×        | Not selected (power down) | I <sub>58</sub> , I <sub>581</sub> | High-Z  | -                  |

| $\times$ | ×       | L    | $\times$ | Not selected (power down) | I <sub>sa</sub> , I <sub>sa1</sub> | High-Z  | -                  |

| н        | L       | н    | н        | Output disable            | l <sub>cc</sub>                    | High-Z  | -                  |

| н        | L       | н    | L        | Read                      | l <sub>oc</sub>                    | Dout    | Read cycle (1)-(3) |

| L        | L       | н    | н        | Write                     | I <sub>cc</sub>                    | Din     | Write cycle (1)    |

| L        | L       | н    | L        | Write                     | I <sub>cc</sub>                    | Din     | Write cycle (2)    |

| Note:    | ×H      | or L |          |                           |                                    |         |                    |

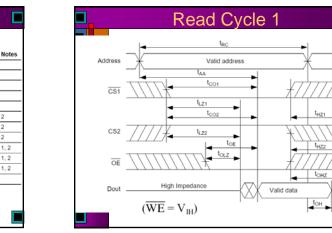

|                                         |        |                  |     | 64B-8L  |     | 64B-10L |     |      |

|-----------------------------------------|--------|------------------|-----|---------|-----|---------|-----|------|

| Parameter                               | Symbol | Min Max          | Max | Min Max | Max | Unit    | Not |      |

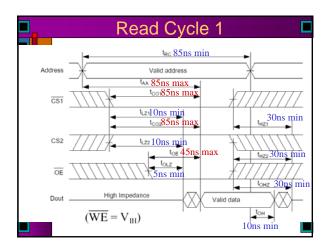

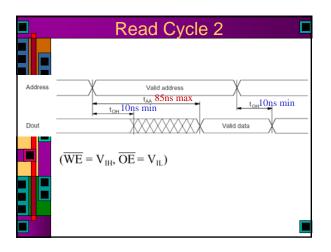

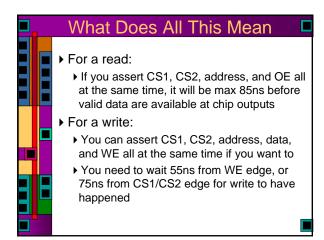

| Read cycle time                         |        | t <sub>RC</sub>  | 85  | _       | 100 | _       | ns  |      |

| Address access time                     |        | t <sub>aa</sub>  | -   | 85      | -   | 100     | ns  |      |

| Chip select access time                 | CS1    | l <sub>co1</sub> | —   | 85      | —   | 100     | ns  |      |

|                                         | CS2    | t <sub>cce</sub> | -   | 85      | -   | 100     | ns  |      |

| Output enable to output valid           |        | t <sub>oe</sub>  | -   | 45      | -   | 50      | ns  |      |

| Chip selection to output in low-Z       | CS1    | t <sub>LZ1</sub> | 10  | _       | 10  | _       | ns  | 2    |

|                                         | CS2    | t <sub>122</sub> | 10  | _       | 10  | _       | ns  | 2    |

| Output enable to output in low-Z        |        | touz             | 5   | -       | 5   | _       | ns  | 2    |

| Chip deselection in to output in high-Z | CS1    | t <sub>HZ1</sub> | 0   | 30      | 0   | 35      | ns  | 1, 3 |

|                                         | CS2    | t <sub>HZ2</sub> | 0   | 30      | 0   | 35      | ns  | 1,3  |

| Output disable to output in high-Z      |        | t <sub>oHZ</sub> | 0   | 30      | 0   | 35      | ns  | 1,2  |

| Output hold from address change         |        | t <sub>on</sub>  | 10  | _       | 10  | _       | ns  |      |

|                                         |        |                  |     |         |     |         |     |      |

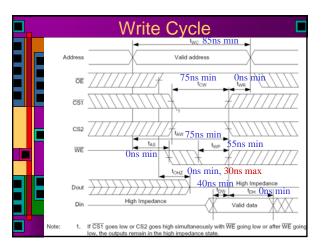

|                                                                                                                                                                                       |                                | HM62               | 64B-8L                | HM62   | 64B-10L   |         |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|-----------------------|--------|-----------|---------|-------|

| Parameter                                                                                                                                                                             | Symbol                         | Min                | Max                   | Min    | Max       | Unit    | Notes |

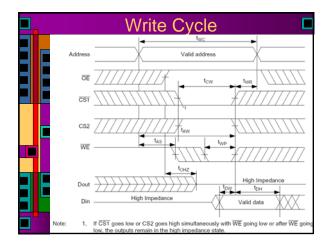

| Write cycle time                                                                                                                                                                      | twc                            | 85                 | -                     | 100    | -         | ns      |       |

| Chip selection to end of write                                                                                                                                                        | t <sub>cw</sub>                | 75                 | _                     | 80     | _         | ns      | 2     |

| Address setup time                                                                                                                                                                    | t <sub>as</sub>                | 0                  | _                     | 0      | -         | ns      | 3     |

| Address valid to end of write                                                                                                                                                         | t <sub>aw</sub>                | 75                 | _                     | 80     | _         | ns      |       |

| Write pulse width                                                                                                                                                                     | t <sub>wp</sub>                | 55                 | _                     | 60     | _         | ns      | 1,6   |

| Write recovery time                                                                                                                                                                   | t <sub>we</sub>                | 0                  | _                     | 0      | -         | ns      | 4     |

| WE to output in high-Z                                                                                                                                                                | twiz                           | 0                  | 30                    | 0      | 35        | ns      | 5     |

| Data to write time overlap                                                                                                                                                            | tow                            | 40                 | _                     | 40     | _         | ns      |       |

| Data hold from write time                                                                                                                                                             | t <sub>on</sub>                | 0                  | _                     | 0      | -         | ns      |       |

| Output active from end of write                                                                                                                                                       | tow                            | 5                  | _                     | 5      | _         | ns      |       |

| Output disable to output in high-Z                                                                                                                                                    | torz                           | 0                  | 30                    | 0      | 35        | ns      | 5     |

| Notes: 1. A write occurs during the overlap<br>at the latest transition among $\overline{CS}'$<br>at the earliest transition among $\overline{C}$<br>measured from the beginning of v | 1 going low,C<br>S1 going higt | S2 goin<br>n CS2 g | g high ar<br>oing low | d WE g | oing low. | A write | ends  |

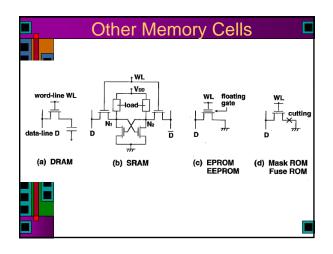

|   | R/W Memories In General                                                        |

|---|--------------------------------------------------------------------------------|

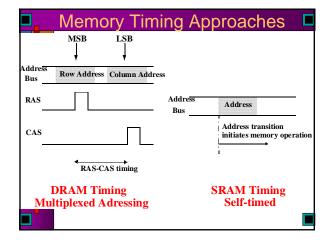

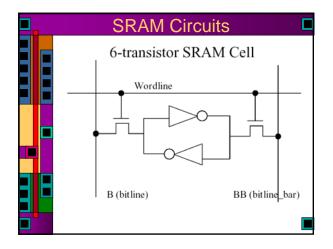

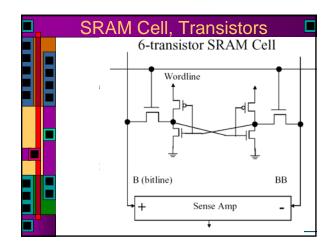

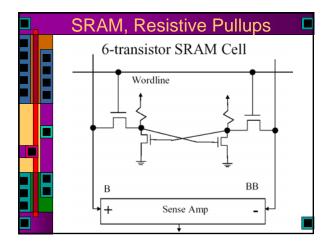

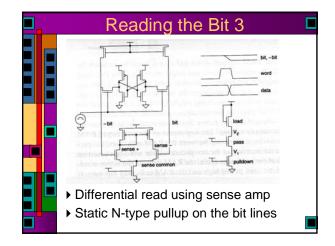

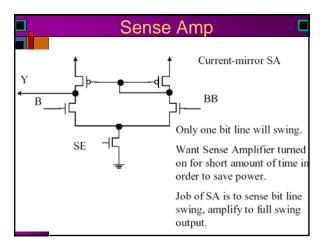

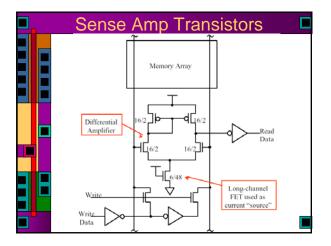

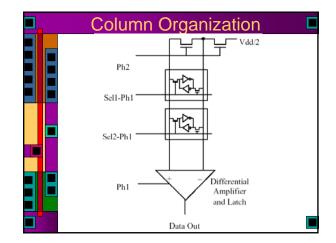

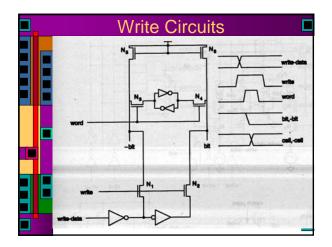

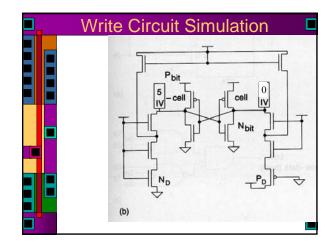

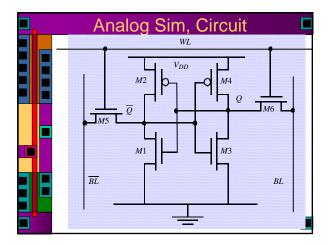

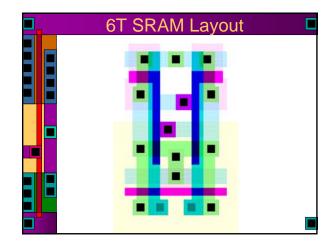

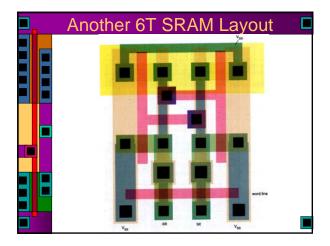

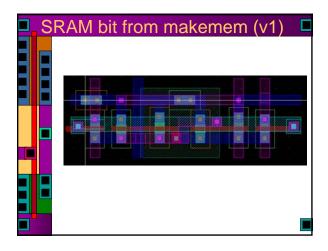

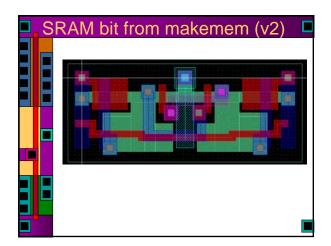

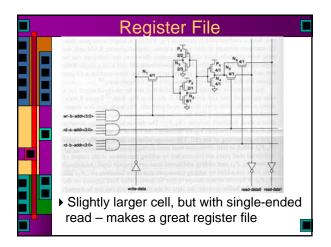

|   | • STATIC (SRAM)                                                                |

|   | Data stored as long as supply is applied<br>Large (6 transistors/cell)<br>Fast |

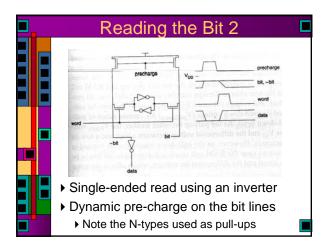

|   | Differential                                                                   |

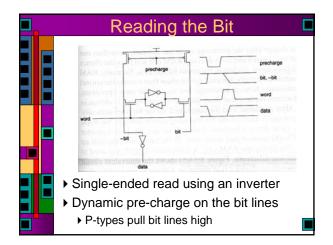

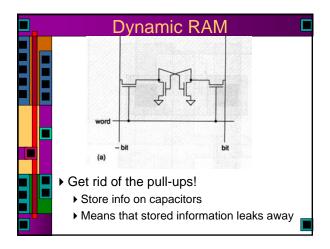

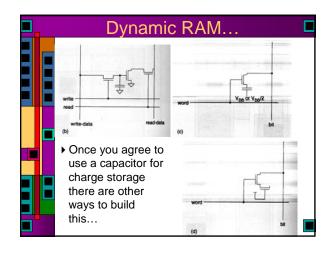

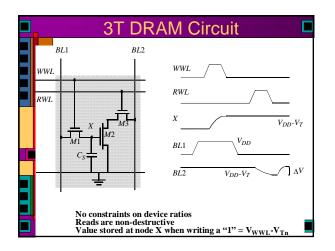

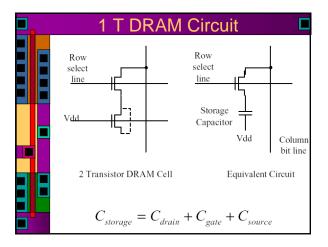

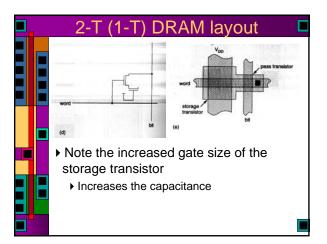

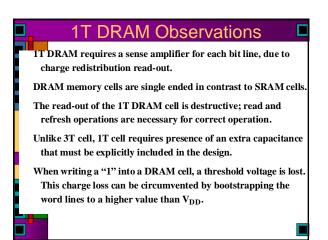

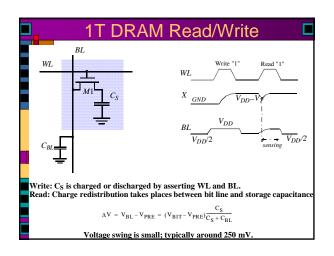

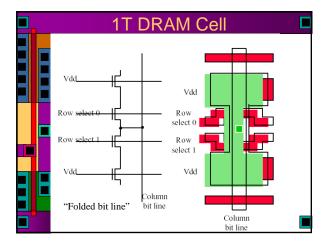

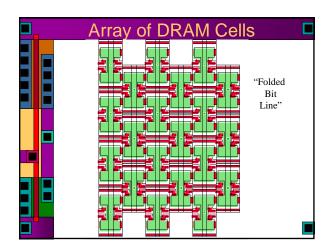

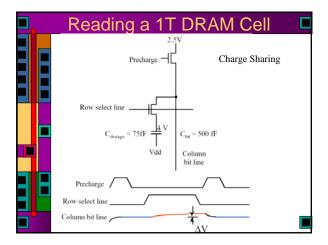

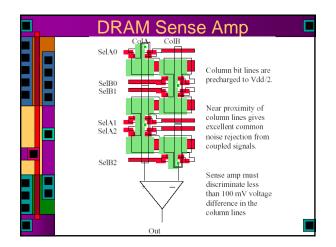

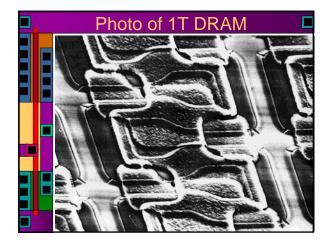

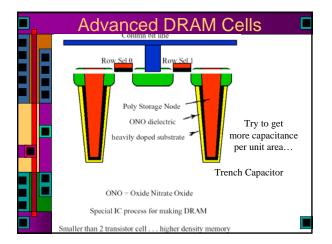

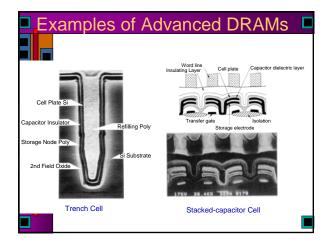

|   | • DYNAMIC (DRAM)                                                               |

| П | Periodic refresh required                                                      |

|   | Small (1-3 transistors/cell)                                                   |

|   | Slower                                                                         |

|   | Single Ended                                                                   |

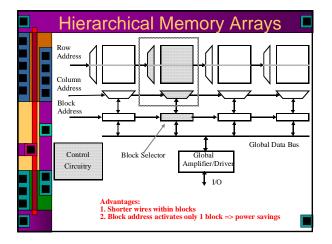

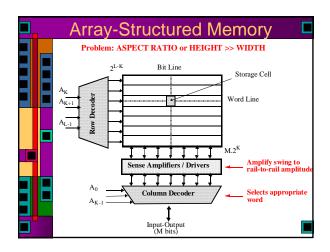

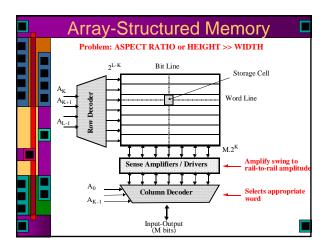

## Improving Speed, Power

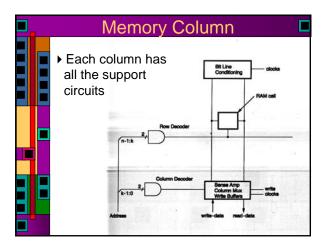

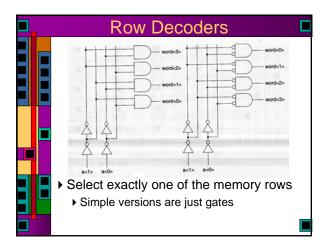

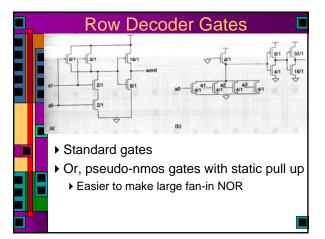

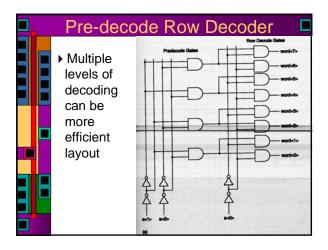

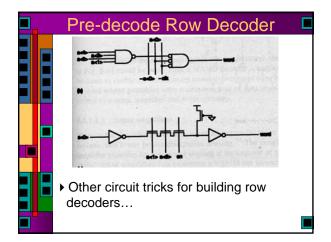

- Critical path runs through row decode, word line assertion

- Need smaller decoding, less word line capacitance in order to improve speed.

- Break a large array into smaller sub-arrays, and use hierarchical decoding to select a sub array

- PowerPC 32K x 8 cache broken into 32 blocks, each 1K x 8

- Cypress 1Mb Dual Port broken into 32 blocks, each 32 K bits (2<sup>5</sup> x 2<sup>5</sup> x 2<sup>10</sup> = 2<sup>20</sup>). Each blocks is 512 rows x 64 columns

- Mitsubishi SRAM (Rabaey text). 32 blocks of 128K bits (1024 rows x 128 columns)

- · Only one sub-array will be activated, saves power!!!!

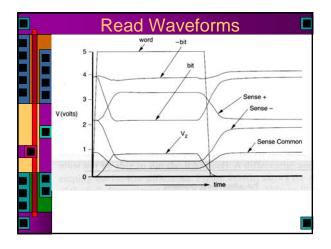

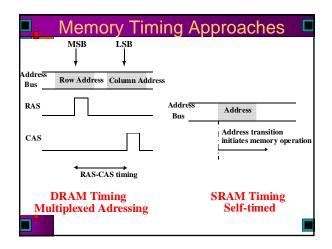

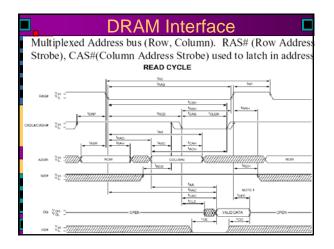

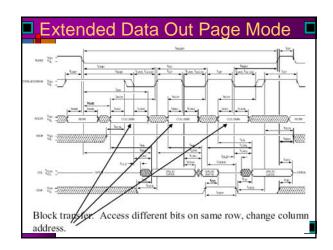

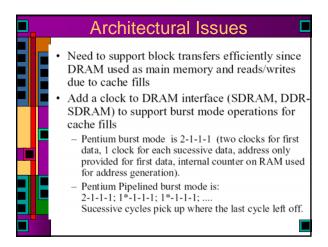

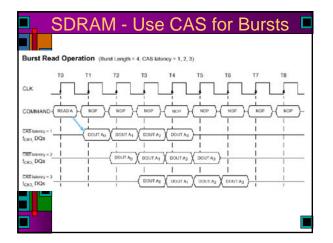

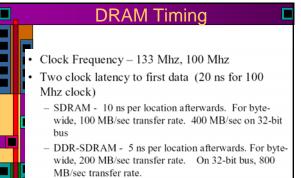

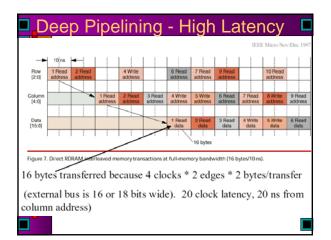

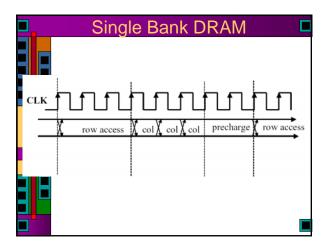

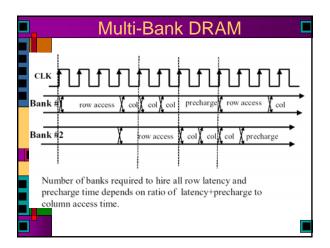

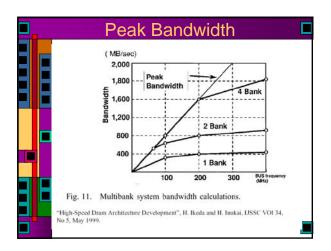

## Comments on Timing Typical times are Tras = 60 ns (RAS pulse width), Trc = 100 ns Extra time on Read cycle (RAS high) is needed to recharge bitlines Block mode transfers (Page mode transfers) read bits from same row Only change column address Time to first bit on row = 50ns, time to successive bits = 25 ns (we have access to all bits on this row, just need to mux them out).

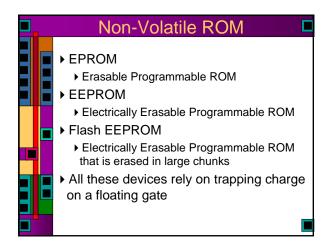

|   | Reali                                | stic PRC                        | DM Dev                             | /ices                            |

|---|--------------------------------------|---------------------------------|------------------------------------|----------------------------------|

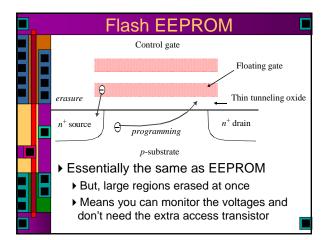

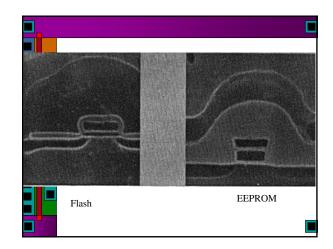

|   |                                      | EPROM<br>[Tomita91]             | EEPROM<br>[Terada89,<br>Pashley89] | Flash EEPROM<br>[Jinbo92]        |

|   | Memory size                          | 16 Mbit (0.6 μm)                | 1 Mbit (0.8<br>μm)                 | 16 Mbit (0.6 µm)                 |

| T | Chip size                            | 7.18 x 17.39<br>mm <sup>2</sup> | 11.8 x 7.7<br>mm <sup>2</sup>      | 6.3 x 18.5 mm <sup>2</sup>       |

|   | Cell size                            | 3.8 µm <sup>2</sup>             | 30 µm <sup>2</sup>                 | $3.4 \ \mu m^2$                  |

|   | Access time                          | 62 nsec                         | 120 nsec                           | 58 nsec                          |

| ٦ | Erasure time                         | minutes                         | N.A.                               | 4 sec                            |

|   | Programming<br>time/word             | 5 µsec                          | 8 msec/word,<br>4 sec /chip        | 5 µsec                           |

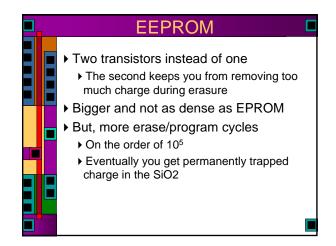

|   | Erase/Write<br>cycles<br>[Pashley89] | 100                             | 105                                | 10 <sup>3</sup> -10 <sup>5</sup> |

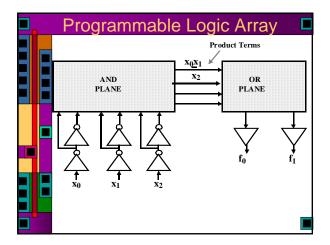

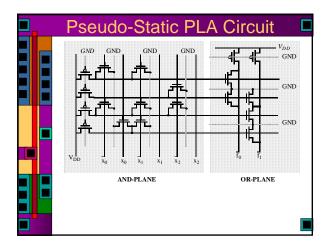

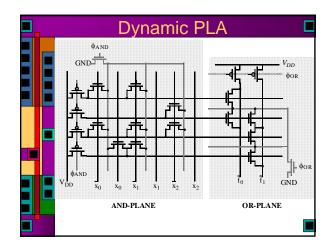

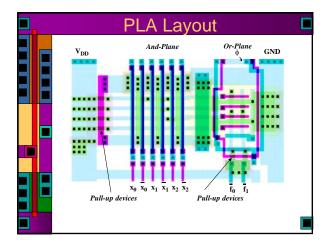

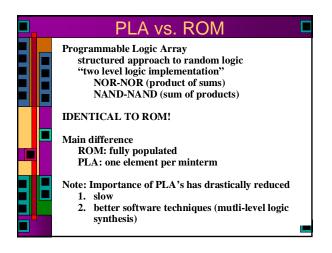

|  | PLA 🗖                                                                                                                                                                    |

|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <ul> <li>Still useful for random combinational logic</li> <li>Standard cell ASIC tools may be replacing them</li> <li>They can generate dense AND-OR circuits</li> </ul> |

## Field Programmable Gate Arrays Array of P-type and N-type transistors Sources and drains connected to Power and ground Metal Map gate structures to sea of gates Less expensive – only modify metal masks