Microprocessors, Lecture 5:

### AVR Microcontrollers -Timers (Chapter 9 of the text book)

## Contents

- Timers 0 and 2 of ATmega32

- Timer programming in C

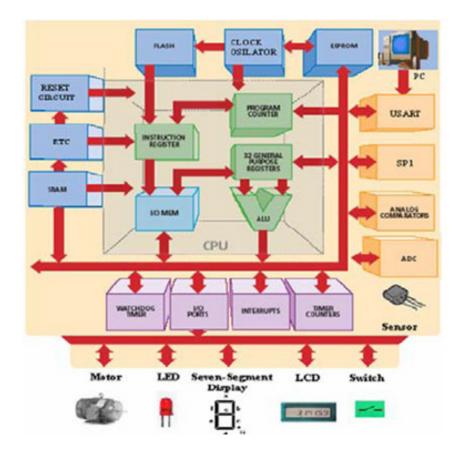

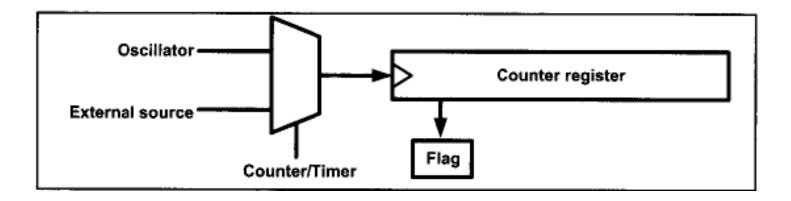

### **Timer/Counter**

- What is a timer?

- To count an event

- To generate delay

- ATmega32: 3 timers

- Timer0 (8-bit)

- -Timer1 (16-bit)

- Timer2 (8-bit)

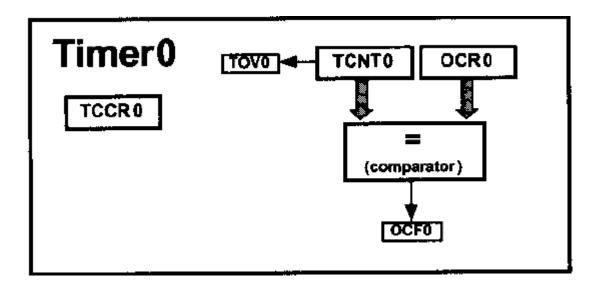

- Basic registers:

- -TCNTx (x=0,1,2)= timer/counter register

- Keeps the timer/counter value

- On reset, contains 0

- Counts up with each pulse

TCNT0

|  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--|----|----|----|----|----|----|----|----|

|--|----|----|----|----|----|----|----|----|

- Basic registers:

- -TOVx(x=0,1,2)= timer/counter overflow flag

- -TOVx Becomes 1 when TCNTx overflows

- » switches from 0xFF to 0x00

- Should be reset by software

- Basic registers:

- -OCRx (x=1,2,3)= output compare register

- Another way to count

- The contents of OCRx are compared to TCNTx

- » OCFx is set if they are equal

- Basic registers:

- -TCCRx (x=1,2,3)= timer/counter control register

- Setting modes of operation

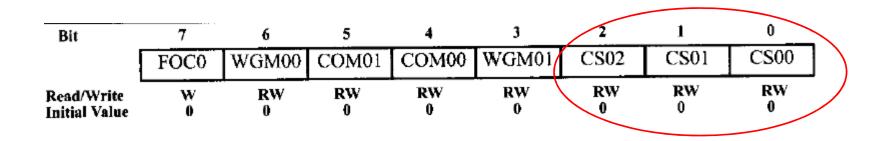

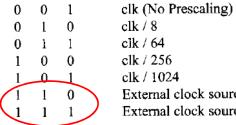

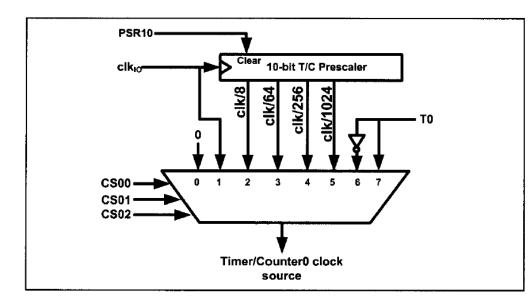

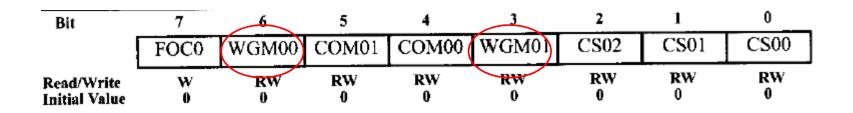

### **TCCR0 in AVR**

| CS02:00 | D2 | D1 | D0 | Timer0 clock selector                                   |

|---------|----|----|----|---------------------------------------------------------|

|         | 0  | 0  | 0  | No clock source (Timer/Counter stopped)                 |

|         | 0  | 0  | 1  | clk (No Prescaling)                                     |

|         | 0  | 1  | 0  | clk / 8                                                 |

|         | 0  | 1  | 1  | clk / 64                                                |

|         | 1  | 0  | 0  | clk / 256                                               |

|         | 1  | 0  | 1  | clk / 1024                                              |

|         | 1  | 1  | 0  | External clock source on T0 pin. Clock on falling edge. |

|         | 1  | 1  | 1  | External clock source on T0 pin. Clock on rising edge.  |

### **TCCR0** in AVR

#### D2 D1 D0 Timer0 clock selector CS02:00

0

No clock source (Timer/Counter stopped) 0 0

External clock source on T0 pin. Clock on falling edge. External clock source on T0 pin. Clock on rising edge.

|                       |             | 40 PIN DIP       |    |             |

|-----------------------|-------------|------------------|----|-------------|

|                       |             | $\neg$ $\square$ | 40 | PA0 (ADC0)  |

| (T1) PB1              |             | $\mathbf{U}$     | 39 | PA1 (ADC1)  |

| (INT2/AIN0) PB2       | <b>–</b> 3  |                  | 38 | PA2 (ADC2)  |

| (OC0/AIN1) PB3        | <b>d</b> 4  | MEGA32           | 37 | PA3 (ADC3)  |

| ( <del>SS</del> ) PB4 | <b>=</b> 5  |                  | 36 | PA4 (ADC4)  |

| (MOSI) PB5            | <b>=</b> 6  |                  | 35 | PA5 (ADC5)  |

| (MISO) PB6            | <b>d</b> 7  |                  | 34 | PA6 (ADC6)  |

| (SCK) PB7             | <b>6</b> 8  |                  | 33 | PA7 (ADC7)  |

| RESET                 | <b>–</b> 9  |                  | 32 | AREF        |

| VCC                   | <b>d</b> 10 |                  | 31 | AGND        |

| GND                   | <b>d</b> 11 |                  | 30 | AVCC        |

| XTAL2                 | <b>d</b> 12 |                  | 29 | PC7 (TOSC2) |

| XTAL1                 | <b>=</b> 13 |                  | 28 | PC6 (TOSC1) |

| (RXD) PD0             | <b>d</b> 14 |                  | 27 | PC5 (TDI)   |

| (TXD) PD1             | <b>H</b> 15 |                  | 26 | PC4 (TDO)   |

| (INT0) PD2            | <b>E</b> 16 |                  | 25 | PC3 (TMS)   |

| (INT1) PD3            | <b>d</b> 17 |                  | 24 | PC2 (TCK)   |

| (OC1B) PD4            | <b>d</b> 18 |                  | 23 | PC1 (SDA)   |

| (OC1A) PD5            | <b>–</b> 19 |                  | 22 | PC0 (SCL)   |

| (ICP) PD6             | <b>d</b> 20 |                  | 21 | PD7 (OC2)   |

### **TCCR0** in AVR

- TIFR (timer/counter interrupt flag register)

- To keep the state of the counters

- One register for all counter/timers

### TIFR

| Bit                         | 7                                 | 6                                                    | 5          | 4          | 3           | 2        | 1        | 0        | 7            |  |  |  |  |  |

|-----------------------------|-----------------------------------|------------------------------------------------------|------------|------------|-------------|----------|----------|----------|--------------|--|--|--|--|--|

|                             | OCF2                              | TOV2                                                 | ICF1       | OCF1A      | OCF1B       | TOVI     | OCF0     | TOV0     |              |  |  |  |  |  |

| Read/Write<br>Initial Value | R/W<br>0                          | R/W<br>0                                             | R/W<br>0   | R/W<br>0   | R/W<br>0    | R/W<br>0 | R/W<br>0 | R/W<br>0 |              |  |  |  |  |  |

| TOV0                        | D0                                | Time                                                 | r0 overfl  | ow flag bi | t           |          |          |          |              |  |  |  |  |  |

|                             | 0 =                               | Timer0 di                                            | id not ov  | erflow.    |             |          |          |          |              |  |  |  |  |  |

|                             | 1 =                               | 1 = Timer0 has overflowed (going from \$FF to \$00). |            |            |             |          |          |          |              |  |  |  |  |  |

| OCF0                        | D1 Timer0 output compare flag bit |                                                      |            |            |             |          |          |          |              |  |  |  |  |  |

|                             | 0 =                               | compare                                              | match die  | ł not occu | I <b>r.</b> |          |          |          |              |  |  |  |  |  |

|                             | 1 =                               | compare :                                            | match oc   | curred.    |             |          |          |          |              |  |  |  |  |  |

| TOV1                        | D2                                | Time                                                 | r1 overfle | ow flag bi | t           |          |          |          |              |  |  |  |  |  |

| OCF1B                       | D3                                | Time                                                 | r1 output  | compare    | B match f   | flag r   | <u></u>  | ···-     |              |  |  |  |  |  |

| OCF1A                       | D4                                | Time                                                 | r1 output  | compare    | A match f   | flag     | Timer0   | TOVO     | TCNT0 OCR0   |  |  |  |  |  |

| ICF1                        | D5                                | Input                                                | Capture    | flag       |             | -        | TCCRO    |          |              |  |  |  |  |  |

| TOV2                        | D6                                | Time                                                 | r2 overflo | ow flag    |             | ļ        |          |          | =            |  |  |  |  |  |

| OCF2                        | D7                                | Time                                                 | r2 output  | compare    | match flag  | g        |          |          | (comparator) |  |  |  |  |  |

|                             |                                   | <b></b>                                              | <u> </u>   |            | •           |          |          |          |              |  |  |  |  |  |

|                             |                                   |                                                      |            |            |             |          |          |          | OCF0         |  |  |  |  |  |

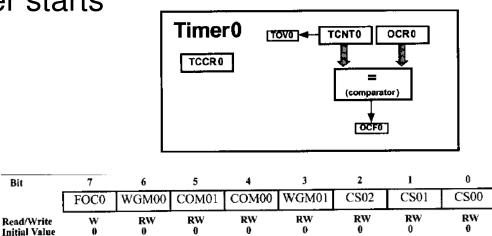

## **Timer0 in normal mode**

Bit

- Set TCNT0 with proper value

- Set TCCR0: which clock source? Which prescalar?

- When is set, the timer starts

- Keep monitoring TOV0

- Stop timer Set TCCR0

- Clear TOV0

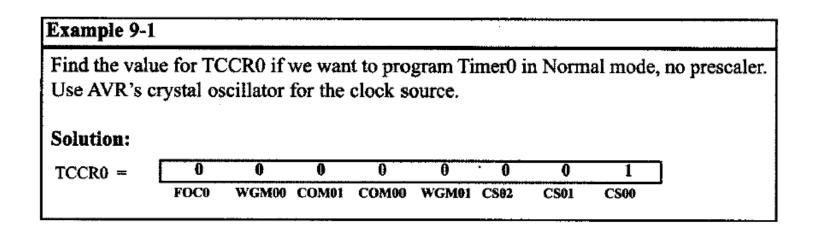

| Example 9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1         |         |       |        |         |        |         |          |          |        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------|--------|---------|--------|---------|----------|----------|--------|--|

| Find the value of the second s |           |         |       |        |         |        | er0 in  | Normal   | mode     | with a |  |

| Solution:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Solution: |         |       |        |         |        |         |          |          |        |  |

| From Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9-5 we    | have TC | CR0 = | 0000 0 | 011; X1 | TAL cl | ock sou | rce, pre | scaler o | of 64. |  |

| TCCR0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0         | 0       | 0     | 0      | 0       | 0      | 1       | 1        |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FOC0      | WGM00   | COM01 | COM00  | WGM01   | CS02   | CS01    | CS00     |          |        |  |

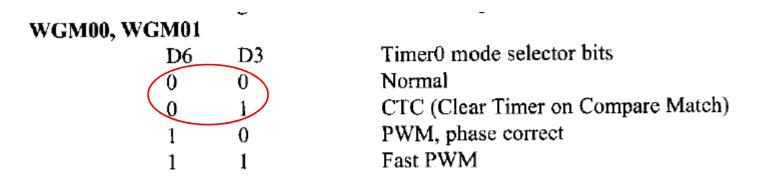

| D2 | D1 | D0 | Timer0 clock selector                             | D6    | D3 | Timer0 mode selector bits          |

|----|----|----|---------------------------------------------------|-------|----|------------------------------------|

| 0  | 0  | 0  | No clock source (Timer/Counter stopped)           |       | 0  | Normal                             |

| 0  | 0  | 1  | clk (No Prescaling)                               | 0     | 0  |                                    |

| ŏ  | ĩ  | Ô  | clk / 8                                           | 0     | 1  | CTC (Clear Timer on Compare Match) |

| 0  | 1  | 1  | •                                                 | 1     | 0  | PWM, phase correct                 |

| 0  | -  | 1  | clk / 64                                          | 1     | 1  | Fast PWM                           |

| 1  | 0  | 0  | clk / 256                                         | -     | -  |                                    |

| 1  | 0  | 1  | clk / 1024                                        |       |    |                                    |

| 1  | 1  | 0  | External clock source on T0 pin. Clock on falling | edge. |    |                                    |

1 1 External clock source on T0 pin. Clock on rising edge.

| D2 | D1 | D0 | Timer0 clock selector                               | D6   | D3 | Timer0 mode selector bits          |

|----|----|----|-----------------------------------------------------|------|----|------------------------------------|

| 0  | 0  | 0  | No clock source (Timer/Counter stopped)             | 0    | 0  | Normal                             |

| 0  | 0  | 1  | clk (No Prescaling)                                 | õ    | 1  | CTC (Clear Timer on Compare Match) |

| 0  | 1  | 0  | clk / 8                                             | 1    | 0  | PWM, phase correct                 |

| 0  | 1  | 1  | clk / 64                                            | 1    | 1  | Fast PWM                           |

| 1  | 0  | 0  | clk / 256                                           | 1    | •  |                                    |

| 1  | 0  | 1  | clk / 1024                                          |      |    |                                    |

| 1  | 1  | 0  | External clock source on T0 pin. Clock on falling e |      |    |                                    |

| 1  | 1  | 1  | External clock source on T0 pin. Clock on rising ed | lge. |    |                                    |

### Example 9-7

Assuming that XTAL = 8 MHz, write a program to generate a square wave with a period of 12.5 µs on pin PORTB.3.

### Solution:

For a square wave with T = 12.5  $\mu$ s we must have a time delay of 6.25  $\mu$ s. Because XTAL = 8 MHz, the counter counts up every 0.125  $\mu$ s. This means that we need 6.25  $\mu$ s / 0.125  $\mu$ s = 50 clocks. 256 - 50 = 206 = 0xCE. Therefore, we have TCNT0 = 0xCE.

TCCR0=0x01 //normal mode, no prescaling TCNT0=0xCE

### Example 9-8

Assuming that XTAL = 8 MHz, modify the program in Example 9-7 to generate a square wave of 16 kHz frequency on pin PORTB.3.

### Solution:

Look at the following steps. (a) T = 1 / F = 1 / 16 kHz = 62.5 µs the period of the square wave. (b) 1/2 of it for the high and low portions of the pulse is 31.25 µs. (c) 31.25 µs / 0.125 µs = 250 and 256 - 250 = 6, which in hex is 0x06. (d) TCNT0 = 0x06.

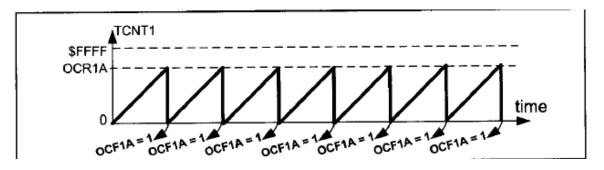

## **Timers in AVR-CTC mode**

- Compare mode (clear timer o compare)

- Another way to count

- 1. Increment TCNT at each clock cycle

- 2. OCFn=1 when OCRn=TCNTn

### Example 9-20

Assuming XTAL = 8 MHz, write a program to generate a delay of 25.6 ms. Use Timer0, CTC mode, with prescaler = 1024.

### Solution:

Due to prescaler = 1024 each timer clock lasts  $1024 \times 0.125 \,\mu s = 128 \,\mu s$ . Thus, in order to generate a delay of 25.6 ms we should wait 25.6 ms / 128  $\mu s = 200$  clocks. Therefore the OCR0 register should be loaded with 200 - 1 = 199.

### **Timer 2 in ATmega32**

- Just like timer 0, but no external clock

Timer only

- TCCR2:

| Bit                         | 7       | 7 |        | 6 5     |            | 4          | 3                | 2          | 1       | 0       |

|-----------------------------|---------|---|--------|---------|------------|------------|------------------|------------|---------|---------|

|                             | FOC     | 2 | WGM20  |         | COM21      | COM20      | OM20 WGM21       |            | CS21    | CS20    |

| Read/Write<br>Initial Value |         |   | R<br>( | :W<br>) | RW<br>0    | RW<br>0    | RW<br>0          | RW<br>0    | RW<br>0 | RW<br>0 |

| CS2                         | CS22:20 |   | D1     | D0<br>0 | Timer2 clo |            | or<br>ce (Timer/ | Counter st | onned)  |         |

|                             | 0       |   | 0      | 1       |            | (No Presca | · ·              | counter st | opped)  |         |

|                             |         | Õ | ĩ      | 0       | clk        | •          | B)               |            |         |         |

|                             |         | 0 | 1      | 1       | clk        | / 32       |                  |            |         |         |

|                             | 1       |   | 0      | 0       | cik        | / 64       |                  |            |         |         |

|                             |         | 1 | 0      | 1       | clk        | / 128      |                  |            |         |         |

|                             |         | 1 | 1      | 0       | clk        | / 256      |                  |            |         |         |

|                             |         | 1 | 1      | 1       | clk        | / 1024     |                  |            |         |         |

# **Timer programming in C**

We can use the register names in C codes:

TCNT0, TCNT1, TCNT2

TIFR0,....

TCCR0,....

— . . . .

# Timer programming in C

#### Example 9-39

Write a C program to toggle all the bits of PORTB continuously with some delay. Use Timer0, Normal mode, and no prescaler options to generate the delay.

#### Solution:

```

#include "avr/io.h"

void TODelay ( );

int main ( )

ł

DDRB = 0xFF; //PORTB output port

while (1)

Ł

PORTB = 0x55; //repeat forever

TODelay (); //delay size unknown

PORTB = 0xAA; //repeat forever

TODelay ();

ł

void TODelay ( )

TCNT0 = 0x20; //load TCNT0

TCCR0 = 0x01; //Timer0, Normal mode, no prescaler

while ((TIFR&0x1)==0); //wait for TF0 to roll over

TCCR0 = 0;

//clear TF0

TIFR = 0x1;

}

```

# Timer programming in C

#### Example 9-40

Write a C program to toggle only the PORTB.4 bit continuously every 70  $\mu$ s. Use Timer0, Normal mode, and 1:8 prescaler to create the delay. Assume XTAL = 8 MHz.

#### Solution:

```

XTAL = 8MHz \rightarrow T_{machine cycle} = 1/8 MHz

Prescaler = 1:8 \rightarrow T<sub>clock</sub> = 8 × 1/8 MHz = 1 µs

70 \,\mu\text{s}/1 \,\mu\text{s} = 70 \,\text{clocks} \Rightarrow 1 + 0 \,\text{xFF} - 70 = 0 \,\text{x}100 - 0 \,\text{x}46 = 0 \,\text{xBA} = 186

#include "avr/io.h"

void TODelay ( );

int main ( )

DDRB = 0xFF; //PORTB output port

while (1)

£

//Timer0, Normal mode

TODelay ( );

PORTB = PORTB ^ 0x10; //toggle PORTB.4

}

void TODelay ( )

{

TCNT0 = 186;

//load TCNT0

TCCR0 = 0x02;

//Timer0, Normal mode, 1:8 prescaler

while ((TIFR&(1<<TOV0))==0); //wait for TOV0 to roll over

//turn off Timer0

TCCR0 = 0;

TIFR = 0x1; //clear TOV0

```

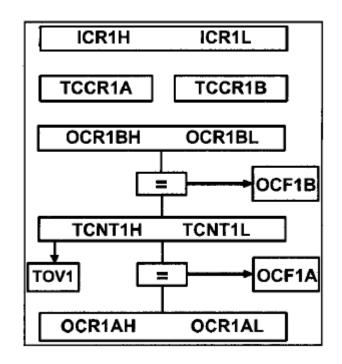

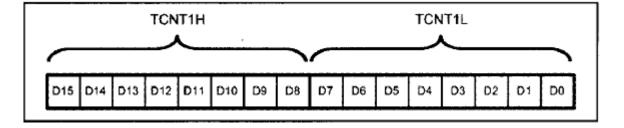

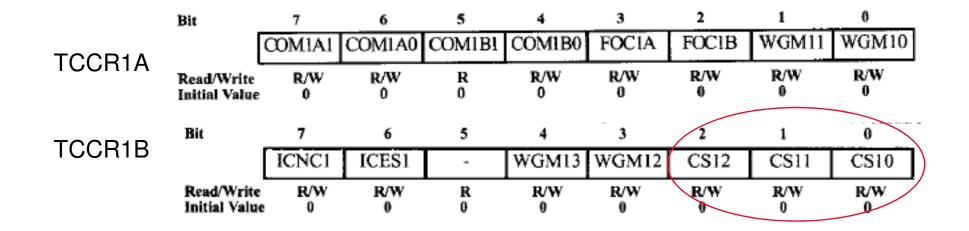

# Timer 1

- 16-bit counter/timer

- TCNT1L and TCNT1H

- 2 8-bit registers to control timer 1

-TCCR1L and TCCR1H

2 registers in compare mode

-OCR1A and OCR1B

# Timer 1

### TCNT1

|                     | Bit                         | 7        | 6                     | 5                        | 4                                | 3          | 2          | 1        | 0        |

|---------------------|-----------------------------|----------|-----------------------|--------------------------|----------------------------------|------------|------------|----------|----------|

|                     | [                           | OCF2     | TOV2                  | ICF1                     | OCF1A                            | OCF1B      | TOV1       | OCF0     | TOV0     |

|                     | Read/Write<br>Initial Value | R/W<br>0 | R/W<br>0              | R/W<br>0                 | R/W<br>0                         | R/W<br>0   | R/W<br>0   | R/W<br>0 | R/W<br>0 |

| 3 flags in<br>TIFR: | TOV0                        | -        | Timer0 di<br>Timer0 h | id not ove<br>as overflo | owed (goin                       | ng from \$ | FF to \$00 | )).      |          |

| TOV1                | OCF0                        |          |                       | match die                | compare<br>d not occu<br>curred. | -          |            |          |          |

| and                 | TOV1<br>OCF1B               | D2<br>D3 | Time                  | r1 output                | •                                | B match f  | -          |          |          |

| OCF1A-              | OCF1A<br>ICF1               | D4<br>D5 | Input                 | Capture                  | flag                             | A match f  | lag        |          |          |

| OCF1B               | TOV2<br>OCF2                | D6<br>D7 |                       | r2 overflo<br>r2 output  |                                  | match fla  | g          |          |          |

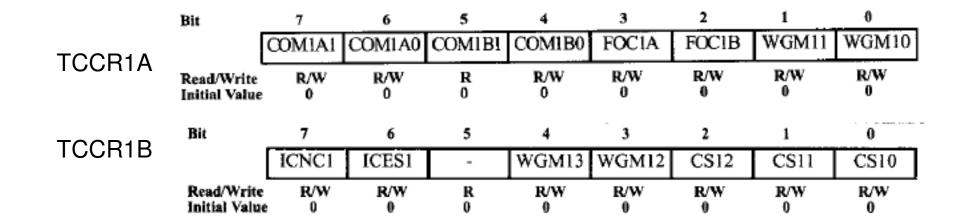

### **Timer 1 control registers**

- 2 registers

- Plenty of operation modes

### **Timer 1 control registers**

In this course, we focus on modes 0 and 4

|     | Mode | WGM13      | WGM12 | WGM11 | WGM10           | Timer/                           | Counter Mod   | le of Operatio | n Top      | Update of<br>OCR1x | TOV1 Flag<br>Set on |

|-----|------|------------|-------|-------|-----------------|----------------------------------|---------------|----------------|------------|--------------------|---------------------|

|     | 0    | 0          | 0     | 0     | 0               | Norma                            | I             |                | 0xFFFF     | Immediate          |                     |

|     | 1    | 0          | 0     | 0     | . 1             | PWM,                             | Phase Correct | t, 8-bit       | 0x00FF     | TOP                | BOTTOM              |

|     | 2    | 0          | 0     | 1     | 0               | PWM,                             | Phase Correct | t, 9-bit       | 0x01FF     | ТОР                | BOTTOM              |

| e   | 3    | 0          | 0     | 1     | 1               | PWM,                             | Phase Correc  | t, 10-bit      | 0x03FF     | TOP                | BOTTOM              |

| C I | 4    | 0          | 1     | 0     | 0               | CTC                              |               |                | OCR1A      | Immediate          | MAX                 |

|     | 5    | 0          | 1     | 0     | 1               | Fast PV                          | VM, 8-bit     |                | 0x00FF     | TOP                | TOP                 |

|     | 6    | 0          | 1     | 1     | 0               | Fast PV                          | VM, 9-bit     |                | 0x01FF     | TOP                | TOP                 |

| [   | 7    | 0          | 1     | 1     | 1               | Fast PV                          | VM, 10-bit    |                | 0x03FF     | TOP                | TOP                 |

|     | 8    | 1          | 0     | 0     | 0               | PWM, Phase and Frequency Correct |               |                | t ICR1     | BOTTOM             | BOTTOM              |

|     | 9    | 1          | 0     | 0     | 1               | PWM,                             | Phase and Fre | equency Correc | tOCR1A     | BOTTOM             | BOTTOM              |

|     | 10   | 1          | 0     | 1     | 0               | PWM,                             | Phase Correc  | t              | ICR1       | TOP                | BOTTOM              |

| [   | 11   | 1          | 0     | 1     | 1               | PWM,                             | Phase Correc  | t              | OCRIA      | TOP                | BOTTOM              |

|     | 12   | 1          | 1     | 0     | 0               | СТС                              |               |                | ICR1       | Immediate          | MAX                 |

|     | 13   | 1          | 1     | 0     | 1               | Reserve                          | ed            |                | -          | -                  | -                   |

|     | 14   | 1          | 1     | 1     | 0               | Fast PV                          | VМ            |                | ICRI       | TOP                | TOP                 |

| [   | 15   | 1          | 1     | 1     | 1               | Fast PV                          | VM            |                | OCR1A      | TOP                | TOP                 |

|     |      |            |       |       |                 | _                                |               |                |            |                    | 0                   |

|     | H    | Bit        |       |       | 6<br>11 A 0 C C | 5<br>MIBI                        | 4<br>COM1B0   | 3<br>FOCIA     | 2<br>FOC1B | WGM11              | WGM10               |

| CR1 | A    | Read/Write | L     |       | w               | R                                | R/W           | R/W            | R/W        | R/W                | R/W                 |

TC 0 õ 0 0 Ð 0 Initial Value 0 Bit 7 6 5 2 1 0 3 ICNC1 ICES1 WGM13 WGM12 CS12 CS11 CS10 -TCCR1B R/W R 0 R/W R/W 0 **Read/Write** R/W R/W R/W R/W **Initial Value** 0 0 0

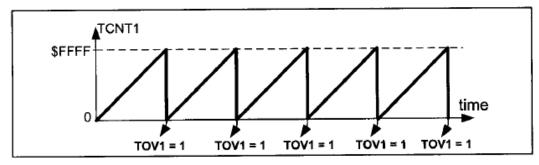

### **Timer 1 modes**

- 16 modes, we use 2 modes in this chapter:

- Normal mode:

• CTC mode

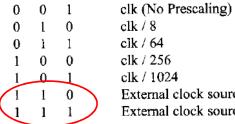

### **Timer 1 control registers**

| CS12:CS10 | D2D1D0 | Timer1 clock selector                                   |

|-----------|--------|---------------------------------------------------------|

|           | 0 0 0  | No clock source (Timer/Counter stopped)                 |

|           | 0 0 1  | clk (no prescaling)                                     |

|           | 0 1 0  | clk / 8                                                 |

|           | 0 1 1  | clk / 64                                                |

|           | 100    | clk / 256                                               |

|           | 1 0 1  | clk / 1024                                              |

|           | 1 1 0  | External clock source on T1 pin. Clock on falling edge. |

|           | 1 1 1  | External clock source on T1 pin. Clock on rising edge.  |

### **Timer 1 control registers**

|        | Mode              | WGM1       | 3 WGM12  | WGM11    | WGM10    | Timer/Count | er Mode of Oper | ration Top         | Update of TO<br>OCR1x S | V1 Flag<br>iet on |          |

|--------|-------------------|------------|----------|----------|----------|-------------|-----------------|--------------------|-------------------------|-------------------|----------|

| CS     | 12:CSI            | 0          | D2D1I    | 50       | Tim      | erl clock   | selector        |                    | 1 1                     | 1                 |          |

|        |                   |            | 0 0      | 0        | No       | clock sou   | rce (Timer/     | Counter            | stopped)                |                   |          |

|        |                   |            | 0 0      | 1        |          | (no presca  | -               |                    |                         |                   |          |

|        |                   |            | 0 1      | 0        | clk      |             |                 |                    |                         |                   |          |

|        |                   |            | 0 1      | 1        | clk      |             |                 |                    |                         |                   |          |

|        |                   |            | 1 0      | 0        |          | / 256       |                 |                    |                         |                   |          |

|        |                   |            | 1 0      | 1        |          | / 1024      |                 |                    |                         |                   |          |

|        |                   |            | 1 1      | 0        |          |             | k source or     | 1 T1 nin           | Clock on                | falling edge      |          |

|        |                   |            | 1 1      | 1 .      |          |             |                 | -                  |                         | rising edge.      |          |

|        | 11                | <b>I</b> 1 | 1 0      | 1<br>  1 |          | PWM, Phase  |                 | I I I pm.<br>OCRIA |                         | TTOM              |          |

|        | 12                | i          | 1        | 0        | 0        | СТС         | -               | ICR1               |                         | XAN               |          |

|        | 13                | 1          | 1        | 0        | 1        | Reserved    |                 | -                  | -                       | -                 |          |

|        | 14                | 1          | 1        | 1        | 0        | Fast PWM    |                 | ICRI               |                         | TOP               |          |

|        | 15                | 1          | 1        | 1        | 1        | Fast PWM    |                 | OCR1A              | ТОР                     | TOP               |          |

|        |                   |            |          |          |          |             |                 |                    |                         |                   |          |

|        | Bit               | _          | 7        |          | 6        | 5           | 4               | 3                  | 2                       | 1                 | 0        |

|        |                   | C          | ЮM1A     | 1 CON    | /11A0    | COMIBI      | COM1B0          | FOCIA              | FOCIB                   | WGM11             | WGM10    |

| TCCR1A | Read/W            |            | R/W      |          | /W       | R           | R/W             | R/W                | R/W                     | R/W               | R/W      |

|        | Initial V         | alue       | 0        |          | 0        | 0           | 0               | 0                  | 0                       | 0                 | 0        |

|        | Bit               |            | 7        |          | 6        | 5           | 4               | 3                  | 2                       | 1                 | 0        |

| TCCR1B |                   | [          | ICNC     | 1 IC     | ES1      | -           | WGM13           | WGM12              | 2 CS12                  | CS11              | CS10     |

|        | Read/\<br>Initial |            | R/W<br>0 | / I      | ₹/₩<br>0 | R<br>0      | R/W<br>Ø        | R/W<br>0           | R/W<br>0                | R/W<br>0          | R/W<br>0 |

University of Tehran 32

An LED is connected to PC4. Assuming XTAL = 8 MHz, write a program that toggles the LED once per second.

#### Solution:

As XTAL = 8 MHz, the different outputs of the prescaler are as follows:

| Scaler No. 1 | Timer Clock             | Timer Period                             | Timer Value                                |

|--------------|-------------------------|------------------------------------------|--------------------------------------------|

| None         | 8 MHz                   | 1/8 MHz = 0.125 μs                       | 1 s/0.125 μs = 8 M                         |

| 8            | 8  MHz/8 = 1  MHz       | $1/1 \text{ MHz} = 1 \mu \text{s}$       | $1 \text{ s/1} \mu \text{s} = 1 \text{ M}$ |

| 64           | 8 MHz/64 = 125 kHz      | $1/125 \text{ kHz} = 8 \mu \text{s}$     | 1 s/8 μs = 125,000                         |

| 256          | 8 MHz/256 = 31.25 kHz   | $1/31.25 \text{ kHz} = 32 \mu \text{s}$  | $1 \text{ s/32 } \mu \text{s} = 31,250$    |

| 1024         | 8 MHz/1024 = 7.8125 kHz | $1/7.8125 \text{ kHz} = 128 \mu\text{s}$ | 1 s/128 µs = 7812.5                        |

From the above calculation we can use only options 256 or 1024. We should use option 256 since we cannot use a decimal point.

Write a C program to toggle only the PORTB.4 bit continuously every 2 ms. Use Timer1, Normal mode, and no prescaler to create the delay. Assume XTAL = 8 MHz.

#### Solution:

XTAL = 8 MHz  $\Rightarrow$  T<sub>machine cycle</sub> = 1/8 MHz = 0.125 µs Prescaler = 1:1  $\Rightarrow$  T<sub>clock</sub>= 0.125 µs 2 ms/0.125 µs = 16,000 clocks = 0x3E80 clocks

1 + 0xFFFF - 0x3E80 = 0xC180

```

#include "avr/io.h"

void T1Delay ( );

int main ( )

Ł

DDRB = 0xFF; //PORTB output port

while (1)

ł

PORTB = PORTB ^ (1<<PB4); //toggle PB4

T1Delay ( );

//delay size unknown

ł

}

void TlDelay ( )

{

//TEMP = 0xC1

TCNT1H = 0xC1;

TCNT1L = 0x80;

//Normal mode

TCCR1A = 0x00;

TCCR1B = 0x01; //Normal mode, no prescaler

while ((TIFR&(0x1 ))==0); //wait for TOV1 to roll over

TCCR1B = 0;

TIFR = 0x1 ; //clear TOV1

}

```

Write a C program to toggle only the PORTB.4 bit continuously every second. Use Timer1, Normal mode, and 1:256 prescaler to create the delay. Assume XTAL = 8 MHz.

#### Solution:

XTAL = 8 MHz  $\Rightarrow$  T<sub>machine cycle</sub> = 1/8 MHz = 0.125 µs = T<sub>clock</sub> Prescaler = 1:256  $\Rightarrow$  T<sub>clock</sub> = 256 × 0.125 µs = 32 µs 1 s/32 µs = 31,250 clocks = 0x7A12 clocks  $\Rightarrow$  1 + 0xFFFF - 0x7A12 = 0x85EE

# Accessing 16-bit registers in AVR

- TCNT1=0x05ff, we want to save the content of TCNT1 in R20 and R21

- Cannot read TCNT in one cycle

- AVR is a 8-bit machine

| IN | R20,TCNT1L  | ;R20 = | TCNT1L, | TEMP = TCNT1H |

|----|-------------|--------|---------|---------------|

| IN | R21, TCNT1H | ;R21 = | TEMP of | Timer1        |

- Read TCNT1L (0xff) at t0, at the same cycle occurs TCNT=0x0600

- Read TCNT1H (0x06)

- The content is detected as 0x06ff instead of the correct value 0x05ff

# Accessing 16-bit registers in AVR

- Solution:

- AVR buffers the high byte when the lower byte is read

- When the higher byte is read, the buffered value is used

- → first read the lowest byte and then the higher byte

| IN | R20,TCNT1L | ;R20 =  | TCNT1L, | TEMP = TCNT1H |

|----|------------|---------|---------|---------------|

| TN | DOI TONTIU | • P21 = | TEMP of | Timer1        |

IN R21, TONTIH ;R21 = TEMP OF TIMETI

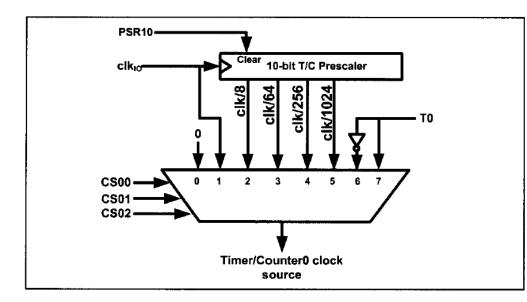

### **Counters in AVR**

To count external events

### **Counter programming in AVR**

#### CS02:00

0

D2 D1 D0 Timer0 clock selector

No clock source (Timer/Counter stopped) 0 0

External clock source on T0 pin. Clock on falling edge. External clock source on T0 pin. Clock on rising edge.

| -                 |             | 40 PIN DIP       |    |             |

|-------------------|-------------|------------------|----|-------------|

|                   |             | $\neg$ $\square$ | 40 | PA0 (ADC0)  |

| (T1) PB1          | <b>–</b> 2  | Ŭ                | 39 | PA1 (ADC1)  |

| (INT2/AIN0) PB2   | <b>–</b> 3  |                  | 38 | PA2 (ADC2)  |

| (OC0/AIN1) PB3    | <b>4</b>    | MEGA32           | 37 | PA3 (ADC3)  |

| ( <u>SS</u> ) PB4 | <b>=</b> 5  |                  | 36 | PA4 (ADC4)  |

| (MOSI) PB5        | <b>⊏</b> 6  |                  | 35 | PA5 (ADC5)  |

| (MISO) PB6        | <b>d</b> 7  |                  | 34 | PA6 (ADC6)  |

| (SCK) PB7         | <b>=</b> 8  |                  | 33 | PA7 (ADC7)  |

| RESET             | <b>–</b> 9  |                  | 32 | AREF        |

| VCC               | <b>H</b> 10 |                  | 31 | AGND        |

| GND               | <b>d</b> 11 |                  | 30 | AVCC        |

| XTAL2             | <b>–</b> 12 |                  | 29 | PC7 (TOSC2) |

| XTAL1             | <b>–</b> 13 |                  | 28 | PC6 (TOSC1) |

| (RXD) PD0         | <b>H</b> 14 |                  | 27 | PC5 (TDI)   |

| (TXD) PD1         | <b>H</b> 15 |                  | 26 | PC4 (TDO)   |

| (INT0) PD2        | <b>–</b> 16 |                  | 25 | PC3 (TMS)   |

| (INT1) PD3        | <b>d</b> 17 |                  | 24 | PC2 (TCK)   |

| (OC1B) PD4        | <b>–</b> 18 |                  | 23 | PC1 (SDA)   |

| (OC1A) PD5        | <b>–</b> 19 |                  | 22 | PC0 (SCL)   |

| (ICP) PD6         | <b>=</b> 20 |                  | 21 | PD7 (OC2)   |

### **Counter programming in AVR**

- Configure T0 (PB0) or T1 (PB1) as input

- Set the other registers as in timers

### Counter

Assuming that a 1 Hz clock pulse is fed into pin T0, use the TOV0 flag to extend Timer0 to a 16-bit counter and display the counter on PORTC and PORTD.

#### Solution:

```

#include "avr/io.h"

ATmega32

int main ( )

ł

PD

//activate pull-up of PB0

to

PORTB = 0x01;

LEDs

//PORTC as output

DDRC = 0xFF;

PC

DDRD = 0 \times FF;

//PORTD as output

PB0

то

1 \text{ Hz}

//output clock source

TCCR0 = 0x06;

TCNTO = 0x00;

while (1)

ł

do

ł

PORTC = TCNT0;

) while((TIFR&(0x1<<TOV0))==0);//wait for TOV0 to roll over

//clear TOV0

TIFR = 0 \times 1 << TOV0;

//increment PORTD

PORTD ++;

}

}

```