# Mixing Reliability Prediction Models Maximizes Accuracy

# **Overcome Component Limitations, Better Reflect Past Experiences, and Achieve Superior Predictions**

Although many models are available for performing reliability prediction analyses, each of these models was originally created with a particular application in mind. This document describes the most widely used reliability prediction models in terms of their intended applications, noting both their advantages and disadvantages. It then explains how mixing models in your reliability analyses yields more accurate predictions.

## Widely Used Reliability Prediction Models

In any system, you have a mixture of electronic and mechanical parts. The selection of a reliability prediction model is driven by the critical parts in the system to be modeled and your system requirements. The following table lists the most widely used reliability prediction models and their intended applications, originating country, advantages, and disadvantages.

| Reliability<br>Prediction Model                                                                                                                                                        | Application &<br>Originating<br>Country      | Advantages                                                                                                                                                                                                                                                                                                                                                                                                                     | Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>MIL-HDBK-217</b><br>The Military Handbook for<br>the Reliability Prediction of<br>Electronic Equipment                                                                              | Military and<br>Commercial, United<br>States | <ul> <li>Provides for both Parts<br/>Stress and Parts Count<br/>analysis of electronic parts.</li> <li>Can easily move from<br/>preliminary design stage to<br/>complete design stage by<br/>progressing from Parts<br/>Count to Parts Stress.</li> <li>Includes models for a broad<br/>range of part types.</li> <li>Provides many choices for<br/>environment types.</li> <li>Well-known and widely<br/>accepted.</li> </ul> | Is based on pessimistic failure<br>rate assumptions.<br>Does not consider other<br>factors that can contribute to<br>failure rate such as burn-in<br>data, lab testing data, field test<br>data, designer experience,<br>wear-out, etc.<br><b>NOTE:</b> The Relex Reliability<br>Prediction module overcomes<br>these limitations by allowing<br>you to use Telcordia<br>calculation methods and<br>PRISM process grades with<br>MIL-HDBK-217. |

| <b>Telcordia (Bellcore)</b><br>Reliability Prediction<br>Procedure for Electronic<br>Equipment (Technical<br>Reference # TR-332 or<br>Telcordia Technologies<br>Special Report SR-332) | Commercial, United<br>States                 | Offers analysis ranging from<br>Parts Count to full Parts<br>Stress through the use of<br>Calculation Methods.<br>Considers burn-in data, lab<br>testing data, and field test<br>data.<br>Well-known and accepted.                                                                                                                                                                                                             | Considers only electronic<br>parts.<br>Supports only a limited<br>number of Ground<br>Environments.<br>Fewer part models compared<br>to MIL-HDBK-217.<br>Does not account for other<br>factors such as designer<br>experience, wear-out, etc.<br><b>NOTE:</b> The Relex Reliability<br>Prediction module overcomes<br>these limitations by allowing<br>you to use PRISM process<br>grades with Telcordia.                                      |

| Mechanical<br>The Handbook of Reliability<br>Prediction Procedures for<br>Mechanical Equipment<br>(NSWC-98/LE1)        | Military and<br>Commercial, United<br>States | Provides for analyzing a<br>broad range of mechanical<br>parts (seals, springs,<br>solenoids, bearings, gears,<br>etc.)                                                                          | Limited to mechanical parts.                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CNET 93</b><br>Recueil de Donnes de<br>Fiabilite des Composants<br>Electroniques RDF 93<br>(UTE C 80-819)           | Telecommunications,<br>France                | Fairly broad range of part<br>types modeled.<br>Provides unique handling of<br>PCBs.                                                                                                             | Considers only electronic parts.<br>Only available in French.                                                                                                                                       |

| RDF 2000<br>Recueil de Donnes de<br>Fiabilite RDF 2000 (UTE C<br>80-810)                                               | Telecommunications,<br>France                | Introduces a new approach<br>to failure rate modeling.<br>Considers cycling profiles<br>and their applicable phases<br>when determining failure<br>rate.<br>Provides unique handling of<br>PCBs. | Considers only electronic<br>parts.<br>Cannot be mixed with other<br>models because of the unique<br>way in which failure rates are<br>calculated.<br>Very new, still gaining<br>acceptance.        |

| HRD5<br>The Handbook for<br>Reliability Data for<br>Electronic Components<br>used in Telecommunication<br>Systems      | Telecommunications,<br>United Kingdom        | Similar to Telcordia.<br>Fairly broad range of part<br>types modeled.                                                                                                                            | Considers only electronic parts.<br>Not widely used.                                                                                                                                                |

| <b>299B</b><br>Chinese Military Standard<br>GJB/z 299B                                                                 | Military, China                              | Provides for both parts<br>stress and parts count<br>analysis.                                                                                                                                   | Considers only electronic<br>parts.<br>Currently used primarily in<br>China.<br>Based on an older version of<br>MIL-HDBK-217.<br>Cannot model hybrids.                                              |

| <b>PRISM</b><br>System Reliability<br>Assessment Methodology<br>developed by the Reliability<br>Analysis Center (RAC)  | Military and<br>Commercial, United<br>States | Incorporates NPRD/EPRD<br>database of failure rates.<br>Enables the use of process<br>grading factors,<br>predecessor data, and test<br>or field data.                                           | Small, limited set of part types<br>modeled.<br>Newer standard, still gaining<br>acceptance.<br>Considers only electronic<br>parts.<br>Cannot model hybrids.<br>No reference standard<br>available. |

| NPRD/EPRD<br>Nonelectronics Parts<br>Reliability (NPRD) and<br>Electronic Parts Reliability<br>(EPRD) databases by RAC | Military and<br>Commercial, United<br>States | Broad array of electronic<br>and non-electronic parts.<br>Based completely on field<br>data.                                                                                                     | Consists entirely of databases<br>of failure rates, not<br>mathematical models.                                                                                                                     |

# **Mixing Models to Overcome Component Limitations**

Each reliability prediction model has its own set of advantages and disadvantages. By mixing the models used in your reliability analyses, you can greatly improve the accuracy of your predictions. For example, even very simple systems often have both electronic and mechanical components. To accurately predict the failure rates of both electronic and mechanical components, you would select a reliability model for electronic components, such as MIL-HDBK-217 or Telcordia, and also refer to *The Handbook of Reliability Prediction Procedures for Mechanical Equipment* from NSWC. By using both electronic and mechanical components and mechanical components models in your reliability analyses, you would obviously obtain more accurate predictions for the system and its components than by using either model alone.

The need to mix reliability prediction models for the electronic components in a system stems from limitations on the component types that these models support. For instance, suppose you select Telcordia as the basis for analyzing the reliability of your electronic components; then, during your analysis, you realize that Telcordia does not support some of the switches and relays used in your system. By adding MIL-HDBK-217 to your modeling mix, you would gain comprehensive coverage for switches, relays, and several other components not supported by Telcordia.

Similarly, if you selected PRISM as the basis for your analysis, coverage for switching devices, connectors, rotary devices, and inductors would be missing. To accurately assess system MTBF (Mean Time Between Failure) for systems with these components, you would have to add reliability models that covered these components to your modeling mix. Having multiple models available for your reliability analyses makes it much more likely that the failure rates predicted for the system and its component are accurate.

## **Mixing Models to Better Reflect Past Experiences**

In addition to mixing reliability prediction models because of part type limitations, you may want to mix models because certain ones more accurately predict the failure rates your system components have experienced in the past. For example, perhaps the failure rates calculated by PRISM best reflect those for the integrated circuits in your system, and the failure rates calculated by Telcordia best reflect those for the resistors in your system. In such cases, you would want to be able to choose the model that calculates the failure rates closest to those experienced in the past for each type of system component. The ability to choose completely different models for various components in the same system empowers you to generate the most accurate predictions possible.

## **Mixing Techniques for Superior Predictions**

**NOTE:** The following paragraphs describe features that are applicable only to specific reliability prediction models. However, none of these limitations apply to the Relex Reliability Prediction module. Providing that you have licensed a model described in this document, the Relex Reliability Prediction module supports the use of that model's features with all other licensed models.

Although PRISM has models for calculating the failure rates of only a limited number of components, it provides many techniques for enhancing reliability predictions. For example, you can use PRISM process grades, which explicitly account for factors contributing to system reliability by grading the process for each system failure cause. If you think the reliability of a component is affected by process-related variability during the design and manufacturing process, you can use process grades to adjust the failure rates calculated for those components.

PRISM also provides summary data from RAC's Nonelectronics Parts Reliability (NPRD) and Electronic Parts Reliability (EPRD) databases for estimating failure rates of components that do not have models. If some of your components are operating within a specific set of environmental conditions and quality levels, you can retrieve the actual life-based failure rate values for components in very similar operating conditions from the NPRD and EPRD databases and then use these values in conjunction with reliability prediction models.

PRISM also allows you to include empirical data on a predecessor system and test data or field data to update the predicted reliability values. Similarly, Telcordia offers Calculation Methods to take advantage of burn-in-data, lab testing data, or field test data that has been collected. If you have such data for certain components, you will want to take advantage of it in the modeling of these components.

In most cases, you would need to use PRISM to factor in process grades, empirical data on a predecessor system, and test data or field data to update predicted reliability values. Likewise, you would need to use Telcordia to have its Calculation Methods factor in burn-in, lab testing, and field test data. However, if you use the Relex Reliability Prediction module to perform your reliability analyses, such limitations do not exist. The Relex Reliability Prediction module extends the advantages and features unique to individual models to all models. Therefore, you can apply the process grade factors defined in PRISM to any licensed model to adjust the failure rates according to design and manufacturing factors. Or, the Calculation Methods defined in Telcordia for adjusting failure rates based on burn-in, lab testing, and field test data can be applied to any other licensed models.

In conclusion, having many reliability prediction models available for your use will help to accurately assess your system MTBF. You can select the model best suited to your specific system parameters and your individual needs.

Relex Reliability Prediction supports all of the models mentioned in this brief. If you would like additional information about how the Relex Reliability Prediction module provides for mixing models and techniques for superior results, please email info@relexsoftware.com.

# Why FRACAS Means Superior Quality and Reliability

# **Closing the Loop to Improve Your Products and Processes**

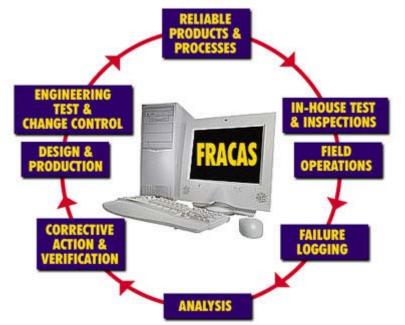

In reliability engineering, **FRACAS** is an acronym for Failure Reporting, Analysis, and Corrective Action System. FRACAS is the term used to designate a process by which companies track product defects and effectively respond and make corrections to fix problems. Product defects may be tracked during product design, testing, manufacturing, and field deployment. A comprehensive FRACAS allows you to efficiently track issues and ensure that reliability problems are addressed in a timely and successful manner. The FRACAS process is used throughout all types of industries. Successful FRACAS programs provide for:

- Easy and timely collection of accurate failure and maintenance data from the lab, field, and supply chain in standardized and compatible data structures.

- Total elimination of complicated and redundant paper-based data records throughout the failure collection process, thereby avoiding dual reporting.

- Effective data analysis to determine root cause mechanisms and real-time failure trends for fast and accurate decisionmaking.

- Accurate historical reliability performance measures, such as mean time between failures (MTBF), mean time to failure (MTTF), mean time to repair (MTTR), and availability for use in determining appropriate corrective actions.

- Customizable reports that facilitate and support corrective action decisions by both management and engineering personnel regarding the improvement of designs, manufacturing processes, and field support systems.

- Optimized workflow management for timely dissemination, information accessibility, and rapid feedback and approval cycles to fully support Collaborative Engineering, Six Sigma, and ISO initiatives.

- Continued monitoring and testing to ensure that implemented corrective actions either prevent failure recurrence or simplify or reduce maintenance tasks.

- Support of legacy systems and contribution to a common database for reliability, maintainability, and system component and part information.

- Automatic conveyance of all failure data and subsequent analysis results to product and system designers to drive design innovation.

## **Closed-Loop System**

To provide such features to the various workgroup and enterprise levels that need them, a FRACAS must be an aggressive closed-loop system that is configurable, flexible, and scaleable! This means that all reported failures and faults must be entered in the FRACAS in an appropriate and controlled manner so that they can then be analyzed and corrective actions identified, implemented, and verified. The knowledge gained from this process must then be fed back into the design, manufacturing, and test process so that quality and reliability are improved. A simplified version of the closed-loop feedback path for a FRACAS follows.

A FRACAS formally captures predetermined types of data about a failure in an Incident Failure Report (IFR). Completed IFRs are submitted to analysts so that they can identify the corrective actions that are to be implemented to prevent these failures from recurring. Whenever corrective actions are implemented and verified or are otherwise determined to be unnecessary, the

IFR is closed. To reduce the possibility of an unmanageable backlog of open IFRs, management periodically reviews all unresolved IFRs to ensure their assignment and eventual closure.

A FRACAS can be used throughout the life cycle of any hardware or software product or system process to track failures, incidents, issues, and even enhancements or suggestions. By implementing a FRACAS during the initial design phase, significant cost savings can be realized from early problem correction, when even major design changes can still be considered to eliminate or reduce susceptibility to known failure causes. Additional benefits of implementing corrective actions while performing in-house tests and inspections are the many opportunities that exist for determining if these corrective actions adequately solve the reported issues.

If a FRACAS is not in place before product inspection or testing begins, problems often go totally unrecorded or insufficient data is captured. If a FRACAS is not in place before the product or process in put into production, it is unlikely that failure and maintenance data will be collected in a structured and timely manner. Consequently, determining and implementing effective corrective actions that either prevent failures from recurring or simplify maintenance tasks will become very difficult.

#### **Failure Logging**

All problems that occur during inspections, tests, and field use must be entered in the FRACAS using an established procedure for recording accurate failure information. Personnel who enter IFRs in the FRACAS should be properly trained to precisely capture the required data. To make entering data in IFRs easy, the entry forms for capturing failure information should be tailored to your hardware, software, or process. Once an IFR is created, the FRACAS should alert the responsible analyst to its existence and indicate the next required action.

#### **Failure Analysis**

An analyst examines the information entered in an IFR to determine the root cause of the failure and identify contributing factors. Methods for analyzing the root cause range from simple investigations of circumstances surrounding a failure to sophisticated laboratory analyses of failed parts. Once the analyst has established the root cause and contributing factors, he or she must develop logically derived corrective actions. As the number of IFRs in the FRACAS grows, the analyst can call upon the historic data for related or similar failures for help in resolving what the appropriate corrective actions for a failure should be. Once corrective actions are noted, the FRACAS should alert the technician who must perform them.

#### **Corrective Action and Verification**

When a technician is implementing corrective actions, he or she may be required to submit time or utilization logs containing operational hours and other time-related data needed to calculate MTBF. The technician may also be required to submit field service logs indicating maintenance times, actions, and part replacements. Visual monitoring or testing must then be performed to indicate that the corrective actions taken have either eliminated the failure or reduced its occurrence. Although verification is sometimes performed by the same or another technician, close out of the IFR is generally performed only by a manager.

#### **Workflow Management**

To be effective in meeting internal and external commitments, a FRACAS must provide for effectively managing the resources and strategies necessary to address open IFRs. Workflow management features within your FRACAS should facilitate the failure analysis process. Managers should be able to assign priorities to failures based on urgency, budgets, and the availability of personnel. To ensure that all IFRs are closed in a timely manner, managers should be able to track IFRs by priority levels, workflow resolution activities, resource assignments, and many other criteria. Management should also strive to improve quality and reliability by participating in the development, implementation, and verification of corrective actions and periodically reviewing failure trends.

#### **Closing the Loop**

A FRACAS builds upon and leverages all of the data entered in its centralized database to ensure early and sustained achievement of improved reliability and maintainability for your product or process. The structured procedure for entering, analyzing, and resolving IFRs produces valuable data about the reliability of your product or process and the efficiency of your organization to address issues. Analyzing and reporting on the IFRs in your FRACAS is vital to the efficiency and profitability of your organization. In addition to complete failure summary reports listing events and problems for specified time periods, your FRACAS should be able to generate root cause analyses (RCAs), problem analysis reports (PARs), material disposition reports (MDRs), product performance reports (which provide MTBF, MTTF, MTTR, availability, etc.), and failure trend charts. Feeding this critical information back into your design, manufacturing, and testing process provides the closed loop that promotes continuously improving quality and reliability throughout the life cycle of your product or process.

If you would like additional information about how the Relex FRACAS Management System can close the loop to dramatically improve the quality and reliability of your products and processes, please email <u>info@relexsoftware.com</u>.

# **Understanding Importance Measures in Fault Tree Analysis**

# Calculating Birnbaum, Criticality, and Fussell-Vesely Importance Measures

Reliability importance measures attempt to identify the fault tree event whose improvement will yield the greatest improvement in system performance. The three most popularly used importance measures are:

- Birnbaum

- Criticality

- Fussell-Vesely

This technical brief explains how to calculate these three importance measures and describes the underlying logic that led to their development. It also demonstrates how to use each importance measure by rank ordering the basic events by the values of their importance measures and then considering improving first that basic event with the highest importance measure value.

#### **Birnbaum Importance Measure**

The Birnbaum importance measure is defined as:

$I_B(A) = P\{X|A\} - P\{X|\sim A\}$

Where:

A indicates that the event whose importance is being measured occurred.

- ~A indicates that this event did not occur.

- X indicates the top event.

The Birnbaum importance measure for the event A is the difference in the probability of the top event given that the event A did occur minus the probability of the top event given that the event A did not occur. This is one measure of the increase in the probability of the top event due to the event A.

Consider a top event X, which is the result of event A and event B being connected by an OR gate. The fault tree would define the top event X to be  $X = \{A \text{ or } B\}$ . Assume that the probability of event A is 0.1 and that of event B is 0.2.

Let P{X|A} denote the probability of the top event X given that the basic event A occurred. Clearly, if A occurs, {A or B} occurs, so that X occurs. Therefore:

$P{X|A} = 1.0$

Also, let  $P{X|\sim A}$  denote the probability of the top event given that the basic event A does not occur. Here, given that A does not occur, X only occurs if the event B occurs. Therefore:

$P{X|\sim A} = P{B}$  where  $P{B} = 0.2$

Thus, the Birnbaum importance measure equals:

$I_B(A) = (P{X|A} - P{X|\sim A}) = (1.0 - P{B}) = (1.0 - 0.2) = 0.8$

#### **Criticality Importance Measure**

Although the Birnbaum importance measure,  $I_B(A)$ , is useful, it does not directly consider how likely the event A is to occur. For instance, in the previous example,  $I_B(A) = (1.0 - P\{B\})$  does not even involve the probability of the event A. This could lead to assigning high importance values to events that are very unlikely to occur and may be very difficult to improve. Remember, an event with a low probability of occurring in a fault tree is an event that has already been improved, so further improvement may be difficult to obtain. Therefore, in an attempt to focus only on those events that truly are important (which not only lead to the top event but also are more likely to occur and may reasonably be improved), a modified Birnbaum importance measure known as a Criticality importance measure is used.

The Criticality importance measure is defined as:

$I_{C}(A) = I_{B}(A) * P\{A\}/P\{X\}$

=  $(P{X|A} - P{X|~A}) * P{A}/P{X}$  where X is the top event.

The Criticality importance measure modifies the Birnbaum importance measure by:

- Adjusting for the relative probability of the basic event A to reflect how likely the event is to occur and how feasible it is to improve the event (which makes it easier to focus on the truly important basic events).

- Conditioning on the occurrence of the top event X to restrict the measure to evaluating the effect of the basic event A, not the probability of the top event X (which makes it possible to compare basic events between fault trees).

Now, the Criticality importance measure,  $I_B(A)$ , for the earlier OR gate example, where  $P\{A\} = 0.1$  and  $P\{B\} = 0.2$ , is to be calculated. The probability of the top event, the event X = {A or B}, is first calculated:

P{X} is the probability of the top event occurring.

P{A} is the probability of event A occurring.

P{-A} is the probability of event A not occurring.

P{A and B} is the probability of both events A and B occurring.

P {A or B} is the probability of either event A or event B or both events occurring.

If events A and B are independent, then  $P{A and B} = (P{A} * P{B})$ . Therefore:  $P{X} = P{A \text{ or } B}$  $= P{A} + P{B} - (P{A} * P{B})$ = 0.1 + 0.2 - (0.1 \* 0.2) = 0.28Based on earlier calculations:  $I_B(A) = 0.8$ ,  $P\{A\} = 0.1$ , and  $P\{X\} = 0.28$ Therefore, the Criticality importance measure is given by:  $I_{C}(A) = (I_{B}(A) * P\{A\}) / P\{X\}$ = (0.8 \* 0.1) / (0.28) = 0.2857143Similar calculations for event B vields:  $I_{\rm B}({\rm B}) = 0.9$ And:  $I_{C}(B) = (I_{B}\{B\} * P\{AB\}) / P\{X\} =$ (0.9 \* 0.2) / (0.28) = 0.6428571Now, consider the Criticality importance measure for the AND gate, where:  $P{A} = 0.1, P{B} = 0.2, and P{X} = P{A and B}$  $= (P{A}) * (P{B}) =$ (0.1) \* (0.2) = 0.02, by independence of the basic events A and B. Here:  $P{X|A} = P{A and B|A}$  $= P\{B\} * P\{X|\sim A\}$ = P{A and B|~A} = 0.0 And:  $I_B(A) = P\{X|A\} - P\{X|\sim A\} = P\{B\} - 0.0 = P\{B\}$ Thus:  $I_{C}(A) = (I_{B}\{A\} * P\{A\}) / P\{X\} = (P\{B\} * P\{A\}) / P\{X\} = P\{X\}/P\{X\} = 1.0$ Similarly,  $I_B(B) = P\{X|B\} - P\{X|\sim B\} = (P(A) - 0.0 = P\{A\})$

So that:

$I_{C}(B) = (I_{B}\{B\} * P\{B\}) / P\{X\} = (P\{A\} * P\{B\}) / P\{X\} = P\{X\}/P\{X\} = 1.0$

Given independence of the basic events, all of the basic events under an AND gate will have the same Criticality importance measure. Thus, the Criticality importance measure is uninformative for AND gates.

#### **Fussell-Vesely Importance Measure**

The Fussell-Vesely importance measure is calculated quite differently than the Birnbaum or Criticality importance measures. It is constructed using minimal cut sets. A cut set is a set of basic events whose occurrence causes the top event to occur. A minimal cut set is a cut set is a cut set if any of its basic events were removed.

For example, the set of all the basic events is a cut set (or else the fault tree would be meaningless). If the fault tree consists of a single AND gate, then the cut set consisting of all the basic events is the only cut set and the minimal cut set. This is because all events leading into an AND gate must occur in order for the AND gate to be activated.

If the fault tree consists of a single OR gate, then the cut set consisting of all the basic events is not a minimal cut set unless there is only one basic event. This is because only one event leading into an OR gate needs to occur for the OR gate to be activated. In this case, any collection of basic events is a cut set. Therefore, given an OR gate, only those cut sets containing a single basic event are minimal cut sets.

Minimal cut sets are important in fault trees because they may be used to calculate the probabilities of events, including the top event. For example, the probability of the top event is given by the probability of the union of all the minimal cut sets.

Another interesting probability associated with the basic event A is the probability of the union of all minimal cut sets containing the basic event A. This is because the probability of the union of all minimal cut sets containing the basic event A is the probability that the top event is caused by a cut set containing the event A. This is a measure of the association of the basic event A with the top event X. It does not directly measure the probability that the top event X was caused by the basic event A, but it does indicate the potential importance of the basic event A.

A useful fact is that the probability of the union (OR) of sets is equal to the sum of the probabilities of the sets when the sets are mutually exclusive. If the sets are "nearly" mutually exclusive and, in addition, the basic events are independent and their probabilities are small, then this equality is approximately satisfied. For example, suppose that two minimal cut sets, C1 and C2, are given by C1 = {A and B and C} and C2 = {A and D}. Then, exactly:

$P{C1 \text{ or } C2} = P{C1} + P{C2} - P{C1 \text{ and } C2}$

= P{C1} + P{C2} - {P(A and B and C) and (A and D)}

=  $P{C1} + P{C2} - P{A and B and C and D}$

=  $P{C1} + P{C2} - P{A} * P{B} * P{C} * P{D}$ , which is approximately equal to  $P{C1} + P{C2}$

when the probability of each of the basic events is small.

This idea is used in calculating the Fussell-Vesely importance measure. This measure considers the ratio of the probability of the union of all minimal cut sets containing the basic event A, divided by the probability of the union of all minimal cut sets. In practice, the numerator is replaced by the approximating sum of the probabilities of all minimal cut sets containing the basic event A, and the denominator uses the exact calculation, which is simply the probability of the top event X.

With the Fussell-Vesely importance measure, the fact that there is only one cut set for an AND gate leads to the uninformative result that all of the basic events leading to an AND gate will have the same value for the Fussell-Vesely importance measure. Now, consider the previous example of the fault tree with an OR gate. Two minimal cut sets exist:  $C1 = \{A\}$  and  $C1 = \{B\}$ . Recall that  $P\{A\} = 0.1$ ,  $P\{B\} = 0.2$ , and that  $P\{X\} = P\{A \text{ or } B\} = 0.28$ . Note that C1 is the only minimal cut set containing the basic event A, and C2 is the only minimal cut set containing the basic event B. Also,  $P\{C1\} = P\{A\} = 0.1$ , and  $P\{C2\} = P\{B\} = 0.2$ . Therefore, the Fussell-Vesely importance measures for the basic events A and B are given by:

$I_{FV}(A) = P\{C1\} / P\{X\} = 0.1 / 0.28 = 0.3571429$  and

$I_{FV}(B) = P\{C2\} / P\{X\} = 0.2 / 0.28 = 0.7142857$

#### Importance Measure Usage

If all three importance measures yield the same rank ordering of basic events, then the strategy for using the importance measures is straightforward. However, when the three importance measures yield different rank orderings of basic events, the following guidelines suggest how to select an appropriate solution:

- Keep in mind that the goal is to assist in selecting the next basic event to consider for improvement. It cannot be concluded definitively that a particular basic event must receive the next improvement effort.

- Ensure the correct **primary time point** is chosen. The rank ordering of the importance measures may be different at different time points.

- Consider averaging the three-way ranking of the three importance measure rank orderings for each basic event. This

may indicate a consensus of the three measures.

- Study the sequential ranking, first by ranking by the Fussell-Vesely or Criticality importance measure and then break ties within the ranking by the Birnbaum importance measure.

- When in doubt or when calculation performance is an issue, the Criticality importance measure is probably a reasonable single measure to use. It considers the probability of the basic event (an improvement over the Birnbaum importance measure). However, if this is a problem with uninformative results caused by AND gates (as can happen with the Fussell-Vesely importance measure), then use the Birnbaum importance measure.

# **Calculating MTTF When You Have Zero Failures**

P

# at Docu

# **Reliability Growth**

## **Observing and Predicting Trends in Reliability**

Today's complex products require that companies focus on establishing detailed plans and procedures for developing and manufacturing products that meet specified reliability, maintainability, and other performance requirements. **Reliability growth** refers to a well-defined process for identifying and correcting reliability problems early in the design process so that the reliability of a product increases or "grows" as the product goes through successive development stages. Reliability growth programs should be established for all new products and for all existing products undergoing major redesigns so that the improvement due to changes in design and manufacturing processes can be easily tracked.

During the early design stage, a reliability goal is set for a product. Because failure data from prototype testing is not yet available, the initial reliability goal is often based on either the failure data for similar products or the failure data for the subcomponents of the product. During the development stage, product prototypes generally undergo extensive testing so that deficiencies in respect to design, engineering, and manufacturing can be identified and corrected.

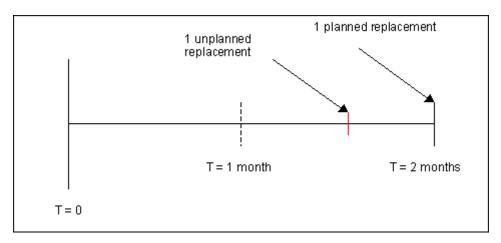

A typical reliability improvement test consists of operating product prototypes for several weeks in the same types of environments in which customers will eventually operate the product. A team of project engineers and technicians analyze every failure that occurs, determining root causes for failures and developing design and manufacturing improvements that are to either eliminate or reduce the recurrences of these failures. As the testing continues, the improvements developed by the team are incorporated into the prototype so that product reliability continues to improve throughout the testing period.

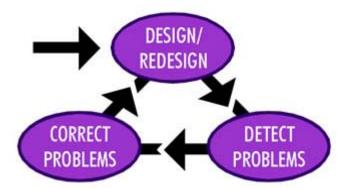

## Acheiving Reliability Growth

The three most important steps in the iterative process for achieving reliability growth are depicted in the feedback loop that follows:

Most of the problems encountered during testing are likely to be component failures and manufacturing deficiencies that could not be foreseen in the early design phase. Because various performance requirements can conflict, optimizing a design to meet one requirement can cause the design to fail to meet another requirement. Thus, iterations of designs are often needed to correct all of the component selection and manufacturing deficiencies that are found during prototype testing.

In addition to improving reliability, early implementation of a reliability growth program minimizes the impact on production scheduling and total product cost, especially since the costs associated with either redesigning a product late in the development cycle or retrofitting products already in the field are extremely high. Developing a product that meets reliability requirements also ensures that the product ultimately meets user needs and has an acceptable total life cycle cost. Setting interim reliability goals that are to be achieved during testing ensures that resources are allocated efficiently.

# **Reliability Growth Data**

The basic principle of any reliability growth model is to apply the testing results and data points to determine if the reliability of the product is growing sufficiently to meet the reliability requirements for the product. The types of data used for predicting reliability growth are:

- **Reliability Data.** The reliability of the product is recorded at different points in time. The reliability is a ratio of the number of units still functioning and the number of units that entered the stage.

- Success/Failure Data. The item is tested and can either succeed or fail. Success data can consist of a code indicating the outcome, such as S for Success or F for Failure; or, it can consist of a code indicating the failure mode for each failure. Success/failure data might also indicate the number of failures that occurred when several units are tested together.

- Failure Time Data. The time to failure for an item is tracked using either cumulative or non-cumulative operating times. Failure time data is the most commonly used type of data in reliability growth. This data can be for one failure or system, or it can be for multiple failures or multiple systems, which is commonly called interval or grouped data.

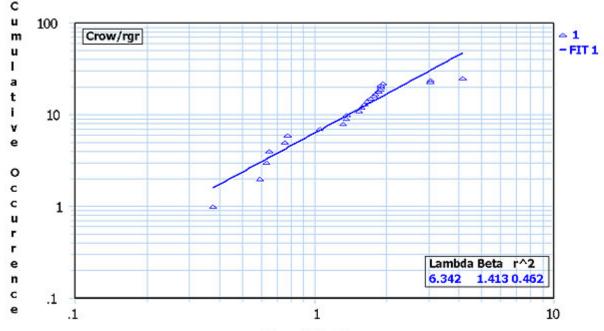

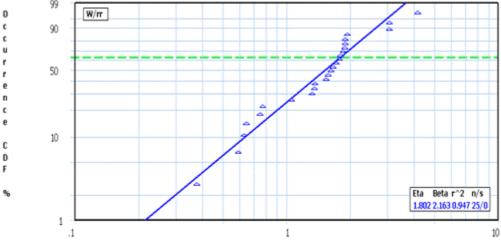

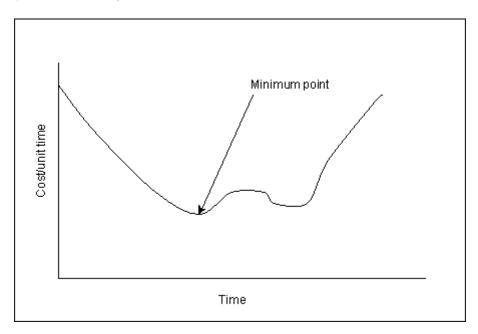

The failure data collected during prototype testing is used to determine whether the reliability goal for the product is likely to be met or exceeded by the time the product is scheduled to be put into full-scale production. Although many methods exist for modeling the reliability growth process, the Duane/Crow-AMSAA model is considered the best practice. In 1964, J. T. Duane, an engineer at the Aerospace Electronics Department of General Electronic Company, published a paper demonstrating how a learning curve approach could be used to monitor the continuing reliability improvements in the early stages of developing complex electromechanical and mechanical systems. Duane explained how this was because the lessons learned from failures were used to refine designs.

According to Duane, a graph of the cumulative MTBF versus the cumulative operating time plotted on log-log paper fell close to a straight line. Graphing this learning curve provides a means of measuring and predicting reliability during a period of product change. Dr. Larry Crow later added powerful statistical capabilities to Duane's postulate for learning curve modeling to create the model so widely respected and implemented today. An example of a reliability growth chart generated by the Duane/Crow-AMSAA model follows:

#### **Cumulative Time**

Reliability growth is generally quantified by graphing any of the following three measures over time:

- The increase in the mission success probability (reliability).

- The increase in MTBF.

- The decrease in failure rate as a function of time.

Reliability growth charts depict trends that are used to forecast failures as a function of additional test time or calendar time, thereby making planning for redesign and test resources easier. In addition to allowing you to determine whether reliability requirements will be achieved, reliability growth charts can help you to determine

the time needed to meet these requirements and the associated costs. Extrapolating a growth curve beyond the currently available data shows what reliability a program can be expected to achieve providing that the conditions of the test and the engineering effort to improve reliability are maintained at their present levels. If the reliability growth graph indicates that the reliability goal is not going to be met or exceeded, then the product design must be improved. This might require the use of more reliable components or redundancy. Additional resources might also have to be devoted to designing and manufacturing a more reliable product to meet the required delivery date.

## **Other Uses for Reliability Growth Charts**

In addition to analyzing the results from testing newly developed or redesigned products, the Duane/Crow-AMSAA model can be used to:

- Predict future failures.

- Track fleets of repairable systems.

- Provide accurate trending of significant events for management.

- Forecast safety incidents that can be controlled.

# Fault Tree Gates Logically Link Basic Events to Top Events

Analyze Numerous Hardware Configurations Using Multiple Gate/Event Options

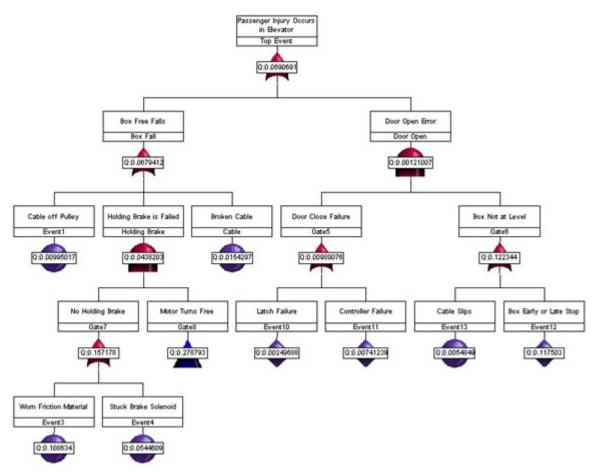

Fault Tree Analysis (FTA) is well recognized worldwide as an important tool for evaluating safety and reliability in system design, development, and operation. Based on a simple set of rules and logic symbols from probability theory and Boolean algebra, FTA uses a top-down approach to generate a logic model that provides for both qualitative and quantitative evaluation of system reliability. The undesirable event at the system level is referred to as the **top event**. It generally represents a system failure mode or hazard for which predicted reliability data is required. The lower level events in each branch of a fault tree are referred to as **basic events**. They represent hardware, software, and human failures for which the probability of failure is given based on historical data. Basic events are linked via logic symbols (**gates**) to one or more undesirable top events.

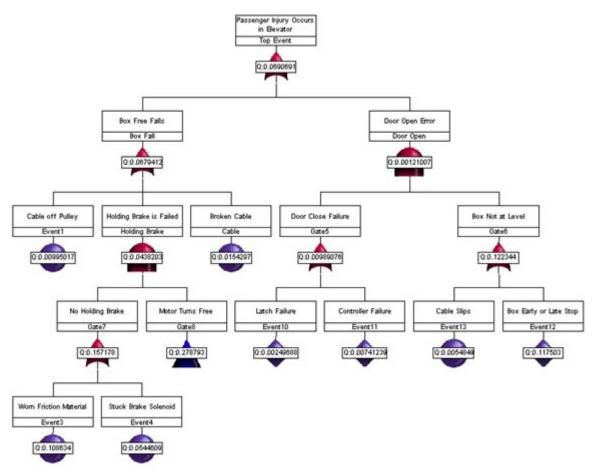

Today, computerized FTA is used to analyze very complex systems as well as very complex relationships between hardware, software, and humans. Small fault trees have fewer than 100 events, medium fault trees have from 100 to 1,000 events, and large fault trees have more than 1,000 events! Using good FTA software, you can cut, copy, paste, rearrange, and delete events and gates in various fault tree branches to quickly and easily compare different hardware configurations. An example of a very simple computer-generated fault tree follows.

\* Generated in Relex Fault Tree. Click the image to view a full-size version.

In this fault tree, "Passenger Injury Occurs in Elevator" is defined as the top event. The reasons why passenger injury in an elevator could occur have been determined to be either that the box free falls or that the door is open at an inappropriate time. After determining all possible causes for each event identified, the events and gates for connecting them to higher-level events are added to the fault tree. Any faults that can be further developed to determine causes are then added as lower-level events and connected by the appropriate gates.

The lowest-level basic events that terminate fault tree paths are often called **terminal events** or **primary events**. They are either component-level events that cannot be further resolved or external events. For example, in the first level of possible

events for the free fall of the box, "Cable off Pulley" and "Broken Cable" are terminal events. Because these events are primary faults, they are not developed any further in the fault tree.

The tables below describe the fault tree gates and events that are implemented in Relex and many other computerized FTA programs. **Note:** Relex Fault Tree is the only commercial software product for reliability analysis that supports dynamic gates (Functional Dependency, Sequence-Enforcing, and SPARE gates). Although a few other competing products support two-input Priority AND gates, none of them perform the dynamic analysis (Markov) required.

## **Fault Tree Gates**

| Bitmap/Line<br>Art | Gate<br>Name                       | Gate Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | AND Gate                           | The AND gate is used to indicate that the output occurs if and only if all the input events occur.<br>The output of an AND gate can be the top event or any intermediate event. The input events can<br>be basic events, intermediate events (outputs of other gates), or a combination of both. There<br>should be at least two input events to an AND gate.<br><b>Summary of Logic:</b> All events must be TRUE for the output to be TRUE.                                                                                                                              |

| $ \land $          | OR Gate                            | The OR gate is used to indicate that the output occurs if and only if at least one of the input events occur. The output of an OR gate can be the top event or any intermediate event. The input events can be basic events, intermediate events, or a combination of both. There should be at least two inputs to an OR gate.  Summary of Logic: If at least 1 event is TRUE, the output is TRUE.                                                                                                                                                                        |

| M:0                | Voting Gate<br>(m/n)               | The Voting gate (m/n) is used to indicate that the output occurs if and only if m out of the n input events occurs. The m input events need not occur simultaneously. The output occurs when at least m input events occur. When m = 1, the Voting gate behaves like an OR gate. The output of a Voting gate can be a top event or an intermediate event. The input events can be basic events, intermediate events, or combinations of both.<br><b>Summary of Logic:</b> If m = 2 and n = 3, 2 input events must be TRUE for the output to be TRUE.                      |

|                    | Exclusive<br>OR Gate<br>(XOR Gate) | The Exclusive OR (XOR) gate is used to indicate that the output occurs if and only if one of the two input events occurs and the other input event does not occur. The output of an XOR gate can be the top event or an intermediate event. The input events can be basic events, intermediate events, or combinations of both. An XOR gate can have only two inputs.<br><b>Summary of Logic:</b> If 1 and only 1 input event is TRUE, the output is TRUE.                                                                                                                |

|                    | NAND Gate                          | The NAND gate functions like a combination of an AND gate and a Not gate. The NAND gate is used to indicate that the output occurs when at least one of the input events is absent. The output of a NAND gate can be the top event or an intermediate event. The input events can be basic events, intermediate events, or combinations of both. The presence of a NAND gate may give rise to non-coherent trees, where the non-occurrence of an event causes the top event to occur.<br><b>Summary of Logic:</b> If there is at least 1 FALSE event, the output is TRUE. |

| À<br>Å                                      | NOR Gate                       | The NOR gate functions like a combination of an OR gate and a Not gate. The NOR gate is used to indicate that the output occurs when all the input events are absent. The output of a NOR gate can be the top event or an intermediate event. The input events can be basic events, intermediate events, or combinations of both. The presence of a NOR gate may give rise to non-coherent trees, where the lack of an event causes the top event to occur.                                                                                                                                                                          |

|---------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             |                                | Summary of Logic: If there is at least 1 TRUE input event, the output is FALSE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Å                                           | Not Gate                       | The Not gate is used to indicate that the output occurs when the input event does not occur. The presence of a Not gate may give rise to non-coherent trees, where the non-occurrence of an event causes the top event to occur. There is only one input to a Not gate.<br><b>Summary of Logic:</b> The output is the opposite of the input gate or event.                                                                                                                                                                                                                                                                           |

|                                             |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                             | Inhibit Gate                   | The Inhibit gate is used to indicate that the output occurs when the input events (I1 and I2) occur and the input condition (C) is satisfied. The output of an Inhibit gate can be a top event or an intermediate event. The input events can be basic events, intermediate events, or combinations of both.                                                                                                                                                                                                                                                                                                                         |

| $\sim$                                      |                                | Summary of Logic: If all input events and the input condition are TRUE, the output is TRUE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                             | Priority AND<br>(PAND)<br>Gate | The Priority AND (PAND) gate is used to indicate that the output occurs if and only if all input events occur in a particular order. The order is the same as that in which the inputs events are connected to the PAND gate from left to right. The PAND gate is a dynamic gate, which means that the order of the occurrence of input events is important to determining the output. Relex PAND gates support multiple inputs. This is a generalization of an earlier version of the Relex PAND gate where only two inputs were allowed.                                                                                           |

|                                             |                                | The output of a PAND gate can be the top event or an intermediate event. The inputs can be basic events or outputs of any AND gate, OR gate, or dynamic gate (Priority AND gate, Functional Dependency gate, Sequence-Enforcing gate, or SPARE gate). (These gates should have the inputs from basic events or other AND gates and OR gates.) You may rearrange items that enter PAND gates to fail in temporal order from left to right to trigger the event. The PAND gate also supports a single input. When only a single input exists, then occurrence of that input will trigger the event.                                    |

|                                             |                                | Summary of Logic: All input events must be TRUE for the output to be TRUE, and the events should occur from left to right in the temporal order.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\stackrel{\blacktriangle}{\bigtriangleup}$ | Transfer<br>Gate               | A Transfer gate is a symbol used to link logic in separate areas of a fault tree. There are two primary uses of Transfer gates. First, an entire fault tree may not fit on a single sheet of paper (or you may want to keep the individual trees small to view and organize them). Second, the same fault tree logic may be used in different places in a fault tree. Through the use of Transfer gates, you can define this logic once and use it in several places. To use a Transfer gate, you insert a Transfer In gate in a fault tree, that links to a Transfer Out gate, which represents the top gate of another fault tree. |

|                                             | Remarks<br>Gate                | A Remarks gate is used for the entry of comments. A Remarks gate has no calculation data associated with it, and, therefore, has no effect on calculations. However, the tree branch may continue after a Remarks gate. There can only be one input to a Remarks gate.                                                                                                                                                                                                                                                                                                                                                               |

|                                             | Pass-<br>Through<br>Gate       | A Pass-Through gate is used for visually aligning the events and gates in a fault tree. A Pass-<br>Through gate extends a vertical connector for visual alignment. A Pass-Through gate has no<br>calculation data associated with it, and, therefore, has no effect on calculations. However, the<br>tree branch may continue after a Pass-Through gate. There can be only one input to a Pass-<br>Through gate.                                                                                                                                                                                                                     |

| Functiona<br>Dependence<br>Gate | I The functional dependency (FDEP) gate is used to indicate that all dependent basic events are forced to occur whenever the trigger event occurs. The separate occurrence of any of the dependent basic events has no effect on the trigger event. The FDEP gate has one trigger event and can have one or more dependent events. All dependent events are either basic events or spare events. The trigger event can be a terminal event or outputs of any AND gate, OR gate, or dynamic gate (PAND gate, FDEP gate, Sequence- Enforcing gate, or SPARE gate).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | Dependent events are repeated events that are present in other parts of the fault tree. The FDEP gate is a dynamic gate, which means the temporal order of the occurrence of events is important to analyze this gate. Generally, the output of the FDEP gate is not that important; however, it is equivalent to the status of its trigger event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                 | The FDEP gate can also be used to set the priorities for SPARE gates. For example, if multiple spares are connected to a FDEP gate, after the occurrence of the trigger event, all spares that are connected to the FDEP gate will fail. Upon failure of these spares, the next available good spare in those SPARE gates will replace the failed spares. If there exists a conflict in choosing the next available spare between multiple SPARE gates, the priority will be based on the order of the connection of these spares in the FDEP gate from left to right.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                 | <b>Summary of Logic:</b> When the trigger event is TRUE, then dependent events are forced to become TRUE. The trigger event must be TRUE for the output to be TRUE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Sequence<br>Enforcing<br>Gate   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | The SEQ gate is a dynamic gate, which means the occurrence of the inputs follows a sequential order. In other words, an event connected to a SEQ gate will be initiated immediately after occurrence of its immediate left event. Therefore, if the leftmost input is a basic event, then the SEQ gate works like a cold SPARE gate. The SEQ gate can be contrasted with the PAND gate in that the PAND gate detects whether events occur in a particular order (but the events can occur in any order), whereas the SEQ gate allows the events to occur only in the specified order.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | The first input (leftmost input) to a SEQ gate can be a terminal event or outputs of any AND gate, OR gate, or dynamic gate (PAND gate, FDEP gate, SEQ gate, or SPARE gate). Only basic events are allowed for all other inputs. You may rearrange the events that enter SEQ gates; however, rearrangement is not allowed if the first input is an output from another gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                 | <b>Summary of Logic:</b> The output is TRUE if and only if all input events are TRUE; but the input events must occur in a particular order.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPARE Ga                        | The SPARE gate is used to model the behavior of spares in the system. The SPARE gate is used to indicate that the output occurs if and only if all input spare events occur. All inputs of a SPARE gate are spare events. A SPARE gate can have multiple inputs. The first event (leftmost event) is known as the primary input, and all other inputs are known as alternative inputs. The primary event is the one that is initially powered on, and the alternative inputs specify that they are in standby mode. After a failure, the active/powered unit that is the first available spare from left to right will be chosen to be active. If all units are failed, then the spare will be considered as failed (output occurred).                                                                                                                                                                                                                                                                                                       |

|                                 | Depending on the dormancy factor of spares, spares can fail even in standby mode. The Relex SPARE gate is more flexible and can handle any kind of spares. If the dormancy factor of all spares connected to a SPARE gate is 0, then the spare acts like a cold spare. If the dormancy factor of all spares connected to a SPARE gate is 1, then the spare acts like a hot spare. If the dormancy factors of all spares connected to a SPARE gate is 1, then the spare acts like a hot spare. If the dormancy factors of all spares connected to a SPARE gate is 1, then the spare acts like a hot spare. If the dormancy factors of all spares connected to a SPARE gate are the same (and are between 0 and 1), then the spare acts like a warm spare. If the dormancy factors of its inputs are different, then it handles generalized situations. The SPARE gate is a dynamic gate, which means the temporal order of the occurrence of events is important to analyze this gate. You may rearrange spare events that enter SPARE gates. |

|                                 | Summary of Logic: All inputs must be TRUE for the output to be TRUE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Fault Tree Events

| Bitmap/Line<br>Art | Event<br>Name        | Event Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\bigcirc$         | Basic Event          | A Basic event is either a component-level event that is not further resolved or an external event.<br>It is at the lowest level in a tree branch and terminates a fault tree path. Component-level<br>events can include hardware or software failures, human errors, and system failures.                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | Spare Event          | A Spare event is used to specify spares in dynamic fault trees. A Spare event is similar to a basic event in functionality; however, a spare event allows only rates as inputs. The dormancy factor of the spare indicates the ratio of failure rate in the spare mode and the failure rate in the operational mode. Spare events can have a spare pool, which represents the number of identical instances of that event. For example, if a spare pool of an event is 2, there are 2 identical spare components of that spare events. Spare events are restricted to use as either spares to SPARE gates or as dependent events to FDEP gates.                                             |

|                    | House Event          | A House event can be turned on or off. When a House event is turned on (TRUE), that event is presumed to have occurred and the probability of that event is set to 1. When a House event is turned off (FALSE), it is presumed not to have occurred, and the probability is set to 0. House events are useful in making parts of a fault tree functional or non-functional. When a House event is turned off, the gate that the House event inputs to will be removed from the tree during calculation. By turning that same House event on, the gate that the House event inputs to will be calculated normally. House events are also referred to as trigger events and switching events. |

| $\Diamond$         | Undeveloped<br>Event | An Undeveloped event is used if further resolution of that event does not improve the understanding of the problem, or if further resolution is not necessary for proper evaluation of the fault tree. It is similar to a Basic event, but is shown as a different symbol to signify that it could be developed further, even though you have not done so for the analysis. Undeveloped events may be broken down into associated gates and events.                                                                                                                                                                                                                                         |

# Selecting the Appropriate Reliability Model

# Choosing Between RBDs, Fault Trees, Event Trees, and Markov Analyses

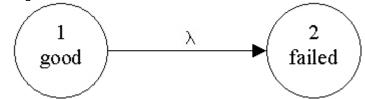

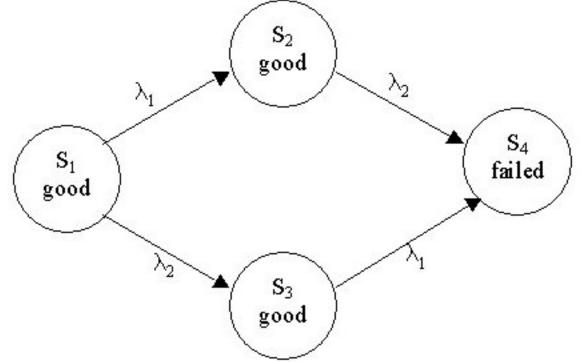

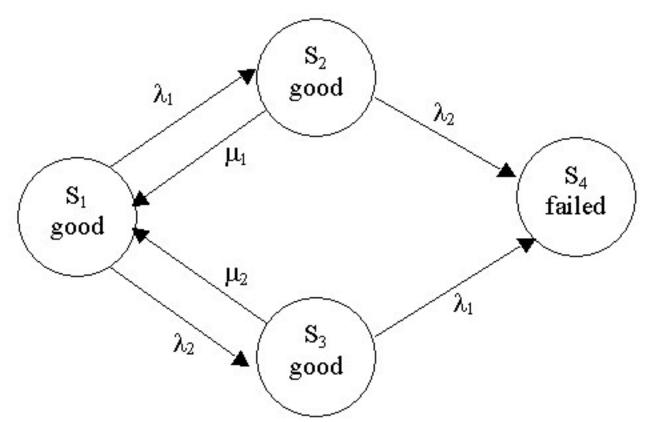

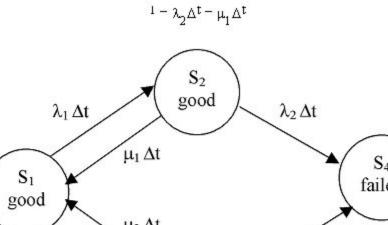

System failure depends on the combination and sequence of component failures. If the system failure can be expressed completely based on the combinations of component failures, then the failure model is known as a combinatorial model.

To model any system effectively, you must:

- Understand the overall system configuration and system behavior.

- Be able to define the failure and repair distributions of the components.

- Be able to represent the system structure visually.

The above system knowledge is essential to determining and performing the appropriate mathematical analysis. The table below provides descriptions of several modeling methodologies and lists both the advantages and disadvantages associated with their traditional implementations. It then notes the more recent advances that either reduce or eliminate some of these disadvantages.

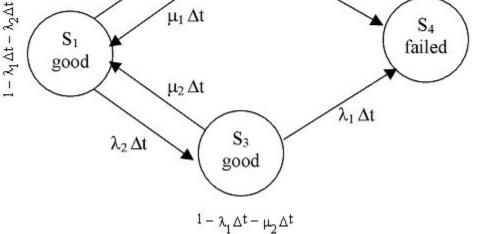

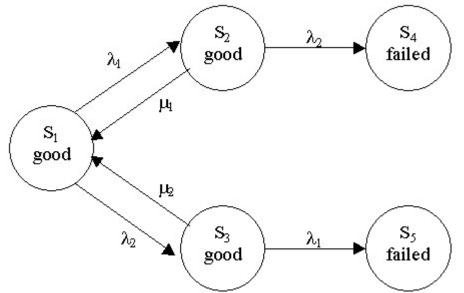

**Note:** Traditional RBDs, Fault Trees, and Event Trees cannot model the temporal order of events. This means that, in these methodologies, it does not matter whether component 1 fails first or component 2 fails first. If component 2 is used only after component 1 fails, then the order of events is important. Only Markov models can consider the order of events and the actual times of their occurrences. Thus, Markov models are the only correct models for highly dependable, complex systems.