# **Tutorial:**

# Model-Based Design Using Model Composer

UG1259 (v2018.3) December 5, 2018

See all versions of this document

# **Revision History**

The following table shows the revision history for this document.

| Section                                            | Revision Summary                                          |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------|--|--|--|

| 12/05/2018 Version 2018.3                          |                                                           |  |  |  |

| Design files                                       | Updates to design files.                                  |  |  |  |

| Lab 3: Automatic Code Generation                   | Revisions to Lab 3                                        |  |  |  |

| 06/06/2018                                         | 8 Version 2018.2                                          |  |  |  |

| General updates                                    | Editorial updates and corrections.                        |  |  |  |

|                                                    | Changed all instances of xmcCreateLibrary                 |  |  |  |

|                                                    | command to xmcImportFunction command.                     |  |  |  |

|                                                    | Command has been renamed to better indicate its           |  |  |  |

|                                                    | function.                                                 |  |  |  |

|                                                    | Added a Step 2 to Lab 2 to create a custom block using    |  |  |  |

| Step 2: Custom Blocks with Function Templates (Lab | function templates.                                       |  |  |  |

| 2)                                                 |                                                           |  |  |  |

| 04/04/2018                                         | 8 Version 2018.1                                          |  |  |  |

| General updates                                    | Editorial updates and corrections.                        |  |  |  |

|                                                    | Updated dialog box displays throughout manual to          |  |  |  |

|                                                    | reflect appearance in 2018.1 release.                     |  |  |  |

| Step 1: Set up the Import Function Example (Lab 2) | Added this Note:                                          |  |  |  |

|                                                    | <b>IMPORTANT:</b> You can use the const qualifier in the  |  |  |  |

|                                                    | function signature to identify the inputs to the block or |  |  |  |

|                                                    | use the pragma INPORT.                                    |  |  |  |

# **Table of Contents**

| Revision History                                         | 2  |

|----------------------------------------------------------|----|

| Model Composer Lab Overview                              | 4  |

| Introduction                                             | 4  |

| Software Requirements                                    | 5  |

| Launching Model Composer                                 | 5  |

| Locating and Preparing the Tutorial Files                | 6  |

| Lab 1: Introduction to Model Composer                    | 7  |

| Introduction                                             | 7  |

| Step 1: Review the Model Composer Library                | 8  |

| Step 2: Build Designs with Model Composer Blocks         | 9  |

| Step 3: Work with Data Types                             |    |

| Conclusion                                               |    |

| Lab 2: Importing Code into Model Composer                | 20 |

| Introduction                                             | 20 |

| Step 1: Set up the Import Function Example               | 20 |

| Step 2: Custom Blocks with Function Templates            | 23 |

| Conclusion                                               | 29 |

| Lab 3: Automatic Code Generation                         |    |

| Introduction                                             |    |

| Step 1: Review Requirements for Generating Code          |    |

| Step 2: Mapping Interfaces                               |    |

| Step 3: Generate IP from Model Composer Design           |    |

| Step 4: Generate HLS Synthesizable Code                  |    |

| Step 5: Port a Model Composer Design to System Generator | 42 |

| Conclusion                                               | 48 |

| Legal Notices                                            | 49 |

| Please Read: Important Legal Notices                     | 49 |

# Model Composer Lab Overview

### Introduction

Xilinx® Model Composer is a model-based design tool that enables rapid design exploration within the Simulink® environment and accelerates the path to production on Xilinx programmable devices through automatic code generation.

Model Composer is designed as an add-on to Simulink and provides a library of performanceoptimized blocks for design and implementation of algorithms on Xilinx FPGAs. The Model Composer library offers over 80 predefined blocks, including application-specific blocks for Computer Vision and Image Processing and functional blocks for Math, Linear Algebra, Logic, and Bit-wise operations, among others.

You can focus on expressing algorithms using blocks from the Xilinx Model Composer library as well as custom user-imported blocks, without worrying about implementation specifics, and leverage all the capabilities of Simulink's graphical environment for algorithm design, simulation, and functional verification. Model Composer then transforms your algorithmic specifications to production-quality implementation using automatic optimizations that extend the Xilinx High Level Synthesis technology.

This tutorial introduces the end-to-end workflow for using Model Composer.

The included labs are as follows:

- Lab 1: Introduction to Model Composer

- o Introduction to Model Composer Library Blocks for design

- o Integration with native Simulink and Support for vectors and matrices

- o Working with data types

- Lab 2: Create Custom Blocks in Model Composer

- Using the xmcImportFunction command to specify functions defined in source and header files to import into Model Composer and create Model Composer blocks or a block library.

- Creating custom blocks with Function templates

- Lab 3: Automatic Code Generation

- o Requirements for Code Generation

- Mapping Interfaces

- o Generate an IP for use in the Vivado® IP Integrator

- o Generate Vivado HLS Synthesizable Code

- o Port a Model Composer Synthesized Design into System Generator for DSP

### **Software Requirements**

The lab exercises in this tutorial require that you have installed the following software:

- MATLAB<sup>™</sup>: The MATLAB releases and simulation tools supported in this release of Model Composer are described in the Compatible Third-Party Tools section of the *Vivado Design Suite User Guide: Release Notes, Installation, and Licensing* (UG973).

- Vivado Design Suite release: 2018.2 (Includes Vivado HLS)

- Model Composer: 2018.2

See the *Vivado Design Suite User Guide: Release Notes, Installation, and Licensing* (UG973) for a complete list and description of the system and software requirements

# Launching Model Composer

To launch Model Composer:

- On Windows systems:

- Select Start > All Programs > Xilinx Design Tools > Model Composer 2018.x > Model Composer 2018.x.

OR

o Double-click the Model Composer icon which was placed on your desktop after installation.

• On Linux systems:

You launch Model Composer under Linux using a shell script called model\_composer located in the <Model\_composer\_install\_dir>/2018.x/bin directory. Before launching this script, you must make sure the MATLAB executable can be found in your Linux system's \$PATH environment variable for your Linux system. When you execute the model\_composer script, it will launch the first MATLAB executable found in \$PATH and attach Model Composer to that session of MATLAB. Also, the model\_composer shell script supports all the options that

MATLAB supports and all options can be passed as command line arguments to the model\_composer script.

When Model Composer opens, you can confirm the version of MATLAB to which Model Composer is attached by entering the version command in the MATLAB Command Window.

```

>> version

ans =

'9.2.0.538062 (R2017a)'

```

### Locating and Preparing the Tutorial Files

There are separate project files and sources for each of the labs in this tutorial. You can find the design files for this tutorial on the www.xilinx.com website.

- 1. Download the Reference Design Files from the Xilinx website.

- 2. **Extract** the zip file contents into any write-accessible location on your hard drive or network location.

**RECOMMENDED:** You will modify the tutorial design data while working through this tutorial. You should use a new copy of the ModelComposer\_Tutorial directory extracted from ug1259-model-composer-tutorial.zip each time you start this tutorial.

**TIP:** This document assumes the tutorial files are stored at C:\ModelComposer\_Tutorial. All pathnames and figures in this document refer to this pathname. If you choose to store the tutorial in another location, adjust the pathnames accordingly.

0

**TIP:** Make sure to save the tutorial files in a folder structure with no spaces in them. There is a known limitation that does not support spaces in the directory structure for code generation.

# Lab 1: Introduction to Model Composer

### Introduction

This tutorial shows how you can use Model Composer for rapid algorithm design and simulation in the Simulink® environment.

### Procedure

This lab has the following steps:

- In Step 1, you examine the Model Composer Simulink library.

- In Step 2, you build a simple design using Model Composer blocks to see how Model Composer blocks integrate with native Simulink blocks and supported Signal Dimensions.

- In Step 3, you look at data types supported by Model Composer and the conversion between data types.

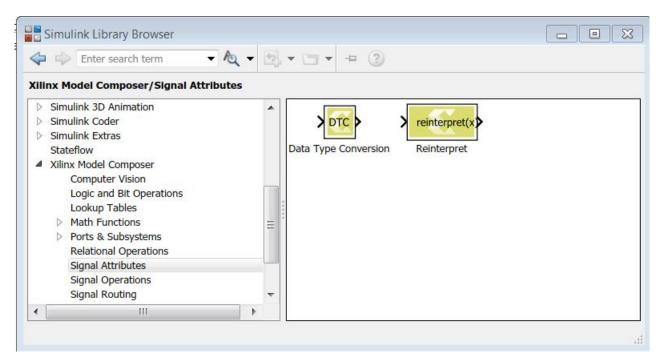

### **Step 1: Review the Model Composer Library**

In this step you see how Model Composer fits into the Simulink environment, and then review the categories of blocks available in the Model Composer library.

### Access Model Composer Library

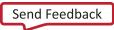

Model Composer provides 80+ blocks for use within the Simulink environment that you can access them from within the Simulink Library Browser:

- 1. Use any of these techniques to open the Simulink Library Browser:

- a. On the Home tab, click Simulink, and choose a model template. In the new model, click the Library Browser button.

b. At the command prompt, type:

slLibraryBrowser

2. In the browser, navigate to the **Xilinx Model Composer** library.

Figure 1: Xilinx Model Composer Library

The Model Composer blocks are organized into subcategories based on functionality. Spend a few minutes navigating through the sub-libraries and familiarizing yourself with the available blocks.

# **Step 2: Build Designs with Model Composer Blocks**

In this step, you build a simple design using the existing Model Composer blocks.

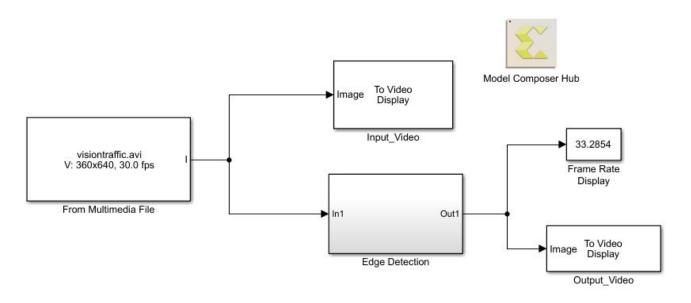

### Sobel Edge Detection: Algorithm Overview

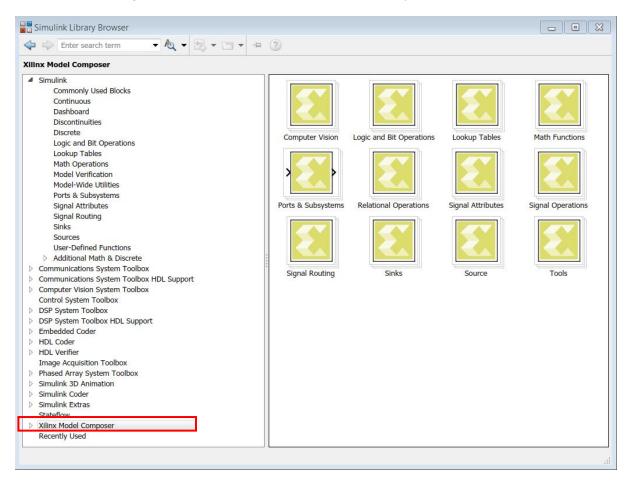

Sobel edge detection is a classical algorithm in the field of image and video processing for the extraction of object edges. Edge detection using Sobel operators works on the premise of computing an estimate of the first derivative of an image to extract edge information.

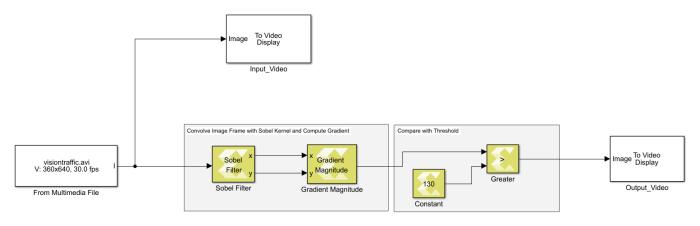

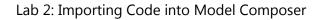

Figure 2: Sobel Edge Detection

### Implementing Algorithm in Model Composer

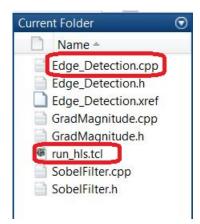

- 1. In the MATLAB Current Folder, navigate to ModelComposer\_Tutorial\Lab1\Section1.

- 2. Double-click the Sobel\_EdgeDetection\_start.slx model.

This model already contains source and sink blocks (from Simulink's **Computer Vision System Toolbox**), to stream video files as input directly into your algorithm and view the results. The model also contains some of the needed Model Composer blocks required for this section. Note the difference in appearance for the Model Composer blocks in the design versus the Simulink blocks.

3. From the Library Browser, select the **Sobel Filter** block from the **Computer Vision** sub-library of the Xilinx Model Composer library. Drag the block into the area labeled **Convolve Image Frame with Sobel Kernel and Compute Gradient** as shown in Figure 4 and connect the input of this block to the output of the **From Multimedia File** block.

**Note:** You can also add Model Composer blocks directly into your model by typing the block name onto the canvas (same as Simulink blocks).

Figure 3: Searching for Sobel Filter Block

- 4. From the Library Browser, select the **Gradient Magnitude** block from the Xilinx Model Composer library (also found in the **Computer Vision** sub-library), drag it into the model, and connect the X and Y outputs of the **Sobel Filter** block to the input of this block.

- 5. Connect the rest of the blocks to complete the algorithm as shown in the following figure:

Figure 4: Algorithm with Sobel Filter and Gradient Magnitude

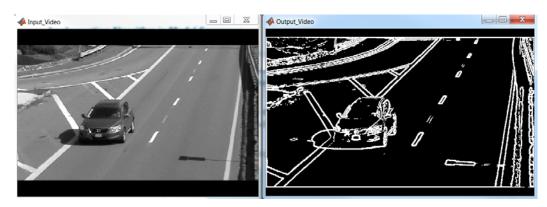

6. Select the **Simulation > Run** command or click the 🕑 button to simulate the model and view the results of the Sobel Edge Detection algorithm.

Note: The Model Composer blocks can operate on matrices (image frames in the following figure).

Figure 5: Input and Output Videos

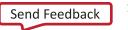

One way to assess the simulation performance of the algorithm is to check the video frame rate of the simulation. To do this:

- 7. Add the **Frame Rate Display** block from the Simulink **Computer Vision System Toolbox** (under the **Sinks** category) and connect it to the output of the algorithm as shown in Figure 6.

- 8. Simulate the model again to see the number of video frames processed per second.

Figure 6: Frames Processed Per Second

- 9. Try these things:

- Change the input video through the **From Multimedia File** block by double-clicking the block and changing the **File Name** field to select a different video. Notice that changing the video resolution in the Source block does not require any structural modifications to the algorithm itself.

**Note:** You must stop simulation before you can change the input file. Also, the .mp4 files in the MATLAB vision data tool box directory are not supported.

• Build any variations using other available blocks in the **Computer Vision** sub-library in Model Composer.

**Note:** You can find other smaller examples for reference in the folder ModelComposer\_Tutorial\Lab1\Section1\Examples

### Step 3: Work with Data Types

In this step, you become familiar with the supported Data Types for Model Composer and conversion from floating to fixed-point types.

This exercise has two primary parts, and one optional part:

- Review a simple floating-point algorithm using Model Composer.

- Look at Data Type Conversions in Model Composer designs.

### Work with Native Simulink Data Types

- 1. In the MATLAB Current Folder, navigate to the ModelComposer\_Tutorial\Lab1\Section2 folder.

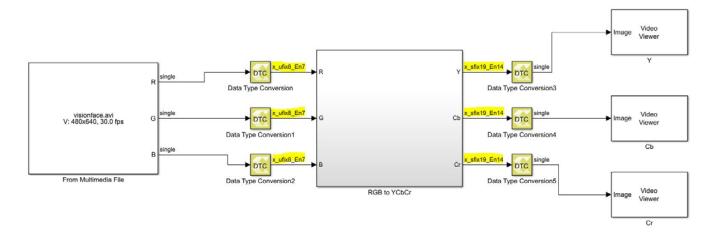

- 2. Double-click ColorSpace\_Conversion.slx to open the design.

This is a Color Space conversion design, built with basic Model Composer blocks, that performs a RGB to YCbCr conversion.

- 3. Update the model (**Ctrl+D**) and observe that the Data Types, Signal Dimensions and Sample Times from the Source blocks in Simulink all propagate through the Model Composer blocks. Note that the design uses single precision floating point data types.

- 4. Simulate the model and observe the results from simulation.

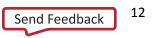

### **Convert Data Types**

To convert the previous design to use Xilinx Fixed Point types:

**Note:** Fixed point representation helps to achieve optimal resource usage and performance for a usually acceptable trade-off in precision, depending on the dataset/algorithm.

- 1. Double-click ColorSpace\_Conversion\_fixed\_start.slx in the Current Folder to open the design.

- 2. Open the Xilinx Model Composer library in the Simulink Library Browser.

- 3. Navigate to the Signal Attributes sub-library, select the **Data Type Conversion** block, and drag it into the empty slots in the designs, before and after the **RGB to YCbCr** subsystem.

#### Figure 7: Model Composer Data Type Conversion Block

Figure 8: RGB to YCbCr Subsystem with DTC Blocks Connected

- 4. Open the **Data Type Conversion** blocks at the inputs of the **RGB to YCbCr** Subsystem, and do the following:

- Change the **Output data type** parameter to **fixed**.

- Set the **Signedness** to **Unsigned**.

- Set the Word length to 8.

- Set Fractional length to 7.

- Click **Apply**, and close the dialog box.

| 🖹 Block Parameters: Data Type Conversion                                                                                                                                                                                                                                       |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data Type Conversion                                                                                                                                                                                                                                                           |  |  |  |  |

| Converts the input value into the user selected data type.<br>This block warns or errors out when an integer output overflows during simulation. To<br>configure, in the Configuration Parameters > Diagnostics > Data Validity pane, set the<br>Wrap or Saturate on overflow. |  |  |  |  |

| Parameters                                                                                                                                                                                                                                                                     |  |  |  |  |

| Output data type: fixed                                                                                                                                                                                                                                                        |  |  |  |  |

| Output Type Attributes                                                                                                                                                                                                                                                         |  |  |  |  |

| Signedness: Unsigned                                                                                                                                                                                                                                                           |  |  |  |  |

| Word length: 8 Eractional length: 7                                                                                                                                                                                                                                            |  |  |  |  |

| Input Conversion Attributes                                                                                                                                                                                                                                                    |  |  |  |  |

| Round: Truncation to minus infinity                                                                                                                                                                                                                                            |  |  |  |  |

| Overflow: Wrap around                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                                                                                                                                                                                                                |  |  |  |  |

| OK Cancel Help Apply                                                                                                                                                                                                                                                           |  |  |  |  |

Figure 9: Data Type Conversion Block Parameters

Add the Data Type Conversion blocks at the output of the RGB to YCbCr Subsystem and set the Output data type parameter to single. This will enable connecting the output signals to the Video Viewer blocks for visualization.

| 📲 Block Parameters: Data Type Conversion                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Type Conversion                                                                                                                                                                                                                                                           |

| Converts the input value into the user selected data type.<br>This block warns or errors out when an integer output overflows during<br>simulation. To configure, in the Configuration Parameters > Diagnostics > Data<br>Validity pane, set the Wrap or Saturate on overflow. |

| Parameters                                                                                                                                                                                                                                                                     |

| Output data type: single                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                |

| OK Cancel Help Apply                                                                                                                                                                                                                                                           |

Figure 10: Setting Output Data Type

6. Double-click the **RGB to YCbCr** subsystem to descend the hierarchy and open the model. Within the **RGB to YCbCr** subsystem, there are subsystems to calculate Y, Cb, and Cr components using Gain and Constant blocks.

You can control the fixed point types for the gain parameter in the **Gain** blocks and the value in the **Constant** blocks. You can do this by opening up the **Calculate\_Y**, **Calculate\_Cb**, and **Calculate\_Cr** blocks and setting the data types as follows.

For **Gain** blocks, set the **Gain data type** to **fixed** and the following options appear:

- Signedness to Signed

- Gain data type to fixed

- Word length to 8

- Fractional length to 7

For **Constant** blocks, on the **Data Types** tab set the **Output data type** to **fixed** and the following options appear:

- Signedness to Signed

- Output data type to fixed

- o Word Length to 8

- Fractional Length to 7

**TIP:** You can use the **View > Property Inspector** command to open the Property Inspector window. When you select the different Gain or Constant blocks, you can see and modify the properties on the selected block.

Make sure you do this for all the Constant and Gain blocks in the design. Update the model (**Ctrl+D**) and observe the fixed point data types being propagated along with automatic bit growth in gain blocks and adder trees in the design as shown below:

#### Figure 11: Propagated Xilinx Fixed-Point Data Types

The general format used to display the Xilinx fixed point data types is as follows:

#### x\_[u/s]fix[wl]\_En[fl]

u: Unsigned

s: Signed

wl: Word Length

fl: Fractional Length

For example, **x\_sfix16\_En8** represents a signed fixed point number with Word Length=16 and Fractional Length=8.

You can view a completed version of the design here:

```

ModelComposer_Tutorial\Lab1\Section2\solution\Colorspace_Conversion_fixed .slx

```

### Convert Data Types (Alternative)

Model Composer supports Data Type Expressions that make it easier to change data types and quickly explore the results from your design.

- 1. Double-click ColorSpace\_Conversion\_Expression.slx in the Current Folder to open the design.

- Notice that the Data Type Conversion blocks at the Input of the RGB to YCbCr Subsystem, the Gain blocks and Constant blocks within the Subsystem have corresponding Output data type and Gain data type set to data type expression.

#### Lab 1: Introduction to Model Composer

| 🚹 Block Parameters: Data Type Conversion                                                                                                                                                                                                                                          | Block Parameters: Gain                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Type Conversion                                                                                                                                                                                                                                                              | Gain                                                                                                                                                                                                                                              |

| Converts the input value into the user selected data type.<br>This block warns or errors out when an integer output overflows<br>during simulation. To configure, in the Configuration Parameters ><br>Diagnostics > Data Validity pane, set the Wrap or Saturate on<br>overflow. | Applies gain to the input.<br>This block warns or errors out when an integer output overflows<br>during simulation. To configure, in the Configuration Parameters<br>> Diagnostics > Data Validity pane, set the Wrap or Saturate on<br>overflow. |

| Parameters                                                                                                                                                                                                                                                                        | Parameters                                                                                                                                                                                                                                        |

| Output data type: data type expression                                                                                                                                                                                                                                            | Gain:                                                                                                                                                                                                                                             |

| InputDataType :                                                                                                                                                                                                                                                                   | 65.738/256                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                   | Gain data type: data type expression -                                                                                                                                                                                                            |

| Saturate on integer overflow                                                                                                                                                                                                                                                      | FDataType                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                   | Output data type same as input                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                   | Saturate on Integer Overflow                                                                                                                                                                                                                      |

| OK Cancel Help Apply                                                                                                                                                                                                                                                              | OK Cancel Help Apply                                                                                                                                                                                                                              |

Figure 12: Controlling Data Types with Workspace Variables

This enables Model Composer blocks to control the data types in the design using workspace variables, in this case InputDataType and FDataType that you can easily change from the MATLAB command prompt.

3. Update the model (**Ctrl+D**) and observe the fixed-point data types propagated through the blocks.

The other Model Composer blocks in the design will automatically take care of the bit-growth in the design. If you want more control over the fixed point data types at other intermediate portions of the design, you can insert **Data Type Conversion** blocks wherever necessary.

4. To change the fixed point types in the **Gain** and **Constant** blocks, type the following at the MATLAB command prompt:

```

>> FDataType = 'x_sfix8_En6'

>> InputDataType = 'x_ufix8_En6'

```

'x\_sfix8\_En6' represents a signed fixed point number with Word Length 8 and Fractional Length 6.

Now update the model (**Ctrl+D**) and observe how the fixed-point data types have changed in the design.

5. Simulate the model and observe the results from the design. Try further changing InpuDataType and FDataType variables through command line and iterate through multiple word lengths and fractional lengths. See the Additional Details section below for information on specifying rounding and overflow modes.

#### Additional Details:

In the example above, we only specified the Word Length and Fractional Length of the fixed point data types using data type expressions. However, for greater control over the fixed point types in your

www.xilinx.com

17

design, you can also specify the Signedness, Rounding, and Overflow. In general the format used for specifying fixed point data types using the data type expression is

#### x\_[u/s]fix[wl]\_En[fl]\_[r<round>w<overflow>]

- u: Unsigned

- s: Signed

- wl: word length

- fl: Fractional length

<**round>:** Specify the corresponding <u>index</u> from table below. It's optional. If not specified, default value is 6 (Truncation to minus infinity). Note that for the rounding cases (1 to 5), the data is rounded to the nearest value that can be represented in the format. When there is a need for tie breaker, these particular roundings behave as specified in the **Meaning** column.

| Index | Meaning                      |

|-------|------------------------------|

| 1     | Round to Plus Infinity       |

| 2     | Round to Zero                |

| 3     | Round to Minus Infinity      |

| 4     | Round to Infinity            |

| 5     | Convergent Rounding          |

| 6     | Truncation to Minus Infinity |

| 7     | Truncation to Zero           |

<**overflow>:** Specify the corresponding <u>index</u> from table below. It's optional. If not specified, default value is 4 (Wrap around)

| Index Meaning |                            |

|---------------|----------------------------|

| 1             | Saturation                 |

| 2             | Saturation to Zero         |

| 3             | Symmetrical Saturation     |

| 4             | Wrap Around                |

| 5             | Sign-Magnitude Wrap Around |

Example. x\_ufix8\_En6\_r6w4 represents a fixed point data type with

Signedness: Unsigned

Word Length: 8

Fractional Length: 6

Rounding Mode: Truncation to Minus Infinity

Overflow Mode: Wrap Around

# Conclusion

In this lab, you learned:

- How to connect Model Composer blocks directly to native Simulink blocks.

- How the Model Composer blocks *support Vectors and Matrices*, allowing you to process an entire frame of an image at a time without converting it from a frame to a stream of pixels at the input.

- How to work with different data types.

- How to use the Data Type Conversion block to control the conversion between data types, including floating-point to fixed-point data types.

Note: Model Composer Supports the same floating and integer data types as Simulink blocks. Model Composer also supports Xilinx fixed point data types.

The following solution directories contain the final Model Composer files for this lab:

C:\ModelComposer\_Tutorial\Lab1\Section1\solution

$\verb|C:\ModelComposer_Tutorial\Lab1\Section2\solution|| \\$

### Lab 2: Importing Code into Model Composer

### Introduction

Model Composer lets you import Vivado HLS library functions and user C/C++ code as custom blocks to use in your algorithm for both simulation and code generation.

The Library Import feature is a MATLAB function, xmcImportFunction, which lets you specify the required source files and automatically creates an associated block that can be added into a model in Simulink.

This lab primarily have two parts

- In Step 1, you are introduced to the xmcImportFunction function, and walk through an example.

- In Step 2, you will learn about the Model Composer feature that enables you to create custom blocks with function templates

For more details and information about other Model Composer features, see the Model Composer User Guide (UG1262).

### **Step 1: Set up the Import Function Example**

In the MATLAB Current Folder panel, navigate to Lab2\Section1 folder.

7. Double-click the basic\_array.cpp and basic\_array.h files to view the source code in the MATLAB Editor.

These are the source files for a simple <code>basic\_array</code> function in C++, which calculates the sum of two arrays of size 4. You will import this function as a Model Composer block using the <code>xmcImportFunction</code> function.

The input and output ports for the generated block are determined by the signature of the source function. Model Composer identifies arguments specified with the const qualifier as inputs to the block, and all other arguments as outputs.

**Note:** For more details and other options for specifying the direction of the arguments, see the Model Composer User Guide (UG1262).

**IMPORTANT:** You can use the const qualifier in the function signature to identify the inputs to the block or use the pragma INPORT.

In the case of the basic\_array function, the in1 and in2 arguments are identified as inputs.

```

void basic_array(

uint8_t out1[4],

const uint8_t in1[4],

const uint8_t in2[4])

```

- 8. To learn how to use the xmcImportFunction function, type help xmcImportFunction at the MATLAB command prompt to view the help text and understand the function signature.

- 9. Open the import\_function.m MATLAB script, and fill in the required fields for the xmcImportFunction function in this way:

```

xmcImportFunction('basic_array_library', {'basic_array'}, 'basic_array.h',

{'basic_array.cpp'}, {});

```

The information is defined as follows:

- Library Name: basic\_array\_library. This is the name of the Simulink library that is created with the new block.

- **Function Names:** basic\_array. This is the name of the function that you want to import as a block.

- **Header File:** basic\_array.h. This is the header file for the function.

- **Source Files:** basic\_array.cpp. This is the source file for the imported function.

- **Search Paths**: This argument is used to specify the search path(s) for header files. In this example, there are no additional search paths to specify and hence you can leave it as { } which indicates none.

Note: Look at **create\_libary\_solution.m** in the **solution** folder for the completed version.

10. Run the import\_function.m script from the MATLAB command line:

>>run('import\_function.m')

Notice that a Simulink library model opens up with the generated block basic\_array.

Save this Simulink library model.

11. Double-click the **basic\_array** block, and look at the generated interface.

The following figure shows the Block Parameters dialog box for **basic\_array**:

| 눰 Block Par  | ameters: basio | _array         | ×           |

|--------------|----------------|----------------|-------------|

| Library Fun  | ction          |                |             |

| Function de  | claration      |                |             |

| void basic a | arrav(uint8    | t out1[4], cor | ost uint8 t |

|              | t uint8_t in2  |                | ist unito_t |

| Function     | General        |                |             |

| - Interfaces | General        |                |             |

| Direction    | Name           | Turno          | Dimension   |

| Direction    | Name           | Туре           | Dimension   |

| Output       | out1           | uint8_t        | 4           |

| Input        | in1            | uint8_t        | 4           |

| Input        | in2            | uint8_t        | 4           |

|              |                |                |             |

|              |                |                |             |

|              |                |                |             |

|              |                |                |             |

|              |                |                |             |

|              |                |                |             |

|              |                |                |             |

| OK           | Cancel         | Holp           | Apply       |

| UK           | Cancel         | Help           | Apply       |

Figure 13: Block Parameters: basic\_array Block

- 12. Open the test\_array.slx model, which is just a skeleton to test the generated block.

- 13. Add the generated **basic\_array** block into this model, then connect the source and sink blocks.

- 14. Simulate this model and observe the results in the display block.

### **Step 2: Custom Blocks with Function Templates**

In this step we will walk through an example to do the following:

- To create a custom block that supports inputs of different sizes.

- To create a custom block that accepts signals with different fixed-point lengths and fractional lengths.

- To perform simple arithmetic operations using template variables.

- 1. Navigate to the Lab2/section2 folder

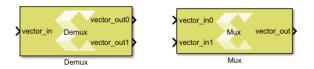

- 2. Double click the template\_design.h file to view the source code in the MATLAB Editor. There are two functions: Demux and Mux. These two functions are a multiplexing and demultiplexing of inputs as shown below.

#### Figure 14: Demux Function

3. In the piece of code, note the #pragma XMC INPORT vector\_in. This is a way to manually specify port directions using pragmas. Here, we are specifying the function argument vector\_in as the InputPort. Similarly, we can define XMC OUTPORT also.

**Note:** For additional information about specifying ports, see Importing C/C++ Code as Custom Blocks in the Model Composer User Guide (UG1262).

4. Notice the use of template before the function declaration. To support the inputs of different sizes, NUMOFELEMENTS is declared as a parameter and used the same while defining an array vector\_in as shown below. This allows you to connect signals of different sizes to the input port of the block.

```

template<int NUMOFELEMENTS, int W, int I>

void Demux(ap_fixed<W,I> vector_in[NUMOFELEMENTS], ap_fixed<W,I> vector_out0[NUMOFELEMENTS/2],

ap_fixed<W,I> vector_out1[NUMOFELEMENTS/2]) {

```

5. Notice the template parameters W and I which are declared to accept signals with different word lengths and integer lengths.

Note: The same library is specified for both the functions.

6. Observe the arithmetic operations performed using template variables as shown below, indicating the output signal length is half of the input signal length.

7. Similar explanation follows for Mux function.

#### **Figure 15: Mux Function**

Now create the library blocks for Mux and Demux functions using the xmcImportFunction command and complete the design below with custom blocks.

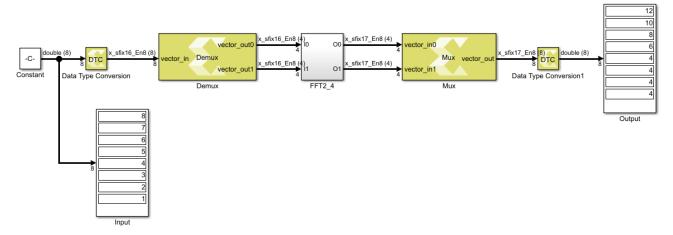

#### Figure 16: Initial Design

8. Double-click the import\_function.m script file in the MATLAB command window and observe the following commands that generate library blocks to embed into your actual design.

```

>>xmcImportFunction('design_lib',{'Demux'},'template_design.h',{},{'$XILINX_VIVADO_

HLS/include'},'ov erride','unlock')

>>xmcImportFunction('design_lib',{'Mux'},'template_design.h',{},{'$XILINX_VIVADO_HL

S/include'},'over ide','unlock')

```

9. Run the import\_function.m script from the MATLAB command line:

>>run('import\_function.m')

10. Observe the generated library blocks in the design\_lib.slx library model file and save it to working directory.

Figure 17: Generated Library blocks

11. Copy the Demux and Mux blocks and paste them in the design.slx file and connect them as shown below.

#### Figure 18: Completed Design

- 12. Note the following after embedding the custom blocks:

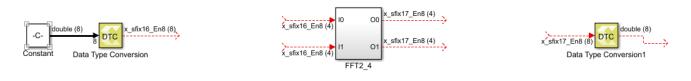

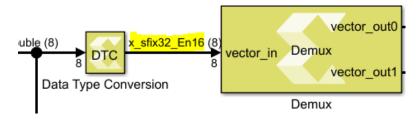

- a. Double-click the Constant block and observe the vector input of type double. SSR is a workspace variable, initially set to **8** from the **initFcn** model callback.

- b. Using the Data Type Conversion (DTC) block, double type is converted to fixed type with 16bit word length and 8-bit fractional length.

Input is configurable to any word length since the design is templatized.

c. Double-click the Demux block and observe the **Template parameters** section and **Dimension** column in the Interface section of the function tab.

| Block Para                                                                                                                                                                      | imeters: Demux                                                                            |                               | ×                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------|----------------------|

| Library Fund                                                                                                                                                                    | ction                                                                                     |                               |                      |

| Function de                                                                                                                                                                     | claration                                                                                 |                               |                      |

| Demux(ap_fixed <w< td=""><td>t NUMOFELEMEN<br/>fixed<w, i=""> vector<br/>/, I&gt; vector_out0[<br/>ut1[NUMOFELEME</w,></td><td>r_in[NUMOFELE<br/>NUMOFELEMEN</td><td></td></w<> | t NUMOFELEMEN<br>fixed <w, i=""> vector<br/>/, I&gt; vector_out0[<br/>ut1[NUMOFELEME</w,> | r_in[NUMOFELE<br>NUMOFELEMEN  |                      |

| Function                                                                                                                                                                        | General                                                                                   |                               |                      |

| Template p                                                                                                                                                                      | arameters                                                                                 |                               |                      |

| Name                                                                                                                                                                            |                                                                                           | Туре                          |                      |

|                                                                                                                                                                                 |                                                                                           |                               |                      |

| NUMOFELE                                                                                                                                                                        | MENTS                                                                                     | int                           |                      |

| w                                                                                                                                                                               |                                                                                           | int                           |                      |

| I                                                                                                                                                                               |                                                                                           | int                           |                      |

| Interfaces                                                                                                                                                                      |                                                                                           |                               |                      |

| Direction                                                                                                                                                                       | Name                                                                                      | Туре                          | Dimension            |

| Input                                                                                                                                                                           | vector_in                                                                                 | ap_fixed <w,<br>I&gt;</w,<br> | NUMOFELEMENTS        |

| Output                                                                                                                                                                          | vector_out0                                                                               | ap_fixed <w,<br>I&gt;</w,<br> | NUMOFELEMENTS        |

| Output                                                                                                                                                                          | vector_out1                                                                               | ap_fixed <w,<br>I&gt;</w,<br> | NUMOFELEMENTS<br>/ 2 |

|                                                                                                                                                                                 | OK                                                                                        | Cancel                        | Help Apply           |

Figure 19: Library Function Block Parameters

- d. Next, double-click the Mux block and observe the **Template parameters** and **Dimension**.

- 13. Add a Display block at the input and output as shown below and simulate the model to observe the results.

#### Figure 20: Output after Simulation

- 14. To understand how templatized inputs add advantage and flexibility to your design, perform the following:

- a. Double-click the DTC block.

- b. In the Block Parameters dialog box, change the **Word length** from 16 to 32.

- c. Change the **Fractional length** from 8 to 16.

| 🚡 Block Paramet                      | ers: Data Type Conversion                                                                                 |             |                |      | $\times$ |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------|----------------|------|----------|

| Data Type Conv                       | /ersion                                                                                                   |             |                |      |          |

| This block warn                      | out value into the user sel<br>s or errors out when an in<br>e Configuration Parameter<br>te on overflow. | nteger outp | ut overflows d |      |          |

| Parameters                           |                                                                                                           |             |                |      |          |

| Output data typ                      | e: fixed                                                                                                  |             |                |      | •        |

| Output Type A                        | ttributes                                                                                                 |             |                |      |          |

| Signedness: S                        | ligned                                                                                                    |             |                |      | •        |

| Word length:                         | 32                                                                                                        | : Fractio   | nal length: 1  | 6    | :        |

| Input Convers<br>Round:<br>Overflow: | ion Attributes<br>Truncation to minus infin<br>Wrap around                                                | ity         |                |      | •        |

|                                      |                                                                                                           | ОК          | Cancel         | Help | Apply    |

Figure 21: DTC Block Parameters

d. Click **OK** and press Ctrl+D. Observe the signal dimensions in the design.

Figure 22: Signal Dimensions in Design

To make sure the output is correct, run the simulation and observe that the same block can still be used in a generic way for different values of Word length and Fractional length. This is possible only because we have templatized the W and I values in our C design.

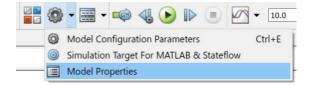

- 15. For an additional understanding of template parameters, perform the following:

- a. Click the arrow mark beside the **Model configuration Parameters** icon and select the **Model Properties** option.

b. In the Model Properties window, go to the Callbacks tab and select **initFcn** and edit the **SSR** value from **8** to **16** as shown below.

| 🚹 Model Properties: des                                                                                                                             | sign    |                      |          | ×       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|----------|---------|

| Main Callbacks                                                                                                                                      | History | Description          | Data     |         |

| Model callbacks<br>PreLoadFcn<br>PostLoadFcn<br>InitFcn*<br>StartFcn<br>PauseFcn<br>ContinueFcn<br>StopFcn<br>PreSaveFcn<br>PostSaveFcn<br>CloseFcn |         | el initialization fi | unction: |         |

|                                                                                                                                                     |         | OK Can               | cel Hel  | p Apply |

Figure 23: Model Properties

c. Click **OK** and press Ctrl+D to observe the change in the number of elements in the Constant block output vector. The bitwidth changes when we change the datatype on the input DTC. This is possible only because of the template parameter NUMOFELEMENTS.

d. Run the simulation and validate the output according to the input values.

**Note:** For information about features such as function templates for data types and pragmas to specify which data type a template variable supports, see Defining Blocks Using Function Templates in the Model Composer User Guide (UG1262).

## Conclusion

In this lab, you learned:

- How to create a custom block using the xmcImportFunction in Model Composer.

- How to create a block that accepts signals with different fixed-point lengths and fractional lengths.

- How to use the syntax for using a function template that lets you create a block that accepts a variable signal size or data dimensions.

- How to perform simple arithmetic operations using template variables.

Note: Current feature support enables you to import code that uses:

- Vectors and 2D matrices

- o Floating, integer, and Vivado HLS fixed-point data types

The following solution directory contains the final Model Composer (\*.slx) files for this lab.

$\verb|C:\ModelComposer_Tutorial\Lab2\section1\solution|| \\$

$\verb|C:\ModelComposer_Tutorial\Lab2\section2\solution|| \\$

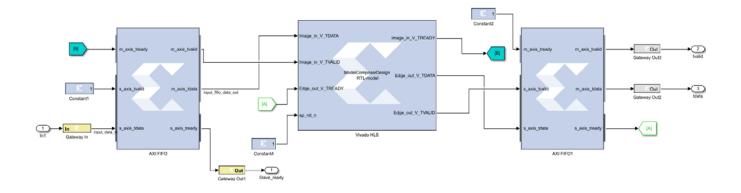

# Lab 3: Automatic Code Generation

### Introduction

In this lab, you look at the flow for generating output from your Model Composer model and moving it into downstream tools like Vivado HLS for RTL synthesis, or into System Generator, or the Vivado Design Suite for implementation into a Xilinx device.

### Procedure

This lab has five steps:

In Step 1, you will review the requirements for automatic code generation.

In Step 2, you will look at how to map Interfaces in your design.

In Step 3, you will look at the flow for generating an IP from your Model Composer design.

In Step 4, you will look at the flow for generating HLS Synthesizable C++ code from the Model Composer design.

In Step 5, you will look at the flow to port a Model Composer design back into System Generator for DSP as a block.

### **Step 1: Review Requirements for Generating Code**

In this step, you review the three requirements to move from your algorithm in Simulink to an implementation through automatic code generation.

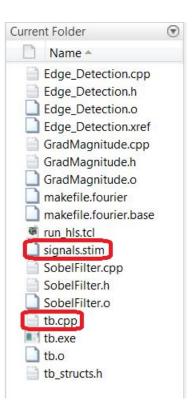

- 1. In the MATLAB Current Folder, navigate to the ModelComposer\_Tutorial\Lab3 directory.

- 2. Double-click **CodeGen\_start.slx** to open the model.

To prepare for code generation, you will enclose your Model Composer design in a subsystem.

3. Right-click the Edge Detection area, and select Create Subsystem from Area.

Note: For code generation to work, all the blocks within the enclosed subsystem should only be from the Xilinx Model Composer library, with the exception of the Simulink blocks noted below. Subsystems with unsupported blocks will generate errors during code generation. The Simulink diagnostic viewer will contain error messages and links to the unsupported blocks in the subsystem.

**Note:** In addition to the base Model Composer blocks, a subset of native Simulink blocks such as From, Goto, Bus Creator, Bus Selector, If, and others, are supported. The supported Simulink blocks appear within the Xilinx Model Composer libraries as well.

Next, you add the **Model Composer Hub** block at the top level of your design.

- 4. Open the Simulink Library Browser and navigate to Xilinx Model Composer Tools sub-library.

- 5. Find the Model Composer Hub block, and add it into the design as shown in the following figure:

#### Figure 24: Edge Detection with Model Composer Hub Block

Next, you use the Model Composer Hub block to select the code generation options for the design.

6. Double-click the block to open the block interface and set up as shown in the following figure:

| 🚹 Block Parameters: Model Composer Hub 🛛 🕹 🗙 |                 |                |              |               |

|----------------------------------------------|-----------------|----------------|--------------|---------------|

| Model Compo                                  | ser Hub         |                |              |               |

| Controls imple                               | ementation of t | he model.      |              |               |

| Compilation                                  | Hardware        | Feedback       |              |               |

| Target directo                               | ry:             |                |              |               |

| ./codegen_ed                                 | ge_detection    |                |              | Browse        |

| Subsystem na                                 | me:             |                |              |               |

| Edge Detection                               | n               |                |              |               |

| Export type:                                 | IP Catalog      |                |              | •             |

| Create and                                   | execute testbe  | nch            |              |               |

|                                              |                 |                |              | Generate      |

|                                              |                 |                |              |               |

|                                              | <u>О</u> К      | <u>C</u> ancel | <u>H</u> elp | <u>A</u> pply |

Figure 25: Block Parameters Dialog Box

- 7. On the Compilation tab, you can set the following options as shown in above figure:

- **Target directory:** In this case, use ./codegen\_edge\_detection for the generating code.

- **Subsystem name:** In this case, use the **Edge Detection** subsystem. You can have multiple subsystems at the top-level and use the **Model Composer Hub** block to select and individually compile the subsystem you want.

- **Export Type:** This option determines what you want to convert your design into. In this case **IP Catalog** (*default*). You can select other compilation targets from drop down.

- Vivado HLS Synthesizable C++ code

- o System Generator for DSP

- 8. On the Hardware tab, you can specify the target **FPGA clock frequency in** MHz. The default value is 200MHz..

### **Step 2: Mapping Interfaces**

1. Double-click the CodeGen\_Interface.slx model in your Current Folder to open the design for this lab section.

Model-Based Design Using Model Composer UG1259 (v2018.3) December 5, 2018 www.xilinx.com

32

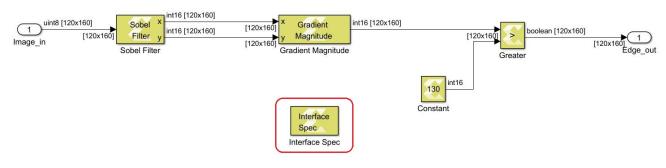

This is a slightly modified version of the Edge Detection algorithm that uses the YCbCr video format at the input and output.

- 2. Simulate the model to see the results in the **Video Viewer** blocks.

- Open the Simulink Library browser, navigate to the Xilinx Model Composer > Tools sub-library and add the Interface Spec block inside the Edge Detection subsystem as shown in the following figure:

Figure 26: Interface Spec Block

4. Double-click the Interface Spec block to open the block interface.

The **Interface Spec** block allows you to control what RTL interfaces should be synthesized for the ports of the subsystem in which the block is instantiated. This affects only code generation; it has no effect on Simulink simulation of your design.

The information gathered by the Interface Spec block consists of three parts (represented as three Tabs on the block):

| Block Parameters: Interface Spec |                   | X                    |

|----------------------------------|-------------------|----------------------|

| Interface Spec                   |                   |                      |

| Specifies the RTL interfaces for | a sub system.     |                      |

| Parameter and Port Properties    |                   |                      |

| Function Protocol Input po       | orts Output ports |                      |

| Mode: AXI4-Lite                  | - Bundle:         | Offset:              |

|                                  |                   |                      |

|                                  |                   |                      |

|                                  |                   |                      |

|                                  |                   |                      |

|                                  |                   | OK Cancel Help Apply |

Figure 27: Interface Spec Block Parameter

- **Function Protocol**: This is the block-level Interface Protocol which tells the IP when to start processing data. It is also used by the IP to indicate whether it accepts new data, or whether it has completed an operation, or whether it is idle.

- **Input Ports:** Detects the Input ports in your subsystem automatically and allows specifying the port-level Interface Protocol for each input port of the subsystem.

- **Output Ports:** Similar to the Input Ports tab, this tab detects the Output ports in the subsystem, and allows specifying the port-level Interface Protocol for each output port of the subsystem.

- 5. For this design, leave the **Function Protocol** mode at the default **AXI4-Lite** and configure the Input ports and Output ports tabs as shown in the following figures:

| Block Parameters: Inte | erface Spec       |                    |        | X                            |

|------------------------|-------------------|--------------------|--------|------------------------------|

| Interface Spec         |                   |                    |        |                              |

| Specifies the RTL inte | erfaces for a sub | system.            |        |                              |

| Parameter and Port F   | Properties        |                    |        |                              |

| Function Protocol      | Input ports       | Output ports       |        |                              |

| Name                   | Mode              | Bundle             | Offset | Video Format Video Component |

| Υ                      | AXI4-Stream       | image_in           |        | YUV 4:2:2 • Y •              |

| Cb                     | AXI4-Stream       | (video) 🔻 image_in |        | YUV 4:2:2 • U •              |

| Cr                     | AXI4-Stream       | (video) 🔻 image_in |        | YUV 4:2:2 • V •              |

|                        |                   |                    |        |                              |

|                        |                   |                    | ОК     | Cancel Help Apply            |

Figure 28: Input Port Settings

| 🚹 Block Parameters: Interface Spec |                 |                  | $\times$ |

|------------------------------------|-----------------|------------------|----------|

| Interface Spec                     |                 |                  |          |

| Specifies the RTL interfaces for a | subsystem.      |                  |          |

| Parameter and Port Properties      |                 |                  |          |

| Function Protocol Input po         | ts Output ports |                  |          |

| Mode: AXI4-Lite Slave              |                 | Offset:          |          |

|                                    |                 |                  |          |

|                                    |                 |                  |          |

|                                    |                 |                  |          |

|                                    |                 |                  |          |

|                                    |                 |                  | Vanha    |

|                                    |                 | OK Cancel Help A | Apply    |

Figure 29: Output Port Settings

• The **Bundle** parameter is used in conjunction with the AXI4-Lite or AXI4-Stream (video) interfaces to indicate that multiple ports should be grouped into the same interface. It lets you bundle multiple input/output signals with the same specified bundle name into a single interface port and assigns the corresponding name to the RTL port.

For example in this case, the specified settings on the Input ports tab result in the YCbCr inputs being mapped to AXI4-Stream (video) interfaces and bundled together as an image\_in port in the generated IP while the YCbCr outputs are bundled together as an image\_out port.

- The Video Format drop-down menu lets you select between the following formats:

- o YUV 4:2:2

- o YUV 4:4:4

- **RGB**

- o Mono/Sensor

- The **Video Component** drop-down menu is used to subsequently select the right component: R,G,B,Y,U,V.

### **Step 3: Generate IP from Model Composer Design**

Using the same example, you will generate an IP from the Edge Detection algorithm.

- 1. Double-click the CodeGen\_IP.slx model in the Current Folder.

- 2. Double-click into the **Edge Detection** subsystem and review the settings on the **Interface Spec** block. Based on the previous lab, this block has already been set up to map the input and output ports to AXI4-Stream Video interface, and to use the YUV 4:2:2 video format.

- 3. Double-click the **Model Composer Hub** block, and set the following in the Block dialog box:

- Export Type: IP Catalog (default)

- Target Directory: codegen\_IP

- Subsystem name: Edge Detection

- 4. To generate an IP from this design, click the **Apply** button in the **Model Composer Hub** block dialog box to save the settings. Then click the **Generate** button to start the code generation process.

Model Composer opens a progress window to show you the status. After completion, click **OK** and you will see the new codegen\_IP folder in the current folder, which contains the generated IP solution folder.

| -                                                                                        |        | ×     |

|------------------------------------------------------------------------------------------|--------|-------|

| Generating RTL for module 'Edge_Detection'                                               |        |       |

|                                                                                          |        |       |

| [KIMG 210 205] IMPTEMENTING FIFO P SIC V V O(THO WO G2 A) USING SHITE REGISTERS.         |        |       |

| [RTMG 210-285] Implementing FIFO 'p_dstx_V_V_U(fifo_wl6_d2_A)' using Shift Registers.    |        | ~     |

| [RTMG 210-285] Implementing FIFO 'p dsty V V U(fifo w16 d2 A)' using Shift Registers.    |        |       |

| [RTMG 210-285] Implementing FIFO 'start for xFSobelfYi U(start for xFSobelfYi)' using Sh | nift F | legi: |

| [RTMG 210-285] Implementing FIFO 'start for Sobel Lg8j U(start for Sobel Lg8j)' using Sh |        | -     |

| [RTMG 210-285] Implementing FIFO 'start for Sobel U0 U(start for Sobel U0)' using Shift  |        | -     |

| [RTMG 210-285] Implementing FIFO 'start for XfMatTohbi U(start for XfMatTohbi)' using Sh | -      |       |

| [RTMG 210-285] Implementing FIFO 'start for XfMatToibs U(start for XfMatToibs)' using Sh |        | -     |

| [RTMG 210-285] Implementing FIFO 'p srcl V V U(fifo w16 d2 A x)' using Shift Registers.  |        | -     |

| [RTMG 210-285] Implementing FIFO 'p src2 V V U(fifo wl6 d2 A x)' using Shift Registers.  |        |       |

| [RTMG 210-285] Implementing FIFO 'p_dst_V_V_U(fifo_w16_d2_A_x)' using Shift Registers.   |        |       |

| [RTMG 210-285] Implementing FIFO 'start_for_magnitujbC_U(start_for_magnitujbC)' using Sh | nift B | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_magnitukbM_U(start_for_magnitukbM)' using Sh | nift B | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_XfMatTolbW_U(start_for_XfMatTolbW)' using Sh | nift B | (egi: |

| [RTMG 210-285] Implementing FIFO 'start_for_SobelFimb6_U(start_for_SobelFimb6)' using Sh | nift B | (egi: |

| [RTMG 210-285] Implementing FIFO 'start_for_Loop_3_ncg_U(start_for_Loop_3_ncg)' using Sh | nift F | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_Loop_4_ocq_U(start_for_Loop_4_ocq)' using Sh | nift F | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_GradMagpcA_U(start_for_GradMagpcA)' using Sh | nift R | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_Loop_1_qcK_U(start_for_Loop_1_qcK)' using Sh | nift P | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_Loop_2_rcU_U(start_for_Loop_2_rcU)' using Sh | nift P | legi: |

| [RTMG 210-285] Implementing FIFO 'start_for_writeStsc4_U(start_for_writeStsc4)' using Sh | nift P | legi: |

|                                                                                          |        | ~     |

| <                                                                                        |        | >     |

|                                                                                          | Ca     | incel |

#### Figure 30: Generation Progress

At the end of the IP generation process, Model Composer opens the **Performance Estimates** and **Utilization Estimates** (from Vivado HLS Synthesis report) in the MATLAB Editor, as shown in the following figures:

**Note:** The Performance and Utilization Numbers here may vary slightly depending on software release.

| == Performance                                           | Estimates                        | 3 |                   |                           |  |

|----------------------------------------------------------|----------------------------------|---|-------------------|---------------------------|--|

|                                                          |                                  |   |                   |                           |  |

| * Summary:                                               |                                  |   |                   |                           |  |

| ++-                                                      | +                                | + |                   | +                         |  |

| Clock  <br>++-                                           |                                  |   |                   |                           |  |

| ap clk                                                   |                                  |   |                   |                           |  |

|                                                          |                                  |   |                   |                           |  |

| ++-                                                      | +                                | + |                   |                           |  |

| + Latency (cloc<br>* Summary:                            | ck cycles)                       | : |                   | +                         |  |

| + Latency (cloc<br>* Summary:<br>++-                     | ck cycles)                       | : |                   | ·+                        |  |

| + Latency (cloc<br>* Summary:<br>++-<br>  Later<br>  min | ck cycles)<br>+-<br>ncy  <br>max | : | +<br>val  <br>max | +<br><br>Pipeline<br>Type |  |

Figure 31: Performance Estimates

| * Summary:  |                                       |         |      |           |  |  |  |

|-------------|---------------------------------------|---------|------|-----------|--|--|--|

|             | ++                                    | +       | +-   | +         |  |  |  |

| Name        | BRAM_18K                              |         |      |           |  |  |  |

| +<br>  DSP  | ++                                    | -+      | -+   | +         |  |  |  |

| Expression  |                                       | -1      | 01   | 12        |  |  |  |

| FIFO        | i 0i                                  | -1      | 01   | 10        |  |  |  |

| Instance    | 12                                    | -       | 2562 | 2994      |  |  |  |

| Memory      |                                       | -       | -    | -         |  |  |  |

| Multiplexer | - 1                                   | -       | -    | -         |  |  |  |

| Register    | -1                                    | -1      | -1   | -         |  |  |  |

| +           |                                       |         |      |           |  |  |  |

| Total       | 12                                    | 0       | 2562 | 3016      |  |  |  |

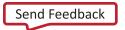

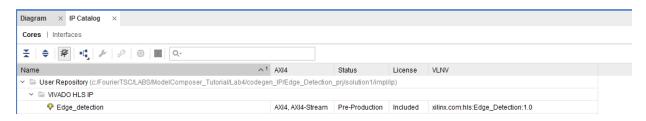

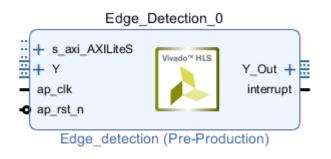

| +           | ++                                    | +-      | +-   | +         |  |  |  |