# Modeling Embedded Systems Using SysML

A thesis Presented to The Electrical and Electronic Department

by

# Carlos Ernesto Gómez Cárdenas

Advisors: Philippe Esteban Jean-Claude Pascal José Fernando Jimenez

In Partial Fulfillment of the Requirements for the Degree Master in Electronic Engineering and Computers

> Electrical and Electronic Department Universidad de Los Andes July 2009

# Modeling Embedded Systems Using SysML

Approved by:

Philippe Esteban Jean-Claude Pascal José Fernando Jimenez, Advisors

Date Approved \_\_\_\_\_

# Table of Contents

| List | t of [                                  | Tables                                                          | vi |  |

|------|-----------------------------------------|-----------------------------------------------------------------|----|--|

| List | List of Figures                         |                                                                 |    |  |

| Ι    | Intr                                    | oduction                                                        | 1  |  |

| II   | Met                                     | hods                                                            | 3  |  |

|      | 2.1                                     | Definition                                                      | 3  |  |

|      | 2.2                                     | Evolution in the embedded system design methods                 | 3  |  |

|      | 2.3                                     | Platform-Based Design                                           | 6  |  |

|      | 2.4                                     | MCSE Method                                                     | 9  |  |

|      | 2.5                                     | Model-Based System Design                                       | 11 |  |

|      | 2.6                                     | HiLeS Method                                                    | 13 |  |

|      | 2.7                                     | Model Driven Architecture                                       | 14 |  |

|      | 2.8                                     | Conclusion                                                      | 16 |  |

| III  | I Tools Used in Embedded Systems Design |                                                                 | 17 |  |

|      | 3.1                                     | Platform-based Tools                                            | 17 |  |

|      |                                         | 3.1.1 Industrial Tools                                          | 18 |  |

|      |                                         | 3.1.2 Academic Tools                                            | 22 |  |

|      |                                         | 3.1.3 Summary, Strengths and weaknesses in Platform-based Tools | 26 |  |

|      | 3.2                                     | Model Based System Design and Model Driven Architecture         | 31 |  |

|      |                                         | 3.2.1 Commercial Tools                                          | 31 |  |

|      |                                         | 3.2.2 Open Source Tools                                         | 33 |  |

|      | 3.3                                     | HiLeS Method tool                                               | 34 |  |

|              |     | 3.3.1            | HiLeS Designer                         | 34 |

|--------------|-----|------------------|----------------------------------------|----|

|              | 3.4 | Conclu           | usion                                  | 34 |

| IV           | Pro | $\mathbf{posed}$ | Methodology                            | 36 |

|              | 4.1 | Metho            | odology definition                     | 36 |

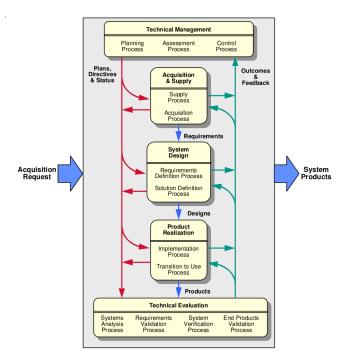

|              | 4.2 | EIA-6            | 32: Processes for Engineering a System | 37 |

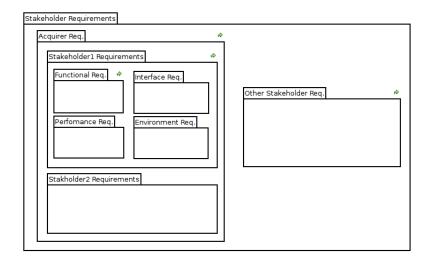

|              |     | 4.2.1            | Acquirer Requirements                  | 38 |

|              |     | 4.2.2            | Other Stakeholder Requirements         | 39 |

|              |     | 4.2.3            | System Technical Requirements          | 39 |

|              |     | 4.2.4            | Logical Solution Representations       | 39 |

|              |     | 4.2.5            | Physical Solution Representations      | 40 |

|              |     | 4.2.6            | Specified Requirements                 | 40 |

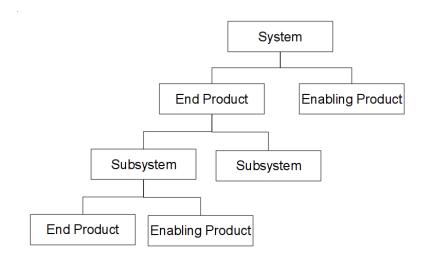

|              |     | 4.2.7            | Building block                         | 40 |

|              | 4.3 | System           | n Modeling Language (SysML)            | 41 |

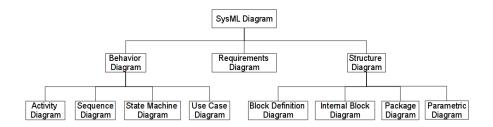

|              |     | 4.3.1            | Behavioral Diagrams                    | 41 |

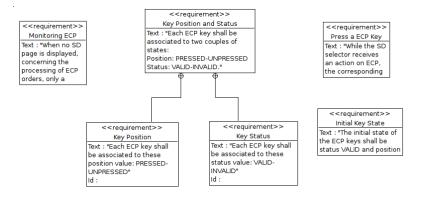

|              |     | 4.3.2            | Requirements Diagram                   | 42 |

|              |     | 4.3.3            | Structural Diagrams                    | 42 |

|              | 4.4 | Metho            | odology                                | 43 |

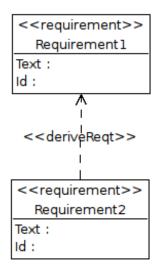

|              |     | 4.4.1            | Requirement Analysis                   | 44 |

|              |     | 4.4.2            | Functional and Architectural Analysis  | 47 |

|              | 4.5 | Conclu           | usion                                  | 63 |

| $\mathbf{V}$ | Exa | mples            |                                        | 65 |

|              | 5.1 | Skatin           | g Manager System                       | 65 |

|              |     | 5.1.1            | Stakeholder Requirements               | 65 |

|              |     | 5.1.2            | Applying the proposed methodology      | 68 |

|              | 5.2 | System           | n Display Selector                     | 84 |

|              |     | 5.2.1            | Methodology applied by Airbus          | 84 |

| Ref           | References 106 |        |                                                |      |  |

|---------------|----------------|--------|------------------------------------------------|------|--|

| $\mathbf{VI}$ | Con            | clusio | ns and Future Work                             | 103  |  |

|               | 5.3            | Conclu | nsion                                          | 101  |  |

|               |                | 5.2.5  | SD Selector System-HiLeS Model Verification    | . 97 |  |

|               |                | 5.2.4  | Applying HiLeS Formalism                       | . 89 |  |

|               |                | 5.2.3  | Proposed Methodology applied to Airbus Example | . 87 |  |

|               |                | 5.2.2  | System Description                             | 85   |  |

# List of Tables

| 1 | Industry tools which reach the Complete Platform-based design con-<br>cepts.( <b>DDF</b> : Dynamic Dataflow, <b>DE</b> : Discrete Events <b>FSM</b> : Finite<br>State Machine <b>SDF</b> : Syncronous Dataflow <b>TLM</b> : Transaction Level |    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Model)                                                                                                                                                                                                                                        | 27 |

| 2 | Strengths and weaknesses in industrial tools                                                                                                                                                                                                  | 28 |

| 3 | Academic tools which reach the Complete Platform-based design concepts.                                                                                                                                                                       | 29 |

| 4 | Strengths and weaknesses in Academic tools                                                                                                                                                                                                    | 30 |

| 5 | Cases to evaluate the requirements 18 and 19 of the SD selector                                                                                                                                                                               | 98 |

# List of Figures

| 1  | Capture-and-Simulate Methodology                    | 5  |

|----|-----------------------------------------------------|----|

| 2  | General design flow in ESL                          | 6  |

| 3  | Platform-Based Design                               | 7  |

| 4  | MCSE Method.                                        | 10 |

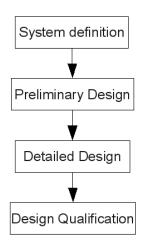

| 5  | Development phases in MBSD proposed in $[BCC^+00]$  | 12 |

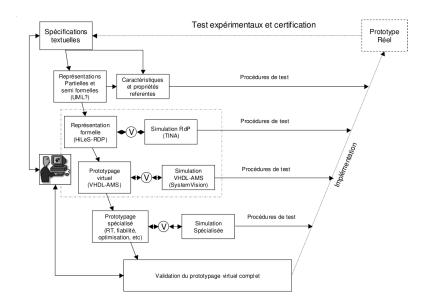

| 6  | V Methodology proposed by Hamon [Ham05]             | 13 |

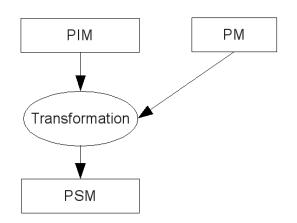

| 7  | MDA Model transformation                            | 15 |

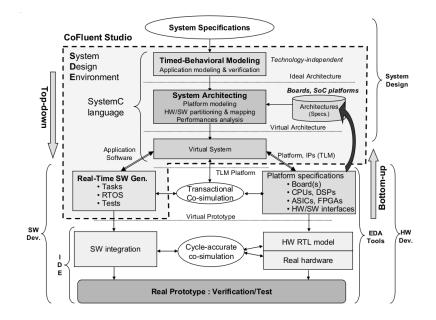

| 8  | CoFluent Studio in the system design flow [Cal93]   | 19 |

| 9  | MILAN architecture [PL01]                           | 25 |

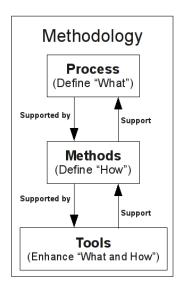

| 10 | Relationship between the methodology parts. [Est08] | 37 |

| 11 | Processes defined in EIA-632. [EIA99]               | 38 |

| 12 | Building block concept                              | 41 |

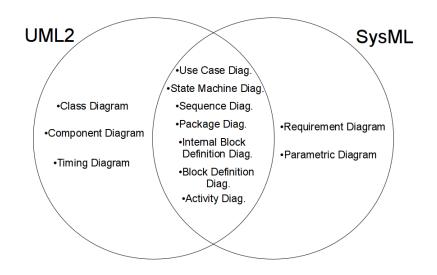

| 13 | Relationship between SysML and UML                  | 42 |

| 14 | SysML diagram groups.                               | 43 |

| 15 | Stakeholder Requirements Package Structure.         | 45 |

| 16 | Connection "Derive Requirement".                    | 46 |

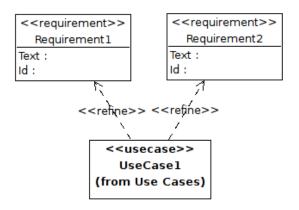

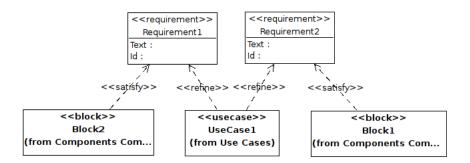

| 17 | Relationship between requirements and use case      | 48 |

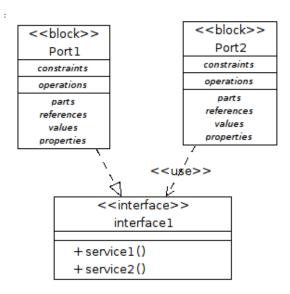

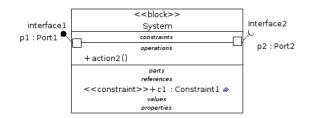

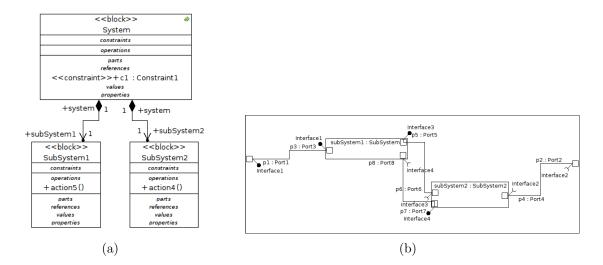

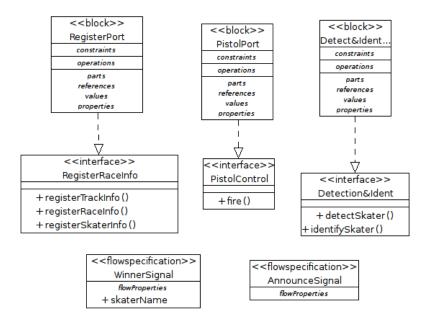

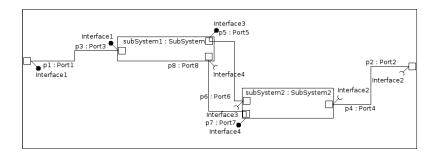

| 18 | Services and ports definition                       | 50 |

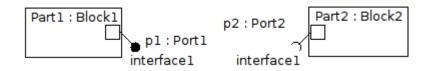

| 19 | Ports use.                                          | 50 |

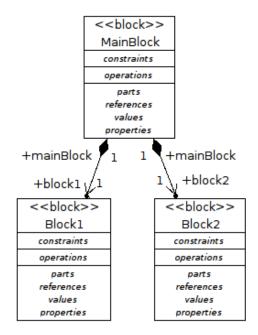

| 20 | BDD of a block composition                          | 51 |

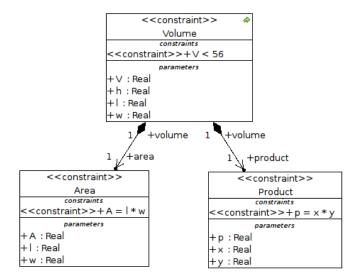

| 21 | Constraints blocks Example                          | 52 |

| 22 | Parametric diagram Example.                         | 53 |

| 23 | Attach constraints to a block.                                                                     | 53 |

|----|----------------------------------------------------------------------------------------------------|----|

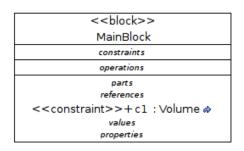

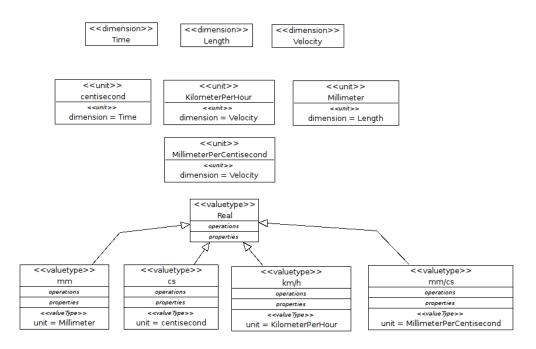

| 24 | "Meter" unit definition.                                                                           | 55 |

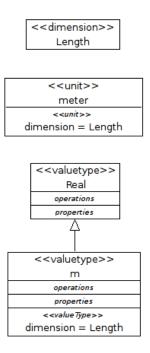

| 25 | Functional and Architectural Analysis Packages distribution                                        | 55 |

| 26 | Relationship between requirements, use case and blocks                                             | 56 |

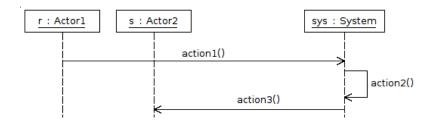

| 27 | Scenario in level 0                                                                                | 57 |

| 28 | System structure representation in level 0                                                         | 58 |

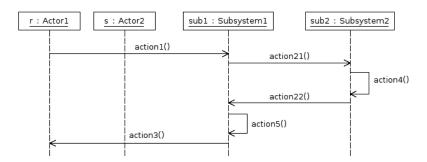

| 29 | Scenario in the level 1                                                                            | 59 |

| 30 | System structure representation in level 1                                                         | 59 |

| 31 | Methodology validation using MDA concepts                                                          | 61 |

| 32 | Logical solution to physical solution mapping in the proposed method-<br>ology using MDA concepts. | 62 |

| 33 | Methodology summary                                                                                | 63 |

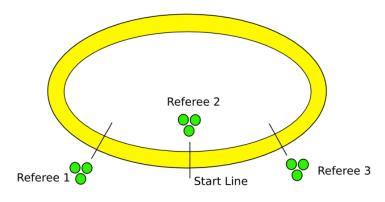

| 34 | The skating course                                                                                 | 66 |

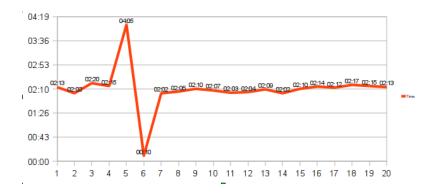

| 35 | A skater times.                                                                                    | 67 |

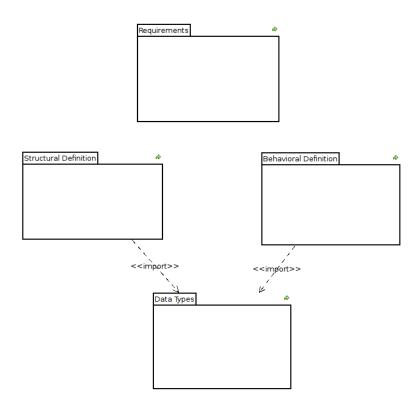

| 36 | Package distribution in the SysML project                                                          | 69 |

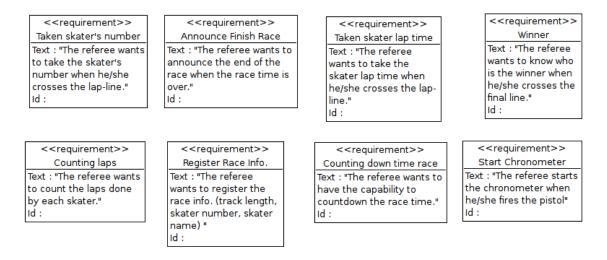

| 37 | Referee Functional Requirements                                                                    | 70 |

| 38 | Referee Performance Requirements                                                                   | 71 |

| 39 | Referee Interface Requirements                                                                     | 71 |

| 40 | Referee Environment Requirements                                                                   | 72 |

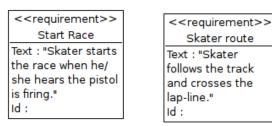

| 41 | Skater Functional Requirement.                                                                     | 73 |

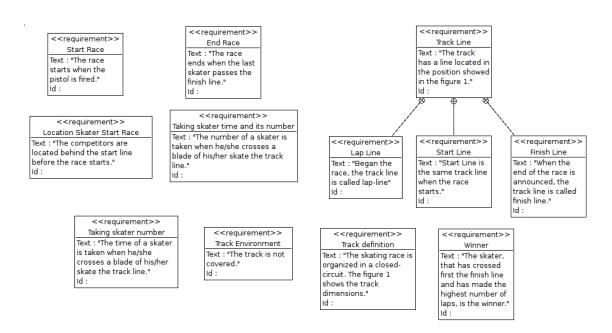

| 42 | Race Rules requirements                                                                            | 73 |

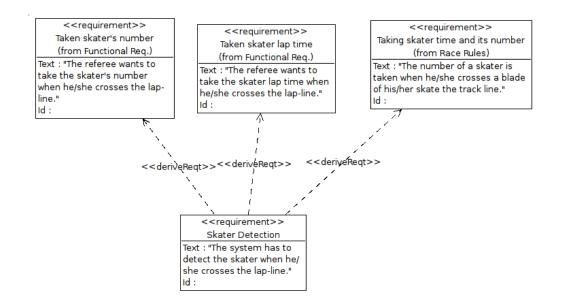

| 43 | Derived System Technical Requirement from Stakeholders requirements.                               | 74 |

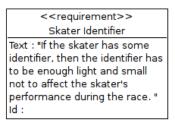

| 44 | Technology requirement.                                                                            | 74 |

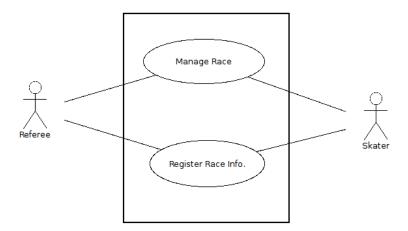

| 45 | Skate Manager System use case diagram                                                              | 75 |

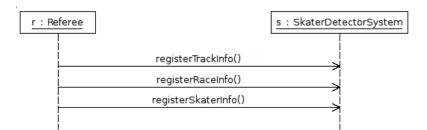

| 46 | Register Race Info scenario in the Level 0                                                         | 76 |

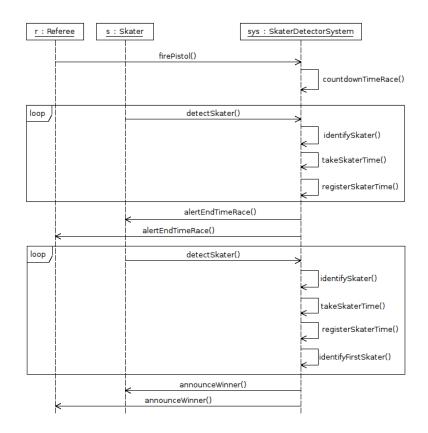

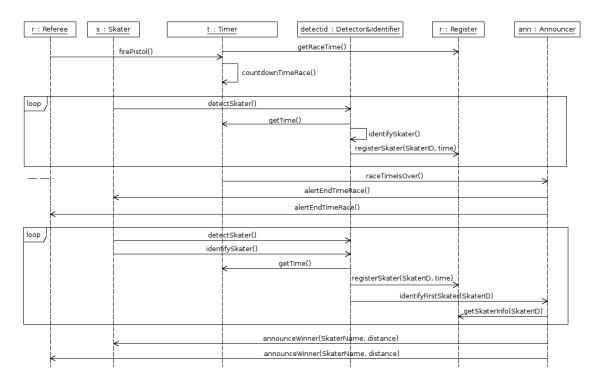

| 47 | Manage Race scenario in the level 0                                                                | 77 |

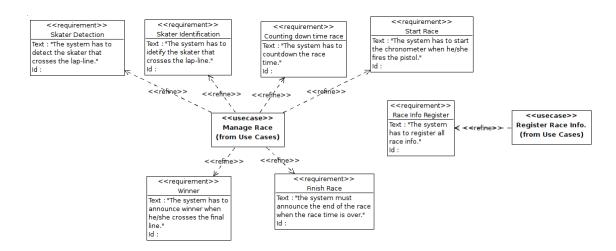

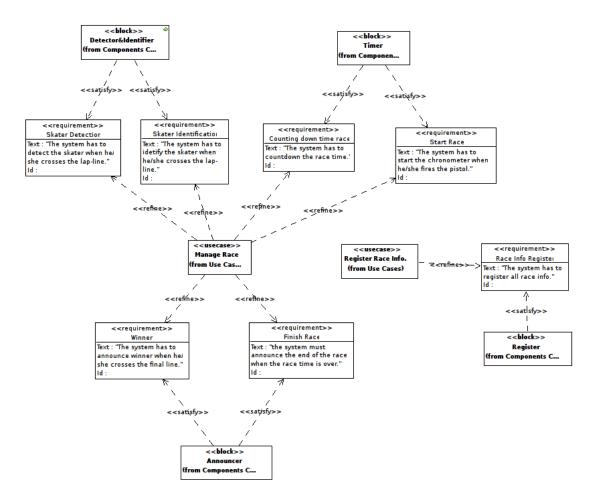

| 48 | Connection between requirements and use cases                                                      | 77 |

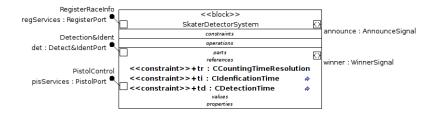

| 49 | Ports, interfaces and services definition for Skater Manager System.                | 78  |

|----|-------------------------------------------------------------------------------------|-----|

| 50 | Data type definition used in the constraints definition. $\ldots$ $\ldots$ $\ldots$ | 79  |

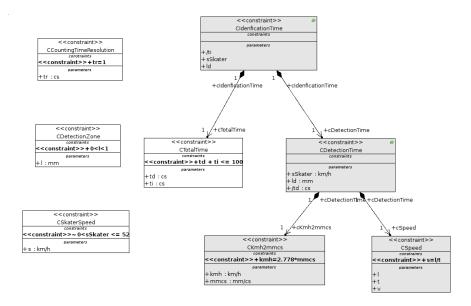

| 51 | Skater Manager System Constraints defined in a BDD                                  | 80  |

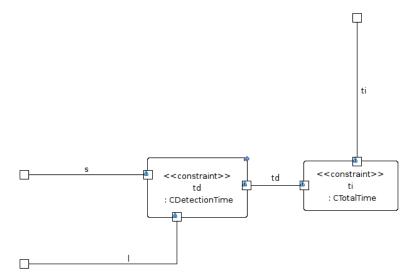

| 52 | Parametric diagram for the Identification Time Constraint                           | 80  |

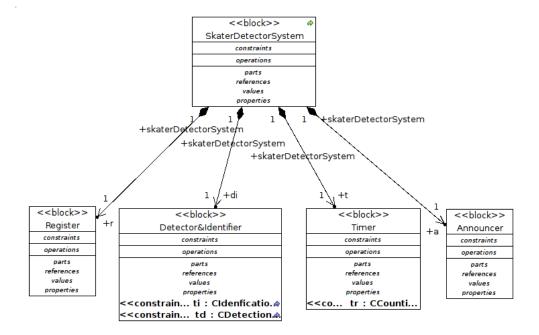

| 53 | Block Definition Diagram in Level 0                                                 | 80  |

| 54 | Manage Race scenario in the level 1                                                 | 81  |

| 55 | Relationship between Use Cases, Blocks and Requirements                             | 82  |

| 56 | Block Diagram Definition in Level 1                                                 | 83  |

| 57 | Internal System Representation in Level 1                                           | 83  |

| 58 | Airbus Methodology                                                                  | 85  |

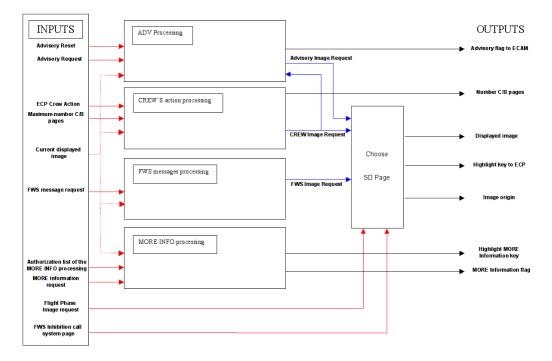

| 59 | General architecture SD selector                                                    | 86  |

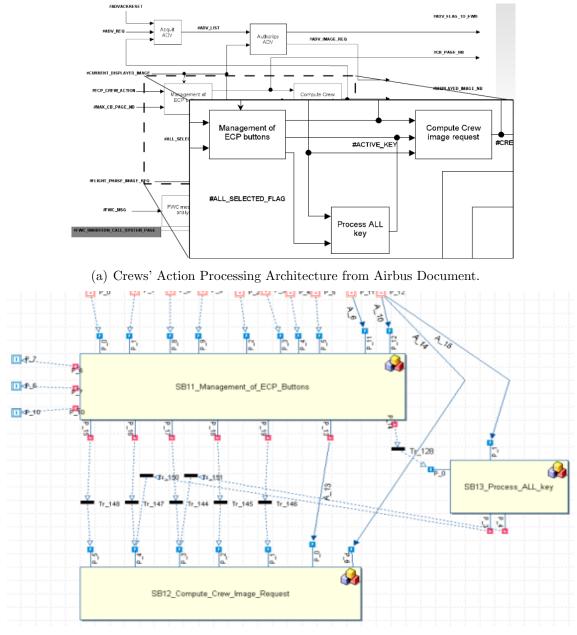

| 60 | Functional requirements of Generalities from Crew's Action Processing.              | 88  |

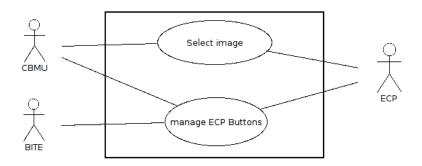

| 61 | Crew's Action Processing Use cases diagram                                          | 88  |

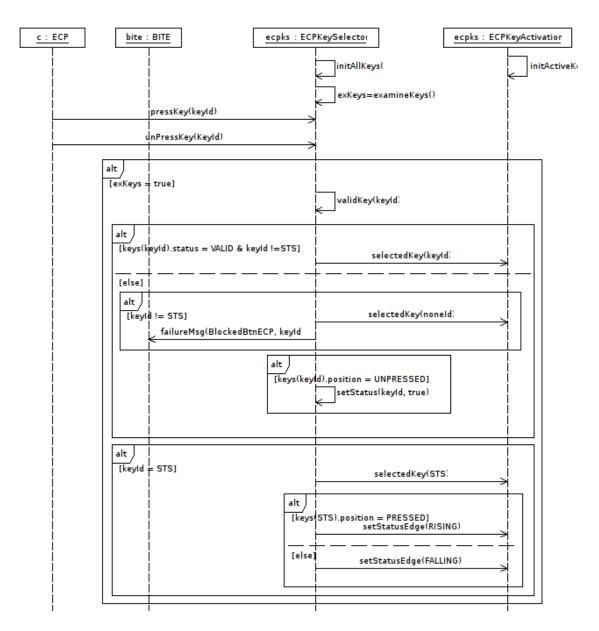

| 62 | Part of a scenario in the Crew's action processing                                  | 90  |

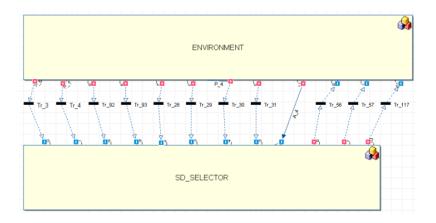

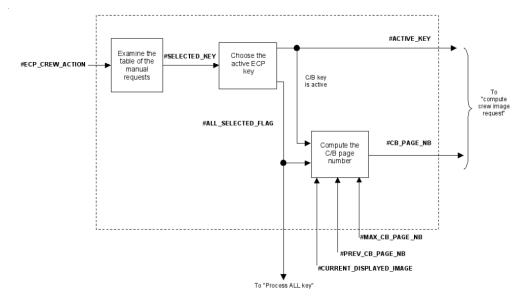

| 63 | SD Selector Level 0 using HiLeS                                                     | 91  |

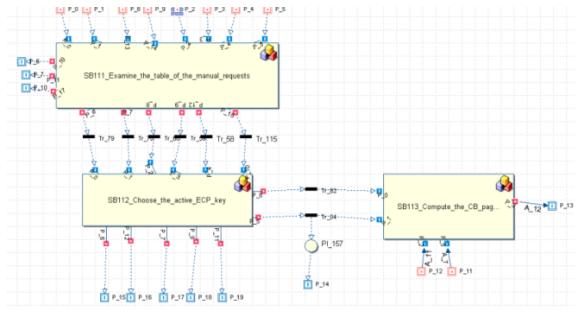

| 64 | SD Selector Level 1 Representation                                                  | 92  |

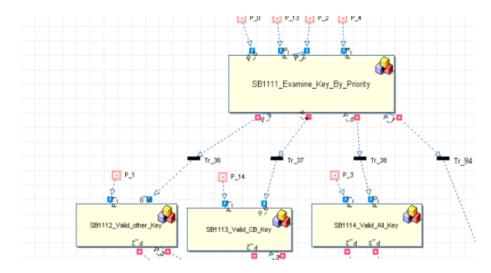

| 65 | SD Selector Level 2 Representation                                                  | 93  |

| 66 | SD Selector Level 3 Representation                                                  | 94  |

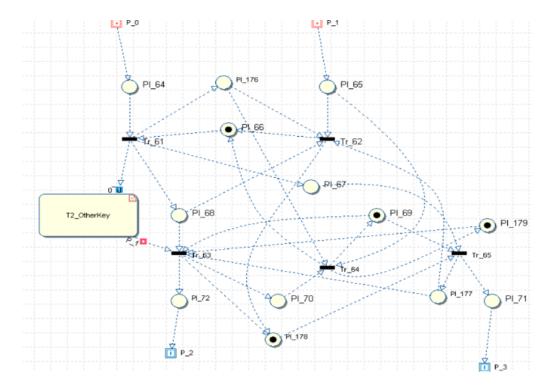

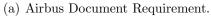

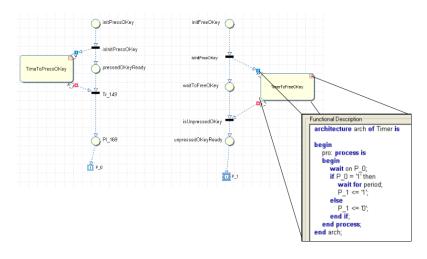

| 67 | "Valid X Key" behavioral description using HiLeS                                    | 95  |

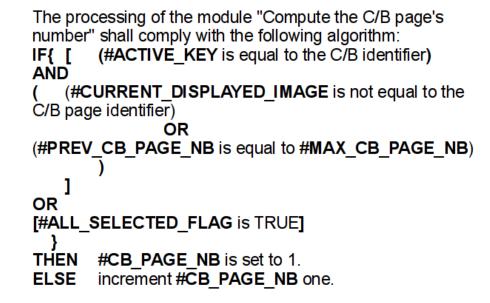

| 68 | Requirement algorithm represented in HiLeS                                          | 96  |

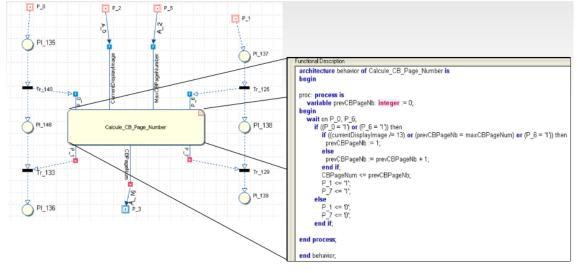

| 69 | Environment levels using HiLeS                                                      | 97  |

| 70 | Action Key representation using HiLeS                                               | 98  |

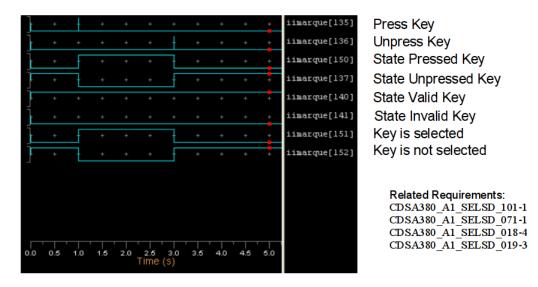

| 71 | Marking in our "Valid X key" unit                                                   | 99  |

| 72 | Simulation of "Valid X key" Scenario 1, press a key during 2 sec                    | 100 |

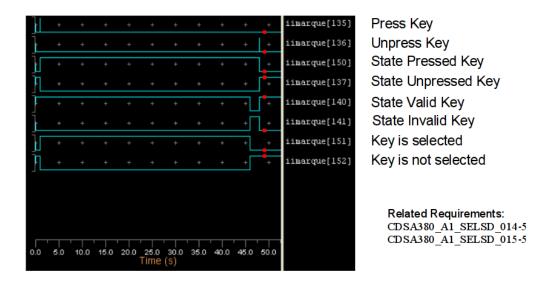

| 73 | Simulation of "Valid X key" Scenario 2, press a key during 48 sec                   | 101 |

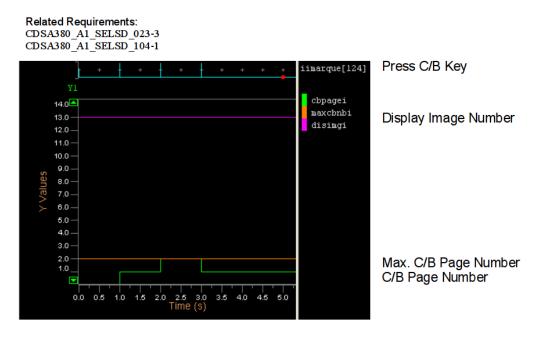

| 74 | Simulation of Scenario 3, press three times C/B Key                                 | 102 |

# CHAPTER I

# Introduction

The complexity in embedded systems has been increased in the last years. New heterogeneous systems which combine different domains are more common. Aircrafts, automobiles, cell phones, medical equipments are systems examples where domains such as electronics, communication, software, mechanics, physics, mathematics and medicine are part of the systems development today.

The markets demand to increase the functionality of the present systems, to mix domains, to anticipate the errors in the system development process and to reduce the delay of time to market in order to minimize design and production costs. Systems such as cell phones have passed from the simple functionality to talk with other people to new functionalities have been added such as SMS, music, videos, Internet, GPS and others, increasing the complexity, adding new systems and reducing their size.

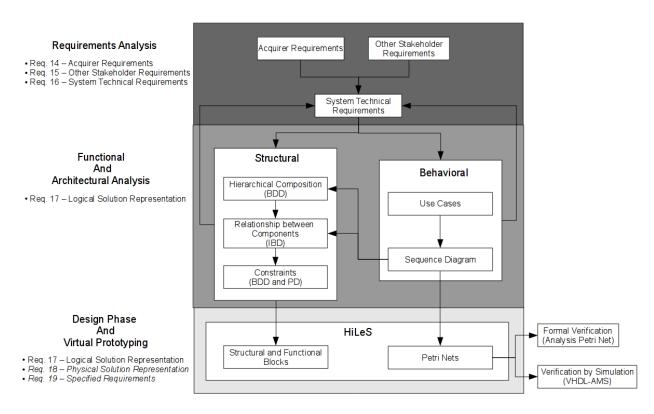

In this work, we propose a methodology to design embedded systems. This methodology is based on EIA-632 standard, which gives the process to the development and production of a system. We use the object-oriented approach to develop each step in the design process proposed by the EIA-632 standard and we create a method based on SysML for its development.

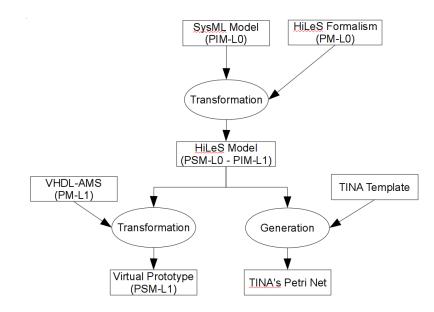

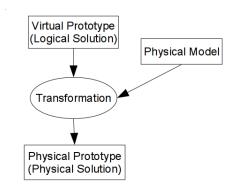

Our methodology uses the MDA concepts to do initial model verification using the transformation from SysML model to HiLeS [Jim00] formalism. In HiLeS, we can execute a formal logical verification extracting the logical behavior represented in Petri Nets and to analyze formally using analyzer tools such as TINA [BRV04]. Also, we can verify by simulation, generating a virtual prototype in VHDL-AMS from the HiLeS model.

The content of this work is the following: In the chapter 2, we give a review in the evolution of embedded system design, we explain some methods used in the system design today. In the chapter 3, we present the tools used to implement the methods exposed in the chapter before. In the chapter 4, we introduce the EIA-632 standard, the model language SysML and we present our methodology. In the chapter 5, we show two examples where the proposed methodology was applied. Finally, we give some conclusion and future work in this topic in the chapter 6.

# CHAPTER II

# Methods

In order to make the design of a complex system, it is necessary to use a method which will guide the steps to conceive a specific system. In this chapter, the term "method" is explained, because it will be used throughout all this work. Also, it will show the evolution of the methods in the design of complex system. We continue describing different approximations to design complex system in order to have a good idea what is the present problem in the design. Finally, we explain the base methodology of our work, MDA, which is strongly used in the development of software system.

## 2.1 Definition

A method is defined as the techniques applied inside a design process by the system designers; which is "how" the design task process works [Est08]. Following this definition, in the design of complex system there is a history involved.

## 2.2 Evolution in the embedded system design methods

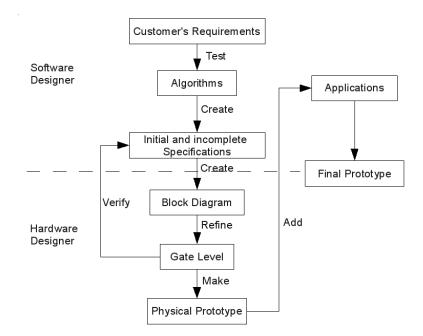

Since the 1960's, the development of embedded systems was a sequential designing process, starting from the requirements that each system had to reach. The software designers developed algorithms which represented the different system's behaviors and created the system's specifications where their application had to run. However, these specifications were not complete, because they did not take into account many features that the software designers were not able to see until after the physical prototype is made. Afterwards, the software designers handed over the specifications

to the hardware designers in order to design and build a physical prototype that would fit the software designer needs.

Hardware designers began building a block diagram of the system, following the given specifications. When the block diagram was finished, they manually transformed it to a gate level. In this level they could simulate and validate if the behavior of their design reached the specifications. This transformation was time-consuming, because they must simulate and verify each specification. Also, the verification was possible only when the hardware design achieved the gate level; therefore the designer had to go down in different abstraction levels without the designer's verification in each step of the process, simply because the verification could not be made in another level.

Once the verification was finished, the hardware designers built a physical prototype for the software team. Often this system prototype did not fit the software team expectations, due to the ambiguity and the incompleteness of the original specifications. Thus, the software team implemented their applications onto the prototype and tried to do their best effort to achieve the system real specifications and get the final system prototype. In the Figure 1, it is drawn this methodology, called "Capture-and-Simulate" in [Gaj07].

When the technology improved and the logic synthesis arose, the design method changed. Hardware designers could describe the system's specifications with boolean equations and they could transform these equations to gate level using a specific tool. With these new methods and tools, the hardware designers could verify their designs in the boolean equation description and re-verify them on gate level. This methodology is called "Describe-and-Synthesis" in [Gaj07].

During 1990's, the boolean equations description was changed for languages which rose the abstraction level to the register transfer level (RTL). Hardware Design Languages (HDL), such as VHDL and Verilog followed this new hardware description. These languages have been the most used until today and they are called "Synthesis-based" in [Gaj07].

Since the late 1990's, the system complexity has risen, therefore system designers have had to increase the abstraction level of their designs. They began to create

Figure 1: Capture-and-Simulate Methodology.

system models using generic languages to describe the system's specifications. These models describe only the behavior and the basic structure of the system without taking into account what will be hardware and what will be software.

Languages as C, C++ and Java were used by the hardware and software designer to create the behavioral model of these systems. However, this approximation was limited, because in this kind of language certain hardware concepts were not present, such as concurrency and the notion of time [HS07]. Hence, it was necessary to extend these languages in order to complete the hardware concepts. Languages such as SystemC [16608] and SpecC [Dom02] are examples of this work.

Concepts such as "Transaction Level Modeling" or TLM [Mon07], which are above RTL, are rising. Their focus is to separate the computation and the communication in the system design to help reusing models. SystemC follows this concept.

Having available this new option, the designer can develop systems in a higher level of abstraction and these systems can be executed to verify their behavior and the fulfillment of their specifications and constrains. This new process is called Electronic System Level (ESL) [Bai07] design (figure 2). The ESL solved an important

Figure 2: General design flow in ESL.

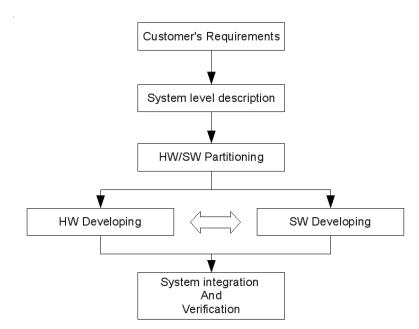

part of the design problem, describing the behavior of the system without deciding which part will be hardware and software. Nevertheless, it helps to decide about the partitioning and to have an early virtual prototype in order to develop, almost at the same time, the software and hardware after the partitioning. This virtual prototype helps to verify the hardware and software developments according to the specifications. A good method example is the platform-based design.

## 2.3 Platform-Based Design

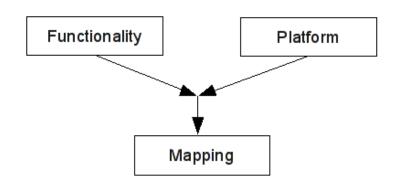

Nowadays, according to the market demands, it is important to reduce the time in the systems design. Therefore, it is necessary to move towards re-using design methods and to develop alternative ways to transform the system specifications to re-use designs.

A proposal was made in [SV07], and it is to separate the system functionality from the platform where the functionality will be implemented. This process is called "Platform-based Design" (PBD). The figure 3 shows the basic design of this

Figure 3: Platform-Based Design.

designing process. It begins with the customer's requirements: Functional and nonfunctional requirements. Functional requirements correspond to the "what", what the system has to do. The non-functional requirements match up to the "which" and "how", how the system's behavior has to be and which the system's size has to be. These requirements will be transformed to specifications and constrains in the system designer terms.

• Functional Side: The system designers develop the system's functionality, where it is expressed the behavior of the system. Usually this is modeled on algorithms, using different languages and there is not distinction between hardware and software design.

The software and the hardware designers have their own approaches in describing the system's functionality. The hardware approach uses languages originally created by software designers, such as C, C++ and its derivation such as SystemC and SpecC. An additional approach came from model-based designers, which use UML as a basis to create a new profile that can be used in the embedded system design. Examples of this tendency are UML for SoC [MM05] and recently SysML [LdOFV07].

On the other hand, the software approach which includes hardware concepts creates languages such as Esterel, Lustre and Signal. Other approaches are models of computation, where the system is graphically represented using Dataflows, Finite State machines, Petri nets, etc. These models can be heterogeneous (a mix between different domains such as analogous and discrete) or homogeneous.

• Architectural Side: The architecture represents the structure where the system's functionality will be implemented. It is made using an architecture's library, a component's library, the system's constraints and the system's specifications. With these elements, the designer can use a preexisting architecture and then change the components which do not fulfill the constraints, and probably adding other components to achieve the wished functionality.

On this subject, there are again two approaches: Software and Hardware approaches. In the software approach, the architecture description languages (ADL's) are used; in [MT00] it is possible to find a complete survey about these languages. Another approach is UML and its extensions. In contrast, the hardware approach has languages such as HDL and more recently TLM, which is used in many architecture design tools.

• Mapping platform result: When the designer has the functionality and the possible architecture where the system will be implemented, he maps these models using different techniques to find the best performance. In this step, the designer decides which functionality will be implemented in the hardware and which will be solved in the software, to achieve the wished performance.

A traditional mapping technique is to force the functionality model and the architectural model to match each other in an iterative way, it means that the functionality is mapped on a candidate architecture and if the constraints are not reached, then the designer has to change either the functionality or the architecture. When the change is made, the system design is tested again and the process starts all over again until the systems' specifications are reached. This technique is not optimal, because it does not use any optimization method to find the best way to match functionality onto architecture.

In [SV07] it is proposed to use a unique mathematical formalism in order to

express both models in equations, and also the functionality, the architectural and the constrains, to be able to build a cost function and to apply an optimisation method to make an automatic mapping. In [CFDBSV<sup>+</sup>05] the idea of the PC architecture continues, in order to create standard architectures for specific fields. The main idea is to apply specific applications using Application Platform Interfaces (API).

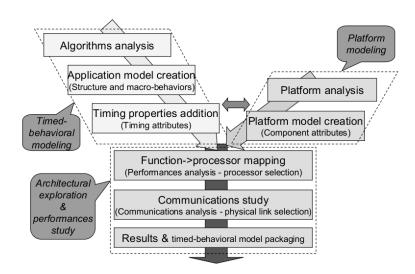

## 2.4 MCSE Method

The Electronic System Design Methodology (MCSE in french) follows the main features of Platform-Based Design. It splits the system functionality from the platform where it will be implemented. By simulation, the platform configuration is evaluated in order to satisfy the functional constraints [Cal93].

This method is decomposed in three stages:

- Timed-Behavioral modeling

- Platform modeling

- Architectural exploration and performances study

In the Figure 4, it is shown the design flow of this approach.

- **Timed-Behavioral modeling:** In this stage the system specifications are transformed to a timed-behavioral model. This model is represented in SystemC, so it can be verified by simulation. This stage has three steps:

- Algorithms analysis: The specifications represented in algorithms are studied. These specifications are analyzed, identifying the level of granularity required for the model, the elementary computational blocks, the data flow and the data structures.

- Application model creation: The analysis made in the last step, is structured in order to create an application model. An application model consists of elementary functions and communication links. Functions are described with a behavioral model including the needed computational

Figure 4: MCSE Method.

blocks. These functions are linked by communication links. This application model is also a SystemC model, so it is possible to verify this stage by simulation.

- Timing properties addition: In this step the time attributes are added to the behavioral model inside the application model in order to get a timed-behavioral model.

- **Platform modeling:** In this stage a platform model is created. The modeling of the platform is built in an abstract level which allows certain performance evaluations, such as message level. There are two steps involved in this stage:

- Performance Analysis: The computational units are identified; their features are defined, as well as the communication links between them.

- Platform model creation: A graphical model of the physical architecture is built. This model contains the computational units which are necessary to run the application model. This model is featured by a set of attributes.

- Architectural Exploration and Performances Study: Finally, this stage allows mapping the application model elements to the platform model elements. In this process, there is an exploration of the design space and it is

studied the system performances. In this stage there are 3 steps:

- Function-to-processor mapping: By experience, the designer does the first partitioning software/hardware. This activity is to map functions to processors inside the SystemC environment. The result is a timed-behavioral model influenced by the processors constrains. Such as the mapped model is also a SystemC-based model, it can be evaluated by simulation.

- Communication study: The influence of the communications links between processors is studied. Modifications and variations are done in order to achieve a wished performance.

- Results production: This step provides a SystemC virtual system architecture which details the specification collected in the two steps developed before; and it is traduced to the execution performance for the application.

This method shows the problem which is concerned to the experience of the designer. The partitioning between software and hardware is done initially by experience and later according to the simulation results, the partition or the selection of the components is modified.

# 2.5 Model-Based System Design

The Model-Based System Design is a method which uses as basis a system engineering process to design a complex system. In [BCC<sup>+</sup>00], the authors used the system engineering process, defined in the standard IEEE 1200, to implement their method inside the process' activities by the development of a complex system based on models. In the figure 5, it is depicted the development phase in [BCC<sup>+</sup>00]. The IEEE 1200 standard follows a top-down design flow.

• System Definition: This phase corresponds to the analysis and requirements baseline validation of the IEEE 1200 activities. In this phase are defined the system requirements and they are integrated to a system model. The system

Figure 5: Development phases in MBSD proposed in [BCC<sup>+</sup>00].

model that is created in this phase has to be executable in order to evaluate the system requirements, in other words, to verify the system model.

- **Preliminary Design:** The system is split into subsystems. The system model descends to a more detailed description level and gives a guide to the component distribution. Also in this phase each subsystem model has to be executable.

- Detailed Design: Subsystems are detailed in this phase. The model of the subsystems is mapped to components, afterwards executable models are created which follow the behaviour of the components mapped of the subsystems. These executable models verify if the detailed subsystem models fulfil the system specifications. Also in this step, other constraints are chosen such as size, weight, colour, etc.

- **Design Qualification:** The model tests are compared to the manufactured components' tests. The complete verification is done in this phase. Models are updated after the integration and they are verified against the specifications.

Based on the conception MBSD, Estefan in [Est08] shows a survey of methodologies that implement it, such as Telelogic Harmony-SE, INCOSE Object-Oriented Systems Engineering Method (OOSEM), IBM Rational Unified Process for Systems

Figure 6: V Methodology proposed by Hamon [Ham05].

Engineering (RUP-SE), Vitech Model-Based System Engineering (MBSE) Methodology and State Analysis (SA). The methods implemented in these methodologies are presented in the different steps of the system design, starting from the customer requirements and all the treatment necessary to conduce to system model and later to a physical system. PBD is only oriented to the phase of the system design, how to do the partitioning and get a real system.

The two methods, PBD and MBSD, are complement each other. PBD can be used to descend from high level description to a low component description, as well as MBSD proposes in each phase, but MBSD does not explain how that is made.

## 2.6 HiLeS Method

Hamon proposes a method to develop complex systems in its PhD thesis [Ham05]. It is a classical V methodology whose steps are represented in figure 6 and its work was in the formal representation of the system, the virtual prototype and its verification by formal analysis and simulation.

He suggests a previous transformation from textual specifications to a semiformal representation in UML. Once the designer has the system described in UML, it can be transformed to a formal representation called HiLeS; a formalism based on Petri Nets [CL08]. The logical representation of the system can be verified formally by formal analysis using a tool called TINA[BRV04] and the behaviour of the whole system is verified by simulation transforming the system model to VHDL-AMS and later using tools such as System Vision [Gra09] to simulate. The system model represented in VHDL-AMS is called "Virtual prototype" and it will be used as a specification to the suppliers in order to get a physical prototype.

## 2.7 Model Driven Architecture

Model Driven Architecture (MDA) is an OMG approach to system development. MDA uses models to understand, design, construct, deploy, operate, maintain and modify systems. Its main purpose is to split the functionality of the system from the platform where the system functionality will be implemented. This helps to the portability, the interoperability and the reusing of the system design [OMG03].

Dividing the functionality and the platform, it is possible to refine the functionality in different levels of abstractions. Each level is transformed using a transformation rule from one level to another. MDA opens the possibility to do an intermediate transformation to verify the system behaviour using a specific platform, such as an executable language (Java or VHDL).

The main elements in MDA are:

- Computation Independent Model (CIM): This model is used to describe the system domain. It is useful to understand the requirements of the system and also, it is a communication link between the customer and the designer. This model does not have any system solution.

- [Platform Independent Model (PIM): This model describes the behaviour of the system which is independent from the platform where it will be implemented. This model can be refined in different degrees of detail, descending on design abstraction levels.

- Platform Specific Model (PSM): It is the model where the PIM will be

Figure 7: MDA Model transformation.

implemented on a platform. This model allows verifying the PIM in different ways, e.g. by simulation.

PIM, PSM and the platform model (PM), where the PIM will be implemented, need to create a metamodel which will be the "template" that allows to create a model either PIM or PM. In order to map the concepts from PIM to PM it is necessary to define transformation rules that relate the PIM's metamodel concepts to PM's metamodel concepts. A transformation engine is used to make these transformations and generate a PIM. In the figure 7 is shown the Model transformation.

MDA is clearly related to PBD, where PIM is the functionality model and PM is the same Platform model. The mapping platform can be considered as the PSM in MDA. Vincentelli said that there are similar concepts between both approaches, but he cleared that MDA does not make a good description on how PM or PIM have to be implemented [SV07]. From this point of view, MDA is only a process which gives support to designing systems, but it does not describe "how" that can be implemented. Hence, PBD can be an implementation way.

There are other works which try to implement the MDA concepts, such as MDA approach for the classical "Y-chart" Design [BDDM03] and MDA applied to embedded systems dedicated to process control [HB03].

## 2.8 Conclusion

In this chapter, we defined the method conception, we gave a brief review in the evolution of embedded system design methods, we explained the Platform-based Design, MCSE method, Model-Based System Design, HiLeS method and MDA. We showed some similarities between the different described methods and we could see that the tendency in system design is the partition between functionality and architecture, and subsequently make the mapping between them. Also, we could appreciate that increasing the abstraction level in the design is a contemporary tendency, in order to reduce the complexity of the systems and to easily verify the model according to the requirements.

In the next chapter, we will present the tools used in the methods described in this chapter, and we will do a classification according to the development group, its features, and its reachability.

# CHAPTER III

# Tools Used in Embedded Systems Design

Part of the complex systems methodologies are the tools which make easier the development of a system design. Each methodology has its own classification of tools, according to what tool fulfills the requirement inside the methodology and who is the developer of the tool, the academia or the industry. In this chapter, we show the classification of the tools used in embedded system design according to the methods described in the last chapter, its developer group, its main features, weakness and strengths of each tool inside a methodology context.

## 3.1 Platform-based Tools

There are different tools, both in the industry and the academy which follow part of the Platform-based principle. In [DPSV06], Densmore et al. make an excellent classification list of these tools, we extract the main tools which use this design method and we give a more detailed description of these tools. We based our work in their web pages and available articles. The authors divide the tools in three groups, according to its functionality:

- *Single:* Tools which only develop a part of the platform-based method, that means just Functional model or Architectural model or Mapping model.

- *Pair:* Tools which develop a combination of two parts of the platform-based method, that means, Functional with Architectural, Architectural with Mapping and so on.

• *Complete:* Tools which develop each part of the platform-based in the same environment.

We are interested in the tools which reach the requirements of the complete group, thus we chose the tools which follow this principle in the industry and the academy world. These tools offer a unique environment to model the functional and the architectural part, and it is also possible to make the mapping between the two models in the same tool. In the following sections, we make a summary of each Industrial and academic tool chosen in [DPSV06], we show a summary table which sums up the main features of these tools and finally we show another table which exposes the strengths and weaknesses of them.

### 3.1.1 Industrial Tools

### 3.1.1.1 Cofluent Studio

This tool is a system design environment based on the SystemC language that covers the timed-behavioral modeling and system architecting steps according to MCSE methodology [Cal93]. This tool helps the designer to convert system specification to a virtual system which is verified by simulation.

The tool has three modules:

- **Timed-Behavioral Modeling:** In this module, the designer creates and validates an application model starting from a well defined system specification. The application model has different refinement levels, starting from a behavioral model without taking into account the time, ending into a timed model.

- System Architecturing: This module allows exploring multiple platform, different hardware/software partitioning and allocation strategies. Non-functional constraints such as performance, real-time constraints and costs are taken into account. The result of this module is a SystemC Virtual System, which is the system application mapped in a platform with a previous performance analysis that follows the non-functional constrains of the system. This virtual System is used to start the development of the hardware and the software part.

Figure 8: CoFluent Studio in the system design flow [Cal93].

• **Real-Time Software Generation:** Using this module, the designer can generate the C code of the software part from the virtual system.

In the figure 8 is pictured the different modules presented in this tool. The pointed area is covered by CoFluent Studio.

#### 3.1.1.2 MLDesigner

This tool is a MLDesign Technologies product. It is a system-level simulation modeling platform which integrates both system level modeling areas (architecture and function), and simulation domains in a single tool [STF<sup>+</sup>03]. The modeling domains that this tool supports are: Discrete event, Dynamic Dataflow, Synchronous Dataflow, Continuous Time/Discrete Event, Finite State Machine, Boolean Dataflow and Higher-Order Function. The domains can be used ether in a homogeneous (to use the same domain to model a system) or heterogeneous (to use different domains to model a system) environment.

The base of this tool is Ptolemy, and its graphic representation is based on the Ptolemy language called Ptolemy Tool command Language (Ptcl).

A system model is represented by hierarchical blocks called modules. A module contains primitives and other modules. A primitive is a single function of the model which is defined ether by a C++ code form or by finite state machine model. Each module and primitives has ports which are connected by visual links called relations [MT07].

Using this tool, the designer can build a complex system starting from a high abstraction level such as mission-level or operational level and descending for System level design (computer architecture, communication network design, etc) arriving to a functional level design where is expressed the algorithm design, the implementation and the partition software/hardware.

The tool is not linked to a specific methodology, therefore it is possible to apply a methodology which describes the system in high level (behavioral and structural) and split it in subsystem following a detailed description when the designer descends into different abstraction levels.

From the point of view of Platform-based design, using this tool, it is possible to describe the system functionality separated from the platform where the system will be implemented using the same language, in this case, Ptolemy. Manually, the designer can map the functionality to the platform by experience, for instance, and to see the mapping result on the simulation of the resulting system model.

The tool helps to simulate whatever behavior that the designer can build, but we cannot find if it has the functionality to help in the mapping process.

#### 3.1.1.3 Visual Sim

This tool is a Mirabilis Design product. It is a block-oriented system model design environment, similar to Ptolemy and MLDesigner, where the designer can create a hierarchical system design in different abstraction levels. Each block inside of a system model is called SmartBlock and it can represent hardware, software, networking components at queuing, performance, transaction and cycle-accurate levels of abstraction [Inc03]. It uses different model domains, Mirabilis calls them "simulation kernel" and they are Discrete event, Synchronous Data Flow, Finite State Machine and Continuous time. Visual Sim has an extended library of components such as CPU, caches, bus and memory ready to use in the system model, reducing the time to design.

A designed system in Visual Sim can be described in three parts: Architecture, Behavior and Workload. Architecture is the representation of the components interconnected, the behavior represents the actions that will be performed by the system and the workload is the transactions that traverse the system such as network traffic. The mapping between behavior and architecture is performed using virtual execution [AM06].

Mirabilis proposes a top-down methodology, which consists of three main steps: Requirement analysis, Functional Analysis and Architecture Analysis. These steps are supported by the System Analysis. Each step can be modeled, detailed and simulated in Visual Sim.

Visual Sim does not have enough documentation to evaluate the real advantage to use this tool compared to MLDesigner because its block-model approach is similar. It is clear that it has an extended library to build system models and the facility of import and build models in different language such as C, C++, Java, SystemC, Matlab, etc. and maybe this is the unique advantage that we can find in this tool.

### 3.1.1.4 System Studio

This tool, developed by Synopsys, allows building, simulating and analyzing complex digital signal processing (DSP) systems in a system-level design environment [Inc08].

The description of a DSP system can be split in functional and structural models. The functional model is defined in a hierarchical block-oriented environment where the description of the lower blocks is made in C/C++. The designer can used the different model domains offered by this tool to describe the functional model of his system. The available model domains are Dynamic Data Flow and Finite State Machine. Each domain can be mixed in the model in order to generate the behavior of the wished system. In order to model the architectural part of the system, this tool uses SystemC language and the designer can build an system architecture graphically by drag-n-drop hierarchical blocks described in SystemC.

System Studio has a library focused to different DSP systems domain, such as

Broad band access (ADSL, DOCSIS cable modem), 3G wireless (CDMA, EDGE), other wireless (Bluetooth, IEEE 802.11, GSM), digital video (MPEG-4), and others.

System Studio gives the tools to analyze the system model performance when the functionality of the system is mapped in an architecture proposed by the designer. We do not find any information that this tool helps in the decision process of the partition hardware/software.

#### 3.1.2 Academic Tools

#### 3.1.2.1 Metropolis

This is a tool developed by the University of California in Berkley and it follows strictly the Platform-based Method proposed by the same university. The base of Metropolis is a metamodel where there are defined the main concepts: process and medium. These concepts correspond to the separation of the model in actions (processes) and communications (mediums). Each process has associated a sequential program called thread. In order to communicate each process, each one of them has ports, and each port is specified with an interface. The interfaces are implemented by mediums which allow the division between actions and communication, getting to the designer the facility to reuse previous models [BWH<sup>+</sup>03].

With the Metropolis metamodel, the designer can represent the functional modeling, the architectural modeling and the candidate platform gotten from the mapping between functional an architectural modeling. Hence it uses the same language to describe behavioral and structural representation, the metamodel helps to do a fast mapping between the components of each representation.

The expression of the non-functional features, such as time, power and size is described in quantity managers. Execution process constraints are represented in the form of logical formulas in order to restrict the execution of the model.

Metropolis offers a framework, which provides to the designer verification, simulation and synthesis of its models.

#### 3.1.2.2 Ptolemy extension as Codesign Environment (PeaCE)

This tool is developed by Seoul National University and it is focus on multimedia system design, however the authors say that the tool can be used in other domains. PeaCE follows a traditional methodology to design embedded system and its functionality can be combined with other more specialized tools in each design step by generation of XML files [HKL<sup>+</sup>07].

The designer begins the system design, building the system level specification using extended Dataflow model and Finite State Machine. In order to simulate the model, PeaCE generates a code C from the model, compiles it and executes it.

When the system model is verified, the designer proceeds to explore the possible architecture candidates. The designer can use the pre-build platform which are available in the PeaCE's data base, or it can build a new one, using the available components in the library.

Once the platform is build, the designer can map the system functionality to the components. In this step, the designer decides the partition Software/Hardware and the component selection. PeaCE helps in this task performing a schedulability analysis, and calculating the performance of each functional block contained in the system model and the communication between different blocks.

After the partition is completed, PeaCE co-simulates the system to generate memory traces from the processing elements. With this information, the designer can explore bus architectures and select the best option. When the system is completed, it can be verified in PeaCE by simulation or using other third tool.

Verified the virtual system solution, PeaCE allows generating C code for processor core and VHDL code for FPGA implementation.

PeaCE follows the platform-based approximation and defines clearly how each step can be implemented.

### 3.1.2.3 Model Integrate Computing (MIC) and Milan

MIC is an environment created by Vanderbilt University to build software systems. However, the group, which develops this environment, uses MIC to create a tool to design embedded system. This tool is called Milan [PL01].

The environment MIC focuses on the formal representation, composition, analysis, and manipulation of models during the design process. It places models in the center of the entire life-cycle of systems; including specification, design, development, verification, integration, and maintenance following an Model-based development approach [fSIS09].

MIC is composed by the following tools:

- Generic Model Environment (GME): Tool allows creating Domain-specific models and program synthesis environments.

- Model Management tool suite

- Model Transformation tool suite

- Design Space Exploration tool suite

With these tools, the design can create an own tool to design a system in a specific domain following its own methodology. An example is Milan [PL01].

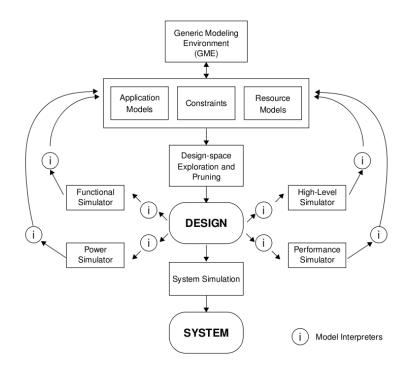

Milan is a tool based on MIC to design embedded systems. This tool has the architecture which is depicted in the Figure 9. A system in Milan is composed by three models: Application model, Constraint model and Resources model. The Application model represents the functionality of the system, Resources model describes the components where the functionality of the system will be implemented. Constraint model is used to characterize the components' limitation in connection level, power consume, etc. Also, this model represents the non-functional requirements that the system has to complete, such as power, performance, size, etc. The language to define these three models is defined in GME.

Milan uses the MIC engine transformation to convert the models expressed in GME to standard languages such as C, Java, VHDL. These languages can be interpreted by specialized-tools, such as Matlab and SimpleScalar, to simulate the model built in Milan. The simulation results are returned to Milan to verify the model behavior.

Figure 9: MILAN architecture [PL01].

In order to reduce the exploration time when the designer is deciding the partition Software/Hardware, Milan uses the MIC Design Space Exploration to reduce the component selection space, in order to map the elements of the application model to the resource model.

There are many applications based on MIC, they are available in [fSIS09]. The group, which developed Milan, has not continued its development.

### 3.1.2.4 Artemis

Artemis is a workbench which contains a set of tools which allows modeling applications and SoC-based architectures at high level of abstraction, mapping the applications on the architecture and estimating performance numbers through co-simulation of application and architecture models [Pim05]. Its domain focus is multimedia solutions.

The main tools of this workbench are:

• Compaan

- Laura

- Molen

- Sesame

Sesame is the base of the Artemis workbench. This tool allows choosing an specific-domain platform architecture (Architecture template) and building an application specification in a sequential program. The platform architecture is instantiated to an architectural model, while the application specification is transformed to a concurrent model in Kahn Process Network (KPN) using Compaan. Between the architecture model and the application model, there is a mapping model which provides the performance result of the mapping between the application model elements and the architecture model elements. This performance result achieved Laura and Molen tools. Laura is used to map the KPN diagram in the architecture and to generate code (Verilog, VHDL or C) to co-simulate and to give performance numbers. Molen is used to calibrate the performance of the architecture model.

#### 3.1.3 Summary, Strengths and weaknesses in Platform-based Tools

In this section, we review the main features of the industrial tools. In the table 1, we show the tools from the industrial world. They are the same tools found in [DPSV06]. They have its own focus on the system design and they use different abstractions to represent the functional, architecture and mapping models. Most of them use Model of Computation (Dataflow, Finite state machine, etc) to represent the models, but each one has a specific limitation. In the table 2 are expressed the strong and weak points of these tools.

In the table 3, we show the tools from the academic groups. They generally do not use standard abstractions to model systems, instead they extend it to reach its own representations. In the table 4, it is shown the strong and the weak points of each academic groups.

| Company                                              | Tool                         |       | <b>A</b> l | Abstraction | iction       | 1     |       | RTL Trans.                                                                       | Alg. Repr.                                      | Domain |

|------------------------------------------------------|------------------------------|-------|------------|-------------|--------------|-------|-------|----------------------------------------------------------------------------------|-------------------------------------------------|--------|

|                                                      |                              | DE    | DE/CT DDF  | DDF         | $^{\rm SDF}$ | FSM   | TLM   |                                                                                  |                                                 |        |

| CoFluent Design                                      | CoFluent Studio              |       |            |             | X            |       | X     |                                                                                  | C, C++, Sys-<br>temC                            | Mix    |

| MLDesign Technolo-<br>gies                           | MLDesigner                   | ×     | X X X X X  | ×           | X            | X     |       |                                                                                  |                                                 | Mix    |

| Mirabilis Design                                     | Visual Sim product<br>family |       | X          |             | X            | X X X | X     | Х                                                                                | C, C++, Java,<br>SystemC, Ver- Mix<br>ilog/VHDL | Mix    |

| Synopsys                                             | System Studio                |       |            | X           | X X X X      | X     | X     | X                                                                                | C, C++, Sys-<br>temC                            | Mix    |

| <b>Table 1:</b> Industry tools which reach the Compl | which reach the Comple       | te Pl | tform-     | based       | l desi       | gn co | ncept | lete Platform-based design concepts.( <b>DDF</b> : Dynamic Dataflow, <b>DE</b> : | : Dataflow, <b>DE</b> :                         |        |

| DE:                                                                                                     |                                                                                                                        |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| ble 1: Industry tools which reach the Complete Platform-based design concepts.(DDF: Dynamic Dataflow, L | screte Events <b>FSM</b> : Finite State Machine <b>SDF</b> : Syncronous Dataflow <b>TLM</b> : Transaction Level Model) |

| На                                                                                                      | Di                                                                                                                     |

| Company                    | Tool                         | Strengths                                                                                                                                                                                                             | Weaknesses                                                                                                                                                      |

|----------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CoFluent Design            | CoFluent Studio              | <ul> <li>The tools is based on MCSE methodology, which is a Platformbased methodology.</li> <li>The tool generates SystemC code from the models made.</li> <li>The mapping action is made by drag and drop</li> </ul> | <ul> <li>It has generic models to aluate the platform where the functionality will be implemented.</li> <li>It cannot generate VHDL or Verilog Code.</li> </ul> |

| MLDesign Technolo-<br>gies | MLDesigner                   | - The tool provides a large range of<br>Model of Computation to model the<br>functional and the architecture of the<br>system.                                                                                        | - It cannot generate neither C/C++<br>Code nor VHDL/Verilog Code.                                                                                               |

| Mirabilis Design           | Visual Sim product<br>family | <ul> <li>The extensive library that the designer can reuse in order to build his own designs.</li> <li>Possibility to use the tools by a simple internet browser.</li> <li>HDL code generation.</li> </ul>            | - Few information available                                                                                                                                     |

| Synopsys                   | System Studio                | <ul> <li>Good library for Digital Signal Processing Systems</li> <li>HDL code generation.</li> </ul>                                                                                                                  | - Its focus is only on Digital Signal Pro-<br>cessing Systems.                                                                                                  |

|                            |                              |                                                                                                                                                                                                                       |                                                                                                                                                                 |

Table 2: Strengths and weaknesses in industrial tools.

| Company                                                                        | Tool                | Abstraction                                                                             | RTL Trans.         | Alg. Repr.                        | Domain |

|--------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------|--------------------|-----------------------------------|--------|

| U. of California, Berkeley                                                     | Metropolis          | Its own model language, fol-<br>lowing the TLM concepts.                                |                    | MoC                               | Mix    |

| Seul National Univ.                                                            | Peace               | Extended SDF, Extended<br>FSM                                                           | X                  | U                                 | Mix    |

| Vanderbilt Univ.                                                               | MIC                 | DSML                                                                                    |                    |                                   | Mix    |

| University of Amsterdam,<br>Leiden University and Delft<br>Univ. Of Technology | Artemis             | Khan process networks<br>(KPN)                                                          | Х                  | MATLAB, C++,<br>Perl, SystemC     | Media  |

| U. of Southern California<br>and Venderbilt University                         | Milan               | SDF, DDF                                                                                |                    | C, Java, MATLAB,<br>SystemC, VHDL | Mix    |

| Table 3: Acad                                                                  | demic tools which 1 | <b>Table 3:</b> Academic tools which reach the Complete Platform-based design concepts. | ased design concep | ts.                               |        |

|        | concept                                   |

|--------|-------------------------------------------|

| •      | design                                    |

| -      | -Dased                                    |

| J 1 10 | latiorm-pased                             |

|        | ine Complete Platiorm-based design concep |

|        |                                           |

| -      | react                                     |

|        | lemic tools which react                   |

| -      | demic tools                               |

| •      | emic                                      |

| -      | Acade                                     |

|        | lable 3:                                  |

| Company                                                              | Tool                                             | Strengths                                                                                                                                | Weaknesses                                                  |

|----------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| U. of California,<br>Berkeley                                        | Metropolis                                       | <ul> <li>It uses the same language to describe functionality and architecture.</li> <li>Constrains can be expressed using its</li> </ul> | It is not clear how the mapping can be<br>made.             |

|                                                                      |                                                  | model language.                                                                                                                          |                                                             |

| Seul National Univ.                                                  | Peace                                            | - It provides an easy way to integrate<br>with other tools. (Using XML)                                                                  | -The mapping is made by testing and<br>error correction.    |

|                                                                      |                                                  | <ul> <li>It guides the architecture exploration<br/>in order to make a good mapping.</li> <li>HDL code generation.</li> </ul>            |                                                             |

| Vanderbilt Univ.                                                     | MIC (GME, GreAT,<br>Desert UDM OTIF)             | - The designer can create its own lan-<br>puage design and its own design flow                                                           | - The designer has to create the tool (tool chain)          |

|                                                                      |                                                  | - It is possible to do a previous auto-<br>matic exploration to reduce the plat-                                                         |                                                             |

| University of Amster-<br>dam, Leiden Univer-<br>sity and Delft Univ. | Artemis (Compaan<br>and Laura, Sesame,<br>Spade) | - It allows transforming a sequential model into concurrent model.                                                                       | - The tool's focus is Multimedia appli-<br>cations.         |

| Of Technology                                                        |                                                  | - Mapping action is made using multi-<br>objective optimization.                                                                         |                                                             |

| U. of Southern Cali-<br>fornia and Venderbilt<br>University          | Milan                                            | - They introduce the concept of Con-<br>strain Model in order to help to the<br>mapping process.                                         | The development of this tool depends<br>of the MIC support. |

|                                                                      |                                                  | - The mapping exploration is made<br>by using Ordered Binary Decision Dia-<br>gram.                                                      |                                                             |

|                                                                      |                                                  |                                                                                                                                          |                                                             |

**Table 4:** Strengths and weaknesses in Academic tools.

# 3.2 Model Based System Design and Model Driven Architecture

There is not a complete tool which can develop all the steps of the methods proposed in Model Based System Design. Different methodologies are described in [Est08] and they use different tools to support them. Estefan relates Model Based System design (MBSD) with MDA based on a work done by Cloutier [Clo08], who said that the system engineering productivity increases 10-20% using of MDA, compared with existing system engineering methods.

Object Management Group (OMG) proposes to use standard language such as UML and SysML to represent the system's concepts in a model based on these languages and implement each step of the MDA method in these languages. There are many tools which help to create models in these languages and we only mention the most representatives, specially tools which support SysML, which is our language base of our work.

In [For09], there is a list of the tools which allow creating system models based on SysML. We classify them in two groups: Commercial and Open source tools. Commercial tools are tools developed by the industry which source code is property of the enterprise which develops the tool. Nobody can access to them, and the user has to pay to use it. In the other hand, open source tools are tools developed by the industry or academy, the source code is accessible by everybody and the user has not to pay to use it.

## 3.2.1 Commercial Tools

## 3.2.1.1 IBM Rational Rhapsody and IBM Rational Tau

Rhapsody is a tool which enables to the designer, system designer and software designer, to create real-time and embedded system model based on UML/SysML. This tool has the capability to do the traceability between the stakeholder requirements and the elements of the model using its link with tools such as DOORS. Rhapsody also has an environment to simulate the model behavior which allows to the designer to verify early their designs and also it allows validating them with the stakeholder in an easy way. This tools also helps to generate documentation automatically in different formats such as HTML, rich text format and Microsoft PowerPoint. Finally Rhapsody can generate code in C, C++, Java and Ada languages for 8, 16 and 64 bit applications [IBM09b].

Tau is other IBM tool which has the same purpose of Rhapsody, just its focus is the design of complex systems [IBM09a]. UML is its main graphical language, and also it has a SysML plugin, through this is not used too much. This tool, as well as Rhapsody, can be generate documentation, simulate and test models and link requirements with model elements. An important feature in this tool is the possibility to collaborate with teams and organizations.

#### 3.2.1.2 MagicDraw

MagicDraw is a No Magic Inc. tool which is used to model systems in UML mainly. This tool has a SysML plugin which is developed with the help of INCOSE, which is one of the SysML standard developers. MagicDraw has connections with Microsoft Excel, MATLAB and Mathematica in order to execute the simulation of the system model built in SysML using ParaMagic plugin [Inc09b]. As Rhapsody and Tau, it binds the requirements with the model elements, using Cameo DataHub [Inc09a]. This tools provides two profiles to extend the description that the designer can make in SysML: MARTE and SYSMOD. MARTE profile [OMG08b] is an extension of UML for the development of real-time and embedded systems, which can be used in SysML. SYSMOD is an extension proposed in [Wei08] to describe more detailed a model designed in SysML and it is used in a methodology also proposed in [Wei08]. MagicDraw has the capacity to generate Java code using Xholon [Pri09] and C/C++ code using SinelaboreRT [Sin09].

#### 3.2.1.3 Enterprise Architecture

Developed by Sparx Systems and, as MagicDraw, it is focus on the system modeling on UML and it has the possibility to use SysML using a plugin developed by them.

Unlike the previous tools, it only gives the elements to model in SysML, but it does not enable to generate specific code to simulate the behavior of the system or to link the requirements from other tools to the requirements diagram in SysML like MagicDraw.

This tool is very used in the software development, although in the case of complex system is too limited and it only can be used to document a system design.

## 3.2.2 Open Source Tools

## 3.2.2.1 *Topcased*

Topcased is a toolkit dedicated to realization of critical embedded systems [Top09]. This tool aims to develop editors for specification, design and implementation of systems, to integrate formal-verification tools, and to generate code and documentation automatically to the implementation of systems [FV09].

AdaCore, Airbus France, Anyware Technologies, Atos Origin, CNES, Laboratoire d'analyse et d'architecture des systmes, Communication & Systmes, EADS Astrium, ENSIETA, ESEO, ENSEEIHT, Ellidiss Technologies, Fdration de Recherche en Informatique et Automatique CNRS FR 2238, INSA, Institut de Recherche en Informatique de Toulouse, Institut National de Recherche en Informatique et en Automatique, MICOUIN Consulting for Innovative Systems Engineering, Laboratoire Modelisation Intelligence Processus Systmes (Universit de Haute Alsace), ONERA, Rockwell Collins, Sodifrance, Siemens VDO, Sogeti High Tech, TNI-Software, Tectosages, Thales Avionics, UFSC DAS, Universit Paul Sabatier are the partners in the developing of this project.

This platform has model editors such as UML, SysML, AADL, SAM which are used to describe the specification of a system. By transformation, the system model can be verified by other simulation or analysis tools using a pivot language such as FIACRE [Berthomieu08], which does the bridge between the model tools and the verification tools. The model can also be transformed to code, e.g. UML to C or UML to Java. Aditionally, there is a tool which made the transformation from the model to natural language in order to create the supporting documentation to the development of the system.

# 3.3 HiLeS Method tool

## 3.3.1 HiLeS Designer

This tool is developed by the Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) and the Universidad de los Andes. HiLeS Designer is the tool which supports the HiLeS method explained in the chapter before.

The objectives of HiLeS Designer are:

- Build system design models using HiLeS formalism.

- Generate automatically a virtual prototype in VHDL-AMS.

- Verify the system design behavior by simulation.

- Verify formally the logical system design by TINA.

- Reuse designs.

At the present, this tool is being redefined to follow the new conceptions in model driven design. The group in charge to develop this tool wants to add new features as the system design representation using general language model such as SysML and UML. In these languages, the designer can make the first description of the system and transforms the SysML or UML model to HiLeS in order to verify the model before to continue with the details of a system design. This is a path to give execution properties to the specification described in SysML and UML; it also allows the designer to make an early verification before to go down abstraction levels in its design. This transformation can also help to search quickly a physical system which matches with the features which are represented in the virtual prototype generated by this tool, especially if the physical system was designed using this tool.

## 3.4 Conclusion