### Modular Multilevel Converters for Power Transmission Systems

by

Ramiar Alaei

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Energy Systems

Department of Electrical and Computer Engineering

University of Alberta

$\ensuremath{\mathbb{C}}$ Ramiar Alaei, 2017

### Abstract

In this research, novel Modular Multilevel Converters (MMCs) intended for various type of power transmission systems are studied. Currently, the MMC, which is built based upon stack of identical half- or full-bridge submodules (SMs), is the dominant Voltage Source Converter (VSC) topology for power transmission systems, because of its salient features including (i) scalability/modularity to meet any voltage/powerlevel requirements, (ii) excellent harmonic performance, (iii) very high efficiency, and (iv) redundancy in the converter configuration. The application of power converters could be extended to novel transmission schemes that might be under research, such as High-frequency Half-Wavelength (HFHW) Transmission Line. Therefore, introducing suitable power converter topologies not only improves the developed technologies, but also facilitates the implementations of novel related ideas.

This research introduces three topologies of MMCs optimized for various type of power transmission systems. The first two topologies are intended for AC/AC applications such as HFHW system and the third converter is proposed for HVDC systems. Compared to conventional MMC, the proposed converters have fewer power switches with a major portion of them operating in soft-switching mode. Beside the theoretical studies, the viability of the proposed topologies, as well as the effectiveness of the control strategy are confirmed by both simulation and experimental results. Furthermore, the economical aspect of HFHW power system is discussed and it is shown that this system can benefit from employing the proposed AC/AC converters.

### Preface

Chapter 2 of this thesis has been published as R. Alaei, S. A. Khajehoddin and W. Xu, "Sparse AC/AC Modular Multilevel Converter," *IEEE Transactions on Power Delivery*, vol. 31, no. 3, pp. 1195-1202, June 2016. and, R. Alaei, S. A. Khajehoddin and W. Xu, "Control and Experiment of AC/AC Sparse Modular Multilevel Converter," *IEEE Transactions on Power Delivery*, (Early Access DOI: 10.1109/T-PWRD.2016.2618935). I was responsible for proposing the topology, simulation and experimental analysis as well as the manuscript composition. Drs. Khajehoddin and Xu contributed to the manuscript edits.

### Acknowledgments

Firstly, I would like to express my sincere gratitude to my advisors Dr. Sayed Ali Khajehoddin and Prof. Wilsun Xu for their patience, motivation, insight and vast knowledge. Their guidance helped me through different phases of my research and writing of this thesis.

I would also like to acknowledge Prof. Yunwei (Ryan) Li and other members of my committee for their constructive comments and feedbacks.

I would like to offer my thanks to all graduate students in the uAPEL lab, especially Mohammad Ebrahimi, who was more than happy to share his invaluable knowledge with me during the experimental phase of my research.

Last but not the least, I would like to thank my parents for supporting me spiritually throughout writing this thesis and my life in general.

# Contents

| Abstract       |                                                   | ii   |

|----------------|---------------------------------------------------|------|

| Preface        |                                                   | iv   |

| Acknowledgn    | nents                                             | v    |

| List of Figure | es                                                | ix   |

| List of Tables | s                                                 | xiii |

| Acronyms       |                                                   | xiv  |

| 1 Introducti   | ion                                               | 1    |

| 1.1 High I     | Frequency Half-Wavelength Transmission Line       | 2    |

| 1.2 Existin    | ng High Power Voltage Source Converters           | 3    |

| 1.2.1          | Two-Level Voltage Source Converter                | 3    |

| 1.2.2          | Matrix Converter                                  | 4    |

| 1.2.3          | Conventional Multilevel Voltage Source Converters | 6    |

|                | 1.2.3.1 Diode-Clamped Converter                   | 6    |

|                | 1.2.3.2 Flying Capacitor Converter                | 7    |

|                | 1.2.3.3 Cascaded H-Bridge Converter               | 8    |

| 1.2.4          | Modular Multilevel Converter                      | 8    |

|                | 1.2.4.1 Principle of Operation                    | 8    |

|                | 1.2.4.2 Modulation Techniques                     | 10   |

|                | 1.2.4.3 Capacitor Voltage Balancing               | 11   |

| 1.3 Descri     | iption of the Proposed Converters                 | 14   |

|                | s Objectives                                      | 16   |

|                | s Outline                                         | 17   |

| <b>2</b> | Spa | rse Modular Multilevel Converter                      | 19               |  |  |  |  |

|----------|-----|-------------------------------------------------------|------------------|--|--|--|--|

|          | 2.1 | Introduction                                          | 19               |  |  |  |  |

|          | 2.2 | Principle of Operation                                | 20               |  |  |  |  |

|          |     | 2.2.1 Demonstration of a Single-phase 5-Level SMMC    | 24               |  |  |  |  |

|          |     | 2.2.2 ZVS of SMMC Unfolders                           | 27               |  |  |  |  |

|          |     | 2.2.3 Unidirectional SMMC                             | 30               |  |  |  |  |

|          | 2.3 | Capacitor Voltage Balancing                           | 32               |  |  |  |  |

|          |     | 2.3.1 The Impact of Frequency Ratio                   | 36               |  |  |  |  |

|          |     | 2.3.2 Voltage Gain Adjustment                         | 36               |  |  |  |  |

|          |     | 2.3.3 The Power Capability of SMMC                    | 42               |  |  |  |  |

|          | 2.4 | Control Strategy                                      | 43               |  |  |  |  |

|          | 2.5 | Simulation Results                                    | 46               |  |  |  |  |

|          | 2.6 | Experimental Results                                  | 50               |  |  |  |  |

|          | 2.7 | Summary                                               | 54               |  |  |  |  |

|          |     |                                                       |                  |  |  |  |  |

| 3        |     | Max AC/AC Multilevel Converter                        | 55               |  |  |  |  |

|          | 3.1 | Introduction                                          | 55<br>5 <i>c</i> |  |  |  |  |

|          | 3.2 | Principle of Operation                                | 56               |  |  |  |  |

|          | 0.0 | 3.2.1 Switching States of a 3-level Single-phase MMMC | 58               |  |  |  |  |

|          | 3.3 | Capacitor Voltage Balancing                           | 59               |  |  |  |  |

|          |     | 3.3.1 Voltage Gain Adjustment                         | 65               |  |  |  |  |

|          | 3.4 | Control Strategy                                      | 68               |  |  |  |  |

|          | 3.5 | Simulation Results                                    |                  |  |  |  |  |

|          | 3.6 | Experimental Results                                  | 72               |  |  |  |  |

|          | 3.7 | Summary                                               | 75               |  |  |  |  |

| 4        | Hig | h Frequency Half-Wavelength Transmission Line         | 76               |  |  |  |  |

|          | 4.1 | Introduction                                          | 76               |  |  |  |  |

|          | 4.2 | Half-Wavelength Transmission Line                     | 76               |  |  |  |  |

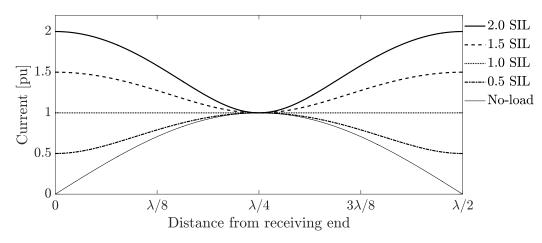

|          |     | 4.2.1 HWTL Voltage and Current Profiles               | 78               |  |  |  |  |

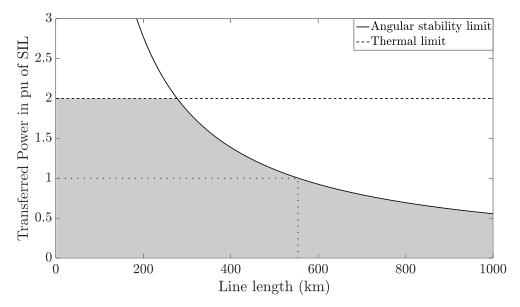

|          |     | 4.2.2 HWTL Loadability Limit                          | 81               |  |  |  |  |

|          |     | 4.2.3 Loadability of HWTL versus Conventional AC line | 82               |  |  |  |  |

|          | 4.3 | Other System Components                               | 84               |  |  |  |  |

|          | -   | 4.3.1 High Frequency Generator                        | 84               |  |  |  |  |

|          |     | 4.3.2 High Frequency Transformer                      | 86               |  |  |  |  |

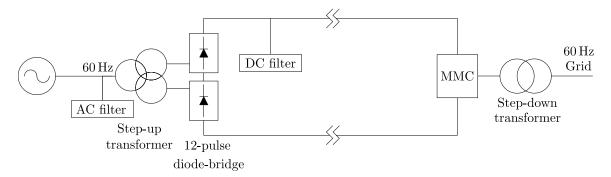

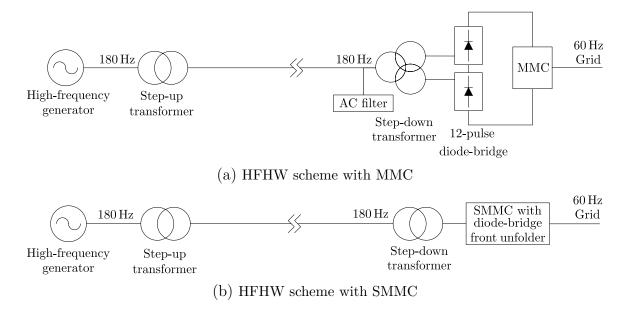

|          |     | 4.3.3 Unidirectional AC/AC Converter                  | 86               |  |  |  |  |

|          | 4.4 | Economical Study                                      | 86               |  |  |  |  |

|          |     | 4.4.1 Converter Station                               | 87               |  |  |  |  |

|          |     |                                                       |                  |  |  |  |  |

|          |       | 4.4.2 Power Plant                                                                              | 89  |

|----------|-------|------------------------------------------------------------------------------------------------|-----|

|          |       | 4.4.2.1 Turbine-Set $\ldots$                                                                   | 90  |

|          |       | $4.4.2.2  \text{Transformer}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 90  |

|          |       | 4.4.3 Transmission Line                                                                        | 91  |

|          | 4.5   | Summary                                                                                        | 92  |

| <b>5</b> | Seri  | es Hybrid Modular Multilevel Converter for HVDC System                                         | 94  |

|          | 5.1   | Introduction                                                                                   | 94  |

|          | 5.2   | Description of SHMMC                                                                           | 95  |

|          |       | 5.2.1 Zero-Crossing Circulating Current                                                        | 96  |

|          |       | 5.2.2 Switching States of 5-level Single-phase SHMMC                                           | 97  |

|          |       | 5.2.3 Component Comparison with Alternative Converters                                         | 97  |

|          |       | 5.2.4 Capacitor Voltage Balancing                                                              | 99  |

|          | 5.3   | Power Capability of the Proposed Converter                                                     | 102 |

|          | 5.4   | Control Strategy                                                                               | 104 |

|          | 5.5   | Simulation Results                                                                             | 105 |

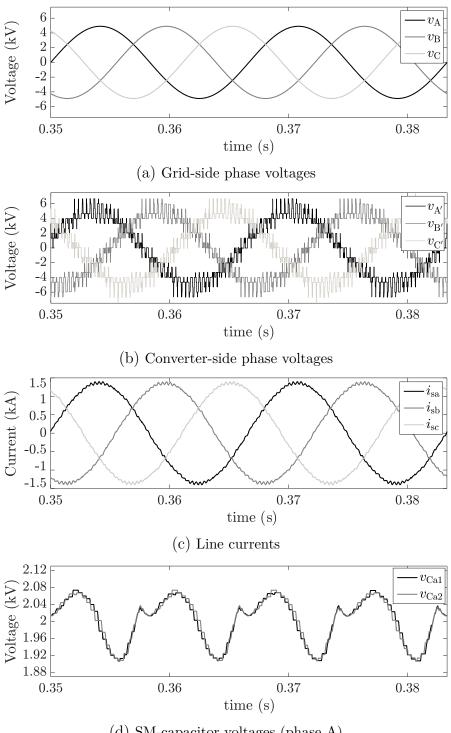

|          |       | 5.5.1 Steady-State Simulation Results                                                          | 107 |

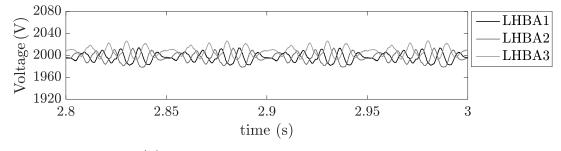

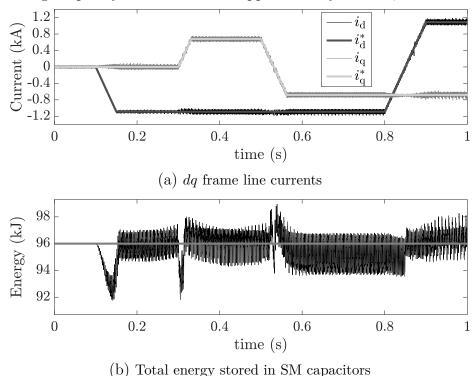

|          |       | 5.5.2 Transient Simulation Results                                                             | 109 |

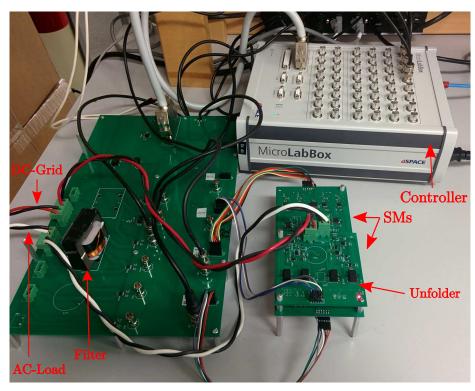

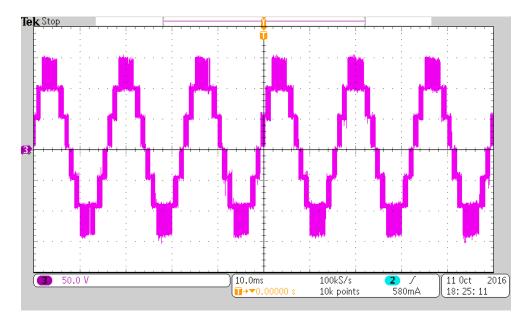

|          | 5.6   | Experimental Result                                                                            | 110 |

|          | 5.7   | Summary                                                                                        | 114 |

| 6        | Sun   | nmary and Future Works                                                                         | 115 |

|          | 6.1   | Summary of Contributions                                                                       | 115 |

|          | 6.2   | Suggested Future Work                                                                          | 116 |

| Bi       | bliog | graphy                                                                                         | 120 |

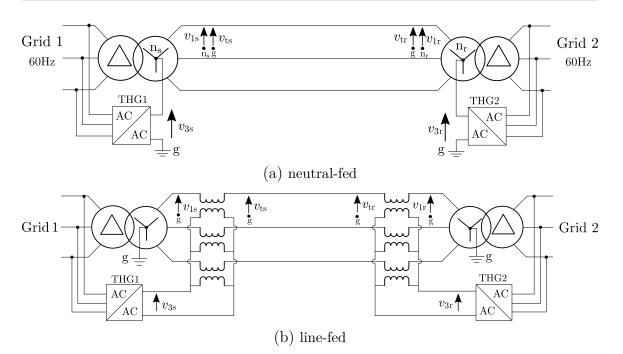

| A        | Vol   | tage Sharing in Series-connected Semiconductors                                                | 1   |

|          | A.1   | Introduction                                                                                   | 1   |

|          | A.2   | Steady State Voltage Sharing                                                                   | 1   |

|          | A.3   | Transient Voltage Sharing                                                                      | 4   |

# List of Figures

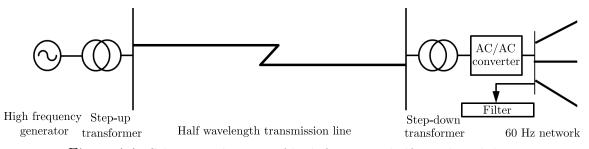

| 1.1  | Schematic diagram of high-frequency half-wavelength line              | 3  |

|------|-----------------------------------------------------------------------|----|

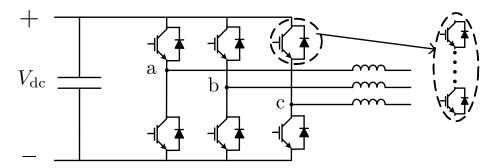

| 1.2  | Schematic diagram of a 2-level high power voltage source inverter     | 4  |

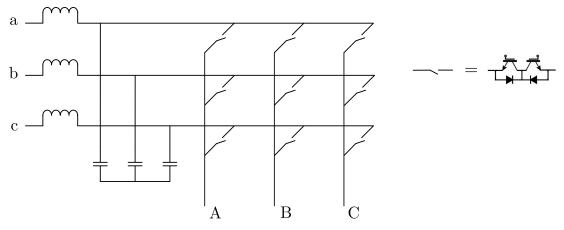

| 1.3  | Conventional Direct Matrix Converter                                  | 5  |

| 1.4  | Conventional Indirect Matrix Converter                                | 6  |

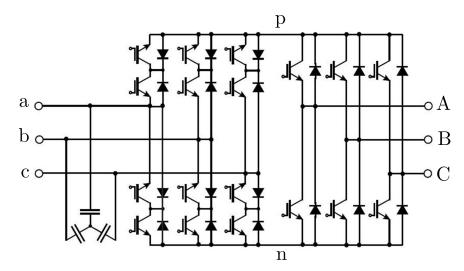

| 1.5  | Different types of conventional multilevel converters                 | 7  |

| 1.6  | Three phase conventional B2B-MMC.                                     | 9  |

| 1.7  | Classification of multilevel converter modulation techniques          | 11 |

| 1.8  | Multilevel phase-shifted carrier-based technique                      | 12 |

| 1.9  | Nearest level control technique.                                      | 12 |

| 1.10 | Capacitor charging/discharging based on HBSM's status                 | 13 |

| 1.11 | Capacitor charging/discharging based on FBSM's status                 | 14 |

| 1.12 | Single-phase sparse modular multilevel converter                      | 15 |

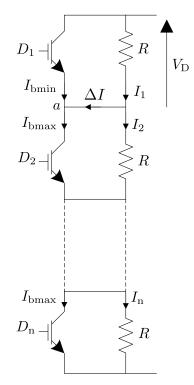

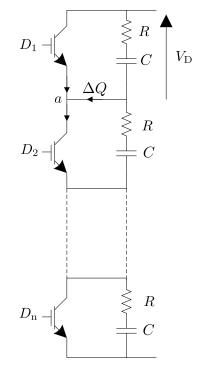

| 2.1  | Schematic diagram of a single-phase <i>n</i> -level SMMC              | 20 |

| 2.2  | Schematic diagram of a three-phase SMMC.                              | 21 |

| 2.3  | Shorting capacitor $C_2$ without using isolating transformer          | 22 |

| 2.4  | Zero-crossing circulating current in 5-level SMMC                     | 23 |

| 2.5  | Schematic diagram of SMMC with modified FBU                           | 23 |

| 2.6  | Description of zero-crossing transition in FBU                        | 26 |

| 2.7  | Schematic diagram of a 5-level SMMC leg.                              | 27 |

| 2.8  | Illustration of switching states 4-6 in a 5-level SMMC                | 28 |

| 2.9  | Schematic diagram of HBU switching transition.                        | 29 |

| 2.10 | Unfolder transition (a) lagging current (b) leading current           | 29 |

| 2.11 | High frequency half-wavelength transmission scheme with unidirec-     |    |

|      | tional SMMC                                                           | 31 |

| 2.12 | One phase of unidirectional SMMC with diode-bridge front unfolder.    | 31 |

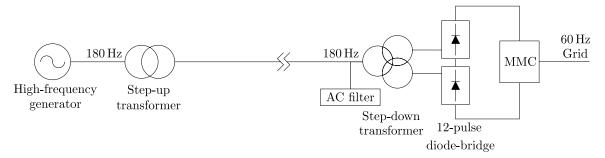

| 2.13 | High frequency half-wavelength transmission scheme with MMC           | 32 |

| 2.14 | Simplified schematic diagram of a single-phase SMMC                   | 32 |

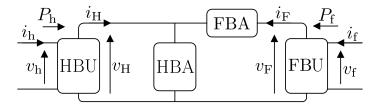

| 2.15 | The value of $A_1$ and $A_2$ based on $\omega_{\rm h}/\omega_{\rm f}$ | 35 |

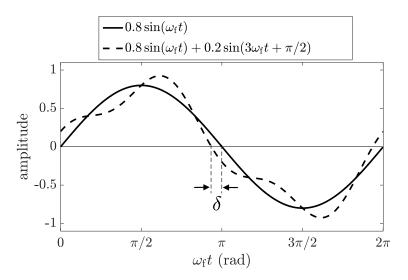

| 2.16 | Adding third harmonic voltage shifts the zero-crossing point 39                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

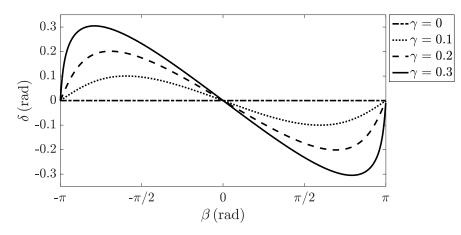

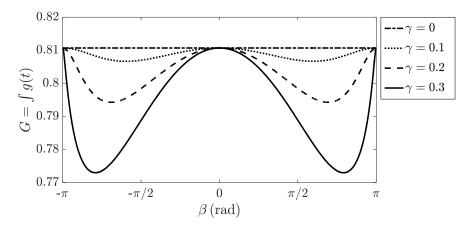

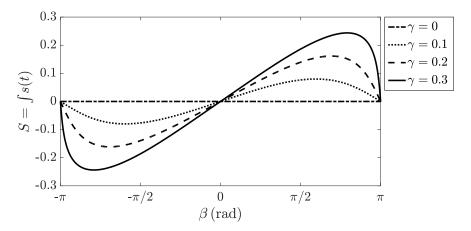

| 2.17 | The value of $\delta$ in regards with $\beta$                                                                                                                  |

| 2.18 | The impact of third harmonic injection on the function $G$ 40                                                                                                  |

| 2.19 | The impact of third harmonic injection on the function $S$ 40                                                                                                  |

| 2.20 | The voltage gain in regards with $\gamma$ ( $\beta = -0.8\pi$ )                                                                                                |

| 2.21 | The voltage gain versus $\gamma$ ( $\beta = 0.8\pi$ )                                                                                                          |

| 2.22 | Simplified single-line diagram of converter-grid circuit                                                                                                       |

|      | The power capability chart of SMMC                                                                                                                             |

| 2.24 | Required output voltage in different power factor (inverter mode) 43                                                                                           |

|      | The schematic diagram of control strategy                                                                                                                      |

|      | The schematic diagram of the current controller                                                                                                                |

| 2.27 | The schematic diagram of HBA Energy Balancing unit                                                                                                             |

| 2.28 | The schematic diagram of FBA Energy Balancing unit                                                                                                             |

|      | Voltage and current waveforms                                                                                                                                  |

|      | Voltage and current waveforms                                                                                                                                  |

| 2.31 | Average HBA and FBA capacitor voltages                                                                                                                         |

|      | Converter transient waveforms during power variation                                                                                                           |

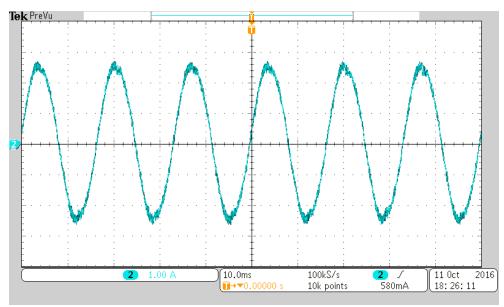

|      | A view of the experimental setup                                                                                                                               |

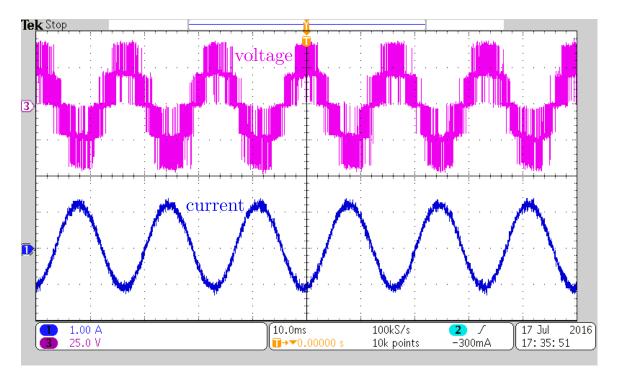

|      | Converter's HB-side waveforms in steady-state condition                                                                                                        |

|      | Converter's FB-side waveforms in steady-state condition                                                                                                        |

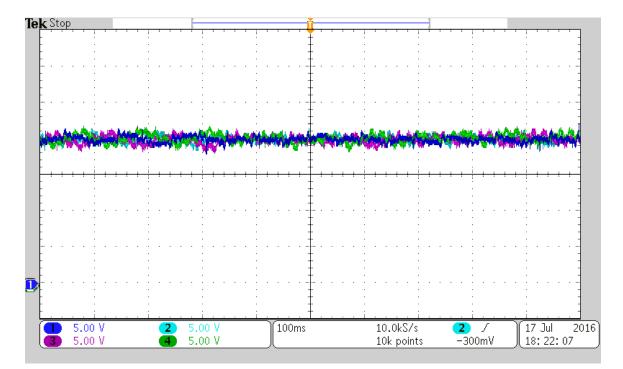

|      | Dynamic response of the converter to the load change                                                                                                           |

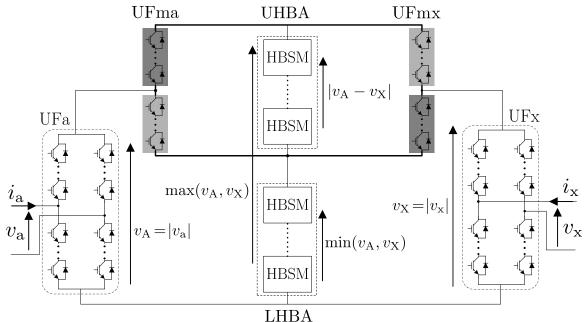

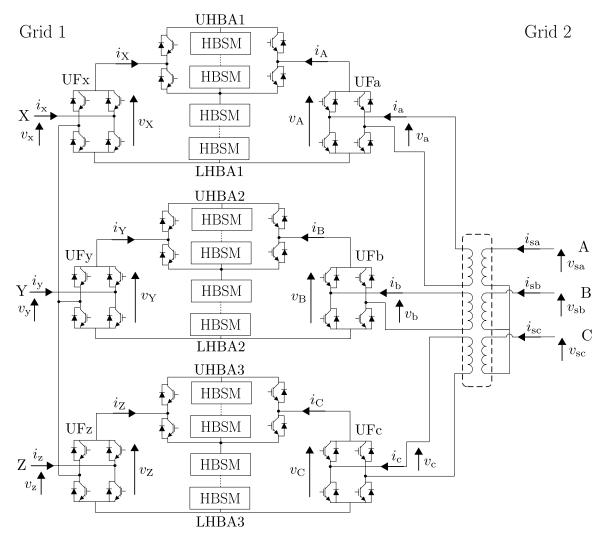

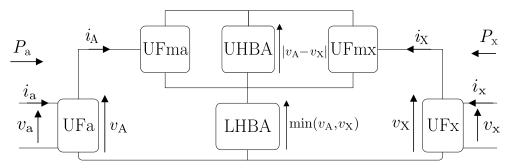

| 3.1  | The schematic diagram of single-phase <i>n</i> -level MMMC                                                                                                     |

| 3.2  | The schematic diagram of 3-phase MMMC                                                                                                                          |

| 3.3  | The schematic diagram of single-phase 3-level MMMC                                                                                                             |

| 3.4  | Simplified schematic diagram of a single-phase MMMC                                                                                                            |

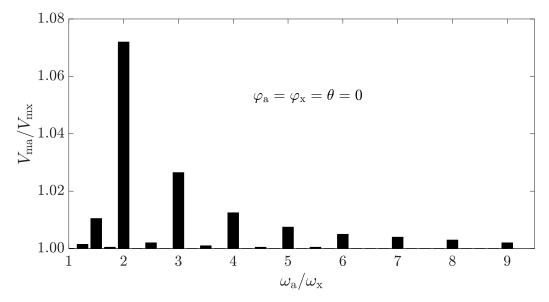

| 3.5  | The voltage gain of MMMC versus frequency ratio                                                                                                                |

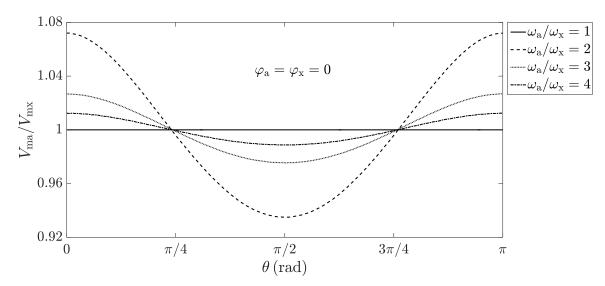

| 3.6  | The voltage gain of MMMC versus $\theta$ (rad)                                                                                                                 |

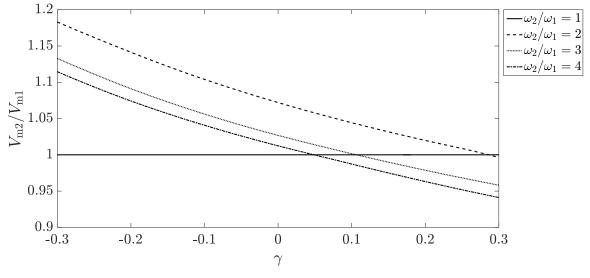

| 3.7  | The voltage gain of MMMC versus $\gamma$                                                                                                                       |

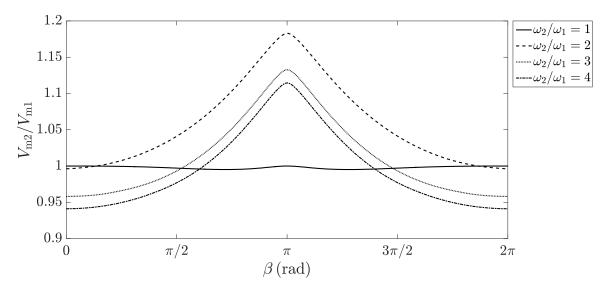

| 3.8  | The voltage gain of MMMC versus $\beta$                                                                                                                        |

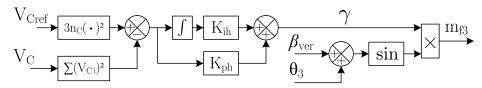

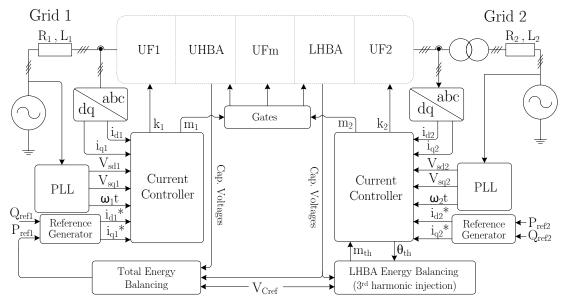

| 3.9  | The schematic diagram of control strategy. $\dots \dots \dots$ |

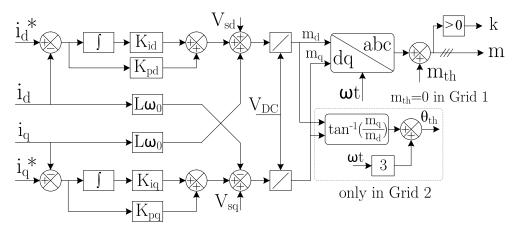

| 3.10 | The schematic diagram of the current controller                                                                                                                |

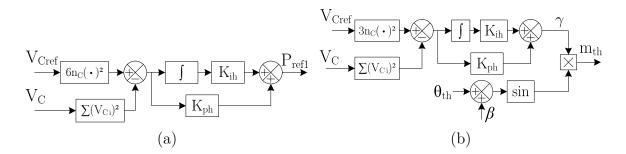

|      | (a) Total energy balancing unit (b) LHBA energy balancing unit 69                                                                                              |

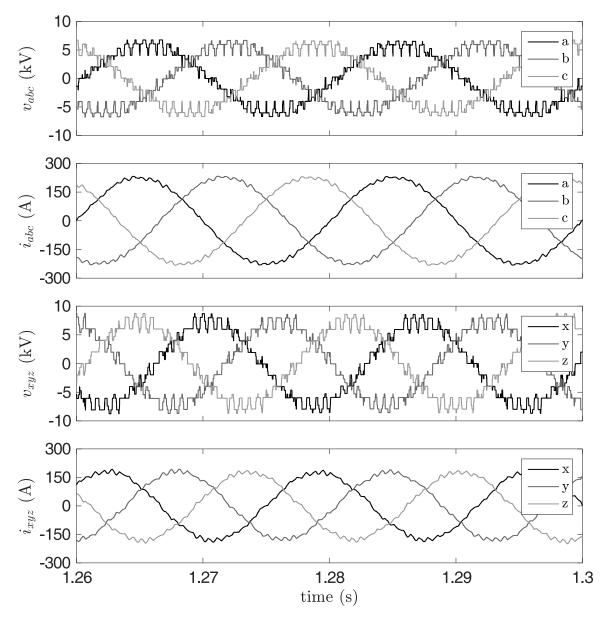

|      | Steady-state simulation results                                                                                                                                |

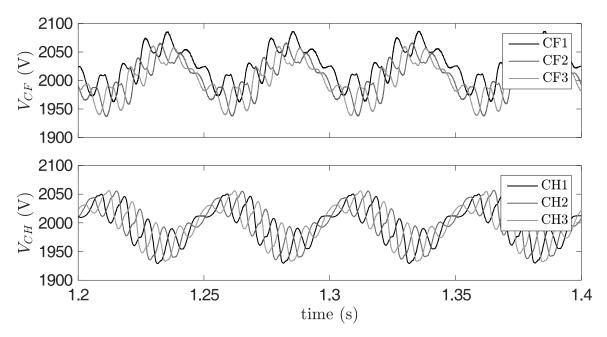

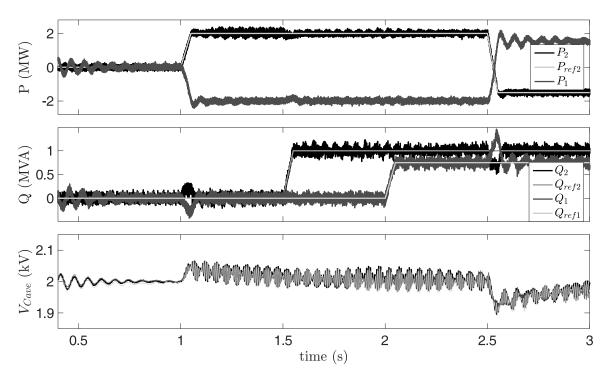

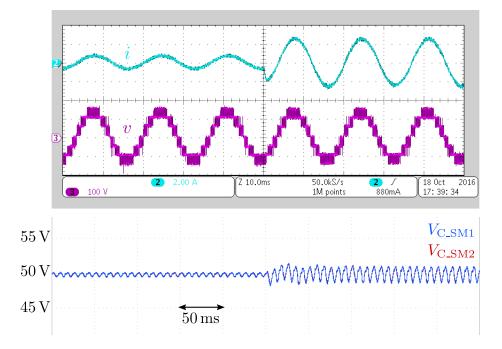

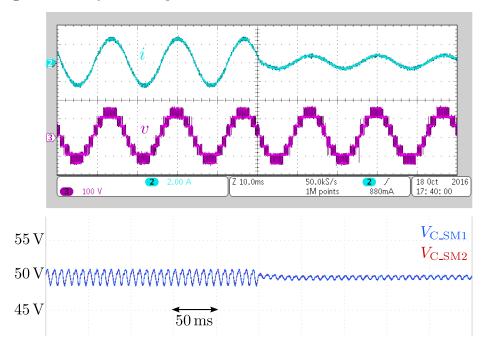

|      | Average arm capacitor voltages (steady state).       72                                                                                                        |

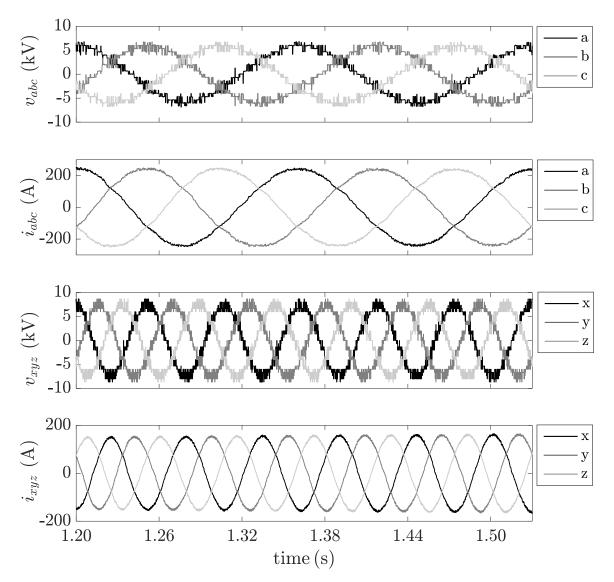

|      | Converter transient response                                                                                                                                   |

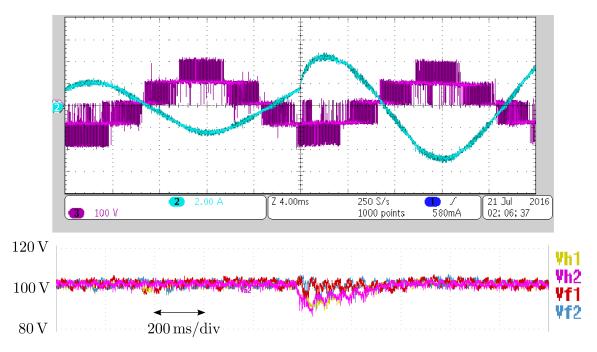

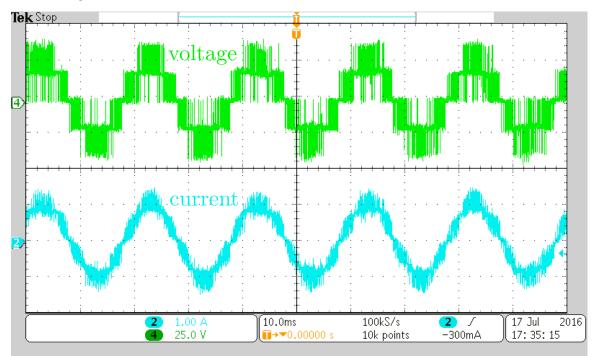

|      | Converter's supply-side waveforms in steady-state condition 74                                                                                                 |

|      |                                                                                                                                                                |

| 3.16 | Converter's load-side waveforms in steady-state condition                                                                                                      |

| 3.17 | Capacitor voltages in steady-state condition                                      | 75   |

|------|-----------------------------------------------------------------------------------|------|

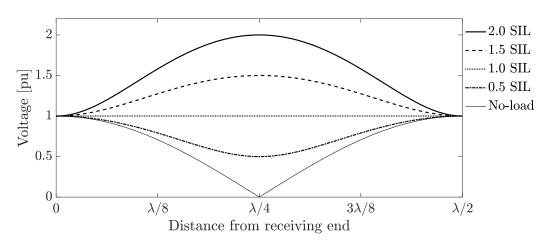

| 4.1  | Voltage profile in HWTL in regards to different load levels                       | 80   |

| 4.2  | Current profile in HWTL in regards to different load levels                       | 80   |

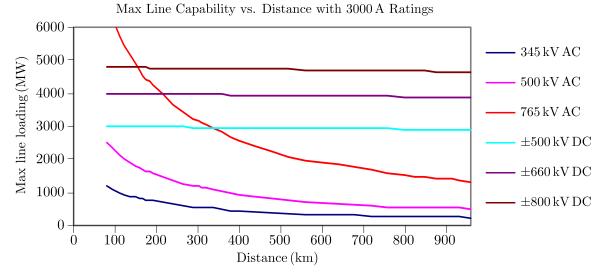

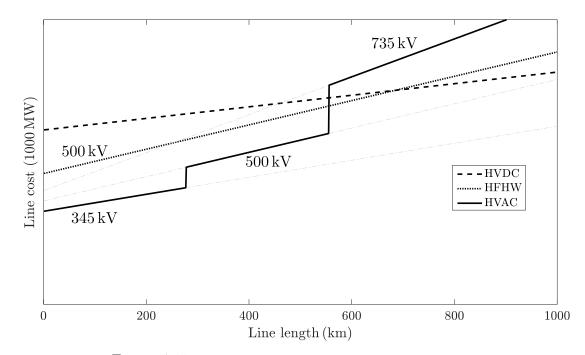

| 4.3  | Loadability curves of AC transmission line                                        | 84   |

| 4.4  | The unidirectional HVDC transmission scheme.                                      | 87   |

| 4.5  | Different transmission lines with their converters.                               | 88   |

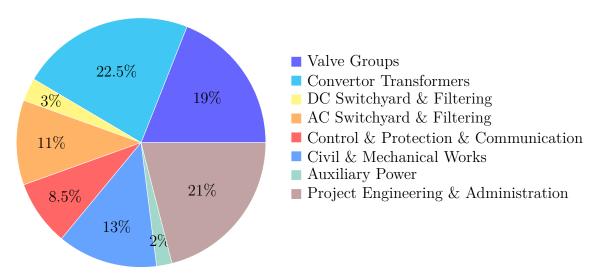

| 4.6  | Cost structure of a back-to-back HVDC station.                                    | 88   |

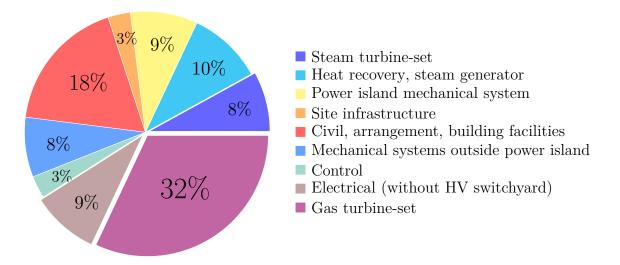

| 4.7  | Breakdown of the capital cost for combined-cycle power plant                      | 89   |

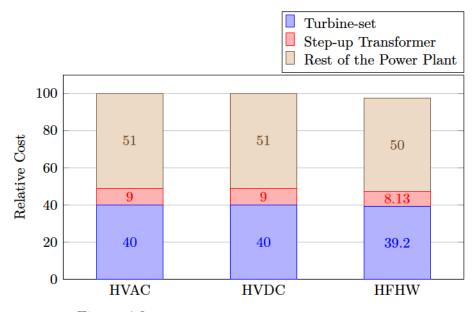

| 4.8  | Relative power plant cost breakdown.                                              | 91   |

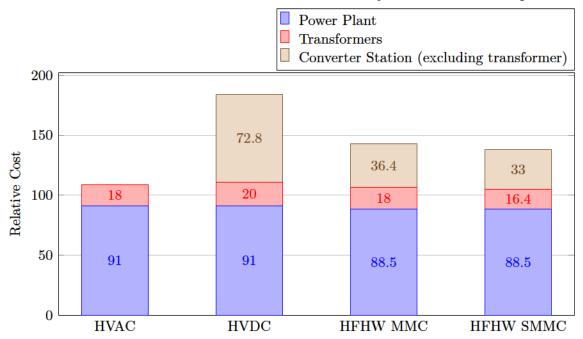

| 4.9  | Relative terminal cost breakdown of different transmission systems.               | 92   |

| 4.10 | Transmission line capability versus distance.                                     | 93   |

| 4.11 | Transmission line capability versus distance.                                     | 93   |

| 5.1  | The schematic diagram of back-to-back SHMMC.                                      | 95   |

| 5.2  | Zero-crossing circulating current in one phase of the converter                   | 97   |

| 5.3  | The schematic diagram of 5-level single-phase converter                           | 98   |

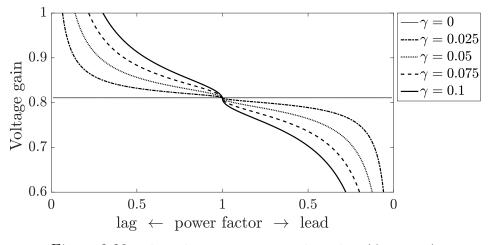

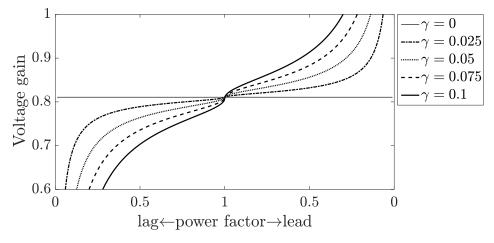

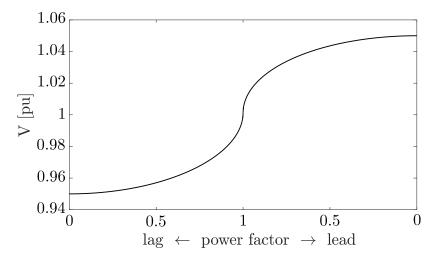

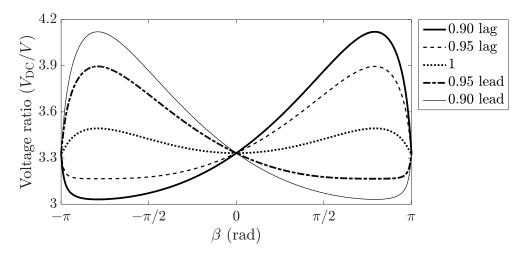

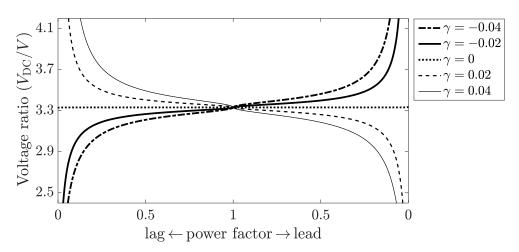

| 5.4  | Voltage gain in terms of different $\beta$ and power factor ( $\gamma = 0.3$ )    | 101  |

| 5.5  | Voltage gain in terms of different $\gamma$ and power factor ( $\beta = 0.8\pi$ ) | 102  |

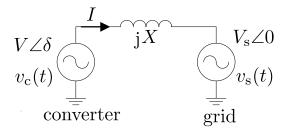

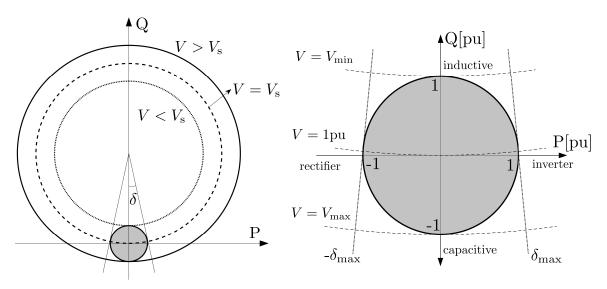

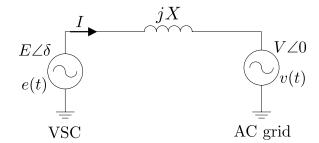

| 5.6  | Simplified single-line diagram of converter-grid circuit.                         | 102  |

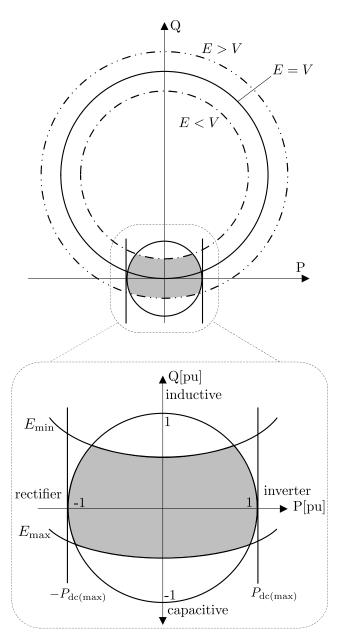

| 5.7  | PQ chart of the converter considering VSC limitation                              | 103  |

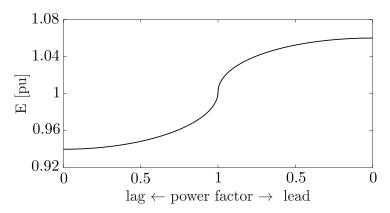

| 5.8  | Required converter's voltage in different power factor (inverter mode).           | 104  |

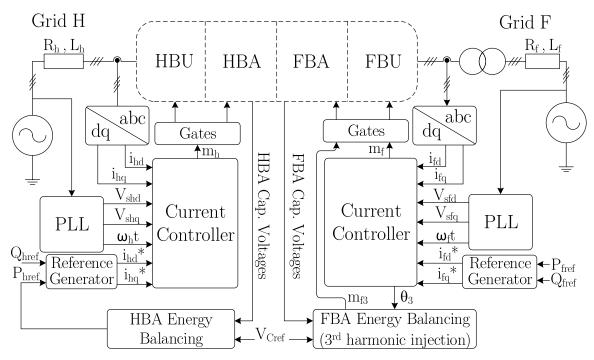

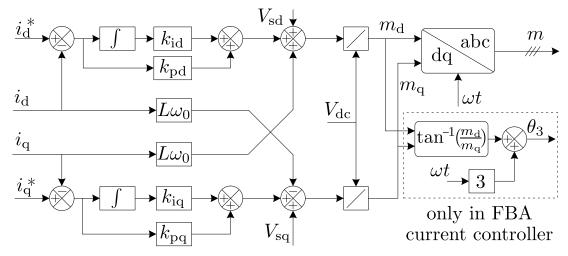

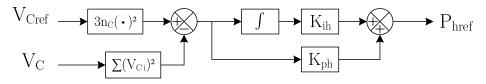

| 5.9  | The schematic diagram of the control strategy.                                    | 106  |

| 5.10 |                                                                                   | .107 |

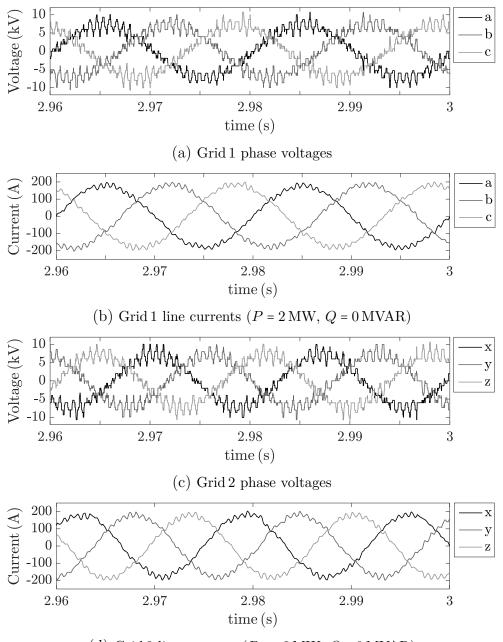

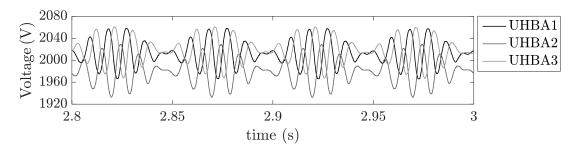

| 5.11 | Steady-state simulation results ( $P = 10 \text{ MW}, Q = 0 \text{ MVAR}$ )       | 108  |

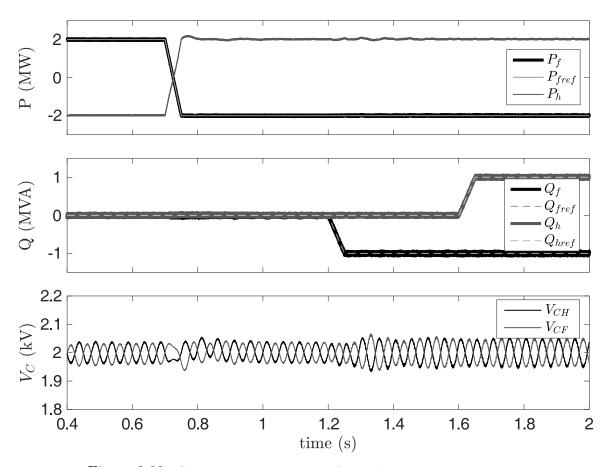

| 5.12 | Transient simulation results.                                                     | 110  |

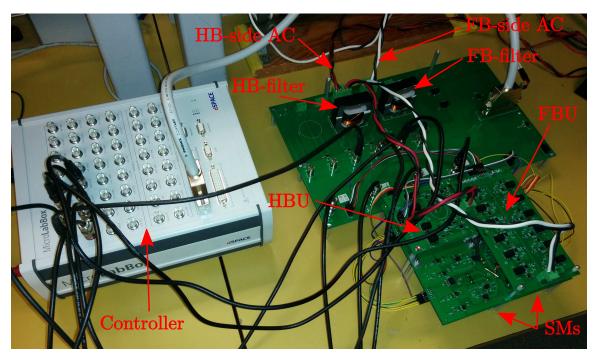

| 5.13 | A view of the experimental setup                                                  | 111  |

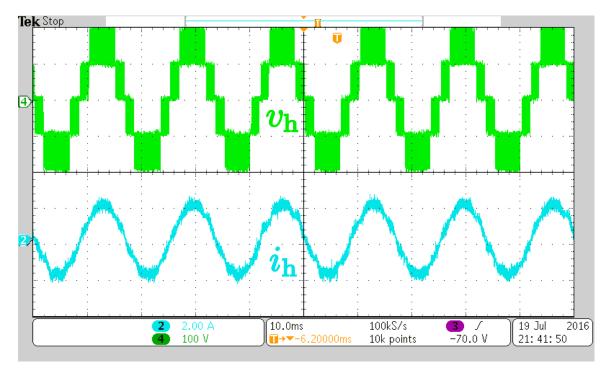

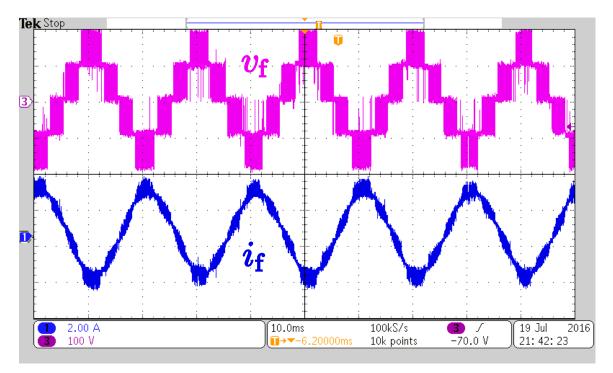

| 5.14 | Converter's AC-side voltage in steady-state condition                             | 112  |

| 5.15 | Converter's AC-side current in steady-state condition.                            | 112  |

| 5.16 | Dynamic response of the converter to the sudden load decrease                     | 113  |

| 5.17 | Dynamic response of the converter to the sudden load increase                     | 113  |

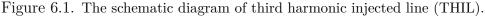

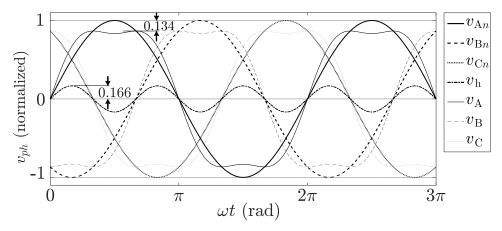

| 6.1  | The schematic diagram of third harmonic injected line (THIL)                      | 117  |

| 6.2  | Decreasing voltage peak amplitude by third harmonic injection                     | 117  |

| 6.3  | Schematic diagram of the modified THIL                                            | 118  |

| A.1  | Collector forward blocking I-V characteristics of two series devices              | 2    |

| A.2  | Shunt resistors for voltage equalization in off-state                             | 3    |

| A.3  | Reverse recovery current and voltage for two mismatched series devices.           | 4    |

| A 4 | 01    | • • • •        | · · ·        | 1.1         | 1.       | 1.       |      | -            |

|-----|-------|----------------|--------------|-------------|----------|----------|------|--------------|

| A.4 | Shunt | capacitors for | or transient | reverse blo | ocking v | voltage. | <br> | $\mathbf{C}$ |

# List of Tables

| 2.1 | Comparison of MMC and SMMC Component Count                                   | 24  |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Valid Switching States of a 5-level SMMC                                     | 25  |

| 2.3 | Component Count of Two Converters for HFHW Scheme                            | 32  |

| 2.4 | Simultion Parameters                                                         | 46  |

| 2.5 | Experimental Parameters                                                      | 51  |

| 3.1 | Comparison of MMC and MMMC Component Count                                   | 58  |

| 3.2 | Switching States of a 3-level MMMC                                           | 59  |

| 3.3 | Simulation Parameters                                                        | 70  |

| 3.4 | Experimental Parameters                                                      | 72  |

| 4.1 | Line Length Regarding Generator's Number of Pole $(P)$ & Speed $(N_{\rm s})$ | 85  |

| 5.1 | Switching States of a 5-Level SHMMC                                          | 98  |

| 5.2 | Component Count Comparison (equal DC-link voltage)                           | 98  |

| 5.3 | Simulation Parameters                                                        | 109 |

| 5.4 | Experimental Parameters                                                      | 111 |

# Acronyms

| B2B            | Back-to-Back                             |

|----------------|------------------------------------------|

| CHBC           | Cascaded H-Bridge Converter              |

| DCC            | Diode-Clamped Converter                  |

| DMC            | Direct Matrix Converter                  |

| FACTS          | Flexible AC Transmission System          |

| $\mathbf{FB}$  | Full-Bridge                              |

| FBA            | Full-Bridge Arm                          |

| FBSM           | Full-Bridge Sub-Module                   |

| $\mathbf{FBU}$ | Full-Bridge Unfolder                     |

| FCC            | Flying Capacitor Converter               |

| FFTS           | Fractional Frequency Transmission System |

| HB             | Half-Bridge                              |

| HBA            | Half-Bridge Arm                          |

| HBSM           | Half-Bridge Sub-Module                   |

| HBU            | Half-Bridge Unfolder                     |

| HF             | High Frequency                           |

| HFHW           | High Frequency Half-Wavelength           |

| HVAC           | High Voltage Alternating Current         |

| HVDC                 | High Voltage Direct Current                  |

|----------------------|----------------------------------------------|

| HWTL                 | Half-Wavelength Transmission Line            |

| IGBT                 | Insulated-Gate Bipolar Transistor            |

| ILMC                 | Inverting Link Matrix Converter              |

| IMC                  | Indirect Matrix Converter                    |

| $\mathbf{MC}$        | Matrix Converter                             |

| MMC                  | Modular Multilevel Converter                 |

| MMMC                 | MinMax Multilevel Converter                  |

| NLC                  | Nearest Level Control                        |

| NPCC                 | Neutral-Point Clamped Converter              |

| PHMMC                | Parallel Hybrid Modular Multilevel Converter |

| $\operatorname{PLL}$ | Phase-Locked Loop                            |

| PWM                  | Pulse-Width Modulation                       |

| RMS                  | Root-Mean-Square                             |

| SHE                  | Selective Harmonic Elimination               |

| SHMMC                | Series Hybrid Modular Multilevel Converter   |

| SIL                  | Surge Impedence Loading                      |

| $\mathbf{SM}$        | Sub-Module                                   |

| SMC                  | Sparse Matrix Converter                      |

| SMMC                 | Sparse Modular Multilevel Converter          |

| SPWM                 | Sinusoidal Pulse-Width Modulation            |

| SVM                  | Space Vector Modulation                      |

| THG                  | Third Harmonic Generator                     |

| THIL                 | Third Harmonic Injected Line                 |

| TOC  | Total Owing Cost              |

|------|-------------------------------|

| USMC | Ultra Sparse Matrix Converter |

| VSC  | Voltage Source Converter      |

| VSI  | Voltage Source Inverter       |

| VSMC | Very Sparse Matrix Converter  |

| ZCS  | Zero Current Switching        |

| ZVS  | Zero Voltage Switching        |

# Chapter 1

# Introduction

High power Voltage Source Converters (VSCs) have been the focus of research and development for a few decades and have found many industrial applications such as renewable energy resource interfaces, Flexible AC Transmission System (FACTS) devices and High Voltage Direct Current (HVDC) lines. The application of high power converters could be also extended to novel transmission schemes such as High Frequency Half-Wavelength (HFHW) power transmission [1]. In order to achieve high power ratings and high voltage levels, a single semiconductor device would be insufficient. Therefore, to increase the power capability, a number of semiconductors are paralleled to increase the current capability or series-connected to increase the voltage ratings. When power semiconductors are connected in series for high-voltage operation, both steady-state and transient voltages must be shared equally among the individual series devices which is often challenging and costly. As a result, multilevel VSC topologies can be used in high power and high voltage applications, as they reach higher voltages by utilizing low voltage power semiconductor switches, while both steady-state and transient voltage sharing are guaranteed. Multilevel VSCs offer very low harmonic distortion and does not require bulk AC-side filters.

Currently, the Modular Multilevel Converter (MMC), which is built based upon stack of identical half- or full-bridge submodules (SMs), is the dominant VSC topology for power transmission systems, because of its salient features including (i) scalability/modularity to meet any voltage/power-level requirements, (ii) excellent harmonic performance, (iii) very high efficiency, and (iv) redundancy in the converter configuration [2–4].

This thesis focuses on introducing novel topologies of MMCs which offer the same advantages as conventional MMC with additional benefits such as lower switching losses and lower number of semiconductors. These converters are intended to operate in AC/AC transmission system such as HFHW and AC/DC systems such as HVDC lines. In total, three novel topologies are presented which their major portion of semiconductor devices operate in Zero Voltage Switching (ZVS) mode.

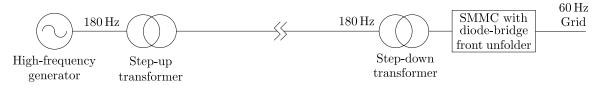

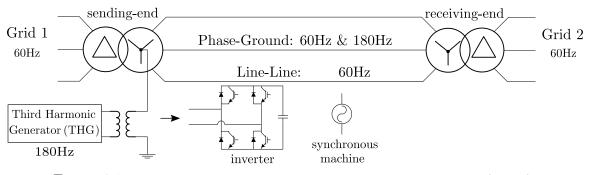

# 1.1 High Frequency Half-Wavelength Transmission Line

In this section, the HFHW system is briefly introduced. In a Half-Wavelength Transmission Line (HWTL), the line length between the sending and receiving ends is about half of the wavelength of the AC current carried by the line. Power transmission at this distance has one very attractive feature that the total line impedance becomes virtually zero (for lossless line). As a result, the sending end can be considered at close distance of the receiving end [5]. In recent years, the HWTL scheme regained the interest of industry and academia due to increasing construction of longer transmission lines [6–10]. In a 60 Hz power network, the half-wavelength will be a fixed length of 2500 km, which is too long and inflexible for practical use. In order to overcome this impediment, it is proposed to generate and transfer power at higher frequencies to shorten the half-wavelength distance, and interconnect the high-frequency portion to the rest of the power system using newly developed high power converters [1]. This scheme is called HFHW and is shown in Fig. 1.1. Unlike HVDC line which has one converter station at each end, the HFHW scheme requires only one converter station at the receiving end.

Figure 1.1. Schematic diagram of high-frequency half-wavelength line

### **1.2** Existing High Power Voltage Source Converters

In this section, different types of high power VSC topologies are reviewed. At the end, MMC is thoroughly discussed as one of the emerging viable options for high power applications.

#### 1.2.1 Two-Level Voltage Source Converter

The schematic diagram of simplified 2-level Voltage Source Inverter (VSI) intended for high power applications is shown in Fig. 1.2. The inverter is composed of six groups of power electronic switches, with a free-wheeling diode in parallel with each switch. There are two ways to increase the power rating of the inverter: i) parallel connection of semiconductor switches to increase the current capability or ii) series connection of switching to increase the voltage ratings. In both approaches, equal sharing of currents or voltages among devices is crucial. The importance and challenges of voltage sharing problem in series-connected switches in existing approaches are studied in Appendix A.

Figure 1.2. Schematic diagram of a 2-level high power voltage source inverter.

In order to decrease the harmonic distortion in a 2-level VSC, the electronic switches must be able to operate at a high switching frequency using Pulse-Width Modulation (PWM). Such high frequency switching current should be filtered before injected to AC-side using bulky filters on the AC-side. It must be added that for AC/AC applications, the Back-to-Back (B2B) version of this converter could be used with employing a DC-link to connect two AC sources [11]. Several topologies are proposed to reduce the component count of the this converter, yet they face limitations in the modes of operation and may require complex control systems [12–14].

#### 1.2.2 Matrix Converter

Matrix Converters (MCs) are able to connect two AC sources with different frequencies without using a DC link. They are further divided into two groups of classical Direct Matrix Converter (DMC) and Indirect Matrix Converter (IMC) with fictitious DC link. A conventional DMC is an array of nine bidirectional switches that allows any load phase to be connected to any source phase as shown in Fig. 1.3. The major advantage of MC is the absence of the DC link capacitor which could lead to a more compact design. However, the higher cost of the bidirectional switches and complex control have made this topology less attractive for industrial applications. Besides the high number of components, MCs have some difficulties to reach high voltages due to the limited availability of high voltage semiconductor switches.

Figure 1.3. Conventional Direct Matrix Converter.

Figure 1.4 shows a conventional IMC which is obtained from the classical DMC structure. In 2002, a novel IMC is proposed called Sparse Matrix Converter (SMC) [15] which reduced the number of switches in conventional IMC. Later on, several other topologies are derived from SMC, such as Very Sparse Matrix Converter (VSMC), Ultra Sparse Matrix Converter (USMC) and Inverting Link Matrix Converter (ILMC) where in each iteration it is attempted to reduce the number of semiconductors [16].

Figure 1.4. Conventional Indirect Matrix Converter.

### 1.2.3 Conventional Multilevel Voltage Source Converters

For higher power and voltage levels, multilevel converters are normally used as they can provide high voltage output with extremely low distortion and lower dv/dt, while the semiconductor devices only have to tolerate a portion of the DC voltage [17–20]. Multilevel converters use an array of electronic switches to achieve the desired high voltage from a number of available DC voltage levels which may be implemented using capacitors. A voltage balancing strategy is needed to insure that the capacitor voltage maintains at the desired value. Conventional multilevel VSCs can be generally divided into the following three main categories:

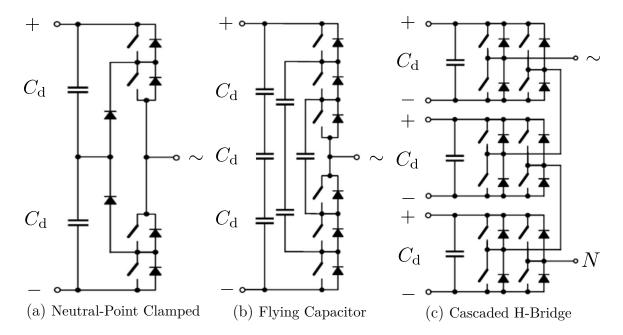

#### 1.2.3.1 Diode-Clamped Converter

Diode-Clamped Converter (DCC) employs clamping diodes and cascaded DC capacitors to produce AC voltage waveforms with multiple levels. However, in practice, only the 3-level inverter, often known as Neutral-Point Clamped Converter (NPCC) shown in Fig. 1.5(a), has found industrial applications due to the unequal distribution of losses among the switches and challenging capacitor voltage balancing for higher number of levels [17, 21–23]. It must be mentioned that, the complexity of the capacitor voltage balancing in DCC is solved in a B2B topology [24], yet it still suffers from high number of components.

Figure 1.5. Different types of conventional multilevel converters.

#### 1.2.3.2 Flying Capacitor Converter

Flying Capacitor Converter (FCC) consists of multiple pair of switches and capacitors. The schematic diagram of a 4-level FCC is shown in Fig. 1.5(b). All the capacitors are charged at the same voltage. Beside the difficulty of voltage balancing, FCC requires high number of capacitors, since as the number of levels increases, the number of capacitors increases rapidly [17].

#### 1.2.3.3 Cascaded H-Bridge Converter

Cascaded H-Bridge Converter (CHBC) is composed of multiple cascaded H-bridge cells to achieve high voltage levels. The schematic diagram of a 4-level CHBC is shown in Fig. 1.5(c). In order to feed these H-bridge cells, the same number of isolated DC supplies are required which may be obtained from multipulse diode rectifiers. The modularity of CHBC not only makes it more cost-effective, but also facilitates reaching very high voltages. One drawback of this topology is the high number of isolated DC supplies for higher levels of CHBCs [25].

### 1.2.4 Modular Multilevel Converter

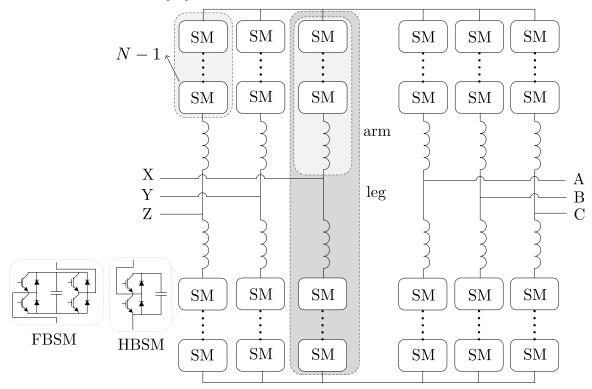

The Modular Multilevel Converter (MMC) is a newer generation of multilevel VSCs which was proposed for in 2003 by Marquardt [26] and first used commercially in the Trans Bay Cable project in San Francisco [27].

#### **1.2.4.1** Principle of Operation

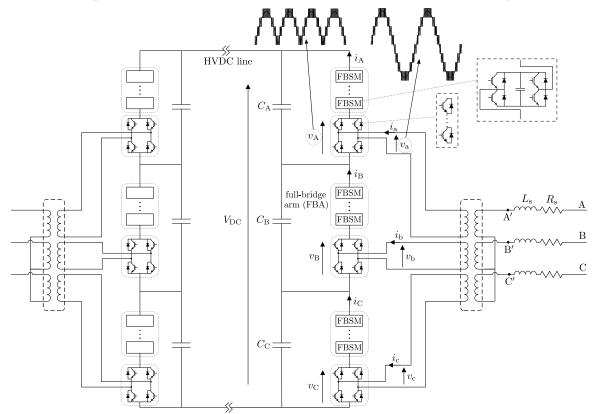

A traditional B2B-MMC is shown in Fig. 1.6 that consists of a number of series Sub-Modules (SMs) with DC capacitors. AC-side voltages are adjusted by changing the number of inserted SMs. The SM insertion/bypassing must be done so that the DClink voltage remains constant and the capacitor voltages stay close to their desired values. Half-Bridge Sub-Module (HBSM) and Full-Bridge Sub-Module (FBSM) are the most popular SMs shown in Fig. 1.6. Unlike HBSM which only generates 0 and  $V_{\rm C}$ , FBSM can produce  $-V_{\rm C}$  as well. Due to the SM capacitor voltage variation and switching transients, the three parallel connected phase units may have different voltages. Thus, for any SM insertion in each arm of the MMC, there must be a SM bypassing in the other arm of the leg simultaneously, so the leg voltage remains constant. Due to switching transients, the insertion and the bypassing may not happen at the same exact time which results in an increase/decrease in the leg voltage. Therefore, the three parallel connected legs may end up having different voltages. This leads to a circulating current which can flow between the three legs of the converter without affecting the AC-side voltages and currents. The circulating current needs to be minimized in order to reduce the branch losses which can be done by installing a small inductor of proper value in each arm. The details of the design procedure for different components of MMC are discussed in [28].

To sum up, MMC is increasingly attracting attention in different high power applications mainly due to its unique modular structure which can be built up into several hundred levels [27]. Although with such high number of levels, MMC offers

Figure 1.6. Three phase conventional B2B-MMC.

very low-harmonic voltage distortion on its output, yet it requires high number of hard-switched PWM-driven electronic switches. This thesis proposes a number of alternative topologies which offer the same advantages, but they require fewer electronic switches. In addition, the major portion of these switches operate in soft-switching mode.

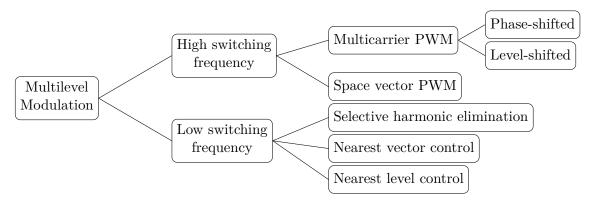

#### 1.2.4.2 Modulation Techniques

Several modulation techniques have been proposed for multilevel inverters [29]. The high number of switches in an MMC compared to a 2-level VSC, leads to a higher number of possible modulation schemes and more complicated modulation techniques. Modulation techniques for a MMC could be classified in two groups according to their switching frequency as shown in Fig. 1.7:

- Fundamental switching frequency, where each switch has only one commutation per cycle, such as multilevel Selective Harmonic Elimination (SHE), nearest voltage level and nearest vector control methods;

- High switching frequency, where each switch has several commutations per cycle, such as multilevel PWM and Space Vector Modulation (SVM) methods.

Among different techniques of multilevel converter modulation, multicarrier PWM and Nearest Level Control (NLC) are explained here due to their popularity in multilevel converter modulation.

#### Multicarrier Pulse Width modulations

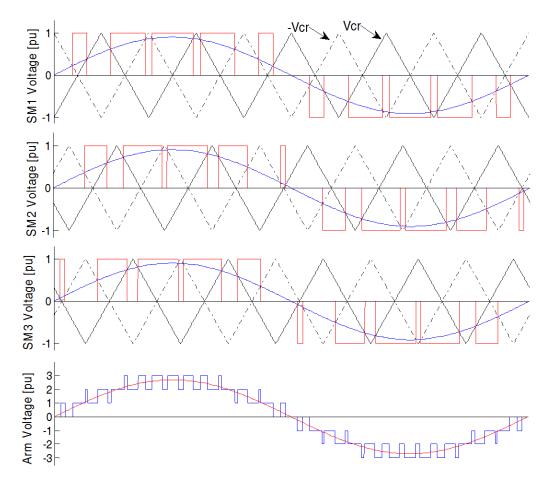

There are two common multicarrier modulations applied to multilevel converters as shown in Fig. 1.7. Phase-shifted PWM is the most commonly used modulation for cascaded multilevel converters as it offers an evenly power distribution among

Figure 1.7. Classification of multilevel converter modulation techniques.

cells. This modulation technique shifts the phase of each carrier in a proper angle to reduce the harmonic content of the output voltage. Figure 1.8 shows the modulation waveforms for a MMC arm with three FBSMs.

#### Nearest Level Control

In NLC technique [30], the nearest voltage level to the desired voltage reference that can be generated by the converter leg would be selected as below:

$$v_{\rm a} = \operatorname{round}\left(\frac{v_{\rm ref}}{E}\right) \times E.$$

(1.1)

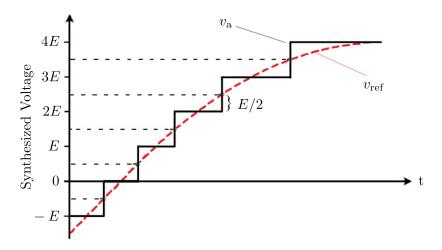

The output synthesized voltage is shown in Fig. 1.9. The main advantage of NLC technique is its easier implementation compared to other multilevel modulation techniques. This method is suitable for converters with a high number of levels, since the approximation error becomes significant for converters with a low number of levels which can lead to low-order harmonics at the AC-side.

#### 1.2.4.3 Capacitor Voltage Balancing

In MMC, SMs are constantly inserted into or bypassed out of the phase arms. In order to keep the capacitor voltages as evenly distributed as possible, the proper

Figure 1.8. Multilevel phase-shifted carrier-based technique.

Figure 1.9. Nearest level control technique.

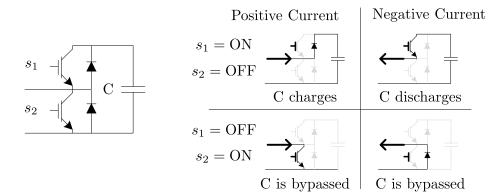

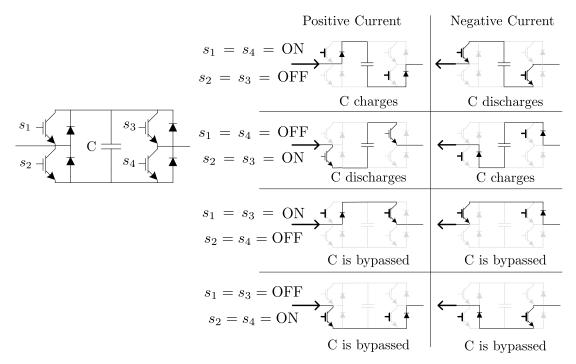

SMs must be selected to operate at any given time. Failure to adequately balance the voltages not only distorts the output voltage but also can result in equipment damage if individual SM voltages fluctuate outside of the rated values of the equipment. The change of a given SM's capacitor voltage is dependent on its inserted/bypassed state, as well as the magnitude and direction of the arm current. When the SM is inserted, the capacitor voltage increases (decreases) if the current is flowing into (out of) the SM. On the other hand, if the SM is bypassed, the capacitor voltage remains unchanged. This fact is shown for both HBSM and FBSM in Figs. 1.10 and 1.11, respectively.

Figure 1.10. Capacitor charging/discharging based on HBSM's status.

The capacitor voltage sorting method in each arm remains the most popular technique for capacitor voltage balancing in MMCs [26, 28, 31]. In this method, first, all capacitor voltages in each arm are sorted and the sign of the arm current is detected. Then, if the arm current is charging the SM capacitors, the SMs with the lowest capacitor voltages are selected to be inserted. Otherwise, if the arm current is discharging the SM capacitors, the SMs with the highest capacitor voltages are selected to be inserted. In other words, by generating a sorted list of SM capacitor

Figure 1.11. Capacitor charging/discharging based on FBSM's status.

voltages and the arm current direction at any time, the ideal SMs to be inserted or bypassed would be identified.

### **1.3** Description of the Proposed Converters

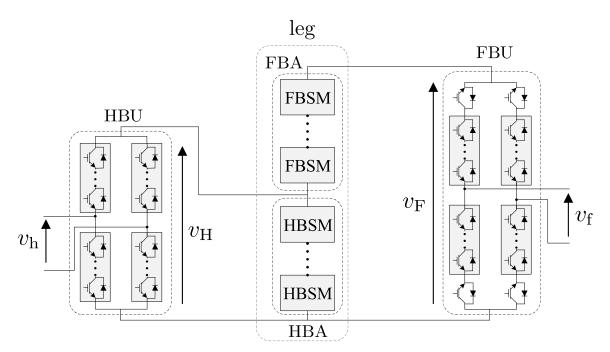

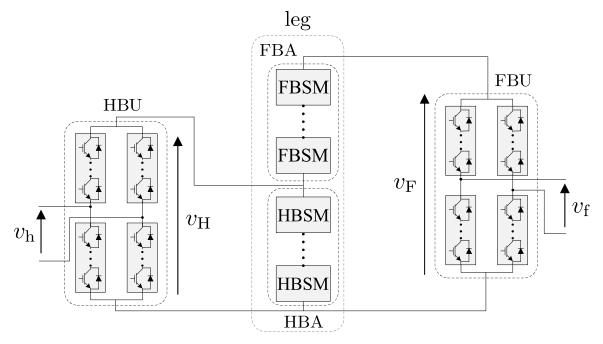

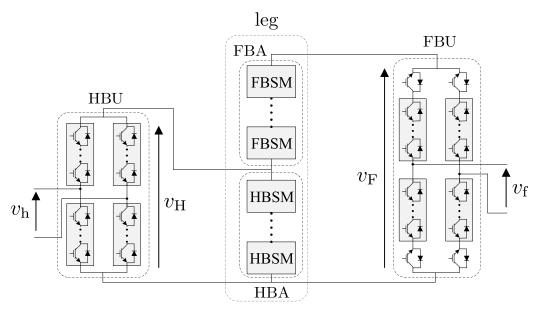

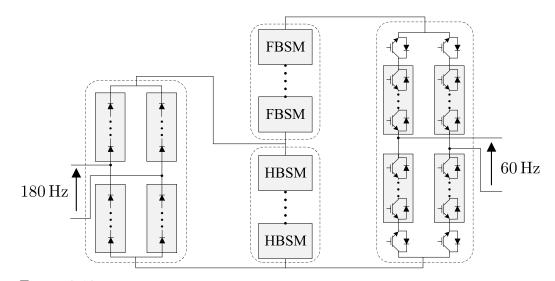

This dissertation intends to propose a number of novel MMCs for various power transmission systems. These MMCs will offer reduced number of components and increased efficiency, as a major portion of the power switches operate in ZVS mode. Figure 1.12 presents a single-phase version of the first proposed topology called Sparse Modular Multilevel Converter (SMMC) which is intended for HFHW transmission system.

The main leg synthesizes two rectified AC-voltages using its PWM-driven HBSMs and FBSMs, located in Half-Bridge Arm (HBA) and Full-Bridge Arm (FBA), respectively. The frequency of these voltages ( $v_{\rm H} \& v_{\rm F}$ ), are independent from each other.

Figure 1.12. Single-phase sparse modular multilevel converter.

Later, two low-frequency and soft-switched unfolders on the converter's sides (Half-Bridge Unfolder (HBU) and Full-Bridge Unfolder (FBU)), would unfold the rectified waveforms every half-cycle, so the full-wave sinusoidal AC-voltages  $v_{\rm h}$  &  $v_{\rm f}$  are constructed in the outputs. It will be shown in Chapter 2 that the proposed SMMC topology is less expensive and less lossy compared to a B2B-MMC. Also, an effective control strategy is proposed for capacitor voltage balancing which is later validated by both simulation and experiment.

The second proposed converter called MinMax Multilevel Converter (MMMC) is also suitable for AC/AC systems such as HFHW. The MMMC further reduces the number of hard-switched power switches by employing an additional soft-switched unfolder. In Chapter 3, this topology is studied in detail. In Chapter 4, the economical aspect of HFHW system is discussed and it is shown that this transmission system can benefit from employing the proposed converters. Finally, in Chapter 5, a highgain MMC called Series Hybrid Modular Multilevel Converter (SHMMC) is proposed for HVDC systems. Similar to the other proposed converters, a major portion of the power switches in SHMMC operate in low-frequency and soft-switching mode.

### 1.4 Thesis Objectives

The main objective of this thesis is to introduce suitable MMC topologies for various power transmission systems. In these converters, the number of power switches are reduced and the major portion of them operate in soft-switching mode. Beside the theoretical studies, the viability of the proposed topologies, as well as the effectiveness of the control strategy will be confirmed by both simulation and experiment. Briefly, the dissertation's objectives are:

- (i) To propose a novel AC/AC MMC for HFHW transmission system, which utilizes fewer power switches compared to conventional MMC and to have switches operating in soft-switching mode;

- (ii) To propose another AC/AC MMC for HFHW system, which achieves more switches operating in soft-switching mode;

- (iii) To propose a high-gain MMC for HVDC systems, which requires fewer power switches compared to MMC and similar to other proposed converters, the majority of its switches operate in soft-switching mode;

- (iv) To propose control strategies for the proposed topologies which regulate the AC-sides active and reactive powers and also guarantee the capacitor voltage balancing in both steady-state and transient conditions;

- (v) To study the economical aspect of HFHW power transmission system and compare the utilization of the proposed topologies with conventional approaches.

- (vi) To experimentally test the proposed topologies and their associated control strategies.

### 1.5 Thesis Outline

Based on flow of the contribution and number of the proposed converters, this dissertation is divided into six chapters as follows:

**Chapter 2** introduces a new topology of AC/AC converters called SMMC suitable for the HFHW transmission system. The advantages of SMMC compared to conventional MMC and its control strategy are then presented. At the end, the feasibility of SMMC is validated by simulation and experimental results.

**Chapter 3** presents another novel topology of MMCs intended for AC/AC power transmission systems such as the HFHW system. The proposed topology further reduces the number of PWM-driven power switches and replace them with low-frequency soft-switched switches, and it is called MMMC. A control strategy is designed to ensure the capacitor voltage balancing of the converter. At the end, the feasibility of MMMC is validated by simulation and experimental results.

Chapter 4 discusses the economical aspects of the HFHW power transmission system. It is shown how the HFHW system could benefit from uitlizing the proposed AC/AC topologies.

**Chapter 5** proposes a high-gain MMC called SHMMC which is intended for HVDC systems. The SHMMC provides a DC-link voltage almost 3.33 higher than AC-side Root-Mean-Square (RMS)-voltage which makes it very attractive for HVDC applications. The feasibility of SHMMC, as well as the effectiveness of the control strategy are validated by simulation and experimental results.

**Chapter 6** summarizes the work that is presented and suggests topics for future research.

# Chapter 2

# Sparse Modular Multilevel Converter

### 2.1 Introduction

In this chapter, a novel topology of MMCs is introduced for high power AC/AC systems. The Fractional Frequency Transmission System (FFTS) is an example that uses lower frequency (50/3 Hz) to reduce the line reactance, and thus to increase its capacity. This transmission system has been used in European railway electrification systems for almost a century [32, 33]. In the last few decades, novel static AC/AC frequency converters are proposed to reduce the weight and losses in traction propulsion systems which has resulted in a lower cost and more efficient system [34–36]. Another example is the HFHW power system which transfers the power in a higher

R. Alaei, S. A. Khajehoddin and W. Xu, "Sparse AC/AC Modular Multilevel Converter," *IEEE Transactions on Power Delivery*, vol. 31, no. 3, pp. 1195-1202, June 2016.

R. Alaei, S. A. Khajehoddin and W. Xu, "Control and Experiment of AC/AC Sparse Modular Multilevel Converter," *IEEE Transactions on Power Delivery*, (Early Access DOI: 10.1109/TP-WRD.2016.2618935).

frequency and requires an AC/AC converter at its receiving-end to connect to the 60 Hz power grid [1].

The proposed converter in this chapter has fewer power switches and capacitors compared to a B2B-MMC, and in addition, 57% of the switches operate in soft switching mode, which considerably decreases the converter losses. Moreover, a control strategy is developed and evaluated with both simulations and experiment which guarantees the capacitor voltage balancing for this converter.

### 2.2 Principle of Operation

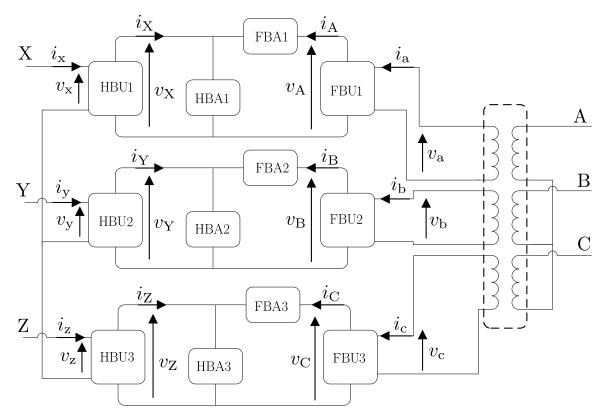

Figures 2.1 and 2.2 show the schematic diagram of single-phase and 3-phase versions of the proposed topology.

Figure 2.1. Schematic diagram of a single-phase *n*-level SMMC.

Compared to a B2B-MMC (see Fig. 1.6), this topology consists of a reduced number of components and therefore, it is called Sparse Modular Multilevel Converter

Figure 2.2. Schematic diagram of a three-phase SMMC.

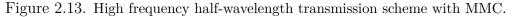

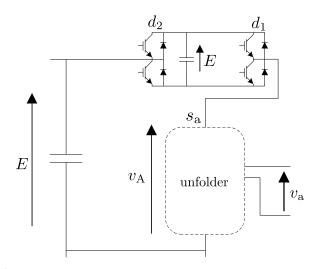

(SMMC). The SMMC consists of three separate stages including Half-Bridge Unfolder (HBU) and Full-Bridge Unfolder (FBU) on the sides and one main leg. The main leg consists of Half-Bridge Arm (HBA) and Full-Bridge Arm (FBA) which are built by a number of cascaded HBSMs and FBSMs, respectively. By inserting/bypassing the proper number of SMs in HBA and FBA, the desired voltage on both sides of the converter can be achieved. The unfolders are employed to apply the arm voltage or its reverse to  $v_{\rm f}$  or  $v_{\rm h}$ . Therefore, the absolute value of AC-side voltages are provided by operating the desired number of SMs, while their polarity are controlled by the unfolders in both sides. In the 3-phase SMMC, utilizing an isolating 3-phase transformer is essential, otherwise, SM capacitors might get shorted in some switching states (as an example, see Fig. 2.3). In Fig. 2.1, the Half-Bridge (HB)-side voltage  $v_{\rm H}$

Figure 2.3. Shorting capacitor  $C_2$  without using isolating transformer.

is the summation of inserted HBSMs in HBA which is a non-negative value as well as independent from FBA voltage. However, the Full-Bridge (FB)-side voltage  $v_{\rm F}$  is the summation of both HBA and FBA voltages. When  $v_{\rm H} \neq v_{\rm F}$ , a proper number of inserted FBSMs would generate the voltage difference. In an *n*-level SMMC, the number of HBSMs and FBSMs are equal to (n-1)/2; so that all desired non-negative values of  $v_{\rm H}$  and  $v_{\rm F}$  can be generated.

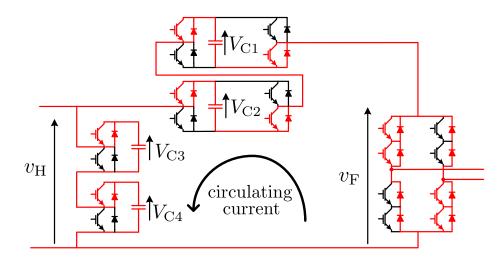

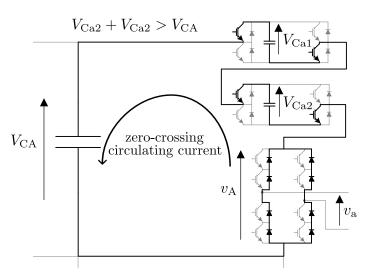

Unlike MMC, there is no circulating current between different legs (phases) of SMMC, as they are isolated from each other by a 3-phase transformer. However, it is inherently possible for current to circulate inside one phase of the SMMC. This current is not continuous and only may flow when  $v_{\rm F}$  crosses zero, and so it is called zero-crossing circulating current. For example, in Fig. 2.4, if  $V_{\rm C3} + V_{\rm C4}$  is slightly smaller than  $V_{\rm C1} + V_{\rm C2}$ , it causes  $v_{\rm F}$  to become a small negative value (when  $v_{\rm F} = 0$  is required). In addition, due to switching transients, the SM insertion/bypassing may not occur simultaneously. This leads to one extra level decrease/increase in  $v_{\rm F}$  for a short period of time. An extra level decrease in  $v_{\rm F}$  (when  $v_{\rm F} = 0$  is required), could

Figure 2.4. Zero-crossing circulating current in 5-level SMMC.

Figure 2.5. Schematic diagram of SMMC with modified FBU.

make  $v_{\rm F}$  negative. This negative voltage turns on the unfolder's anti-parallel diodes and current circulates through the leg.

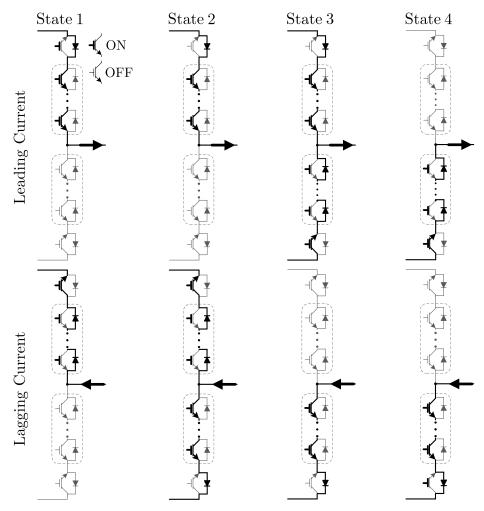

Adding one reversed Insulated-Gate Bipolar Transistor (IGBT) in each arm of the FBU as shown in Fig. 2.5, could block the possible small negative  $v_{\rm F}$ . The HBU remains intact. It should be noticed that the maximum voltage-drop across the reversed IGBT occurs, when HBA and FBA capacitors are in their lowest and highest acceptable voltages, respectively. Therefore, this IGBT must withstand the predefined capacitor voltage ripple,  $\Delta V_{\text{ripp}}$  multiplied by the number of HBSMs (or FBSMs) which equals to  $(n-1)/2 \times \Delta V_{\text{ripp}}$ . This implies that in case of high number of levels, more than one reversed IGBT might be required. Figure 2.6 demonstrates FBU's principle of operation at voltage zero-crossing transition for both cases of leading and lagging currents. Note that here only the right leg of the unfolder is shown. It can be seen that at any stage of unfolding transition, there is at least one reversed IGBT blocking the zero-crossing circulating current.

Table 2.1 compares an *n*-level B2B-MMC with the alternative SMMC based on the number of main components. The multiple number of IGBTs for the unfolder valves is taken into account in the calculation. This converter also offers ZVS for more than half of its semiconductors which later on will be used for voltage sharing of series-connected semiconductors.

| Comparison of MMC and SMMC Component Count                                 |                                                                   |              |               |               |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------|--------------|---------------|---------------|--|

|                                                                            | 1-Phase                                                           |              | 3-Phase       |               |  |

| Quantity                                                                   | MMC                                                               | SMMC         | MMC           | SMMC          |  |

| Capacitor<br>Inductor                                                      | 8                                                                 | 0            | 12(n-1)<br>12 | 0             |  |

| High-frequency & hard-switched IGBT<br>Line-frequency & soft-switched IGBT | $     \begin{array}{c}       16(n-1) \\       0     \end{array} $ | 3(n-1)<br>4n | 24(n-1)<br>0  | 9(n-1)<br>12n |  |

Table 2.1.Comparison of MMC and SMMC Component Count

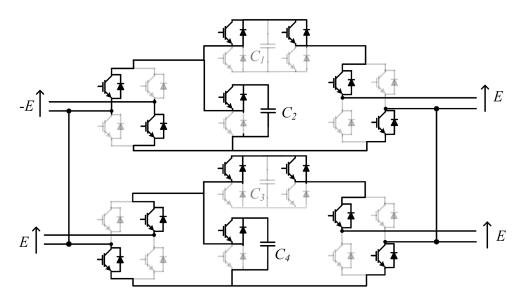

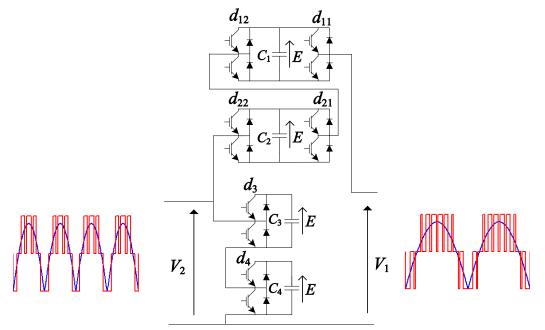

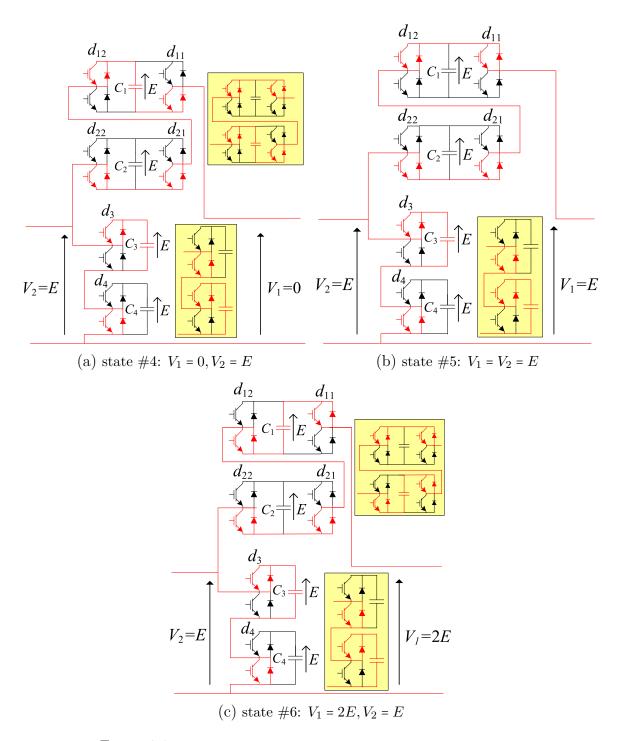

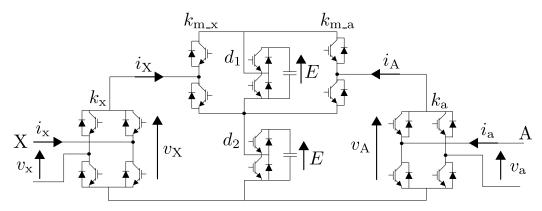

#### 2.2.1 Demonstration of a Single-phase 5-Level SMMC

The main leg of a 5-level SMMC is shown in Fig. 2.7 to be studied in detail. For the sake of simplicity, all capacitor voltages are assumed to be regulated at voltage E. Switching function  $d_i$  (i = 11, 12, 21, 22, 3, 4) is defined so that  $d_i = 1$ , when upper

| VALID SWIT      | CHINC                                 | G STA    |                                       |                                       | 5-le                                | VEL    | SMM   | [C    |

|-----------------|---------------------------------------|----------|---------------------------------------|---------------------------------------|-------------------------------------|--------|-------|-------|

| Switching state | $d_{11}$                              | $d_{12}$ | $d_{21}$                              | $d_{22}$                              | $d_3$                               | $d_4$  | $V_1$ | $V_2$ |

| 1               | 0                                     | 0        | 0                                     | 0                                     | 0                                   | 0      | 0     | 0     |

|                 | 0                                     | 0        | 1                                     | 1                                     | 0                                   | 0      |       |       |

|                 | 1                                     | 1        | 0                                     | 0                                     | 0                                   | 0      |       |       |

|                 | 1                                     | 1        | 1                                     | 1                                     | 0                                   | 0      |       |       |

|                 | 1                                     | 0        | 0                                     | 0                                     | 0                                   | 0      | E     | 0     |

| 2               | 1                                     | 0        | 1                                     | 1                                     | 0                                   | 0      |       |       |

| -               | 0                                     | 0        | 1                                     | 0                                     | 0                                   | 0      |       |       |

|                 | 1                                     | 1        | 1                                     | 0                                     | 0                                   | 0      |       |       |

| 3               | 1                                     | 0        | 1                                     | 0                                     | 0                                   | 0      | 2E    | 0     |

|                 | 0                                     | 1        | 0                                     | 0                                     | 1                                   | 0      |       |       |

|                 | 0                                     | 1        | 1                                     | 1                                     | 1                                   | 0      |       |       |

|                 | 0                                     | 0        | 0                                     | 0                                     | 1                                   | 0      |       |       |

| 4               | $\begin{array}{c} 1 \\ 0 \end{array}$ | 1<br>1   | $\begin{array}{c} 1 \\ 0 \end{array}$ | $\begin{array}{c} 1 \\ 0 \end{array}$ | 1                                   | 0      | 0     | E     |

|                 | 0                                     | 1        | 1                                     | 1                                     | $\begin{array}{c} 0\\ 0\end{array}$ | 1<br>1 |       |       |

|                 | 0                                     | 0        | 0                                     | 0                                     | 0                                   | 1      |       |       |

|                 | 1                                     | 1        | 1                                     | 1                                     | 0                                   | 1      |       |       |

|                 | 0                                     | 0        | 0                                     | 0                                     | 1                                   | 0      | E     | E     |

|                 | 0                                     | 0        | 1                                     | 1                                     | 1                                   | 0      |       |       |

|                 | 1                                     | 1        | 0                                     | 0                                     | 1                                   | 0      |       |       |

| F               | 1                                     | 1        | 1                                     | 1                                     | 1                                   | 0      |       |       |

| 5               | 0                                     | 0        | 0                                     | 0                                     | 0                                   | 1      |       |       |

|                 | 0                                     | 0        | 1                                     | 1                                     | 0                                   | 1      |       |       |

|                 | 1                                     | 1        | 0                                     | 0                                     | 0                                   | 1      |       |       |

|                 | 1                                     | 1        | 1                                     | 1                                     | 0                                   | 1      |       |       |

|                 | 1                                     | 0        | 0                                     | 0                                     | 1                                   | 0      |       | E     |

|                 | 1                                     | 0        | 1                                     | 1                                     | 1                                   | 0      |       |       |

|                 | 0                                     | 0        | 1                                     | 0                                     | 1                                   | 0      |       |       |

| 6               | 1                                     | 1        | 1                                     | 0                                     | 1                                   | 0      | 2E    |       |

| -               | 1<br>1                                | 0<br>0   | $\begin{array}{c} 0 \\ 1 \end{array}$ | $\begin{array}{c} 0 \\ 1 \end{array}$ | $\begin{array}{c} 0\\ 0\end{array}$ | 1<br>1 |       |       |

|                 | 0                                     | 0        | 1                                     |                                       | 0                                   | 1      |       |       |

|                 | 1                                     | 1        | 1                                     | 0                                     | 0                                   | 1      |       |       |

| 7               | 0                                     | 1        | 0                                     | 1                                     | 1                                   | 1      | 0     | 2E    |

| 8               | 0                                     | 1        | 0                                     | 0                                     | 1                                   | 1      | -     |       |

|                 | 0                                     | 1        | 1                                     | 1                                     | 1                                   | 1      |       |       |

|                 | 0                                     | 0        | 0                                     | 1                                     | 1                                   | 1      | E     | 2E    |

|                 | 1                                     | 1        | 0                                     | 1                                     | 1                                   | 1      |       |       |

|                 | 0                                     | 0        | 0                                     | 0                                     | 1                                   | 1      |       |       |

| C               | 0                                     | 0        | 1                                     | 1                                     | 1                                   | 1      | 0.77  | 0.77  |

| 9               | 1                                     | 1        | 0                                     | 0                                     | 1                                   | 1      | 2E    | 2E    |

|                 | 1                                     | 1        | 1                                     | 1                                     | 1                                   | 1      |       |       |

|                 |                                       |          |                                       |                                       |                                     |        |       |       |

Table 2.2.

Figure 2.6. Description of zero-crossing transition in FBU.

switch of the SM is ON and the lower switch is OFF and  $d_i = 0$ , for the reverse case. Table 2.2 lists all the valid switching states for the main leg of 5-level SMMC. Note that for many of these states, there are several redundancies and also all desired voltages for  $V_1$  and  $V_2$  could be provided independent from each other. As an example, the switching states 4-6 are illustrated in Fig. 2.8.

#### 2.2.2 ZVS of SMMC Unfolders

Since the HBA and FBA arms operate with a voltage higher than the available switch ratings, several switches are connected in series to tolerate the desired voltage. Thus, steady-state and transient voltage sharing between the series switches need to be ensured, since most power semiconductors do not hold voltages above their rating and their recovery characteristics differ even within the same type and manufacturer. The steady-state voltage sharing can be achieved by installing high-value parallel resistors. Generally, additional circuitry has to be provided to ensure equal transient voltage sharing. Here, there is no need for extra components, since all the switchings in the unfolders occur in ZVS regardless of the operating condition. Figure 2.9 shows the HBU switching transition.

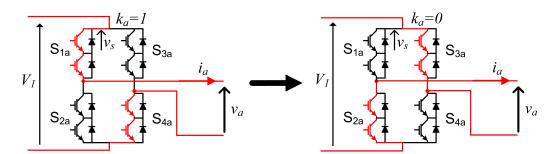

In case of lagging current, shown in Fig. 2.10(a), the turn on gate signals are set for  $S_{1a}$  and  $S_{4a}$  at time instant of  $t_0$ . However, they will not start conducting until

Figure 2.7. Schematic diagram of a 5-level SMMC leg.

Figure 2.8. Illustration of switching states 4-6 in a 5-level SMMC

Figure 2.9. Schematic diagram of HBU switching transition.

Figure 2.10. Unfolder transition (a) lagging current (b) leading current.

the current  $i_a$  crosses zero and becomes positive at time instant of  $t_1$  causing a Zero Current Switching (ZCS). From  $t_0$  to  $t_1$ ,  $D_{1a}$  and  $D_{4a}$  are ON which forces the voltage across  $S_{1a}$  and  $S_{4a}$  to be close to zero before turning on causing a ZVS. Thus,  $S_{1a}$ and  $S_{4a}$  are experiencing both ZVS and ZCS at turn on in case of lagging current. At time instant of  $t_2$ , the turn off gate signals are set for  $S_{1a}$  and  $S_{4a}$ , however due to their different gating characteristics, they may not turn off at the exact same time. In this situation, in a valve including n series IGBTs, the one which turns off first, will experience the full voltage of the series string. Here, this voltage is  $n \times v_{\text{IGBT-ON}}$ , since the current  $i_a$  is commutating from  $S_{1a}$  and  $S_{4a}$  to  $D_{2a}$  and  $D_{3a}$ . Because this voltage is still negligible compared to an IGBT's blocking voltage, it can be concluded that  $S_{1a}$  and  $S_{4a}$  are experiencing ZVS at turn off in case of lagging current. Similarly,  $S_{2a}$  and  $S_{3a}$  are experiencing both ZVS and ZCS at turn on and ZVS at turn off when the current is lagging.

In case of a leading current (see Fig. 2.10(b)), the turn on gate signals are set for  $S_{1a}$  and  $S_{4a}$  at time instant of  $t_0$ . However, due to their different gating characteristics, they may not turn simultaneously. In this case, in a string of n series IGBTs, the one which turns on last will experience the full voltage of the string. Here, this voltage is  $n \times v_{D-ON}$ , since the current  $i_a$  is commutating from  $D_{2a}$  and  $D_{3a}$  to  $S_{1a}$  and  $S_{4a}$ . Because this voltage is still negligible compared to an IGBT's blocking voltage, it can be concluded that  $S_{1a}$  and  $S_{4a}$  are experiencing ZVS at turn on in case of a leading current. At time instant of  $t_2$ , the turn off gate signals are set for  $S_{1a}$  and  $S_{4a}$ . As the current  $i_a$  becomes negative and flows through  $D_{1a}$  and  $D_{4a}$  at time instant of  $t_1$ ,  $S_{1a}$  and  $S_{4a}$  are experiencing ZVS at turn off in case of a leading current. Similarly,  $S_{2a}$  and  $S_{3a}$  are experiencing ZVS at turn on and both ZVS and ZCS at turn off when the current is lagging.

Since ZVS occurs in the unfolders for all operating conditions, voltage across the valve is small when gate pulses are applied and even if the gate pulses come at different times, maximum voltage during transient will not exceed the device rating. Therefore, without any extra circuitry, a limited maximum transient voltage sharing is achieved in the unfolders.

#### 2.2.3 Unidirectional SMMC

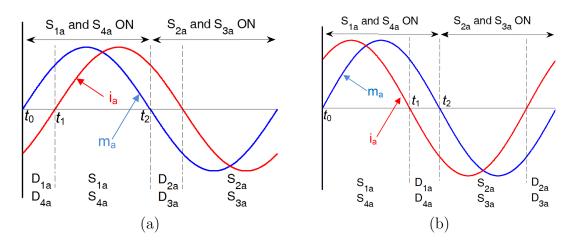

Figure 2.11 shows a HFHW system operating in 180 Hz. It must be noted that this system is unidirectional and the active power always flow from the high-frequency generator to the 60 Hz grid. Thus, the proposed converter could be modified to

operate in unidirectional mode. This unidirectional SMMC is derived from the original SMMC by using diode-bridge front unfolder as shown in Figure 2.12. Table 2.3 presents the comparison of these two AC/AC converters in terms of the number of different components.

Figure 2.11. High frequency half-wavelength transmission scheme with unidirectional SMMC.

Figure 2.12. One phase of unidirectional SMMC with diode-bridge front unfolder.

In must be noted that although, the modified SMMC utilizes a diode-bridge in the front-end, it does not inject any harmonic to the AC-side. To compare this topology with alternative MMC-based converter, a HFHW system operating in 180 Hz is presented in Fig. 2.13. Table 2.3 presents the comparison of these two AC/AC converters in terms of the number of different components.

| Table 2.3.COMPONENT COUNT OF TWO CONVERTERS FOR HFHW SCHEME. |                        |                        |  |  |  |

|--------------------------------------------------------------|------------------------|------------------------|--|--|--|

| COMPONENT COUNT C                                            | Diode-bridge Rectifier | SMMC with              |  |  |  |

|                                                              | + MMC                  | diode-bridge front-end |  |  |  |

| Diode                                                        | 6(n-1)                 | 6(n-1)                 |  |  |  |

| $\mathrm{IGBT}^\dagger$                                      | 12(n-1)                | 9(n-1)                 |  |  |  |

| $\mathrm{IGBT}^\ddagger$                                     | 0                      | 6(n+1)                 |  |  |  |

| Capacitor                                                    | 6(n-1)                 | 3(n-1)                 |  |  |  |

| AC filter                                                    | Required               | Not Required           |  |  |  |

| Step-down transformer                                        | Special                | Conventional           |  |  |  |

| <sup>†</sup> High-frequency                                  | & hard-switched        |                        |  |  |  |

<sup>†</sup> High-frequency & hard-switched

<sup>‡</sup> Line-frequency & soft-switched

# 2.3 Capacitor Voltage Balancing

Figure 2.14 shows the simplified schematic diagram of a single-phase SMMC.

Figure 2.14. Simplified schematic diagram of a single-phase SMMC.

The voltages and currents on FB- and HB-sides of the converter can be represented as:

$$\begin{cases} v_{\rm f} = V_{\rm mf} \sin(\omega_{\rm f} t) , \quad v_{\rm F} = \lambda_{\rm f} . v_{\rm f} \\ i_{\rm f} = I_{\rm mf} \sin(\omega_{\rm f} t - \varphi_{\rm f}) , \quad i_{\rm F} = \lambda_{\rm f} . i_{\rm f} \\ \lambda_{\rm f} = \operatorname{sign}(v_{\rm f}) = \operatorname{sign}(\sin(\omega_{\rm f} t)) \\ \\ v_{\rm h} = V_{\rm mh} \sin(\omega_{\rm h} t + \theta_{\rm h}) , \quad v_{\rm H} = \lambda_{\rm h} . v_{\rm h} \\ i_{\rm h} = I_{\rm mh} \sin(\omega_{\rm h} t + \theta_{\rm h} - \varphi_{\rm h}) , \quad i_{\rm H} = \lambda_{\rm h} . i_{\rm h} \\ \lambda_{\rm h} = \operatorname{sign}(v_{\rm h}) = \operatorname{sign}(\sin(\omega_{\rm h} t + \theta_{\rm h})). \end{cases}$$

$$(2.1)$$

The instantaneous power going through FBA and HBA are calculated as:

$$p_{\rm HB}(t) = (i_{\rm F} + i_{\rm H}) \times v_{\rm H} , \quad p_{\rm FB}(t) = i_{\rm F} \times (v_{\rm F} - v_{\rm H}).$$

(2.3)

In the steady state condition, the stored energy of FBA and HBA must be constant, so the capacitor voltages remain unchanged. This leads to the following equations:

$$\int_{T} p_{\rm HB}(t) dt = 0 \quad , \quad \int_{T} p_{\rm FB}(t) dt = 0.$$

(2.4)

The above equation can be rewritten as below voltage balancing criteria:

$$\int_{T} \left( p_{\rm FB}(t) + p_{\rm HB}(t) \right) dt = 0 \\

\int_{T} p_{\rm FB}(t) dt = 0$$

voltage balancing criteria. (2.5)

The first criterion leads to the real power balance between the AC-sides as presented below:

$$0 = \int_{T} \left( p_{\rm FB}(t) + p_{\rm HB}(t) \right) dt$$

=

$$\int_{T} \left( i_{\rm F} \times v_{\rm F} + i_{\rm H} \times v_{\rm H} \right) dt$$

=

$$\frac{1}{2} V_{\rm mf} I_{\rm mf} \cos(\varphi_{\rm f}) + \frac{1}{2} V_{\rm mh} I_{\rm mh} \cos(\varphi_{\rm f})$$

$$\Rightarrow P_{\rm f} + P_{\rm h} = 0.$$

(2.6)

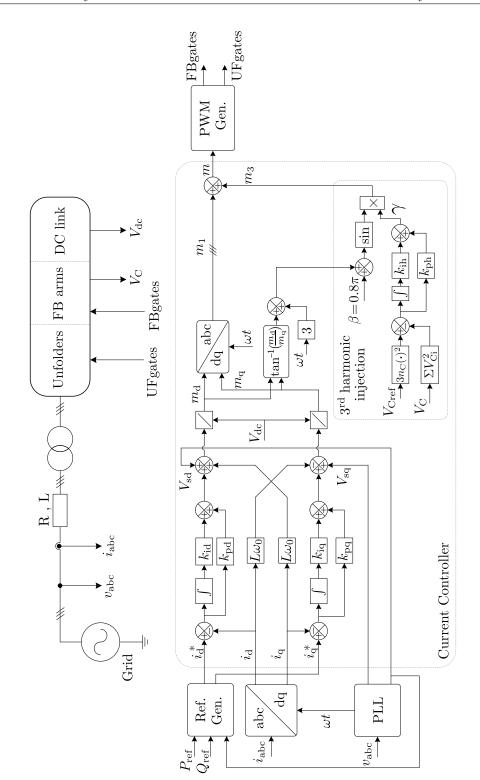

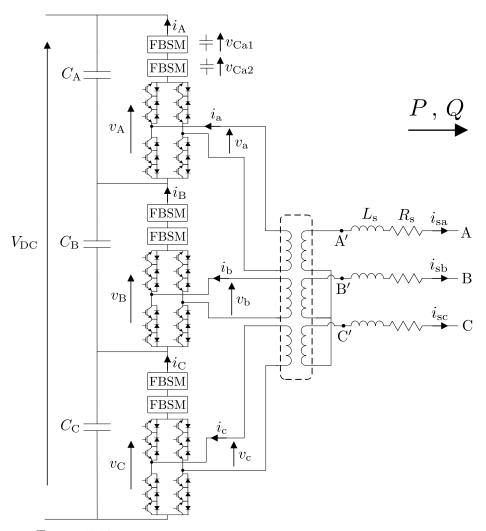

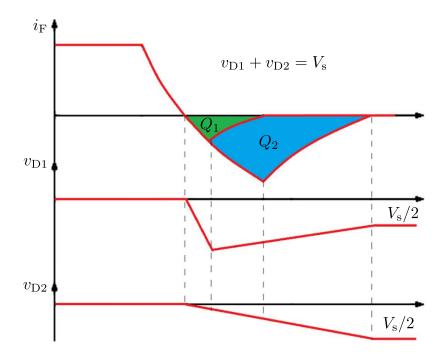

The second criterion is studied as: