### Non Hermetic Ceramic Flip Chip Package Construction and Reliability

Gerry Maloney, Gabriel Dosdos, Paul Ton

8/28/09, MAPLD

Non Hermetic Ceramic Flip Chip Package Construction and Reliability

# Agenda:

- Section 1: Package Construction Overview

- Section 2: Why Flip Chip, Why Non Hermetic

- Section 3: Reliability Review

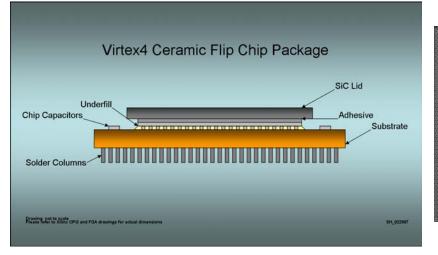

### **Ceramic Flip Chip CGA (CF) Package Construction**

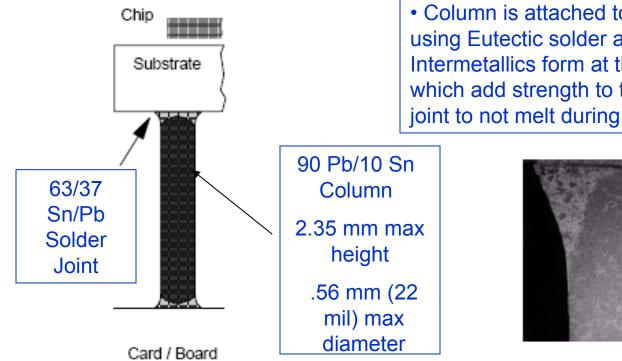

- The CF package substrate is ceramic and the columns are 90%Pb/10%Sn solid solder columns.

- All Xilinx Ceramic Flip Chip package (CF) die are Flip Chip and are bumped with High Lead bumping (95%Pb/5%Sn).

- The bumped die is flipped and reflowed to the ceramic substrate at assembly. A moisture resistant epoxy underfill encapsulates the bumps.

V4 Bumped Die

-Minimum Bump Pitch: 190 microns

-# of Bumps: 3896-8248

Epoxy Underfill encases bumps

Xilinx CF Package Construction

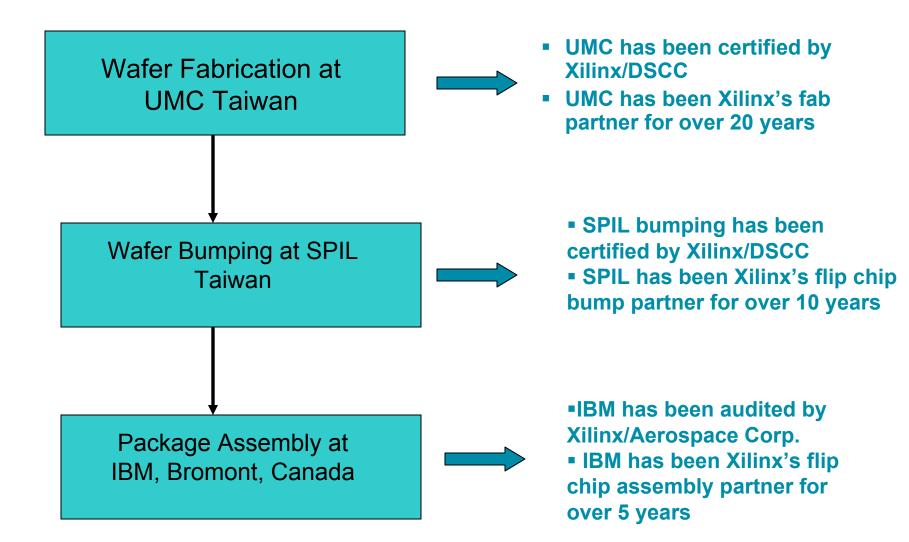

### **CF Package Manufacturing Flow**

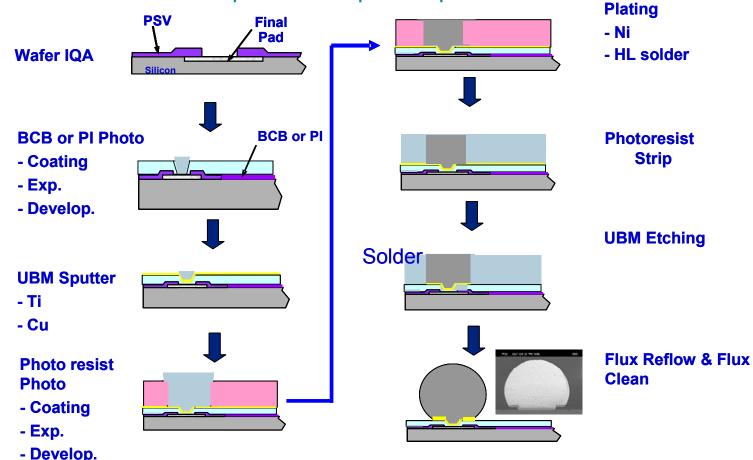

### **CF Package Bumping**

- All CF package die are flip chip and are bumped with High Lead Bumping. (95% Pb/5% Sn)

- Bump Pads are arranged across the top surface of the die. Bump pads consist of power, ground and I/O pads.

- Bumps are attached after wafer sort. Bump Pads and Bumps are not probed.

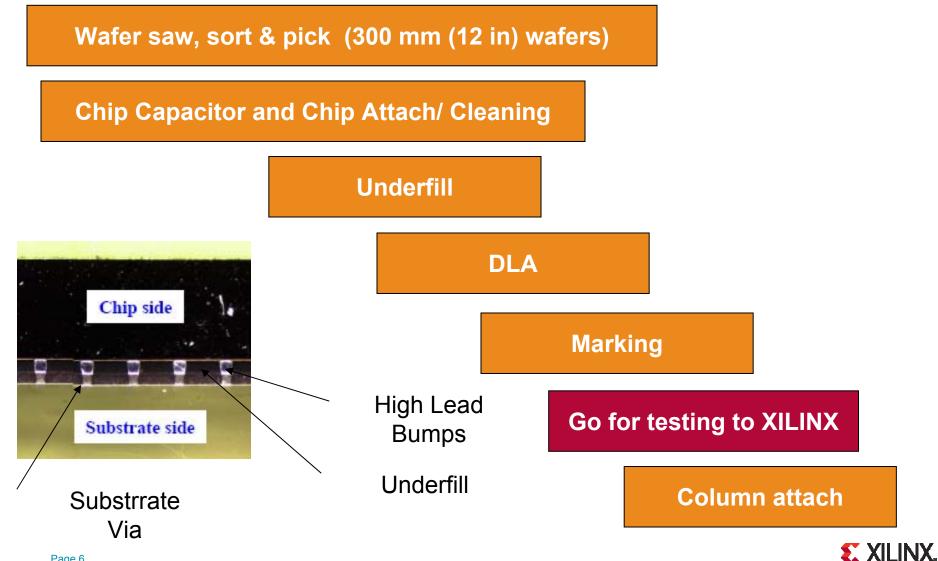

### **CF Package Assembly Flow**

### **CF Package Assembly Process**

- CF package is assembled at IBM using IBM's qualified material set/process flow

- Xilinx and Aerospace Corp. have audited IBM and have added the following additional assembly process monitors to Xilinx's Class V flow to closely match Class S military screening requirements:

| Assembly Monitor           | Sample Size                          | Xilinx Specification |

|----------------------------|--------------------------------------|----------------------|

| Die Visual Inspection      | 100%                                 | MAC0123              |

| Die Adhesion Test (Pad     | Package Substrate Lot Acceptance,    | MFC0087              |

| Wettability Test)          | 1% per substrate lot                 |                      |

| Die Bump Shear and Die     | Lot Acceptance, 3 units per assembly | MAC0117              |

| Bump Pull Monitor          | lot                                  |                      |

| Underfill Coverage Monitor | 100% of lot                          | MAC0120              |

| (CSAM)                     |                                      |                      |

| Lid Shear Test             | Lot Acceptance, 8 units per assembly | MAC0118              |

|                            | lot                                  |                      |

| Temperature Cycle          | 100% of lot, 50 cycles, Condition C  | MFC0087              |

|                            | (-65 to 150 C)                       |                      |

### Why Flip Chip, Why Non Hermetic

- All Xilinx V4/V5 devices are only offered in Flip Chip for both commercial & military markets.

- Flip Chip gives the best electrical performance. Eliminating wire bond wires improves the inductance and capacitance of the electrical connections.

- Flip Chip connections uses the whole area of the die (compared to the peripheral for wire bond) thus allowing more I/O, Power & Ground signals.

- Non Hermetic Ceramic Flip Design allows Xilinx to assemble at IBM. IBM has been assembling Non Hermetic Ceramic Flip Chip for over 30 years, so the package has a proven excellent reliability record.

### **Ceramic Flip Chip Reliability**

#### • CF Package has proven excellent Reliability:

| Reliability Characteristic                  | Detail                                                                                                                                          |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| MSL 1: Package is rated as a Moisture       | 2 Passivations (BCB & SiN) cover the top surface                                                                                                |

| Superior MSL 1 (Package has passed 168      | of the die. Epoxy underfill protects the bumps                                                                                                  |

| hrs 85/85 followed by 4000 TCB testing)     | from moisture.                                                                                                                                  |

| CTE Matching: CTE of the ceramic package    | CTE matching eliminates thermal expansion                                                                                                       |

| (7) closely matches the die CTE (3)         | stresses and so there is little risk for bump or die cracks with ceramic flip chip.                                                             |

| Excellent Bump Quality                      | Automoated bumping fabrication process provdes<br>strong bumps. Bumps are not probed and are<br>100% visualed before assembly.                  |

| Strong Bump to Package Interconnection      | Bumps form strong solder joint connections with<br>the package. No marginal connections (like low<br>wire pull on wire bond packages) are seen. |

| Multiple 100% Open/Short Electrical Testing | All package connections go through multiple<br>100% Open/Short testings in the screening flow<br>as part of Final Test.                         |

### Virtex-4, XQR CF Package V Grade Qualification Summary

- Virtex-4, XQR-CF product has completed and passed qualification to the requirements of MIL-PRF-38535 & MIL-STD-883.

- Product qualified are:

| Family | Device/Package       |

|--------|----------------------|

| V4     | XQR4VLX200-10CF1509V |

| V4     | XQR4VSX55-10CF1140V  |

| V4     | XQR4VFX60-10CF1144V  |

| V4     | XQR4VFX140-10CF1509V |

#### Product has passed the following qualification tests:

| Qualification Test                    | Test Method         | Sample Size         | Device               | Results             |

|---------------------------------------|---------------------|---------------------|----------------------|---------------------|

| Group A testing                       | Mil Std 883, TM5005 | 100%                | AII 4 V4 XQR CF's    | Pass                |

| Modified* Group B Testing             | Mil Std 883         | per Mil Std 883     | AII 4 V4 XQR CF's    | Pass, see Section 1 |

|                                       |                     |                     | XQR4VFX60,           |                     |

|                                       |                     |                     | XQR4VLX200 &         |                     |

| Group C testing                       | Mil Std 883, TM1005 | 15 units per device | XQR4VSX55            | Pass, see Section 2 |

|                                       |                     |                     | XQR4VLX200 &         |                     |

| Group D testing                       | Mil Std 883         | per Mil Std 883     | XQR4VSX55            | Pass, see Section 1 |

| Group E testing                       | Mil Std 883         | per Mil Std 883     | AII 4 V4 XQR CF's    | Pass                |

| BLR Temperature Cycle Testing         | IPC 9701            | per IPC 9701        | XQR4VLX200-CF1509    | Pass, see Section 3 |

| MLS 1 testing + CSAM                  | JEDEC Std 020A      | 15 units            | XQR4VLX200-CF1509    | Pass, see Section 4 |

| Package Temperature Cycle Condition B |                     |                     |                      |                     |

| Testing + CSAM                        | JEDEC & Xilinx Std  | 14 units            | XQR4VLX200-CF1509    | Pass, see Section 4 |

|                                       |                     |                     | CF Underfill and Lid |                     |

| Outgassing Testing                    | ASTM E-595          | 3 units             | Adhesive             | Pass, see Section 5 |

| Wear Out Tests                        | Xilinx Std          | Xilinx Std          | V4                   | Pass, see Section 6 |

| Mask Qualification (Latch Up and ESD) | Xilinx Std          | Xilinx Std          | AII 4 V4 XQR CF's    | Pass, see Section 6 |

\* Some tests do not apply to ceramic flip chip

# Appendix: Virtex-4, XQR CF Package Group B & D Qualification Results

- Group B and D Test Results:

- Group B Test Results:

| Subgroup | Test                               | Method  | Sample Size          | Results                           |

|----------|------------------------------------|---------|----------------------|-----------------------------------|

| 1        | Physical Dimensions                | 2016    | 2                    | Pass                              |

|          | Internal Water Vapor               | 1018    | N/A                  | Parts are not hermetically sealed |

| 2        | Resistance to Solvents             | 2015    | N/A                  | Parts are laser marked            |

|          | Internal Visual and Mechanical     | 2013    | 2                    | Pass                              |

|          | Die Pull (Bond Strength/Die Shear) |         | 3                    | Pass                              |

| 3        | Solderability                      | IBM Std | 1% per substrate lot | Pass                              |

| N/A      | CSAM                               | IBM Std | 100% of lot          | Pass                              |

| N/A      | Lid Shear                          | IBM Std | 8 units per lot      | Pass                              |

#### - Group D Test Results: D3 & D4 units passed -55, 25 and 125 °C electrical testing

| before and aft | Subgroup | MIL-S                        | TD-883      |                   | Sample | Results | Ref #              |

|----------------|----------|------------------------------|-------------|-------------------|--------|---------|--------------------|

|                | Subgroup | Test Method Condition        |             | Condition         | Size   | Results | Hel#               |

| 1              |          | Physical Dimensions          | 2016        |                   | 2      | 0 fail  | N/A <sup>(1)</sup> |

|                |          | a. Thermal Shock             | 1011        | B, 15 cycles      | 15     | 0 fail  |                    |

|                |          | b. Temperature Cycle         | 1010        | C, 100 cycles     | 15     | 0 fail  | ]                  |

|                | 3        | c. Moisture Resistance       | 1004        |                   | 15     | 0 fail  | STS139014          |

|                |          | e. Visual Inspection         | 1004 & 1010 | 4 &1010 15 0 fail |        | 0 fail  | 7                  |

|                |          | f. End-Point Electrical Test |             |                   | 15     | 0 fail  | ]                  |

|                |          | a. Mechanical Shock          | 2002        | В                 | 15     | 0 fail  |                    |

|                |          | b. Vibration                 | 2007        | А                 | 15     | 0 fail  | ]                  |

|                | 4        | c. Constant Acceleration     | 2001        | E, Y1 only        | 15     | 0 fail  | STS139015          |

|                |          | e. Visual Inspection         | 1010        |                   | 15     | 0 fail  |                    |

|                |          | f. End-Point Electrical Test |             |                   | 15     | 0 fail  | ]                  |

|                | 5(2)     | a. Salt Atmosphere           | 1009        | А                 | 15     | 0 fail  | STS137031          |

|                | 3.4      | c. Visual Inspection         | 1009        |                   | 15     | 0 fail  | 51515/051          |

# Appendix: Virtex-4, XQR CF Package Group C, Steady State Life Test Qualification Results

- Virtex 4, XQR4VFX60, XQR4 VLX200 & XQR4VSX55 V Grade CF product have successfully passed qualification with each device passing 2000 hours of steady state life.

- Steady State Life Conditions are per Mil Std 883, Method 1005 as follows:

- Static Burn In, Temperature = 125°C -0/+8°C

- VCC CORE: 1.26v

- VCC AUX: 2.625v

- VCC IO: 3.45v

- -55, 25 and 125 °C Electrical Testing at each readpoint

### Background:

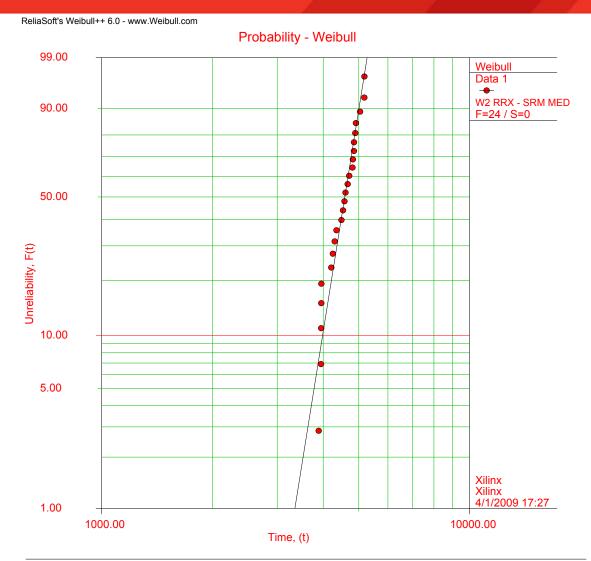

- Daisy Chain CF parts were assembled and columns were attached following the Xilinx production approved IBM V flow.

- Parts were then attached to 8-layer thick FR4 boards and put through Temperature Cycling Condition J (0°C to 100°C)

- Daisy Chain nets were continuously electrically monitored for resistance change.

- Failure criteria is when the resistance of a net exceeds the threshold resistance (300 ohms)

- BLR testing successfully completed using XQR4VLX200-CF1509 IBM columns

- Results very good with first failure not seen until 3892 cycles.

- IBM column is used on all Xilinx CF products.

#### 90 Pb/10 Sn IBM Column:

- After Final Test screening, CF packages are column attached at IBM with 90 Pb/10 Sn columns using IBM's proprietary CLASP process.

- Columns are non Wire solid solder.

- IBM's column attach CLASP process is fully automated with no manual handling.

• Column is attached to the CF package substrate using Eutectic solder and additional dopant. Intermetallics form at the column to package interface which add strength to the solder joint and causes the joint to not melt during board attach.

#### Test Board

- 8 Layer FR4 Board: Signal/GND/Signal/Power/Signal/GND/Signal/Power

- 0.70mm NSMD Pad, 0.85mm Solder Mask Opening, HASL Finish

- Size: 220x140x2.36 mm

#### Package

- Substrate Thickness: 2.97 mm.

- Package size: 40 x 40 mm

- Die size: 23.8 x 20.4 mm, XQR4VLX200

- Column: 0.56mm diameter with 1.0mm pitch

- Pad size: 0.80mm

#### Test Condition

- Temperature Cycle, 0°C to 100°C

- 30 min/cycle (10min. Dwell and 5min. Ramp)

#### Test Results

- 24 out of 27 units failed until 5305 cycles

| Package | Cycles<br>Completed | # Tested | # Failed | 1st. Failure<br>(Cycles) | Characteristic<br>Life (Cycles) |

|---------|---------------------|----------|----------|--------------------------|---------------------------------|

| CF1509  | 5305                | 27       | 44       | 3892                     | 4707                            |

β=13.5523, η=4707.0417, ρ=0.9639

#### Failure Analysis

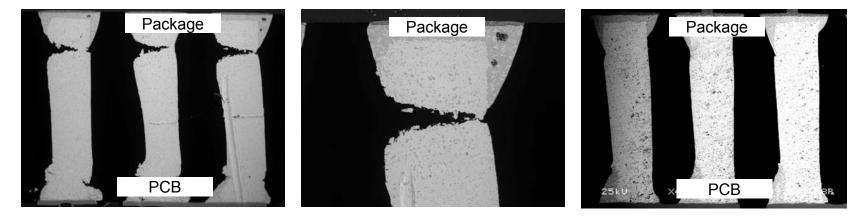

Cross section of the failing chain showed that the failure occurred at the columns on the package side.

SEM photo of crack columns of First Fail Unit – SN112

SEM photo of good columns

# Appendix: XQR4VLX200-CF1509 Moisture PreConditioning Qualification Results

- XQR4VLX200-CF1509 has been put through MSL 1 Preconditioning (168 hrs. 85°C/85% RH) followed by 25°C Electrical Test & CSAM. Results are as follows:

- 15/15 units pass Electrical testing after Preconditioning.

- I/1 units pass CSAM inspection. See below.

# Appendix: XQR4VLX200-CF1509 Package Temperature Cycling Qualification Results

- Temperature Cycling Test Conditions:

- Condition B (-55 to 125° C) followed by 25°C Electrical Test on fully electrically functional die.

- Results:

- 14/14 units pass Electrical testing at 1000, 1500 & 2000 3000 & 4000 cycle readpoints.

### Appendix: XQR CF Package Outgassing Results

- CF Package Material Set passes outgassing criteria per ASTM E-595 testing and criteria.

- Key Outgassing Parameters:

- TML (Total Mass Loss)

- CVCM (Collected Volatile Condensable Materials)

- Specification:

- TML < 1%

- CVCM < 0.1%

- CF Package Outgassing Data is as follows:

|         | Underfill (LP2) | Lid Adhesive (ATI) |

|---------|-----------------|--------------------|

| TML %:  | 0.21%           | 0.36%              |

| CVCM %: | 0.01%           | 0.01%              |

### Appendix: XQR CF Package Wear Out Test and Latch Up and ESD Test Summary

#### Wear Out Test Summary for M-Grade and V-Grade Products

#### Table 4: Wear-out Test Summary

| Mechanism                | Sample                                                                                                  | Condition                                           | Conditions                                                            | Fallure                                                                                                  | Comments                                               | Product Life           | Time at Tj of         |

|--------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|-----------------------|

| Mechanism                | Size                                                                                                    | sofStress<br>Test                                   | of Quoted<br>results                                                  | Criterion                                                                                                | Comments .                                             | 100°C                  | 125°C                 |

| Hot Carrier<br>Injection | 20 per<br>condition                                                                                     | 3 voltages<br>25°⊂                                  | ≥1.09CVcc<br>123 <sup>0</sup> C for com,<br>-65 <sup>0</sup> C for 10 | Δldsat ><br>10%                                                                                          | Worst at<br>cold for IO<br>NMOS &<br>hot for<br>others | 53 years               | 50 years              |

| Vtstability              | 10 per<br>condition                                                                                     | 3 voltages/3<br>temps, 100 to<br>160 <sup>6</sup> C | 1.05 Vec,<br>1259C                                                    | 100mV for<br>core/mid<br>oxide;<br>110mV for<br>2.5V<br>device;<br>200mV for<br>3.3V device              | Verified by<br>produce<br>HTOL                         | 42 years               | 12 years              |

| Gaie oxide<br>TDDB       | 20 per<br>condition                                                                                     | 3 voltages/3<br>temp, 300°C<br>to 160°C             | 1.05 Vec                                                              | Ign/Ign -<br>1>1.2 for<br>core<br>NMC6/mi<br>d oxide & 2<br>for core<br>PMC6,>10<br>for IO CDP<br>= 0.1% | Equivalent<br>to 11 HTs<br>after 10<br>years           | 157 years<br>for L3200 | 27 years<br>for LX200 |

| Electromi-<br>gration    | 20-24 per<br>condition                                                                                  | 250°C to<br>250°C                                   | design rule<br>J <sub>ann</sub> at 100 <sup>0</sup> C                 | Δ R/R<br>>20% CDF<br>= 100 PPM                                                                           | Equivalent<br>to 1 FIT<br>after 10<br>years            | 34 years               | 6 years               |

| VRDB                     | total test<br>areas<br>>0.2cm*2<br>for area; ><br>1E3cm for<br>STI edge;<br>> 1E4cm<br>for poly<br>edge | Vidiage ramp<br>@ 25 <sup>9</sup> C                 | DD                                                                    | lgn/lgn -<br>1>12 for<br>core∣<br>exide,>10<br>for 10                                                    | Broode<br>1.1Vcc-(VB<br>D-(2.3 Vcc                     | pass                   | Pass                  |

#### Table 4: Wear-out Test Summary (Continued)

|              | Sample                 | Condition                             | Conditions           | Failure                                                                         |                                             | Product Life | Time at Tj of |

|--------------|------------------------|---------------------------------------|----------------------|---------------------------------------------------------------------------------|---------------------------------------------|--------------|---------------|

| Mechanism    | Size                   | sofStress<br>Test                     | of Quoted<br>results | Criterion                                                                       | Criterion Comments                          | 100°C        | 125°C         |

| SM           | 20-30 per<br>condition | 3 tempera-<br>turos 1000<br>hours     | pass or fail         | Δ R/R<br>>20% of<br>EDR for<br>single Via;<br>Δ R/R<br>> 2.5% for<br>via chains | No sample<br>seress fail<br>allowed         | разя         | Pass          |

| BEOL<br>TDDB | 16-20 per<br>condition | 125 <sup>0</sup> C-203 <sup>0</sup> C | 1.1 Var, 100°C       | line to line<br>leakage > 1<br>µA<br>CDF=0.01<br>%                              | Equivalent<br>to 1 FIT<br>after 10<br>years | 646 years    | 214 years     |

The Latch-Up, HBM and CDM tests are performed according to the following industry standard specifications:

- Latch-Up: JESD-78, ±200mA and 1.5 x V<sup>\*</sup><sub>DD</sub>

- HBM: JESD-22-A114, ESDA STM5.1

- CDM: JESD-22-A115, ESDA STM5.3.1

Table 5: Mask Qualification Summary

| Device     | Latoh-Up | HBM Passing Voltage | CDM Passing Voltage |

|------------|----------|---------------------|---------------------|

| XQ4VLX60   | pass     | 2000V               | 400V                |

| XQR4VLX200 | Pass     | 2000V               | 350V                |

| XQR4VSX55  | pass     | 2000V               | 400V                |

| XQR4VFX60  | pass     | 2000V               | 500V                |

\*Latch up performed at 125°C