# TECH LIBRARY KAFB,

NASA Reference Publication 1122

November 1984

Procedures for Precap Visual Inspection

> LOAN COPY: RETURN TO AFWL TECHNICAL LIBRARY KIRTLAND AFB, N.M. 87117

## NASA Reference Publication 1122

1984

# Procedures for Precap Visual Inspection

Office of the Chief Engineer National Aeronautics and Space Administration Washington, D.C.

Scientific and Technical Information Branch

# **Library of Congress Cataloging in Publication Data** Main entry under title:

Procedures for precap visual inspection.

(NASA Reference Publication; 1122)

Bibliography: p. 75

1. Integrated circuits—Inspection I. United States.

National Aeronautics and Space Administration. Scientific and Technical Information Branch. II. Series. TK7874,P74 1984 621.381'.73'0287 84-16628

#### **FOREWORD**

This document describes the techniques that can be employed for the final precap visual inspection of microcircuits used in electronic system components. It can also serve as an effective tool in training personnel to perform these tasks in an efficient and reliable manner.

To aid in the training of personnel unfamiliar with microcircuits, the first chapter includes a brief description of the processing techniques that are commonly used in industry for the manufacture of monolithic and hybrid components.

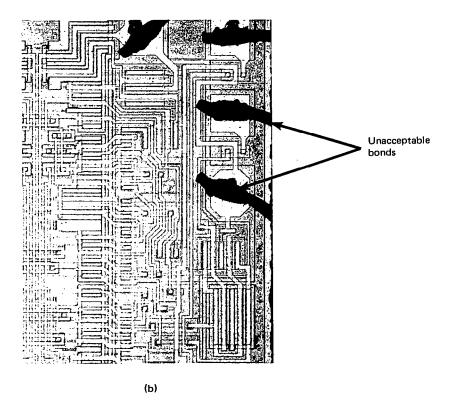

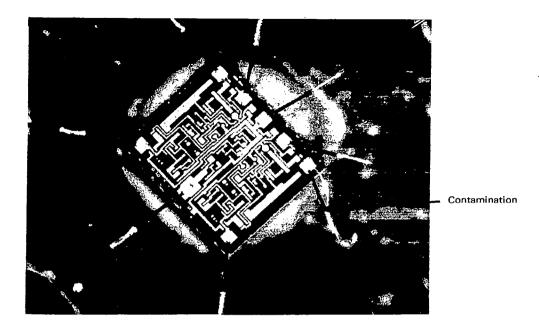

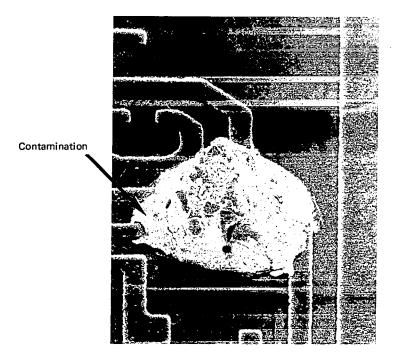

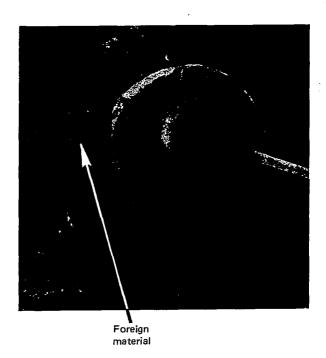

Subsequent sections describe the imperfections that may be encountered in the precap visual inspection of these semiconductor components. Photomicrographs are used to illustrate problem areas, such as scratches, voids, adhesions, bridging of the metallization, corrosion of the aluminum, misalignment, and wire bonding faults. Acceptance and rejection criteria are established for many defects.

The information contained herein may be used for the guidance of NASA personnel. It is distributed to other government agencies and contractors as a courtesy. Although portions of it may be altered, revised, or rescinded, depending on new developments, these changes may not be imparted directly to the holders of this document, but may be provided instead to NASA personnel by means of memoranda or other correspondence through limited channels. Users of this document should therefore keep abreast of the state of the art of precap visual inspection.

Neither the United States Government nor any personnel acting on behalf of the United States Government assumes any liability for the use of this document.

MILTON A. SILVEIRA Chief Engineer

| · — |   | <br>- |  |

|-----|---|-------|--|

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     | • |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   | •     |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

|     |   |       |  |

### **CONTENTS**

|                                                                                                          | Page                       |

|----------------------------------------------------------------------------------------------------------|----------------------------|

| GLOSSARY                                                                                                 | vii                        |

| INTRODUCTION                                                                                             | 1                          |

| INTEGRATED CIRCUIT PROCESSING                                                                            | 2                          |

| Monolithic Circuits                                                                                      | 2                          |

| Fabrication                                                                                              | 2<br>8                     |

| Hybrid Circuits                                                                                          | 11                         |

| MONOLITHIC CIRCUIT DEFECTS                                                                               | 15                         |

| Die                                                                                                      | 15                         |

| Metallization Diffusion, Passivation, and Dielectric Isolation Glassivation Scribing Thin-Film Resistors | 15<br>21<br>28<br>33<br>33 |

| Wire Bonding                                                                                             | 41                         |

| Internal Packaging                                                                                       | 52                         |

| Foreign Material                                                                                         | 52<br>57                   |

| HYBRID CIRCUIT DEFECTS                                                                                   | 64                         |

| Substrate                                                                                                | 64<br>65<br>65<br>70<br>71 |

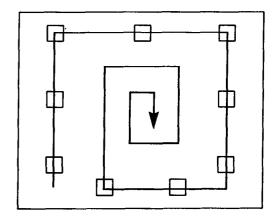

| PRECAP SCENARIO                                                                                          | 71                         |

| SUMMARY                                                                                                  | 73                         |

| ACKNOWLEDGMENT                                                                                           | 73                         |

| REFERENCES                                                                                               | 75                         |

| RIRI IOGR APHY                                                                                           | 75                         |

|  |   | e <sup>c</sup> |  |

|--|---|----------------|--|

|  |   |                |  |

|  |   |                |  |

|  |   | •              |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  | • |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  | • |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

|  |   |                |  |

#### **GLOSSARY**

Bimetallic-Metallurgical system consisting of two different metals.

Chip—Piece of a silicon wafer in which a transistor, or an entire integrated circuit, is contained.

Contact window—Opening etched in the silicon oxide layer to allow ohmic contact to the underlying silicon.

Dice-(v) To break a silicon wafer into individual pieces; (n) pieces of silicon wafer (plural of die-see die).

Die-Singular of dice-individual piece of silicon wafer in which a transistor, or a whole integrated circuit, is contained (see chip).

Epitaxial growth (epitaxy)-Process by which single-crystal material is grown on top of another single crystal.

Eutectic temperature-Lowest temperature at which a two-element metal system can melt.

Evaporation (vapor deposition)—Method of depositing one material on top of another. Atoms of the first material are boiled off a heated filament and deposited on the second material. The process is carried out in a vacuum.

Interference color—Color that appears in thin films as a result of destructive interference of the light waves as they are transmitted through the film and reflected back from the substrate.

Laminar flow hood—Hood in which airflow in the work area is uniform in its flow pattern and which is relatively free of back-streaming contamination.

Photosensitivity—Property of a material whereby its chemical makeup is altered by exposure to light.

Mil-Unit of measure equal to 0.001 inch.

Passivation layer—Layer of silicon dioxide that is grown on the die surface to act as an insulating medium.

Scribing-Process in which a sharp diamond stylus is moved along a single-crystal silicon wafer, creating stresses in the crystal lattice.

Scrubbing—Process used during soldering in which one of the parts is rapidly moved across the other. The rubbing motion breaks up oxide formations.

Wafer-Slice of semiconductor material.

| · |     |  |  |

|---|-----|--|--|

|   |     |  |  |

|   | · . |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

|   |     |  |  |

#### INTRODUCTION

The need for highly reliable electronic components has become a critical factor in electronic systems as the demands and complexity of these systems have increased. This is true for both space missions and the consumer market. Consumers have come to expect reliable electronic systems. The same is true for spacecraft designers. However, spacecraft differ in four areas:

- They are exposed to a unique environment.

- After they are launched, unmanned orbiters cannot be repaired (until shuttle-based repair missions become a reality).

- Production is limited to one or at most a few models, increasing the total production cost.

- A high rate of success is essential for some or all

of the following reasons: budget constraints,

national defense, and the dependence of human

lives on the information supplied by spacecraft.

In addition, these requirements have become even more stringent with the advent of longer missions and reusable spacecraft such as the shuttle.

The reliability of an electronic system depends entirely on the reliability (along with good circuit design) of the electronic components that make up the system. Once the concern of specialists, quality is becoming central to production. The detection of errors is being shifted from final inspection to production and preproduction phases all the way to top management. Original equipment manufacturers (OEM) once accepted good and bad parts from vendors and performed their own testing to weed out bad parts-a costly procedure. More and more original equipment manufacturers are recognizing the need for working with vendors to produce good parts in the beginning of manufacturing to ensure that incoming components meet quality assurance levels without the need for extensive screening. Until this level of assurance is met, most users of high-reliability parts will continue to specify elaborate screening procedures. These additional screens have increased the cost to three or four times that of off-the-shelf components. The screening procedures are effective in removing many parts with built-in manufacturing defects due to deficiency in workmanship or design. However, a significant number of such parts escape these screens.

Failure analyses conducted at Goddard Space Flight Center (GSFC) have shown that a large percentage of microcircuit failures caused by manufacturing defects are attributable to poor workmanship. An important method of detecting workmanship problems is the final precap visual inspection performed during the last step in fabrication before sealing the device within its package. In this inspection, each microcircuit is examined (100 percent inspection) at various magnifications and viewing angles.

Experience has shown that manufacturers do not remove all devices that show poor workmanship. It is therefore inevitable that some of the devices find their way into high-reliability procurements. There are several reasons for the inefficient removal of questionable devices:

- Despite screening standards (for example, MIL-STD-883B), the vendor and user do not completely agree on what constitutes a visual reject.

- Because of the complexity of the parts and often the specification, accept/reject criteria may be misinterpreted.

- The inspector at the final precap visual station examines many devices and may become careless.

- The inspector is not always aware of the seriousness of evident imperfections and/or does not ask for clarification when uncertain.

- At times, standards are relaxed (with and without approval) for hard-to-produce state-of-theart devices.

As a result, users of extremely high-reliability material often perform their own final precap visual inspection

in addition to or rather than the normal vendor inspection. This makes it necessary for procuring agencies to have personnel who are experienced and trained in the complexities of semiconductor fabrication and inspection. Unfortunately, there are not enough qualified personnel to perform visual examinations with a high degree of competence. To alleviate this problem, this document has been prepared to aid in instructing personnel in the art and science of visual inspection.

The material in this document closely follows that of MIL-STD-883B, Methods 2010 and 2017, condition A (class S). Users of class B components should consult Methods 2010 and 2017, condition B, for details. Although most of the text concentrates on microcircuits, the techniques apply to the visual inspection of a variety of electronic components. The text is divided into two major parts. The first part discusses integrated circuit processing of both monolithic and hybrid devices for personnel who are unfamiliar with integrated circuits. The second part discusses defects that can be found in both monolithic and hybrid circuits. The major emphasis is on monolithic device defects. The discussion of hybrids is concerned with areas of fabrication unique to hybrid circuits.

#### INTEGRATED CIRCUIT PROCESSING

#### **Monolithic Circuits**

Fabrication

Two basic types of electronic components can be fabricated with integrated circuit technology: bipolar and unipolar. These two designations refer to the type of charge carrier present in the device. In a bipolar device, there are two charge carriers of opposite polarity; in a unipolar device, there is only one charge carrier. Bipolar devices are generally classified by their circuit type: transistor, transistor logic (T<sup>2</sup>L), emitter coupled logic (ECL), integrated injection logic (I<sup>2</sup>L), or diode-transistor logic (DTL). Unipolar devices are classified on the basis of conductivity type (p-channel or n-channel), as well as other processing variations. Unipolar devices are commonly referred to as either field effect transistors (FET) or metal oxide semiconductors (MOS).

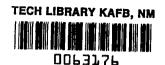

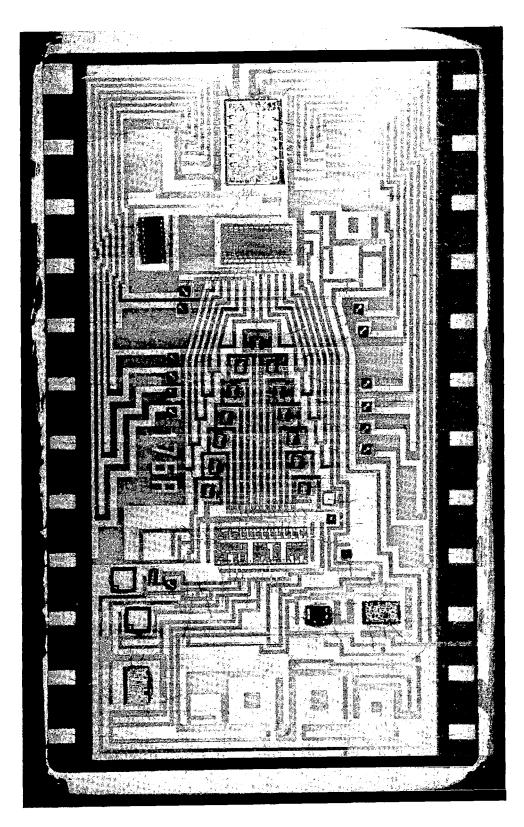

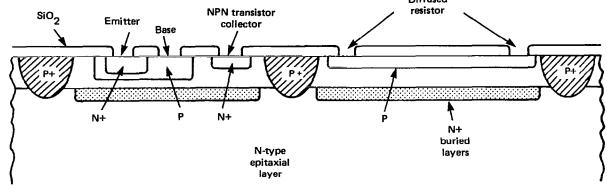

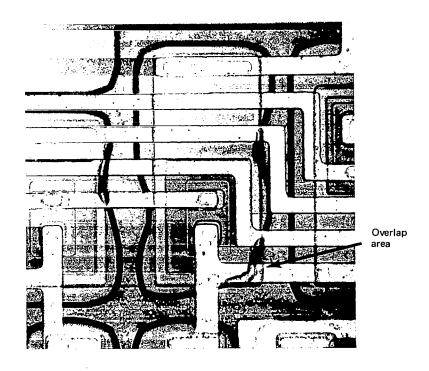

A bipolar integrated circuit is made by combining different types of bipolar components on a silicon chip (fig. 1). Similarly, various MOS components are integrated to form an MOS integrated circuit. Recent advances in semiconductor technology have permitted both MOS and bipolar components to be fabricated in a single integrated circuit chip.

The number of logic components, usually referred to as gates, on an integrated circuit chip defines the complexity of the device. One to ten gates are referred to as small-scale integration (SSI). Ten to one hundred gates are referred to as medium-scale integration (MSI). Large-scale integration (LSI) corresponds to 100 to 1000 gates on one integrated circuit chip. Each very-large-scale integration (VLSI) chip contains from 1000 to 10000 gates.

Similar processes, materials, and design principles are used in the fabrication of both bipolar and MOS integrated circuits. These processes include epitaxial growth, masked impurity diffusion, oxide growth, oxide etching, and evaporation.

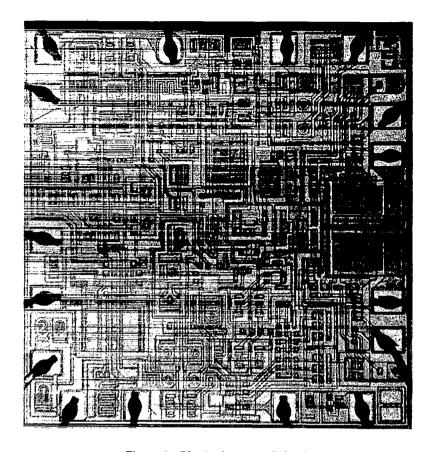

The manufacture of an integrated circuit begins with a large silicon wafer, usually 3 to 4 inches in diameter, as shown in figure 2. The wafers themselves are cut in thin slices from a large uniform crystal grown under tightly controlled environmental and electrical conditions from a seed crystal (a small, single crystal of silicon having very few dislocations and oriented in the predetermined plane). The material is doped with the impurities (boron, antimony, and phosphorus) to produce the desired electrical characteristics. After being cut, the wafers are lapped on abrasive lapping machines to the thicknesses required for integrated circuits. The lapped wafers are polished and are then ready for the next phases of fabrication.

With this brief description of wafer processing, we can now proceed to a more detailed consideration of the individual wafer-processing steps. These steps will be considered in the order in which they are performed on integrated circuit wafers.

After the wafers are prepared, the next step in the fabrication process is epitaxial growth—the ordered growth of a monocrystalline layer on the single-crystal substrate so that the lattice structure of the resulting layer is an exact extension of the substrate crystal structure. It is in this epitaxial layer that the components of the integrated circuit are fabricated. A feature of epitaxy is that the doping of the epitaxial

Figure 1. Bipolar integrated circuit.

Figure 2. Wafers before and after processing.

layer is relatively independent of the substrate doping, permitting high-quality, lightly doped layers to be grown on heavily doped substrates of either conductivity. For example, the n-type epitaxial layer on a heavily n+-doped layer is used for the transistors and other circuit elements in an integrated circuit.

The epitaxial growth of silicon on a wafer is produced by a process involving the decomposition of a silicon compound. The most commonly used reactions are the hydrogen reduction of silicon tetrachloride or trichlorosilane and the pyrolysis of silane or dichlorosilane. Each of these processes has some disadvantages. High temperatures are required and hydrochloric acid is produced during hydrogen reduction epitaxy; a lower deposition rate and the high cost of silane are drawbacks for pyrolysis.

After the epitaxial layer is grown, the wafer is cleaned and polished. A thin layer of oxide (SiO<sub>2</sub>) is formed

over the entire wafer. This oxide is grown by exposing the epitaxial layer to an oxygen atmosphere while it is heated to approximately 1000°C. The diffusion of impurities through silicon dioxide is several orders of magnitude lower than that through silicon. This property is used during subsequent stages of wafer fabrication.

An essential requirement of fabricating integrated circuits is the ability to introduce controlled quantities of dopant impurity atoms into selected regions of the wafer. One method of producing impurity distribution is by diffusion. This process also causes the redistribution of impurities when a doped crystal is heated. Selectivity of areas to be diffused is provided by a mask on the surface of the wafer through which the new impurities are to be introduced.

The results of diffusion are dependent on a number of process variables:

- Doping level and distribution within the substrate

- Temperature and time the diffusion is permitted to continue

- Characteristics of the dopants

- Amount and form of dopant available.

Because diffusion is performed at a high temperature (i.e., 1000 to 1350°C), it is more difficult to control the profile when making a second diffusion into a region that was previously diffused than to control a first diffusion (e.g., the diffusion of an emitter into a previously diffused base region). While the emitter diffusion is in process, the dopant distributed in the base diffusion will continue to move from the higher concentration region to the lower. This behavior must be considered in programming the diffusion schedule to ensure that all diffused regions will have the desired gradients (impurity concentration) and junction locations.

Another technique for introducing impurities into the substrate is by ion implantation. This process introduces a layer of impurities just below the surface of the host material by bombarding it with a beam of ions (of the type impurity to be implanted) whose energy is in the range of one to several hundred kiloelectron volts. The advantages of ion implantation include the following:

- It offers precise control over the number of impurities introduced into the silicon.

- It is a low temperature process.

- Impurity layers can be introduced completely below the surface.

- There is a wide choice of mask material.

- Implanted junctions can be self-aligned to the mask edge.

- Impurity layers can be introduced in any order in the processing sequence.

The disadvantages of ion implantation are that complex expensive machinery is required and the junctions are not automatically passivated.

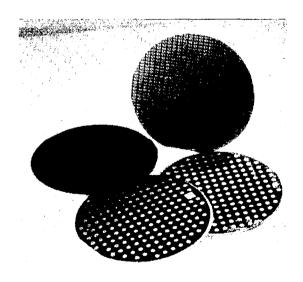

Diffusions and ion implantation require the selective removal of the silicon dioxide to form openings through which impurities may be introduced. Figure 3 illustrates the photoetching method used for this removal.

During the photolithographic process, the wafer is coated with a uniform film of a photosensitive emulsion such as Kodak photoresist KPR (fig. 3a). A large black and white layout of the desired pattern of openings is made and then reduced photographically. This negative, or stencil, of the required dimensions is placed as a mask over the photoresist. By exposing the photoresist to ultraviolet light through the mask (fig. 3b), the photoresist becomes polymerized under the transparent region of the stencil. The mask is then removed, and the wafer is "developed" by using a chemical that dissolves the unexposed portions of the photoresist film and leaves the desired surface pattern (fig. 3c). The emulsion not removed in development is fixed, so that it becomes resistant to the corrosive etches used next. The wafer is immersed in an etching solution of hydrofluoric acid, which removes the oxide from the areas through which the dopants are to be diffused. The portions of the SiO, protected by photoresist are unaffected by the acid. The resist mask is removed with a chemical solvent by means of a mechanical abrasion process (fig. 3d), and the wafer is ready for any subsequent process, for example, diffusion (fig. 3e).

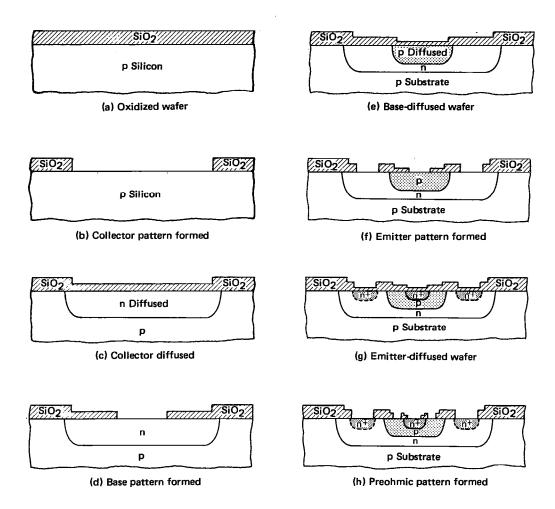

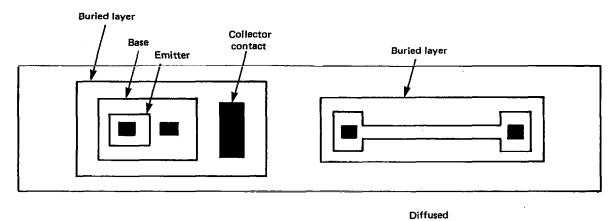

Figure 4 illustrates the diffused collector process (for an NPN transistor structure), which consists of three

Figure 3. Photolithographic process steps.

Figure 4. Process steps for the diffused collector process (Warner, 1974).

sequential diffusion cycles for forming the three junctions in a monolithic die. The substrate is a p-type silicon wafer on which a layer of silicon dioxide has been thermally grown (fig. 4a). The silicon dioxide is selectively etched using the photolithographic process to expose specific areas into which an n-type impurity is to be diffused (fig. 4b). The wafer is then subjected to an n-type phosphorus diffusion (fig. 4c), which forms the isolated collectors of the transistors, as well as isolated n-type islands, into which resistors and elements of diodes and capacitors can be diffused. After a new layer of silicon dioxide is grown, a window is opened to form the base pattern (figs. 4c and 4d). The base is diffused with a p-type impurity such as boron, and silicon dioxide is regrown (fig. 4e). New windows are etched in the oxide layer that covers the base and collector regions.

A subsequent n-type diffusion forms an emitter in the base region and a high-concentration ohmic contact in the collector (fig. 4f). After diffusion of the phosphorus and oxide regrowth (fig. 4g) over the diffused areas, new windows are opened in the silicon dioxide (fig. 4h). These windows will allow ohmic contact to the circuit elements after metallization deposition.

The wafers are then cleaned and placed in a vacuum evaporation apparatus. The silicon wafer is coated with a layer of hyperpure metal(s). The metal film is typically 0.8 to  $1.2 \mu m$  (8000 to  $12 000 \text{\AA}$ ) thick.

To obtain a reasonably clean film, the evaporation must take place in a moderately high vacuum  $<10^{-4}$  N/m<sup>2</sup> ( $<10^{-6}$  torr). The surface of the wafer must also be dry and free of stains, film, and dust in order to obtain good adherence of the deposited metal film.

Proper distance of the wafer from the evaporant source and location of the wafer with respect to the source are necessary to ensure uniform thickness of the evaporated layer(s) and to prevent thinning (shadowing) of the layer over steps in the various oxide diffusion and contact windows. The thickness of the layer(s) is also controlled by the temperature of the source and the time allowed for deposition. After the metal layer(s) is deposited, the metallized surface within the area of the matrix of circuits on the silicon wafer must not be touched by tweezers or other handling tools.

The geometry of the metal contacts and interconnection is produced by the inverse of the photolithographic process used for creating windows in the oxide. The photoresist is placed on the metal layer on the silicon wafer, but is exposed to a pattern in which the interconnection design on the glass plate is transparent, rather than opaque. In developing the resist, all portions are washed away except the exposed pattern. The metal layer is etched, and all metal is attacked except the interconnection pattern, which is protected by the photoresist mask. The resist is stripped, and the wafer then has a matrix of circuits, complete with contacts and interconnections.

Thin-film components (discussed more fully in the following section), usually resistors, can be fabricated on top of the passivated silicon monolithic integrated circuit by using vacuum evaporation techniques similar to those used to deposit the interconnection metallization. The advantages of combining thin-film and semiconductor technologies are:

- Greater degree of design freedom

- Greater range of component values than those possible with diffused resistors

- Improved tolerances

- On-chip adjustment of resistance by laser trimming.

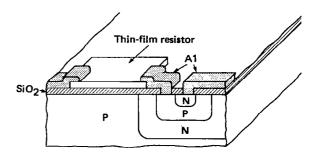

Figure 5 illustrates a compatible thin-film integrated circuit that has a thin-film resistor in series with a transistor.

One operation that is often overlooked in a discussion of integrated circuit processing is the cleaning of the wafers. Clean processing is a key to producing devices whose characteristics are stable and reproducible.

Figure 5. Monolithic integrated circuit with resistor in series with the base of a transistor.

More than half of the operations in making a silicon integrated circuit are for wafer cleaning between processing steps.

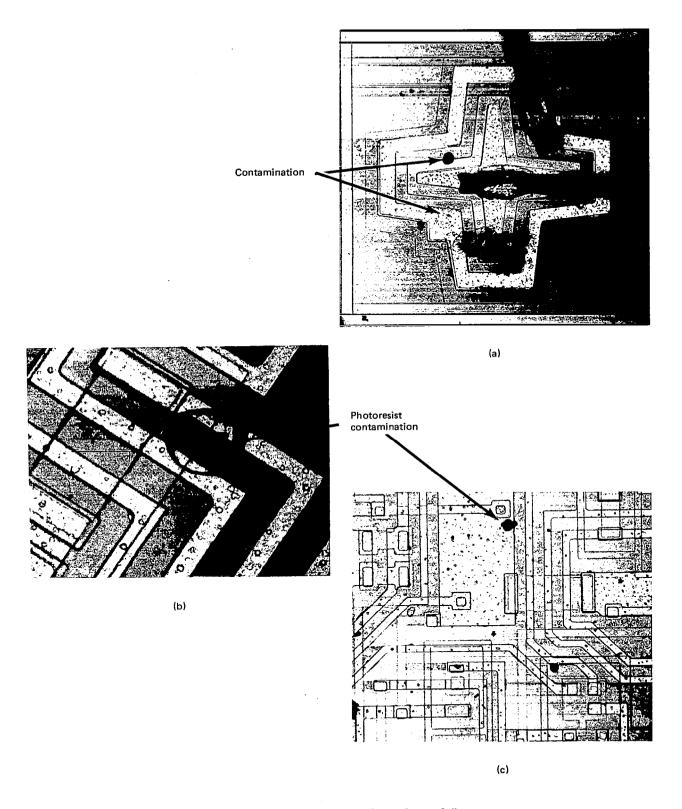

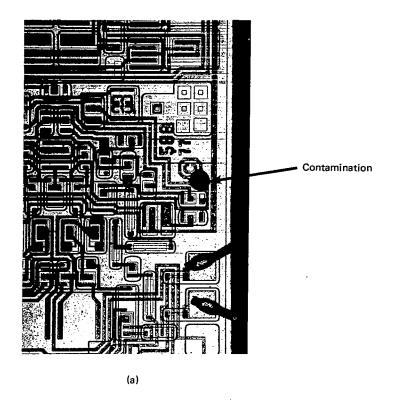

Surface contaminants fall into three broad classes: molecular, ionic, or atomic. Molecular contaminants such as waxes, oils, or resins include oil from fingers or greasy films picked up from the air or from plastic containers. Photoresists used for defining patterns on the surface of the wafer are also sources of molecular contaminants, as are organic solvent residues. Hydrochloric acid and caustic solutions used as etchants are sources of ionic contaminants. These contaminants adhere to the surface by adsorption or chemisorption and remain even after the surface is washed in deionized water. Atomic contaminants include copper, gold, and other heavy metals.

A suitable wafer-cleaning procedure is based on the use of two solutions that contain volatile reagents diluted with pure deionized or quartz-distilled water. The first solution contains ammonium hydroxide and hydrogen peroxide. It removes organic contaminants by the solvating action of the ammonium hydroxide and the oxidizing action of the peroxide. The second solution is used to remove heavy metals and to prevent their displacement replating from the solution by forming soluble complexes from the resulting ions. This solution contains hydrogen peroxide and hydrochloric acid. After cleaning at high temperature (75°C), the wafers are spun dry.

To complete the wafer processing, a passivation layer of phosphosilicate glass or other dielectric layer is deposited on the wafer surface. The passivation layer is a protective mechanism that can prevent conductive residue particles that result from packaging from short-circuiting metallization. The passivation layer also contributes to a higher level of reliability by acting as getter (collector) or barrier to mobile ions left on the surface of the device after the final metallization wash. Other dielectric layers are plasma-deposited silicon nitride films or phosphosilicate glass (PSG), followed by a layer of polyimide plastic (Kapton). Windows in the passivation are cut out for external connection to the metallization.

Up to this point, all process steps were carried out on full silicon wafers. To utilize the wafers, they must be separated into individual chips; this step is accomplished in the scribing and dicing operation. Before the actual scribing, the oxide on the wafer is preferentially removed along each scribing path so that scribing can be performed on bare silicon. This forms a scribe grid for the dicing operation.

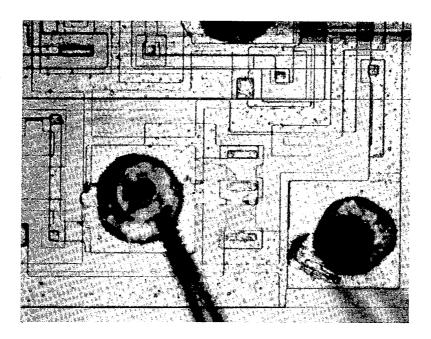

The finished wafer is placed on a vacuum chuck, which is capable of rotation about a vertical axis and translation in both horizontal directions. Typically, a diamond stylus loaded with a suitable weight is drawn across each scribing path, first in one direction and again after the wafer is rotated 90°. After removal from the chuck, the wafer is separated into individual dice by applying pressure to the wafer. The finished dice are then cleaned in a solvent (such as trichloroethylene) to remove scribing dust and other foreign matter. This cleaning completes the fabrication of integrated circuits on wafers. The individual dice are then ready for mounting in the package (fig. 6).

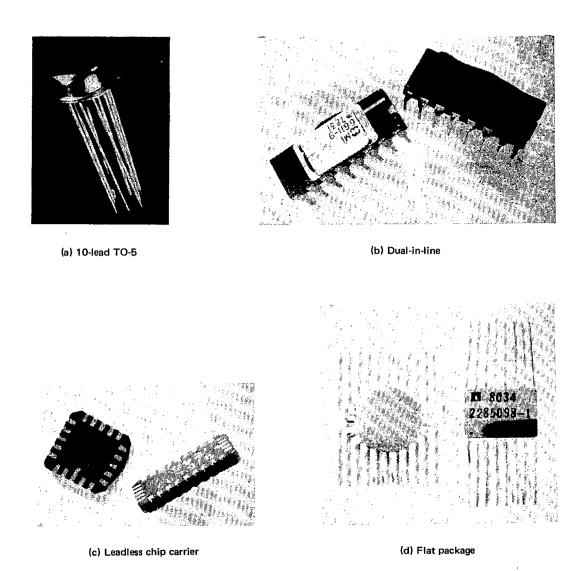

#### **Packaging**

In a monolithic integrated circuit, the die normally requires no isolation from the package header because the substrate of the monolithic integrated circuit is usually at the lowest circuit potential and is often grounded. Therefore, there is no reason to isolate the die from the header of the package even if it is metallic. The die can be mounted directly to the header. Figure 7 shows some of the variety of packages available. When mounting and bonding a die to a metallic header (such as a TO-type can), a gold/silicon eutectic bonding material is used. In the case of ceramic flatpacks and dual-in-line packages that do not have metallized islands for eutectic bonding, an

Figure 6. Completed dice ready for packaging.

epoxy resin is used to bond the die. Bonding temperatures range from 300 to 500°C, and bonding times range from a few seconds to 5 minutes.

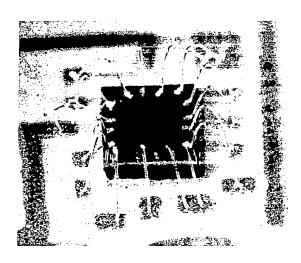

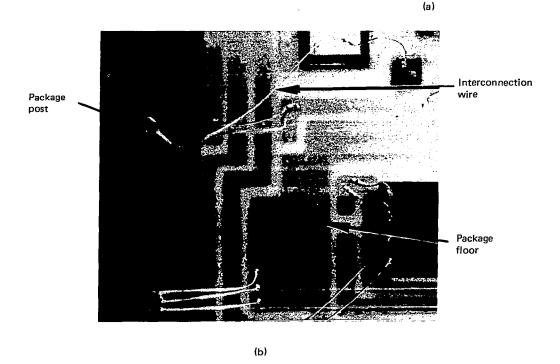

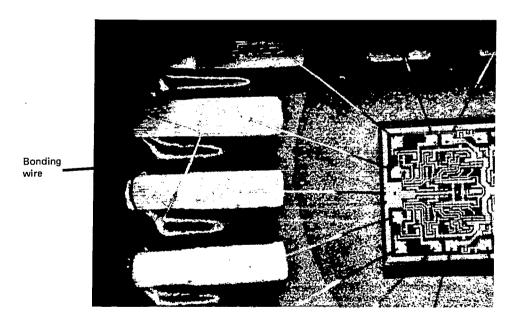

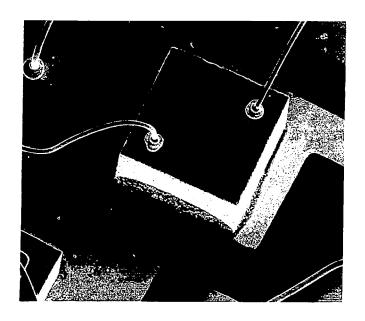

After the integrated circuit die has been attached to the package, electrical connections must be made between the die and the package by bonding fine-diameter wire (typically 0.7 or 1 mil in diameter) between the die metallization and the external leads that come through the package. Normally, gold or aluminum wire is used.

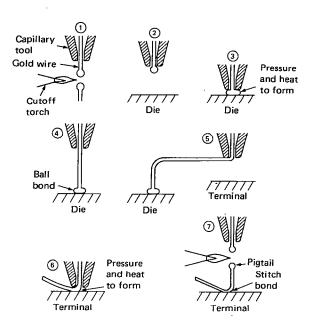

Making connections between the integrated circuit and the package leads usually involves two major bonding techniques: thermocompression (TC) and ultrasonic (US). The most popular techniques for TC bonding are "ball" bonding and "wedge" bonding. Figure 8 shows properly formed TC ball bonds. The TC ball bond is formed by feeding a wire through a capillary bonding tool. The wire end exiting the capillary is melted by a hydrogen flame (or capacitance discharge technique) to form the ball. The tool is then lowered onto the bonding surface, forcing the ball onto the surface under pressure and deforming the ball. (TC ball bonding can be applied to only gold wires.) The capillary tool is then raised while the wire is fed through the capillary. The wire is then terminated in a TC wedge bond on the ends of the external leads that come through the package. To form the wedge bond, the capillary tool is brought down on

Figure 7. Packages available for mounting integrated circuits.

(a) Optical micrograph

(b) Scanning electron micrograph

Figure 8. Typical ball bonds.

the external lead, producing the bond. The wire is then cut or flamed off to separate it from the bonding tool. Figure 9 shows a typical TC bonding sequence. The metal system involving bonds between the wire and external lead are usually monometallic to avoid intermetallic formation problems.

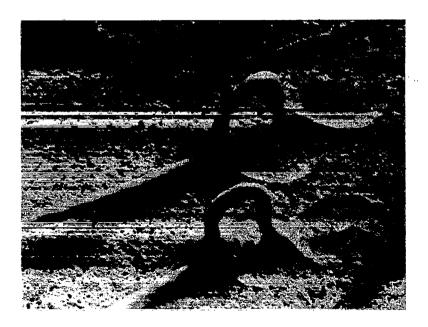

In TC bonding, the energy for bonding is supplied by heat and pressure. The heat is supplied to the bond by either heating the substrate or slightly heating the substrate in combination with capillary heating. The pressure affects a plastic deformation at the bond interface, whereas a diffusion occurs during the bonding cycle. Plastic deformation destroys interface films of oxides and dirt and achieves an optimum contact between the metal surfaces.

Figure 9. Steps required to make thermocompression wire bonds and wire run (National Bureau of Standards, 1972).

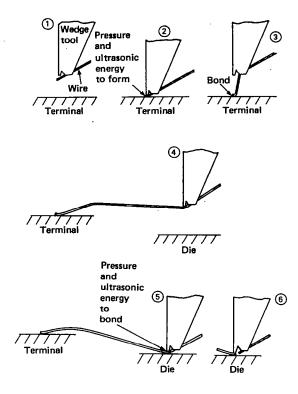

The second major method of bonding is US wire bonding (fig. 10). US bonding uses the same mechanism for making bonds as TC bonding. The ultrasonic energy (fig. 11), when applied to the metal to be bonded, renders it temporarily soft and plastic, causing it to flow under pressure. Heat is a by-product of the bonding process and is not necessary for forming the bond. Pressure and deformation of the bond will break up and sweep aside contaminants, exposing clean metal surfaces that are then able to form metallurgical welds. The bonding tool does not grip the wire, but moves cyclically across the top of the wire. Tool-to-wire coupling takes place by a series of microwelds that are repeatedly made and broken as the tool moves back and forth across the wire surface. US bonding is normally done at room temperature using aluminum wire and wedge bonding.

The ultrasonic wire can be significantly improved by heating the bonding area during bonding. This process is called "thermosonic" bonding. Thermosonic bonding is widely used in the manufacture of hybrids. Thermosonic bonding is used in place of TC bonding because the high temperatures utilized in TC bonding

(a) Optical micrograph

(b) Scanning electron micrograph

Figure 10. Typical aluminum wedge bond.

could cause the outgassing of epoxy materials used in hybrids. This outgassing could result in the deposition of contaminants on the die surface, possibly inhibiting the bonding processes. Normally gold wire and wedge and ball bonding are used in thermosonic bonding.

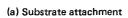

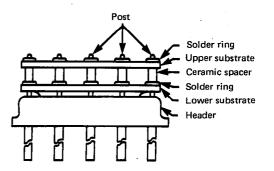

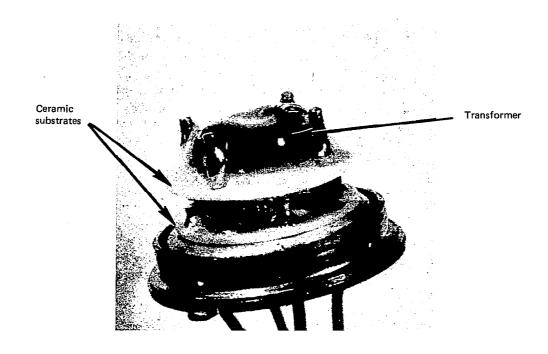

#### **Hybrid Circuits**

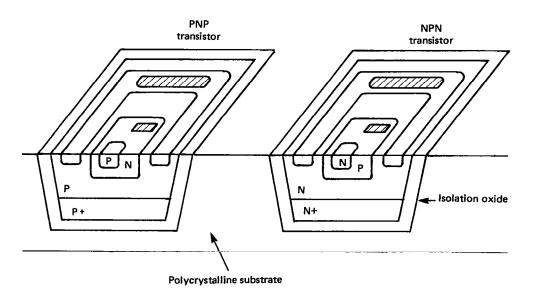

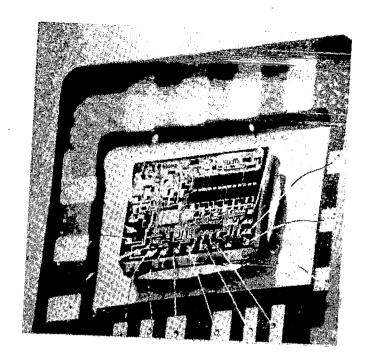

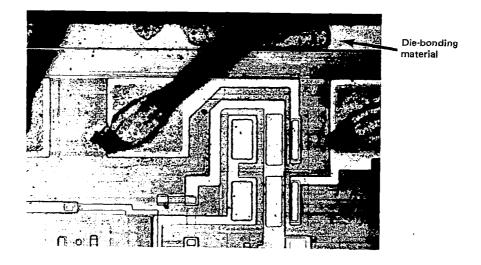

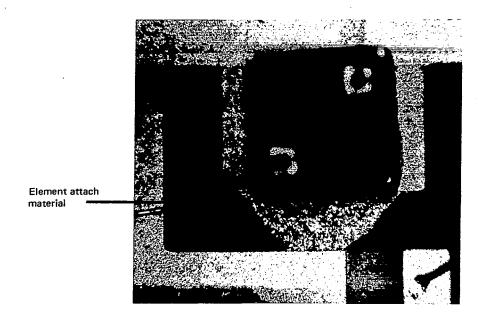

The hybrid integrated circuit, in contrast to the monolithic integrated circuit, consists of several component parts (transistors, diodes, resistors, capacitors, and monolithic integrated circuit chips or dice) attached to one common substrate (fig. 12). The concept of a hybrid is similar to the conventional discrete component circuit, except that the individual circuit elements consist of unencapsulated diffused or film

Figure 11. Steps required to make ultrasonic wire bonds and wire run (National Bureau of Standards, 1972).

components and the circuit is physically smaller than its discrete counterpart. In addition to the size advantage, the combination of film and semiconductor technologies provides a greater degree of design freedom, a wider range of component values, improved tolerances, and better electrical performance than either technology can provide separately. Hybrids can contain more than one monolithic integrated circuit chip or can consist solely of individual component parts (e.g., resistors or capacitors) or a monolithic integrated circuit chip used with individual component parts-if a device is housed in a single package, it is called a hybrid circuit. In hybrids, wire bonding is used between individual components or metallization runs on the common substrate to interconnect the constituent parts, and electrical isolation is provided by the physical separation of the component parts.

The fabrication and some of the assembly techniques of the semiconductor components (transistors, diodes, and integrated circuits) are the same as those already presented for monolithic devices. The attachment of

Figure 12. Hybrid integrated circuit.

the chips onto the ceramic substrate and the substrate onto the package header involves processes identical to monolithic integrated circuit bonding techniques. Some technologies and processes, such as thin and thick films, are unique to hybrids and will be discussed here.

Film circuits usually contain only resistors, capacitors, and conductor patterns. Film circuits are often supplemented by silicon transistors, diodes, and/or integrated circuit chips to form hybrid circuits. Materials used for these films include aluminum, nichrome, titanium, tantalum, tantalum pentoxide, gold, palladium, platinum, manganese oxide, and copper.

Thin films are deposited on inert substrates by chemical or vapor deposition techniques. These films are usually hundreds of angstroms to several microns thick. The substrate commonly used for thin-film circuits is of fine-grained 99+ percent alumina. Alumina is probably the most popular substrate material because of its high thermal conductivity, good resistance to chemical attack, and high compressive strength for lead bonding. Beryllia is sometimes used when increased thermal conductivity is desirable. The least expensive substrate is glass. Silicon can serve as a substrate, but it must be coated with a dielectric layer of silicon dioxide.

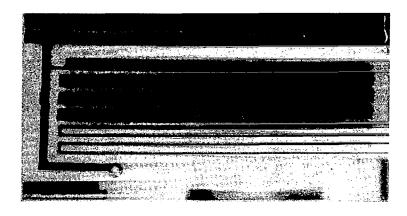

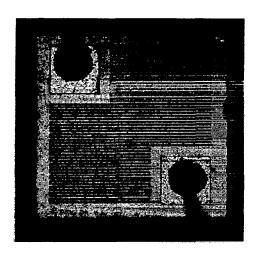

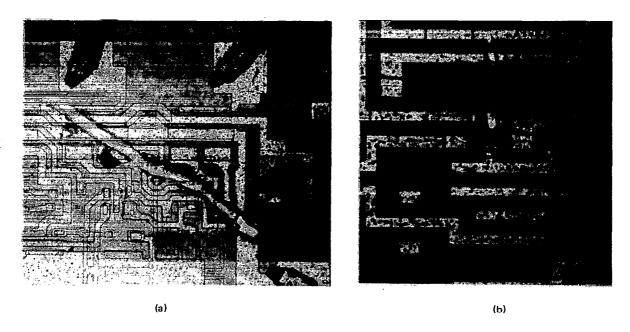

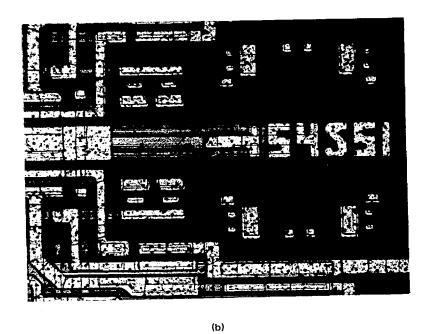

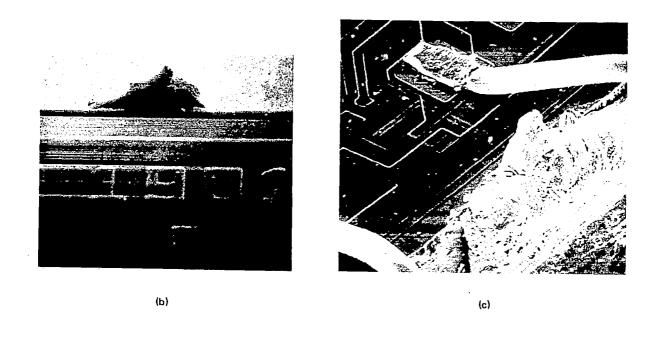

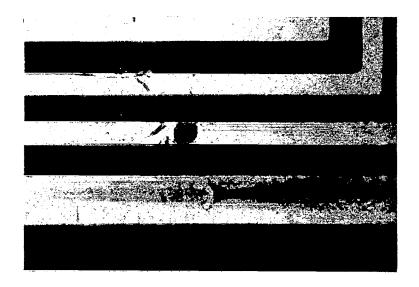

Most of the film circuits (figs. 13a and b) consist of elements patterned from several thin films of different materials. It is possible to form the components directly by selectively depositing the films through masks. However, the most popular technique for producing thin-film circuits is the subtractive process in which a multilayer film is deposited uniformly over the substrate, followed by selective removal of the material from the individual layers to form the desired components. The chemicals used to etch films are basically the same as those used to dissolve bulk silicon, but they are more dilute, resulting in a reduced etch rate minimizing attack on the photoresist and the underlying film.

Anodization, another process used to alter thin films, is defined as the electrochemical oxidation of a metal anode in an electrolytic cell. Anodization is used to form an adherent oxide film on certain metals called valve metals. Among these metals are tantalum, titanium, tungsten, and aluminum. Although the anodic process has been used to trim resistors to value

by creating an oxide at the expense of the parent film, laser trimming has been displacing the anodic method. Laser machining can be used to alter the geometry (changing the electrical path) of a thin-film resistor to increase its total resistance. Whereas trim anodization causes the change in resistance by reducing the effective thickness of the film and increasing its sheet resistance, laser trimming leaves the film properties substantially unchanged and varies the geometry.

Other types of thin films can be used for fabricating capacitors and conductor films, as well as resistors. The materials listed previously have specific properties and methods of deposition that can provide optimum component characteristics.

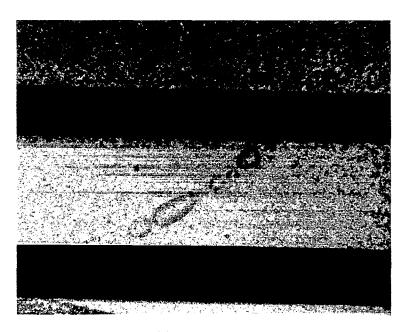

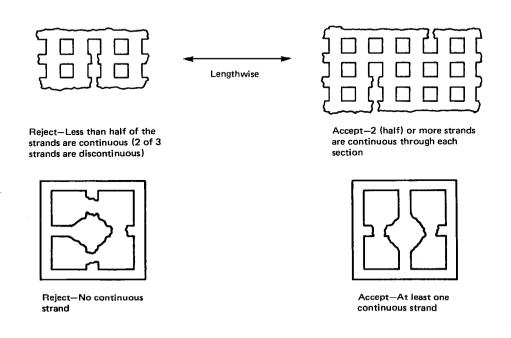

Another type of circuit used in the fabrication of hybrids is the thick-film circuit (fig. 13c). A thick-film circuit consists of passive components that are formed in place on the substrates by the selective application of materials in the form of pastes. These pastes are subsequently fired at high temperatures to form the desired films. As with thin-film circuits, discrete components such as transistor and integrated circuit chips are added to form a thick-film hybrid integrated circuit. The vertical and horizontal dimensions of the film pattern are two to five times larger than those of thin films.

The chief passive components formed from thick films are conductive interconnections, high-precision resistor networks, and capacitors. The materials that will ultimately form the film are prepared as a suspension of particles in a suitable organic vehicle of solvents. The suspended materials are then forced through a patterned screen to form the desired pattern. These thick-film inks, as they are called, consist of some or all of the following:

- Finely divided metal or alloy powders that give the film cohesion or joinability. For conductive films, these metals determine electrical conductivity.

- Metallic oxides that, for resistive films, determine the film resistivity.

- Finely divided glass frits, which chiefly determine the adherence of the film to the substrate

and of different metals in the film to each other.

- An organic vehicle for providing basic flow properties. Among these agents are solvents

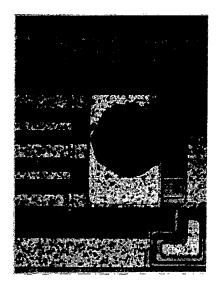

(a) Thin-film resistor on alumina substrate

(b) Thin-film resistor on silicon substrate

(c) Thick-film resistors

Figure 13. Thin- and thick-film resistors.

that dilute the paste and can later be evaporated and surfactants (surface active agents) that permit solid particles to be wet by the vehicle and properly dispersed within it.

After the ink has been screened on, it is air died and baked to dry out the volatile solvents. The circuits are then fired for approximately 45 minutes. The glass frits and the bonding materials melt or react with the substrate to form an adhesion layer for the film. At the same time, the metallic particles are sintered, forming the film.

In the usual sequence, the conductive pattern is first screened, printed, and fired. The resistor pattern is then deposited over the conductive terminations and fired at the same or lower temperature than that for the conductive patterns.

After the resistors are trimmed, either abrasively or by laser, a hybrid thick-film circuit is completed by attaching the other chip components. The substrate assembly is then mounted in a suitable package using solder or adhesive, and the necessary interconnections are wire bonded.

#### MONOLITHIC CIRCUIT DEFECTS

#### Die

#### Metallization

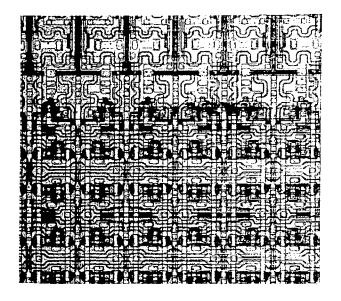

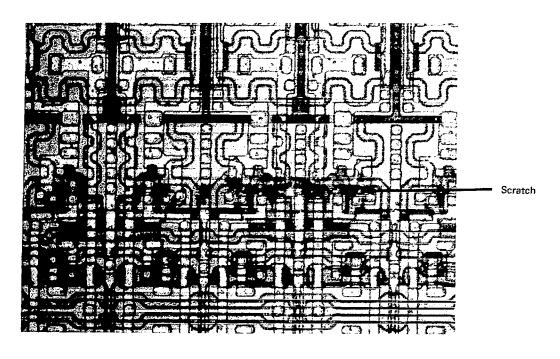

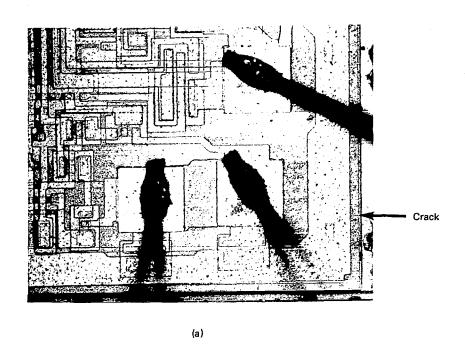

Metallization defects result from either mishandling or flaws in the photolithographic process. To observe defects in the metallization, a magnification of 100X to 200X is normally used (per MIL-STD-883B, Method 2010). However, with the new VLSI devices, higher magnifications will be needed to adequately examine the metallization.

Figure 14a is a photomicrograph of a VLSI memory device with a defect that is difficult to distinguish under the precap examination criteria of 100X to 200X. If the magnification is tripled, the defect shows up as a disturbed area (scratch) of metallization (fig. 14b). The scratch resulted in an open-circuited metallization stripe that caused the device to malfunction. Because examining complex devices at higher magnifications requires an amount of time that is not normally available to a precap inspector, the following paragraphs will address those metallization defects that are easily observable at 100X to 200X.

Two of the most common kinds of metallization defects are scratches and voids. A scratch (fig. 14b) can be defined as any tearing defect, including probe marks, in the surface of the metallization. Scratches most often result from mechanical or mishandling damage; wafer probing is one source of scratches in metallization (fig. 15). Each circuit on a silicon wafer is electrically tested (either on a 100 percent basis or by sampling) after contact is established by means of fine-pointed micropositioned probes. (This test is performed to screen out bad devices before packaging.) The actual motion of the probes is mechanically controlled by an operator or automatic test equipment. This motion often results in a scrubbing motion that causes scratches in the metallization. Because it is softer than other metal systems (i.e., titanium/tungsten and gold/molybdenum), aluminum is particularly susceptible to scratching, smearing, and other deformations.

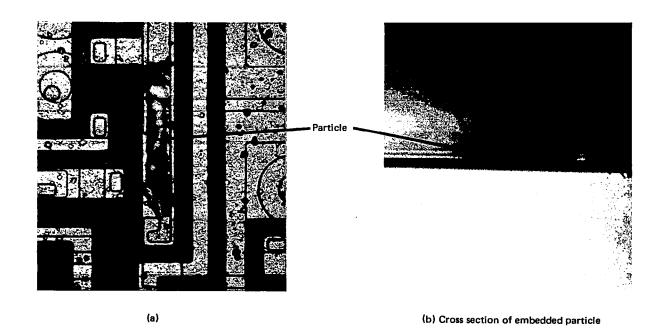

Voids are the result of an inadvertent etching of the metallization in the photolithographic process. A void can be defined as any region in the metallization where underlying metal or passivation is visible that is not caused by a scratch (fig. 16). The inadvertent etching

could cause an interconnection stripe to be severely reduced in width (as will also happen with scratches). Therefore, current in the metallization stripe is crowded through a very narrow region. As a consequence of this, electromigration of the aluminum atoms can occur, possibly resulting in the open-circuiting of the stripe. With the new VLSI devices, two-and three-layer interconnection systems, such as polysilicon/aluminum or aluminum/aluminum, are being used, making it more difficult for inspectors to detect voids in underlying interconnect layers (fig. 17). MIL-STD-883B lists the following rejection criteria for scratches and voids:

- A scratch or a void in the metallization stripe that reduces the width of the metallization stripe to less than one-half of the minimum designed width (fig. 16c).

- A scratch in the metallization over a passivation step that leaves less than 75 percent of the original metal width at the step undisturbed (fig. 16a).

- Void(s) in the metallization over the gate oxide bridge that leaves less than 75 percent of the metallization length and width between the source and drain diffusions undisturbed (fig. 17).

Bridging metallization is the result of incomplete etching during the photolithographic process. Two conditions can occur from this type of defect:

- An unetched metallization path is left between adjacent metallization stripes (figs. 18a, b, and d), between adjacent contact windows, or between an adjacent contact window and metallization stripe(s).

- An unetched metallization path is left between adjacent stripes; however, the path begins at one stripe and terminates very close to the other stripe, but does not touch it (fig. 18c).

The first defect produces a direct short circuit and is detectable during a precap examination or electrical tests. The second phenomenon often escapes visual detection and is usually not detectable electrically. If the die is not glassivated or if the glassivation is of high porosity, high moisture content in the package

(a) 150X

(b) 475X

Figure 14. Photomicrographs of a VLSI device.

Figure 15. Metallization scratches.

Figure 16. Voids in metallization stripes.

Figure 17. Void in a polysilicon gate.

Figure 18. Bridging metallization.

can cause dendrites to grow under bias. These dendrites can plate across the narrow gap between metallization stripes, producing a short circuit and causing the device to fail.

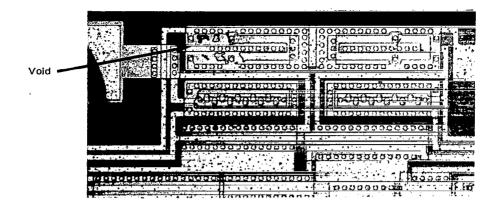

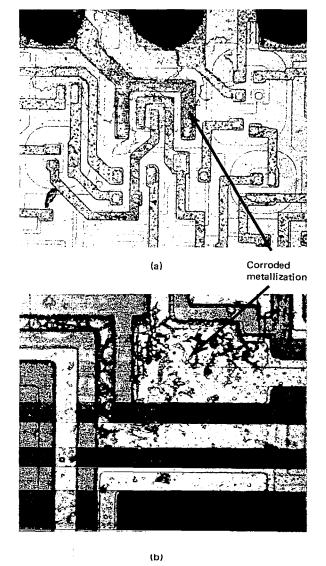

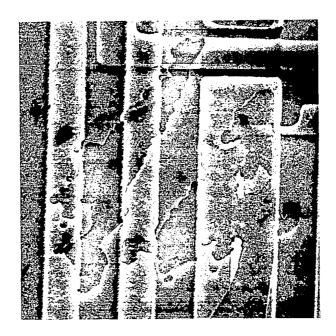

Another latent electrical problem is the open circuiting of metallization due to corrosion of the aluminum (fig. 19). Occasionally during manufacturing, the metal etching solution is not completely rinsed off the surface of the die, leaving salts deposited along the edge of the metallization stripes. In addition, if

Figure 19. Corrosion of aluminum metallization.

any photoresist is left on the die, the salts may become entrapped in the resist. In the presence of very small amounts of residual water vapor in the sealed package or water vapor from definite package leaks, the salts react with the aluminum. Aluminum normally has a stable oxide and is therefore self-passivating. In the presence of ionic contaminants (sodium and chloride), the oxide can be broken down and attacked. An additional source of aluminum corrosion is phosphoric acid. If there is too much phosphorus (>6 percent) in the phosphosilicate glassivation and an appreciable amount of moisture is present within a package, leeching of P2O5 from the glassivation can occur, resulting in the formation of phosphoric acid. The phosphorus in the glass acts as a getter (collector) for mobile sodium ions.

A metallization problem related to improper cleaning of the die surface before deposition of the aluminum metallization is adhesion. Adhesion can be defined as any lifting, peeling, or blistering (fig. 20) of the metallization from the surface of the die. Any devices that exhibit the foregoing defects should be rejected. Adhesion between the thin-film aluminum metallization layer and the dielectric substrate (usually SiO2) is achieved by an adhesion layer. The three basic types of adhesions are: physical interactions (van der Waals' interactions), chemical interactions (solid-state interdiffusion), and mechanical interlocking (surface roughness). Actual adhesion is a combination of these three types, of which chemical interaction is the strongest. Adhesion loss is usually caused by diffusion of the adhesion layer into the adjacent metallic layer or by chemical reaction.

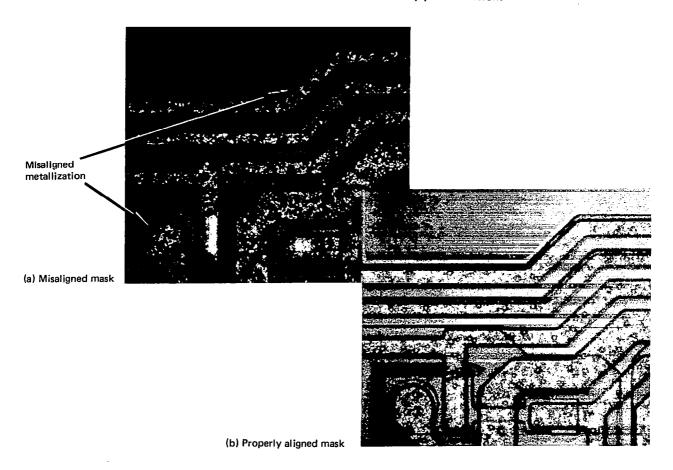

As stated previously, the photolithographic process can be the source of many errors during integrated circuit fabrication. Another defect that can occur to the metallization during the photolithographic process is misalignment. Misalignment occurs when the mask used to produce the metallization pattern becomes misaligned with the contact windows on the silicon die (fig. 21), with the result that the contact windows have reduced metallization coverage. In addition, interconnection stripes on the die may pass over areas that were not intended to be covered by metal. For example, unintended metal coverage over a thin-film capacitor could make a device more susceptible to electrostatic discharge than a device that is properly constructed. This is the case in figure 21,

(a) Topographic view

(b) Scanning electron micrograph of (a)

Figure 20. Peeling metallization caused by poor adhesion.

Figure 21. Photomicrographs of metallization alignment.

where a misaligned mask resulted in a system failure. Contact windows that are not completely covered by metallization can result in latent device failure. The small part of the contact window covered by metallization could develop a hot spot when a high current density is flowing through the contact. Electromigration could open-circuit the metal after a period of time.

Listed below are some of the rejection criteria for inspecting contact windows. It will become more difficult to enforce these criteria as device densities increase.

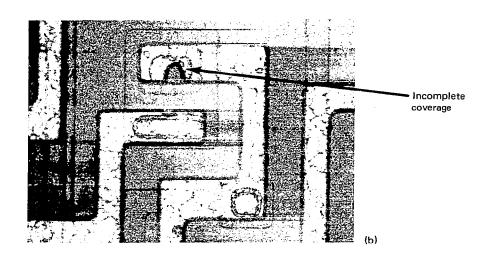

- Less than 75 percent of the area of the contact window is covered by metallization (fig. 22).

- Less than a continuous 50 percent of the perimeter of the contact window is covered by metallization.

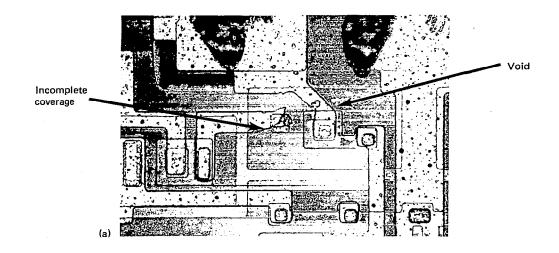

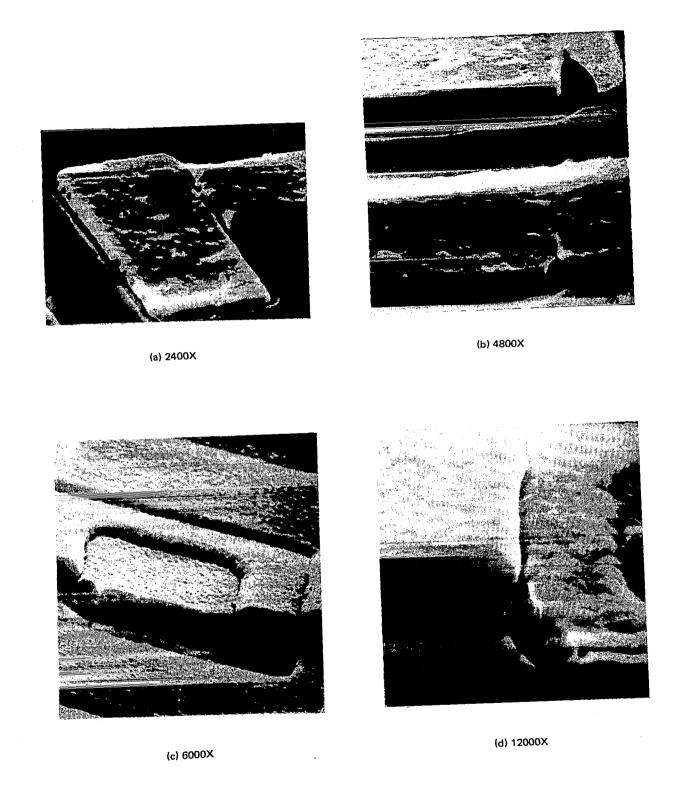

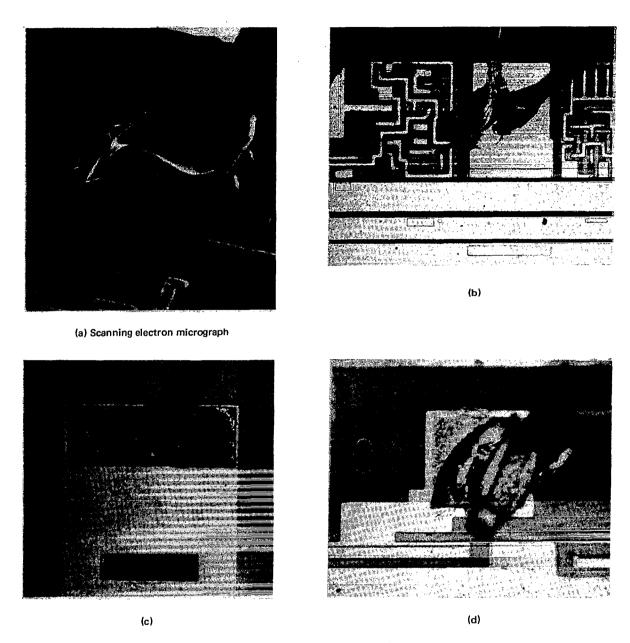

Some metallization defects are not readily observable during a precap examination. Normally, a scanning electron microscope is needed to view these defects. However, because it is important for the precap inspector to understand these defects, they are presented here. The problem arises with the coverage of metallization over the edges of oxide (oxide steps). Generally, during manufacturing, the oxide step is preferentially etched to provide a beveled edge. If the oxide step is not etched properly, it can have a very steep angle. A steep oxide step causes voiding, cracking, and thinning of the metallization (fig. 23). Latent open-circuit failures can occur from electromigration of the metal at these areas. Cracks and voids can also occur at contact window cutouts (fig. 23c).

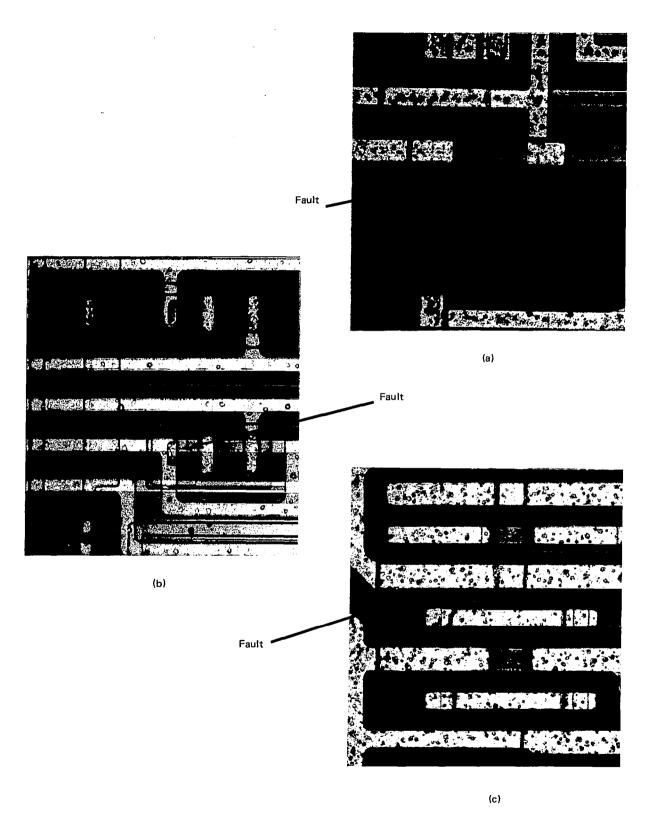

#### Diffusion, Passivation, and Dielectric Isolation

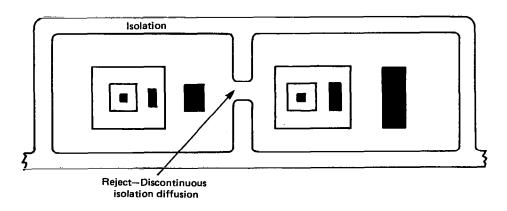

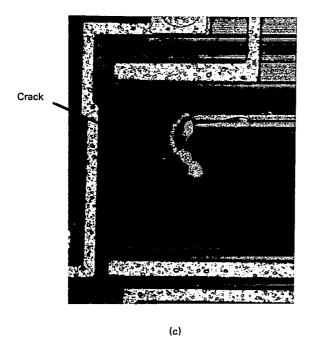

Diffusion, passivation, and dielectric isolation faults are normally the result of defects or inconsistencies in the photolithographic process. Two diffusion-type faults are of most concern in precap visual examinations. Any diffusion fault that allows bridging between diffused areas is unacceptable (fig. 24a). Faults like this can be traced to lifting and peeling of the photoresist, causing exposure irregularities. These faults could manifest themselves as resistive short circuits between two diffused areas. Figures 24a and 24b show some diffusion irregularities.

The second type of diffusion fault deals with junction isolation. In integrated circuit design, junction isolation (fig. 25a) can be used to prevent undesired electrical interconnection between regions in the same silicon substrate. These isolation areas are formed by the diffusion process. Processing faults can cause a discontinuity in the isolation diffusion. If this occurs, adjacent isolated areas are short-circuited (fig. 25b). This is an unacceptable defect. Even if the isolation diffusion is continuous, it can be reduced in width. If sufficiently reduced in width, the depletion layers of the isolated regions could spread far enough to touch each other. Similar defects (reduction in width) can also occur in diffused resistors. This changes the resistance of the resistor and might affect the circuit operation only under unusual circumstances that are not normally covered during electrical testing. Some of the rejection criteria for diffusion faults are:

- Any isolation diffusion that is discontinuous.

- Any diffused area with less than 25 percent of the original diffusion width.

- Any diffused resistor with less than 50 percent of the original diffusion width.

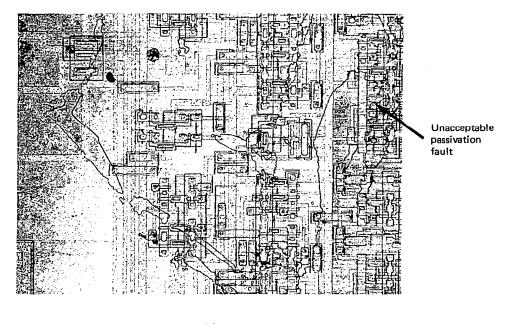

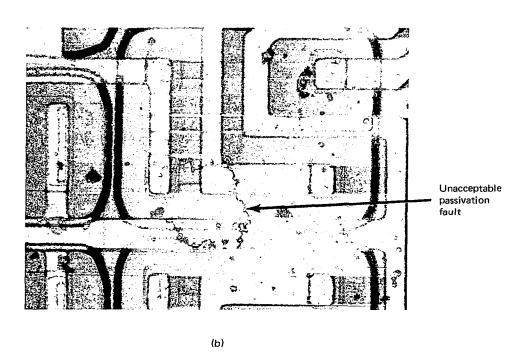

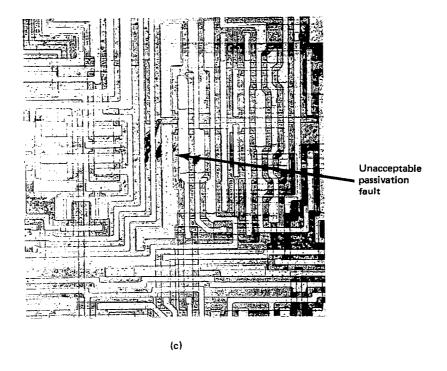

Passivation faults are defects in the silicon dioxide that are detectable by a thinning or absence of passivation (silicon dioxide). Masking problems are the major contributor to passivation faults. Passivation faults become rejectable when they exist underneath metallization stripes (fig. 26). If the passivation fault is deep enough, the metallization could short circuit underlying conductors or even the silicon substrate. The depth of the passivation fault can be estimated by the number of lines observable at the edge of the fault. Even though the depth of the fault does not cause short circuits, the oxide may be thin enough to break down during electrical operation over the life of the device.

Active junction areas not covered by passivation, unless by design, are rejectable. If not covered by passivation, junction areas are susceptible to mobile charges on the surface that can cause junction leakage currents and lower breakdown voltages.

Occasionally, cutouts in the passivation for contact windows extend across a junction area because of a

(c) Scanning electron micrograph

Figure 22. Incomplete metallization coverage of contact windows.

Figure 23. Scanning electron micrographs of voiding, cracking, and thinning of metallization.

Figure 24. Diffusion faults.

(a) Structure of the various components found in the junction isolation process

(b) Visual criteria for discontinuous isolation diffusion

Figure 25. Junction isolation.

(a)

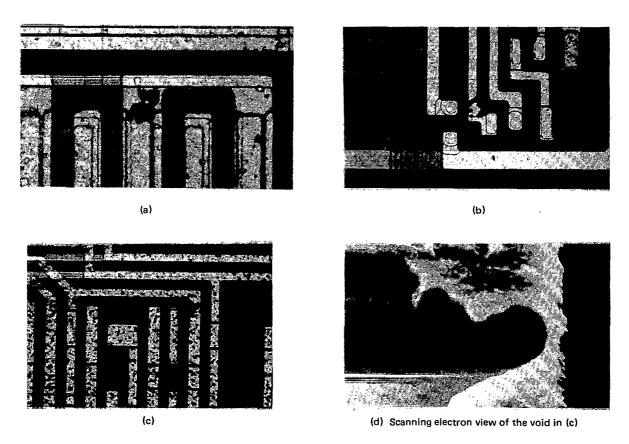

Figure 26. Faults in silicon dioxide passivation (a and b).

(d) Scanning electron micrograph of (c)

Figure 26. Faults in silicon dioxide passivation (c and d).

masking fault, unless called for in the design. When the metallization is deposited, a shorted junction results. A good example would be the cutout for a base contact window that unintentionally extends across to the collector. When the metal is deposited, a shorted collector-base junction results, producing a diode between the shorted collector-base junction and the emitter.

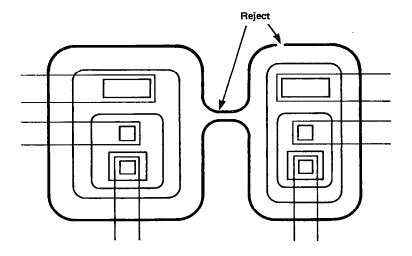

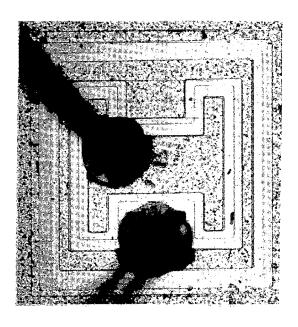

Some manufacturers use a process called dielectric isolation to isolate individual active circuit elements. Each circuit element is surrounded on the sides and bottom by an insulating layer of silicon dioxide (fig. 27). If problems occurred during processing due to masking faults, isolation regions could be bridged, resulting in a short circuit between active regions. This type of fault is detectable by the absence of a continuous isolation line (fig. 28a) between adjacent active areas. (Each active area is in reality a diffusion tub.) The isolation line is typically a black line whose discontinuity is easily recognized. A similar rejectable defect is a discontinuous isolation around each active area. Diffusions that are made into an active tub area are sometimes offset because of small alignment problems. Defects such as this are rejectable if an overlapping diffused area comes closer than 0.1 mil to an adjacent tub or an overlap of more than one diffusion into the dielectric isolation material occurs (fig. 28b).

## Glassivation

Rejectable defects that can occur in the glassivation are numerous. Crazing of the glassivation is one defect that is rejectable because it usually prohibits detection of any defects under the glassivation. When crazing occurs, the glassivation has small, numerous, interconnected cracks that obscure the underlying silicon. Crazing occurs in the dicing operation when the wafer is turned upside down and broken into individual dice. If the surface is not cleaned between operations, small particles of silicon impact on the glassivation surface when pressure is applied to the wafer to break it up.

At times during the manufacturing process, a defect occurs in the mask used to generate the glassivation pattern, or the photoresist does not adhere properly. When this occurs, areas of metallization on the die are left uncovered by glassivation. If two or more active adjacent metallization stripes are left uncovered, the device is rejectable (fig. 29). Uncovered active areas of metallization can be resistively short-circuited if conductive particles come to rest in the area.

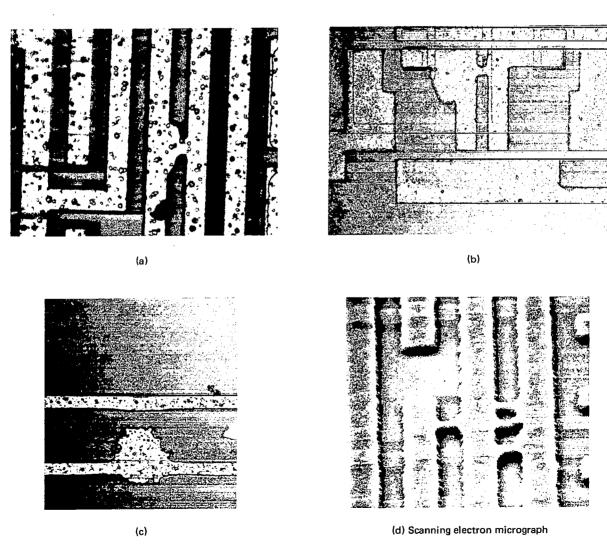

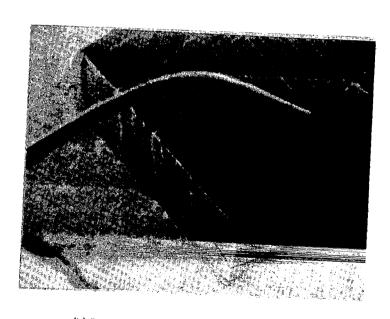

Cracks (not crazing) often occur in vapor-deposited glassivations. Vapor glassivations are in tensile stress. If the adhesion of the glassivation to the die surface is poor, localized lifting or cracking of the glassivation

Figure 27. Dielectric isolation.

(a) Visual criteria for isolation lines

(b) Two diffusions overlapping into the dielectric material

Figure 28. Dielectric isolation visual criteria.

Figure 29. Two active adjacent metallization stripes not covered by glassivation.

can occur (fig. 30). Poor adhesion of the glassivation can result from improper cleaning of the die surface during processing. In these areas of poor adhesion, the glassivation can crack enough to form closed loops over adjacent metallization stripes. This is considered to be rejectable because the glassivation could peel off in this area, allowing the two adjacent exposed stripes to become short-circuited by loose particles inside the package.

The PSG can be affected by its phosphorus content. If the phosphorus content of the glassivation drops below 2 percent, cracks are more likely to occur because reduced phosphorus content increases the tensile stress of the film. When this occurs, large areas or all the glassivation are more likely to develop cracks rather than isolated die areas that were poorly cleaned. When cracks occur throughout the glassivated die area, the die metallization becomes more susceptible to the moisture content within the package. A high moisture content increases the probability of corrosion of the die metallization by impurities.

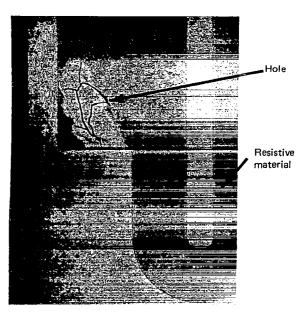

Cracks in glassivation can occur by other means. The increased use of thin-film resistors on monolithic cir-

cuits requires that resistor trimming take place after PSG deposition. Trimming is performed by a laser, and if the power output of the laser is too high, the heat produced during trimming can crack the glass (fig. 31). High moisture content within a package can enter through the cracks and can be absorbed by the resistor material. This moisture subsequently changes the electrical characteristics of a highly trimmed circuit. For this reason, circuits that exhibit crazing, voids, and cracks in the glassivation over thin-film resistors are rejectable.

Two last factors in the examination of glassivation are scratches and the presence of glassivation on bonding pads. Occasionally, during the dicing, probing, or mounting and bonding operations, scratches can occur in the glassivation. These scratches are often not serious enough to penetrate to the underlying oxide. (Penetration to the underlying oxide is detectable by a change in oxide color.) However, the scratches become rejectable when they penetrate to the underlying circuit and cause bridging between the metal stripes. Metallization bridging is also discussed under the metallization criteria because scratches can occur before deposition of the glassivation.

(a)

Figure 30. Cracks in the glassivation. Note the interference rings in (a), indicating lifted glassivation.

(b) Scanning electron micrograph of the cracked glassivation in (a)

(d) Hole in the glassivation

Figure 31. Cracks in the glassivation over thin-film resistors.

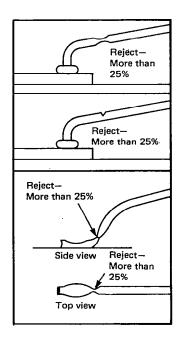

The presence of glassivation on a bonding pad is caused by a defect in the photolithographic process. In general, glassivation that covers more than 25 percent of a bonding pad area is considered to be rejectable. The presence of glassivation on bonding pads is easier to detect at the wafer level before the bonding process. After bonding, the bonds obscure the presence of the glassivation on the pad. Bonds that are made on glassivated pads are usually weak, although they are physically acceptable in appearance. The presence of the glassivation inhibits the interfacial welding during the bonding process because it is difficult to break the glassivation to obtain metal-to-metal contact. Weak bonds as described above can be screened out by nondestructive bond pull tests.

#### Scribing

During the scribing process, small cracks can be introduced along the edges of a chip. The cracks develop when the diamond point tears the silicon during scribing. This is not as big a problem with dice that have been laser scribed. Cracks can also develop when the wafer is broken into individual chips. When cracks occur, some of them inevitably point toward the active portions of the chip. If a crack later propagates into the active circuit areas, it could degrade junctions by creating leakage paths and/or partially or completely open circuit the metallization stripes. Some cracks have been observed to propagate under aluminum metallization without open circuiting the stripe. In one case, the aluminum actually stretched over the crack, allowing the circuit to operate under worstcase conditions. Because it is difficult to provide effective screens for cracks, it is imperative that they be detected during the precap visual examination.

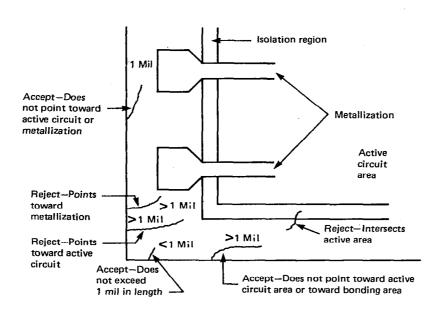

MIL-STD-883B, Method 2010, lists the following rejection criteria for cracks:

- A crack in the active circuit area

- A crack that exceeds 3.0 mils in length or comes closer than 0.25 mil to any operating metallization or circuit element

- A crack that exceeds 1.0 mil in length inside the scribe line that points toward functional circuit elements or metallization.

Unless proper lighting is used during precap screening, devices with cracks can sometimes look acceptable.

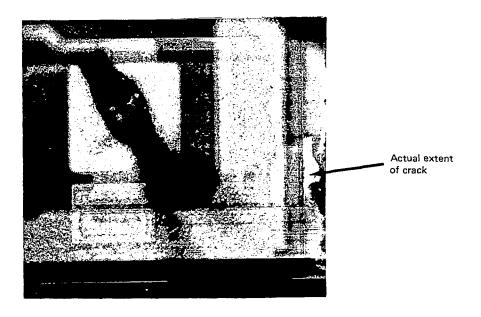

Figure 32a shows cracks in the scribe area under normal bright-field lighting. Note that some of the cracks come too close to active operating metallization to be acceptable. If phase-contrast lighting is used, the actual extent of the crack can be seen (fig. 32b). A defect of this type is rejectable. In the course of normal precap examinations, however, the time required for individual microcircuit attention such as that described above usually cannot be spared. Figure 33 illustrates the rejection criteria for cracks, and figure 34 shows cracks in dice.

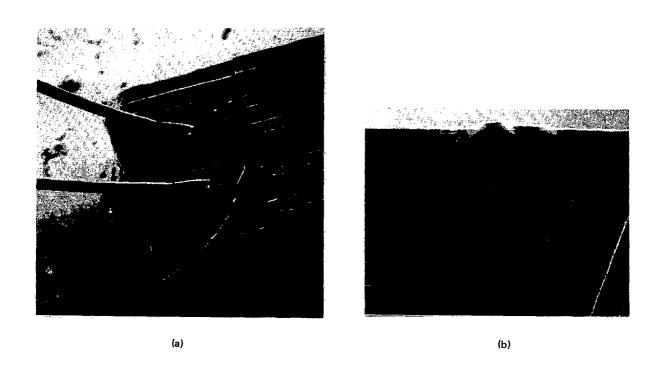

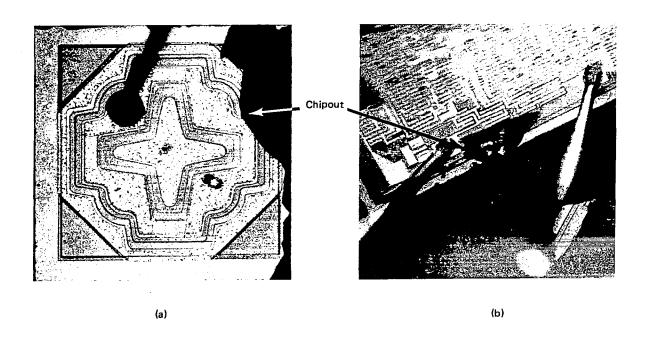

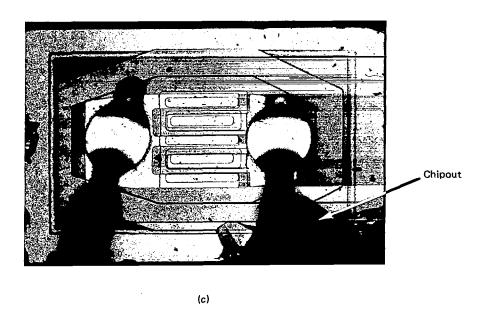

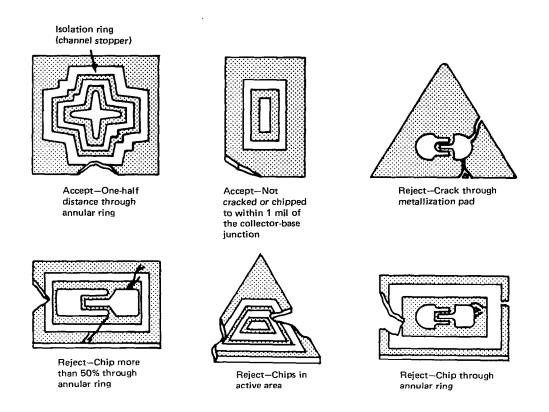

Other defects that can occur in the scribing operation are chipouts in the die. Chipouts occur when the wafer has not been completely scribed. In the subsequent breakup of the wafer, the silicon fractures rather than breaking cleanly along the scribe line. Chipouts can also occur during subsequent handling operations (fig. 35b), such as when the die is being mounted inside the package. The photographs in figure 35 show some rejectable chipouts in dice. Figure 36 illustrates the rejection criteria for chipouts.

If the wafer is not aligned properly during the scribing operation, scribing takes place along some plane other than the scribe grid. When this occurs, some dice will have attached portions of active circuit area of other dice—a rejectable defect (fig. 37).

# Thin-Film Resistors

A thin-film resistor consists of a thin resistive film that is deposited on an insulating substrate. The film materials used are metals, metal alloys, and metal compounds such as gold, palladium, palladium/gold, and titanium. More and more, manufacturers are using thin-film resistors in analog circuitry, particularly in digital-to-analog and analog-to-digital converters.

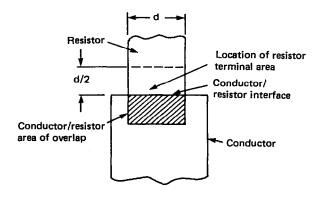

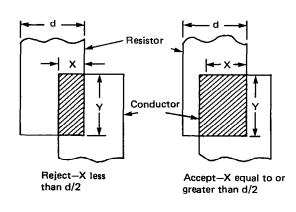

Because thin-film resistors are deposited by a separate process similar to aluminum metallization, misalignments can occur. Any misalignment between the conductor/resistor in which the actual width of the overlap is less than 50 percent of the original resistor width is unacceptable (fig. 38). This criterion is analogous to the 50 percent reduction rejection criterion of metallization conductors discussed previously. Misalignment of more than 50 percent could cause problems due to electromigration. Similar problems can occur if there is not enough overlap between the

(b) Phase-contrast lighting showing the extent of crack in (a)

Figure 32. Cracks in the scribe grid of a die.

Figure 33. Visual inspection criteria for cracks in semiconductor dice.

Figure 34. Scanning electron micrographs of unacceptable cracks in two dice.

Figure 35. Unacceptable chipouts in semiconductor dice.

Figure 36. Visual inspection criteria for chips in semiconductor dice.

metallization and the film resistor. The overlap is rejectable if it is less than 0.25 mil. Occasionally, due to matching errors, inactive resistor material inadvertently connects two separate points on an active circuit, causing a short circuit. This type of defect is more difficult to detect unless the inspector is thoroughly familiar with the circuit. MIL-STD-883B, Method 2010, lists additional rejectable defects for thin-film resistors:

Necking down that reduces the width of the resistor material at a terminal

- Void that leaves less than 75 percent of the film resistor material undisturbed at a terminal

- Any thin-film resistor that crosses a substrate irregularity (e.g., dielectric isolation, oxide/ diffusion step, etc.).

Note the similarity of these rejection criteria to some of the inspection criteria for metallization.

Photolithographic errors can cause excess thin-film material to be left on the die (fig. 39a). In the extreme case, the extra material could contact other active

Figure 37. Semiconductor dice that have attached portions of the active circuit areas of other dice.

Resistor

Accept—Y equal to or greater than 0.25 mil

(a) Photolithographic defect

Figure 38. Visual inspection criteria for thin-film resistor contact area.

(b) Variations in kerf width due to beam irregularity

Figure 39. Thin-film resistor anomalies.

circuit areas. A thin-film resistor is unacceptable if it has an increase greater than 25 percent of the original width or if the separation between resistors or a resistor and a metallization path is less than 0.25 mil.

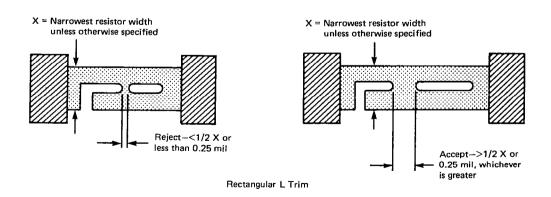

Thin-film resistors are trimmed to their proper resistance value by laser trimming—moving the laser beam through the resistor material in a set pattern necessary for achieving the desired resistance. The area from which material is removed by laser trimming, called the "kerf," should be absent of any resistor

material. As the laser is trimming, the beam spot diameter must be very tightly controlled to prevent variations in the width of the kerf (fig. 39b). A thin-film resistor is rejectable if it has a kerf of less than 0.1 mil in width. Occasionally, trimmed resistor material remains in the kerf after the processing operation. This material can short the opposing sides of the kerf, changing the overall circuit operation. Figure 40 illustrates some rejection criteria for thin-film resistors based on trimming errors.

Figure 40. Visual criteria for laser-trimmed thin-film resistors.

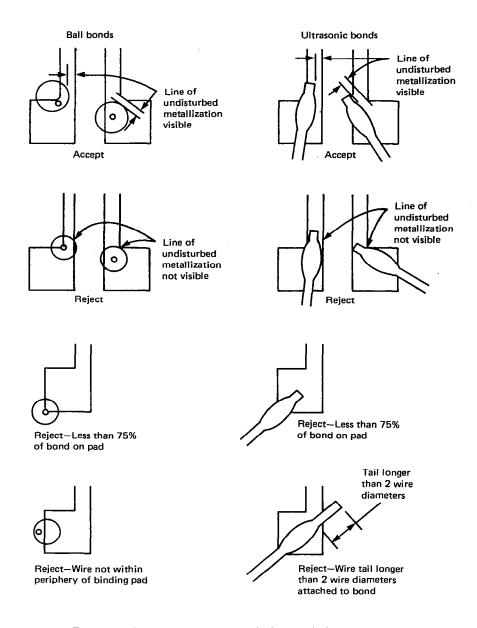

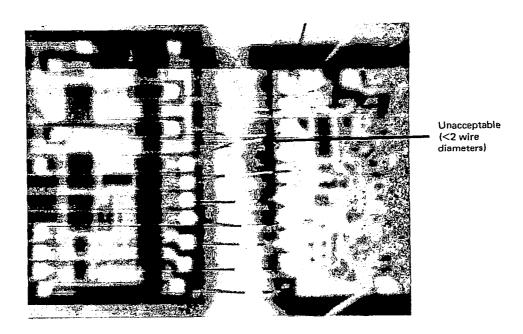

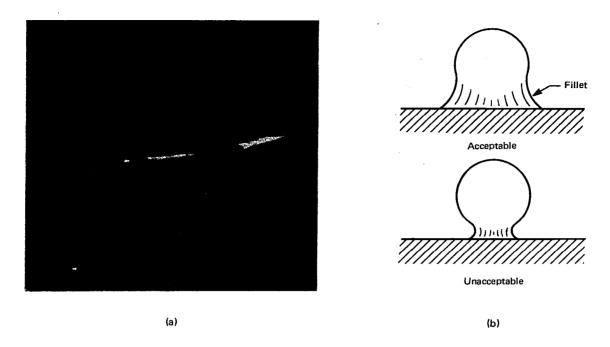

#### Wire Bonding

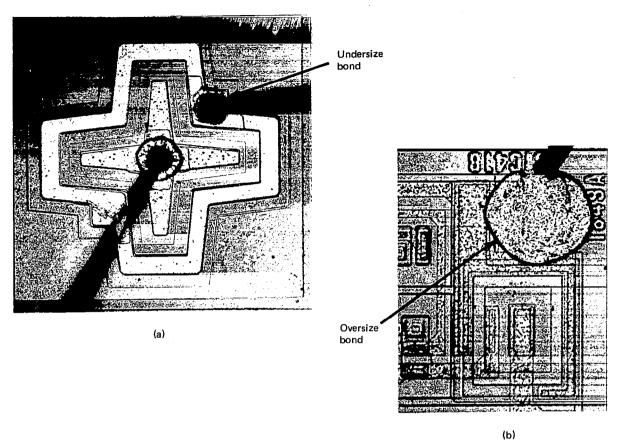

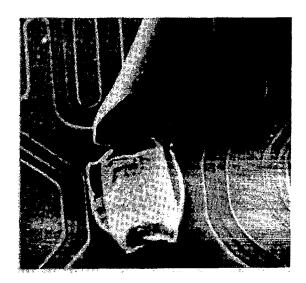

In integrated circuits, wire bonds are common sources of failure, particularly the bonds on the die. It is therefore important to pay close attention to the bonds during precap visual examinations. Several criteria are important to the reliability of gold ball bonds. The first is the size of the bond. The bond should not be less than 2 times, nor greater than 5 times, the wire diameter (fig. 41). When the bond is less than 2 times the wire diameter, not enough area of the ball is bonded to the metallization pad. In addition, when the bond is too small, a phenomenon called "cratering" can occur. Cratering is a fracture in the silicon substrate under the bond that results from the impact of the hard bonding tool (fig. 42). If the bond is greater than 5 times the wire diameter, the ball bond can overlap the metallization bonding pad. As integrated circuits become more dense, the size of the bonding pads decrease; currently they are on the order of 4 mils square. When ball bonds overlap the pad, the glassivation can crack. Cracking of the glassivation could be a reliability hazard if excessive moisture is present in the package. If the ball bond size falls between 2 and 5 times the wire diameter, the bond will probably be good. However, the ball size is sometimes visually acceptable even though an underbond has occurred.

An underbond occurs where insufficient heat and/or bonding pressure has been applied during bonding, and the ball is only tacked on although its appearance is visually acceptable. To detect this type of bond, more than a visual inspection is required. One way of detecting bonds of this type (although it is outside the scope of a precap examination) is to use a nondestructive wire bond pull test (NDP). The intent of this test is to use a force great enough to cause weak bonds to fail, but not great enough to damage good bonds. However, when using the NDP test, variables such as wire and bond-loop elongation, bond geometry, and the mean and the standard deviation of the destructive bond pull test must be considered in devising safe nondestructive wire bond pull force limits. Harman and Cannon (1978) summarized the recommended NDP force limits. An alternative to the NDP test is to subject the device to mechanical shock or vibration screening. These tests are performed to work the bond loose, usually after package sealing.

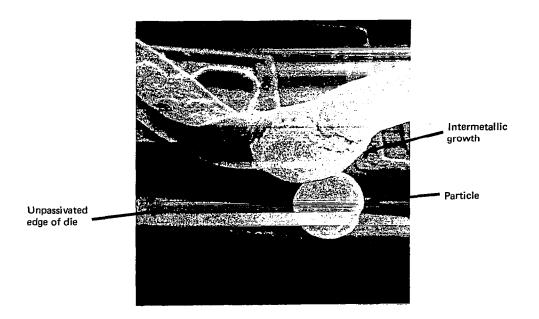

When inspecting gold ball bonds that are bonded in bimetallic systems (usually gold/aluminum), it is important to examine the bond for intermetallic growth (fig. 43). According to MIL-STD-883B, Method 2010, condition A, a bond is unacceptable if it exhibits intermetallic formation that extends radially more than 0.1 mil completely around the periphery of any gold ball bond for that portion of the bond located on metal. Gold/aluminum intermetallic compound formations have been studied extensively. These compounds may form during thermocompression bonding, during subsequent qualifying thermal screens, and during storage of the device if the temperature is 200°C (475 K) or higher. The fact that intermetallic formations can occur at any time in the life of a device when high temperatures are encountered does not mean that the bond will necessarily degrade either electrically or mechanically. It was originally assumed that any bond with intermetallic compounds was bad. Only after extensive study was it found that metallurgical (Kirkendall) voids actually caused the failures rather than the intermetallic compounds.

Two types of void-induced bond failures have been observed. In the first failure type, the bond can be mechanically strong, but it can have a high electrical resistance or even be open circuited. This type of failure occurs when voids form around the bond periphery, limiting the current carrying area of the bonding pad metallization. In the second type of failure, the voids in the metallization occur underneath the bond. This type of bond fails because of mechanical weakness.

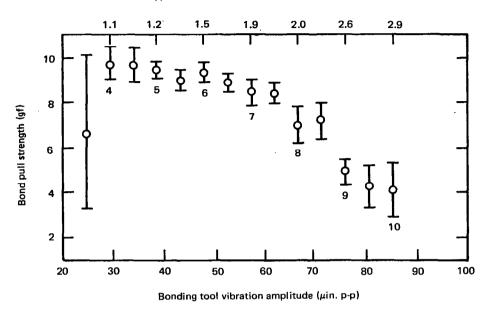

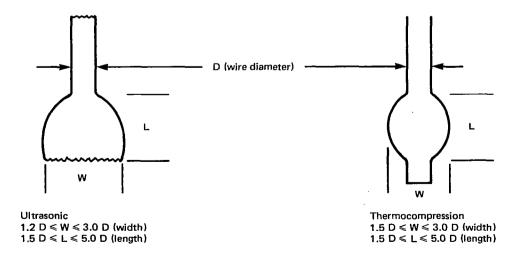

Wedge bonds are judged on a different basis as far as the criteria relating to wire size is concerned. Ultrasonic wedge bonds are considered unacceptable if the bond is less than 1.2 times, or greater than 3 times, the wire diameter in width. If the bond is less than 1.2 times the wire diameter, a large variability in the pull strength results as shown in figure 44. Bonds less than 1.2 times the wire diameter are susceptible to contamination on the surface of the bonding pads. Ultrasonic wedge bonds of less than 1.2 wire diameters result from a combination of insufficient bonding-tool vibration amplitude and force so that the surface contaminants are not broken up and properly swept

(c) Scanning electron micrograph of the undersize bond in (a)

Figure 41. Unacceptable ball bonds.

Figure 42. Scanning electron micrograph of cratering that occurred underneath a wedge bond.

aside. Instead, contaminants remain intact and prevent metallurgical bonding. Ultrasonic wedge bonding is normally performed using aluminum wire.

If the bond is greater than 3 times the wire diameter, problems also occur. This is usually the result of excessive bonding-tool vibration amplitude; this in turn results in wedge bonds whose cross-sectional areas are too thin. As a consequence, low wire bond pull forces result. As can be seen in figure 44, as the bond deformation approaches 3 wire diameters, bond pull strength decreases, and the variability in bond pull strength becomes greater.

Thermocompression and thermosonic wedge bonds of gold to aluminum are not recommended because the intermetallic phases weaken the bond and the thinning (overworking) of the wire from the wedge tool induces weakening. Bonding pressure and temperature are therefore critical in this operation. Because the wire becomes overworked and weakened as it gets thinner, a thermocompression wedge bond is

considered unacceptable if the bond is greater than 3 (width) or 5 (length) times the wire diameter. These criteria would be more critical in thermosonic wedge bonds because they tend to have a thinner heel than thermocompression bonds, making them more susceptible to tearing. A bond is also considered unacceptable if the bond is less than 1.5 (width or length) times the wire diameter. Wire bonds that fail this criterion do not have enough area of the wire bonded. These types of bonds are considered to be underbonded. Normally, thermocompression and thermosonic wedge bonds are monometallic systems such as gold wire to gold contacts and aluminum wire to aluminum contacts. As such, they do not experience intermetallic formations and should be more reliable, Figure 45 summarizes the dimension criteria for ultrasonic and thermocompression wedge bonds.

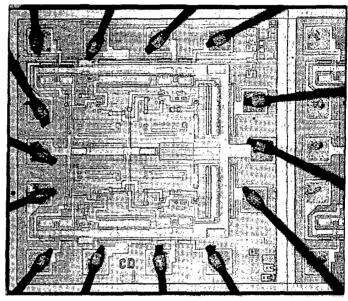

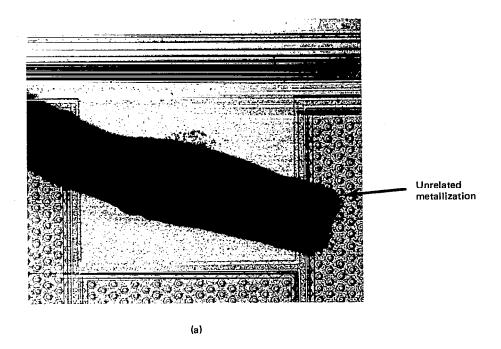

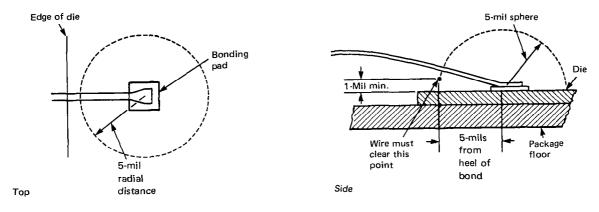

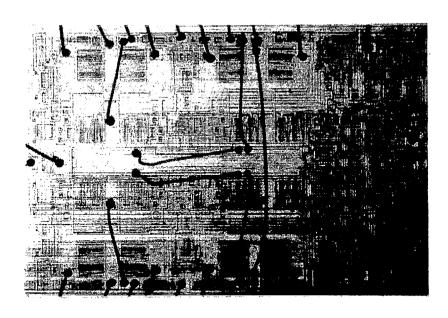

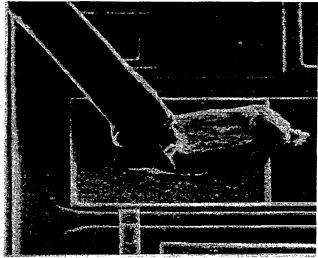

During a precap visual examination, an inspector should be aware of other bond defects. One of these is bond placement on the metallization bonding pads on the silicon die. These defects can lead to latent