#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 TestConX China workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 TestConX China workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 TestConX China workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The TestConX China logo and TestConX logo are trademarks of TestConX. All rights reserved.

www.TestConX.org

# Large Panel Fan Out Technology Overview and Development

Dr. Lin Tingyu

National Center for Advanced Packaging (NCAP)

Suzhou • October 23, 2018 Shenzhen • October 25, 2018

#### **Contents**

- Background Overview

- Personal and Company Introduction

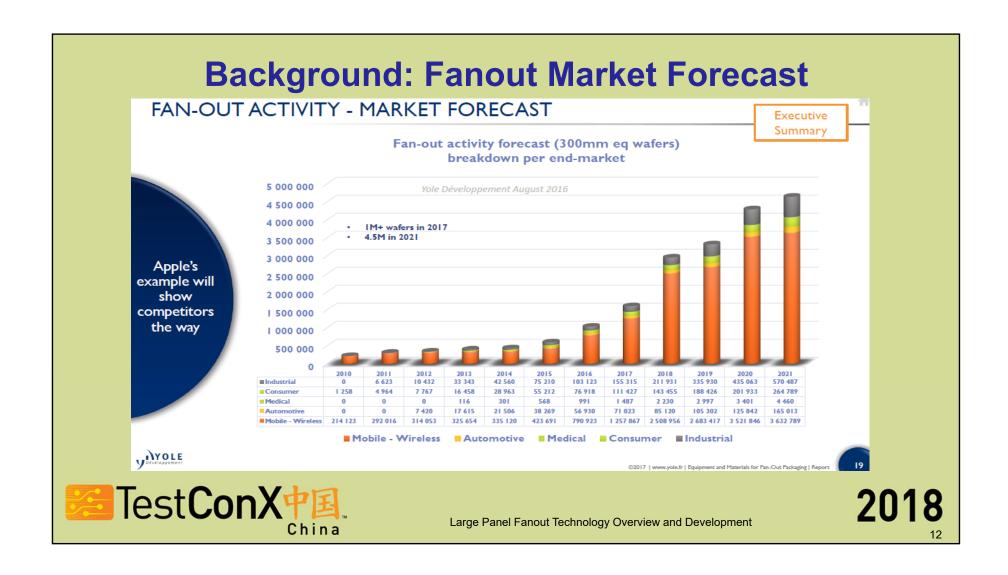

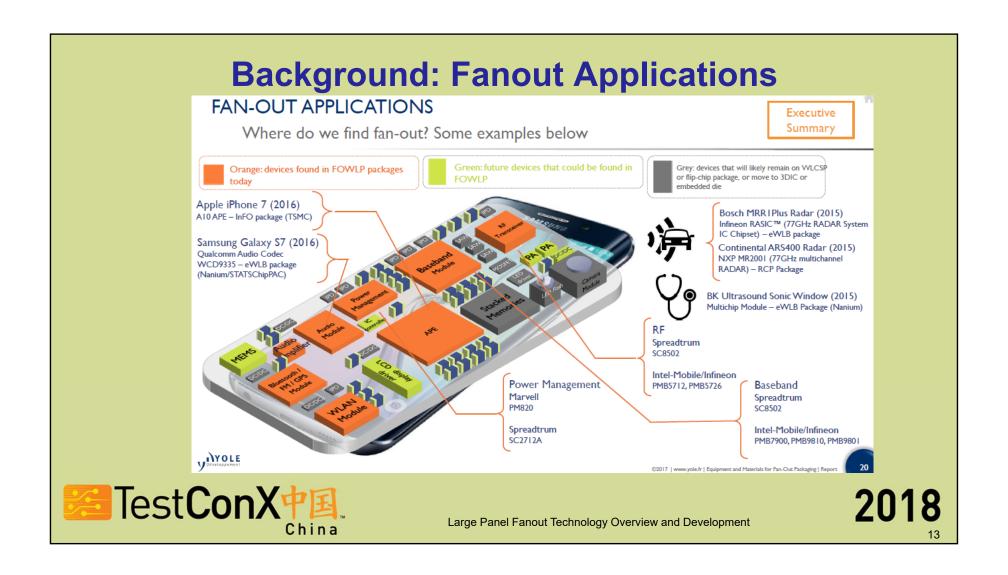

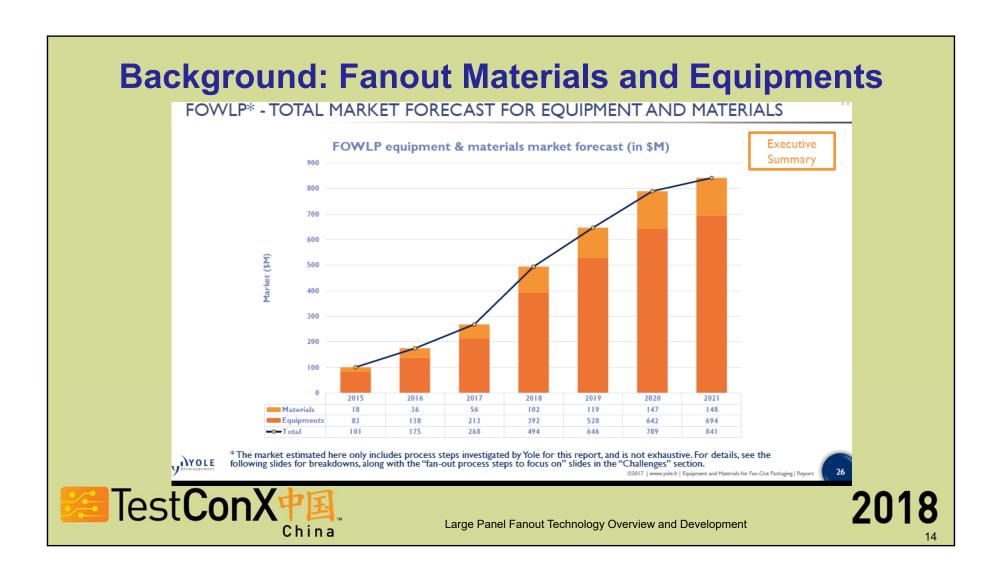

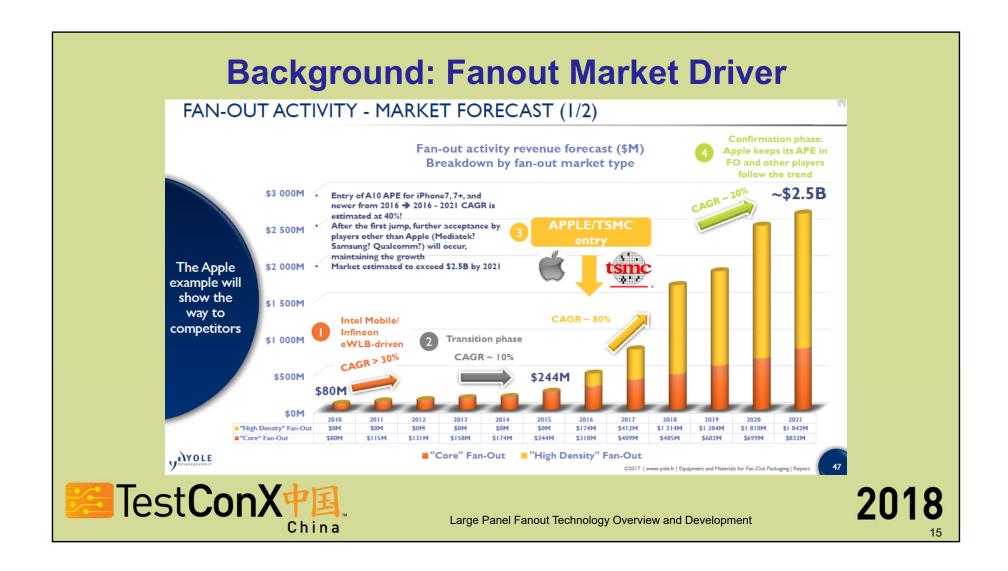

- Market analysis

- Major technologies and global players

- Patent aspects & distribution

- Main process technologies

- Challenges & solutions

- China OSATs on fan out executions

- Some Works Updates of Wafer Level and Panel Level Fan out in NCAP

- Basic Works Introduction in NCAP Consortium

- Critical Works Implementation in GD Province

- Conclusions

Large Panel Fanout Technology Overview and Development

#### **Personal Introduction**

More than 25-year experiences in design, process, assembly, reliability and business management in electronics IC packaging, semiconductor, consumer electronics, mobile phone assembly, PCBA, thermal and aerospace industry. Motorola certified Six Sigma Black Belt. Holding position of board member of CSR (chip scale review), have filed more than 40 international patents and 150 international Journal and conference papers; working in NCAP 5 years, and prepare to move Guangdong province for LPFO integrated equipment and process development and commercialization

Large Panel Fanout Technology Overview and Development

#### **NCAP** Introduction

- Wuxi Headquarters

- 3000m<sup>2</sup> Cleanroom

- Class 10/100/1,000/10,000

- 8"/12" wafer

- Beijing Center

- 1000m<sup>2</sup> Cleanroom

- Class 1,000/10,000

- R&D & Engineering with 9000m<sup>2</sup>

- engineering assembly &metrology equipment with ¥160 million, fixed total equipment value ¥345 million。

- Established in Wuxi in 2012

- Including the Institute of Microelectronics and the largest OSATs and substrate companies in China (JCAP, NT Fujitsu, WLCSP, ANJILI, WULIWANG, SCC, NDB, IME, Hua Tian, XIN Sheng Kuai Jie)

- Independent business entity

2018

Technology Overview and Development

Large Panel Fanout Technology Overview and Development

#### **CNC Equipment Innovation Institute Introduction**

Foshan Nanhai Guangdong Technology University CNC Equipment Cooperation Innovation Institute is jointly set up by Guangdong Provincial Department of Science and Technology, The People's Government of Foshan Municipality, Nanhai People's Government of Foshan and Guangdong University of Technology.

- Honor and Qualifications

- National High-tech Business Incubator

- National Group Innovation Space

- New R&D institution in Guangdong

- Joint-postgraduates Demonstration Base

- College Students Practical Teaching Base in Guangdong

- Leadership Concern

中华人民共和国科学政务保证

联合培养基地

Chinese Premier Li Kegiang

Large Panel Fanout Technology Overview and Development

2018

7

@ 唐井二生子学

东省大学生实践教学基

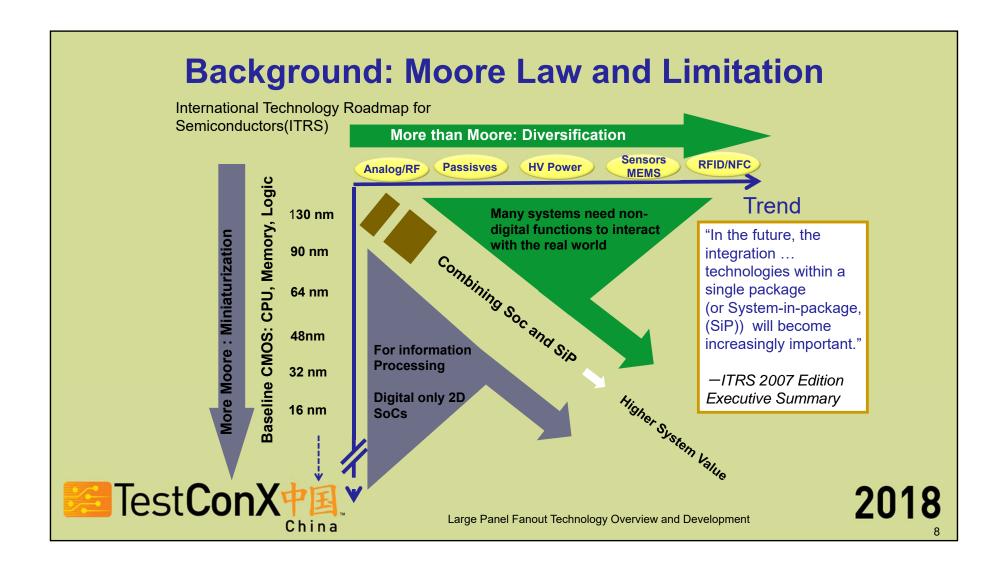

#### **Background: Development Trend**

- The extension of Moore's law is subjected to multiple pressures such as physical limits, huge investment and so on.

- The urgent need to develop a new style technology progress "More Than Moore"

Large Panel Fanout Technology Overview and Development

2018

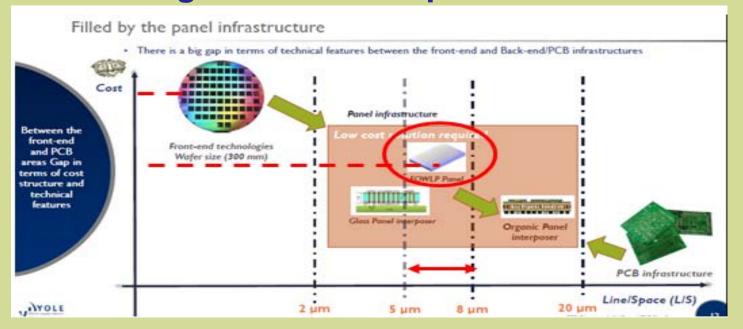

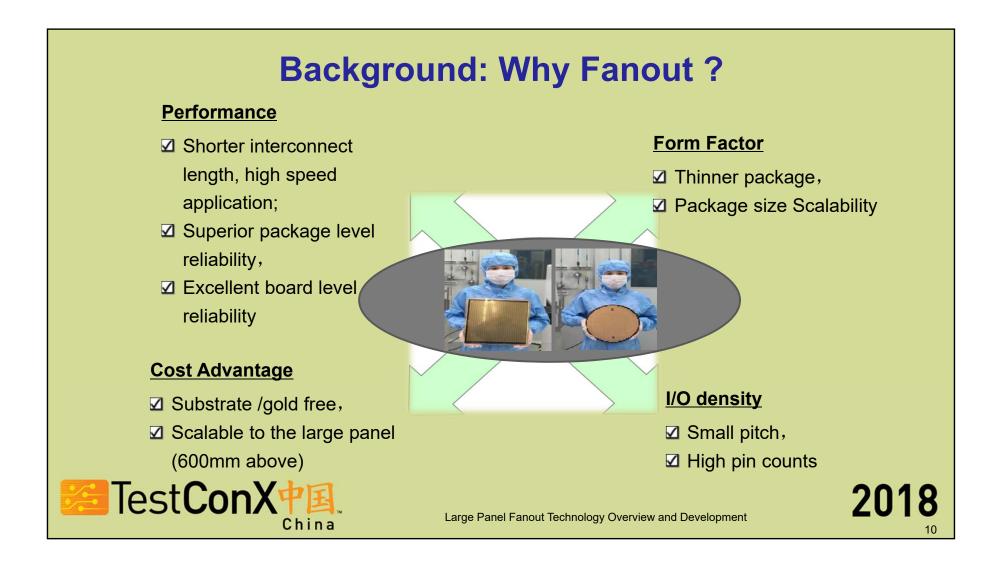

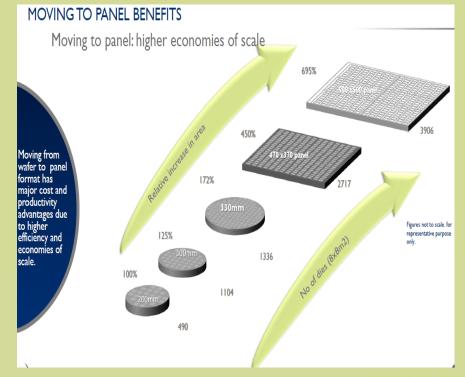

### **Background: Advantages of LPFO**

Through LPFO integration advanced packaging technology, to achieve high-density integration, volume miniaturization and lower cost.

#### The advantages of LPFO

- Higher integration and wider application;

- More flexible design and higher density wiring;

- Better electro-thermal performance, smaller and thinner volume;

- High efficiency and low cost

Large Panel Fanout Technology Overview and Development

2018

#### **Typical InFO-WLP Process Characterization**

## TSMC InFO-WLP (Integrated Fan-Out WLP)

At the TSMC Technology Symposium in San Jose, CA in April 2014, TSMC announced the latest InFO-WLP platforms:

- 8mm x 8mm is targeted at RF and WiFi chips

- 15mm x 15mm is targeted at application processor and baseband chips

- > 25mm x 25mm could be applied to GPU and networking chips

Large Panel Fanout Technology Overview and Development

2018

#### **OSAT Distribution for Fan out**

| OSAT in China                                                              | Packaging Fan out Technologies available | status                                                                               |

|----------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|

| Hua Tian Scientific Co., Ltd                                               | eSIFO ™                                  | Qualified and engineering samples are ready; and ready for ramping in the production |

| JCET                                                                       | MIS technology based                     | Ready for mass production                                                            |

| NT Fujitsu                                                                 | Panel level fan out                      | In development                                                                       |

| National Centre for Advanced<br>Packaging (China), mass<br>production OSAT | eWLP, PLP, etc.                          | Factory built up in Jiangsu province                                                 |

Large Panel Fanout Technology Overview and Development

2018

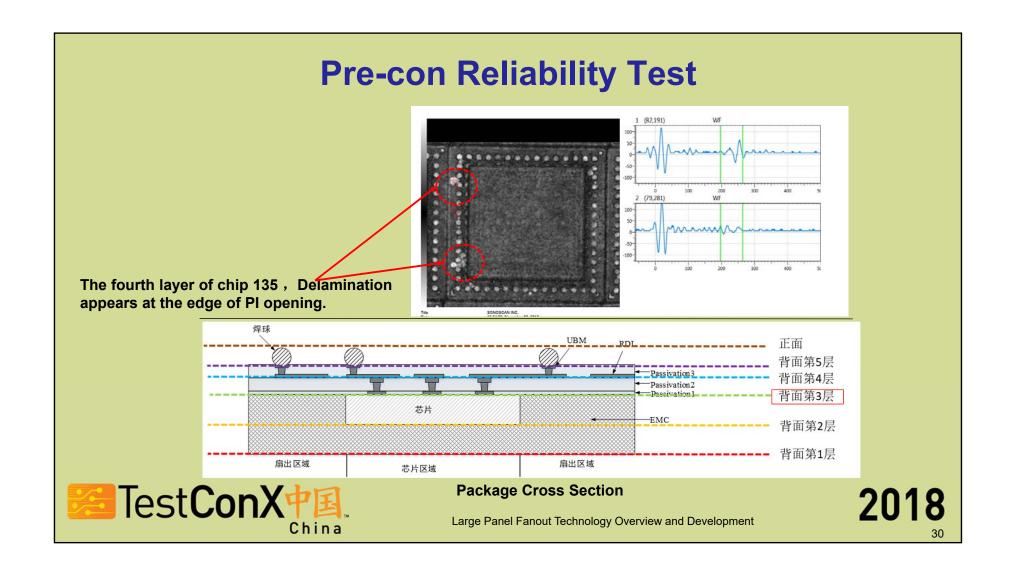

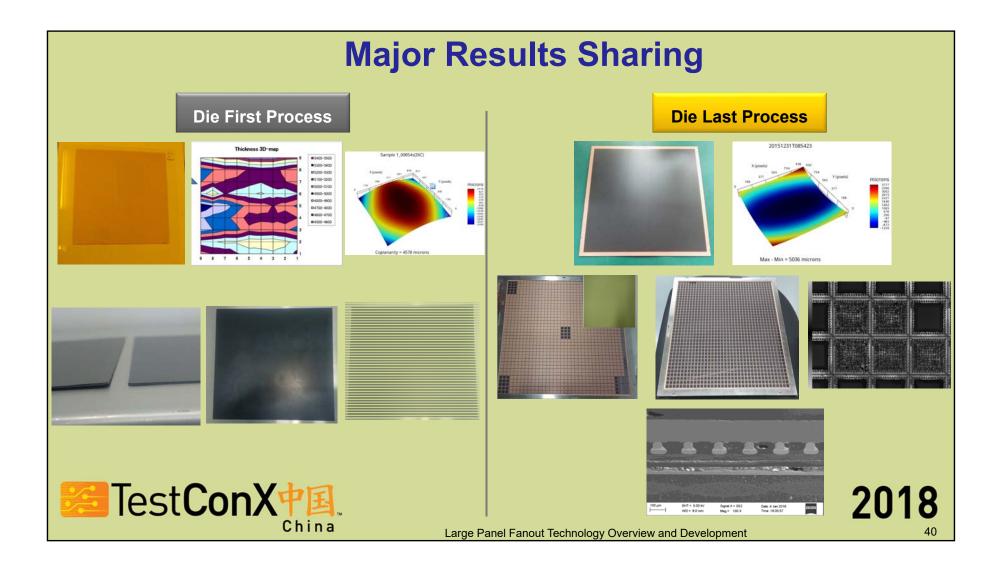

#### **Key Observations from Reliability & FA**

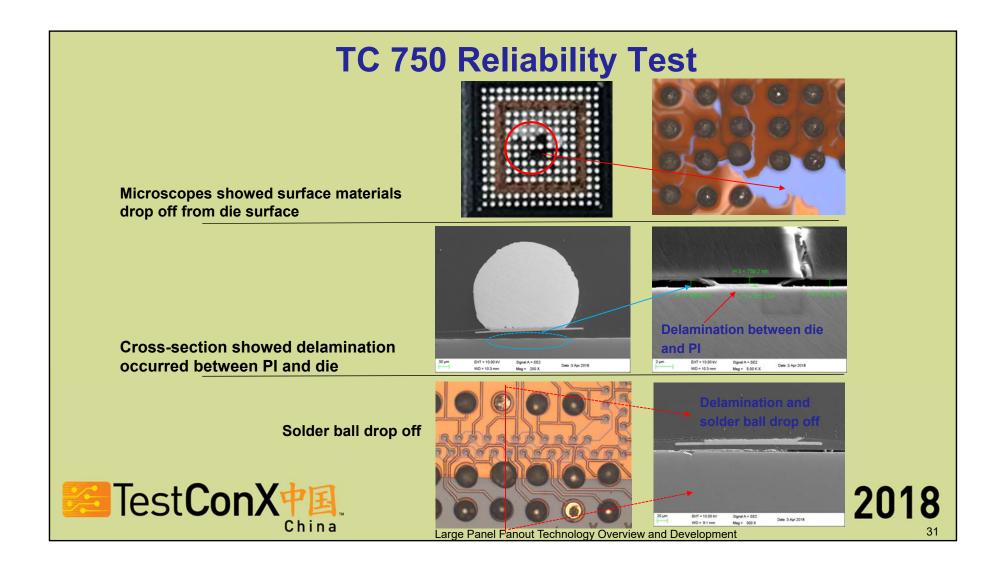

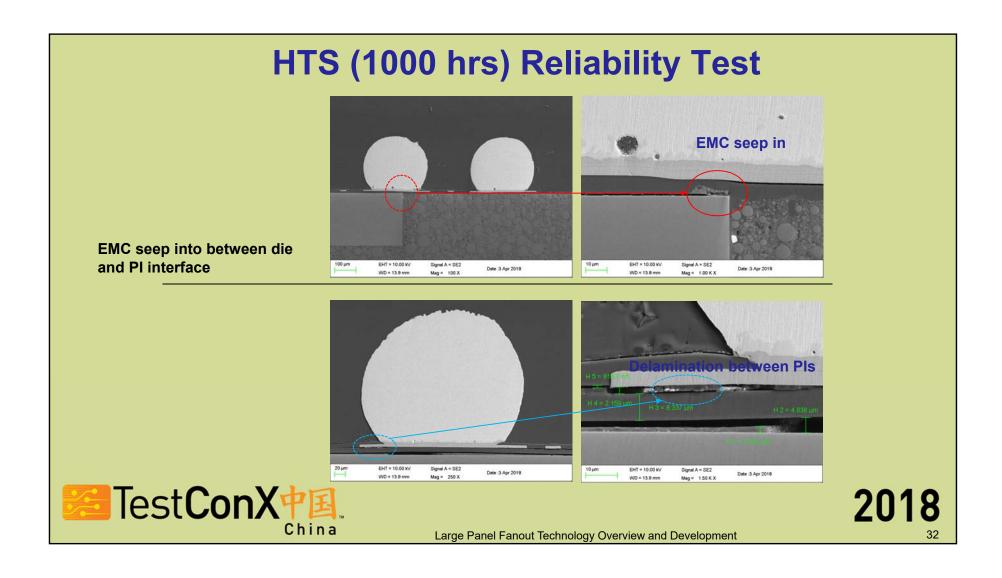

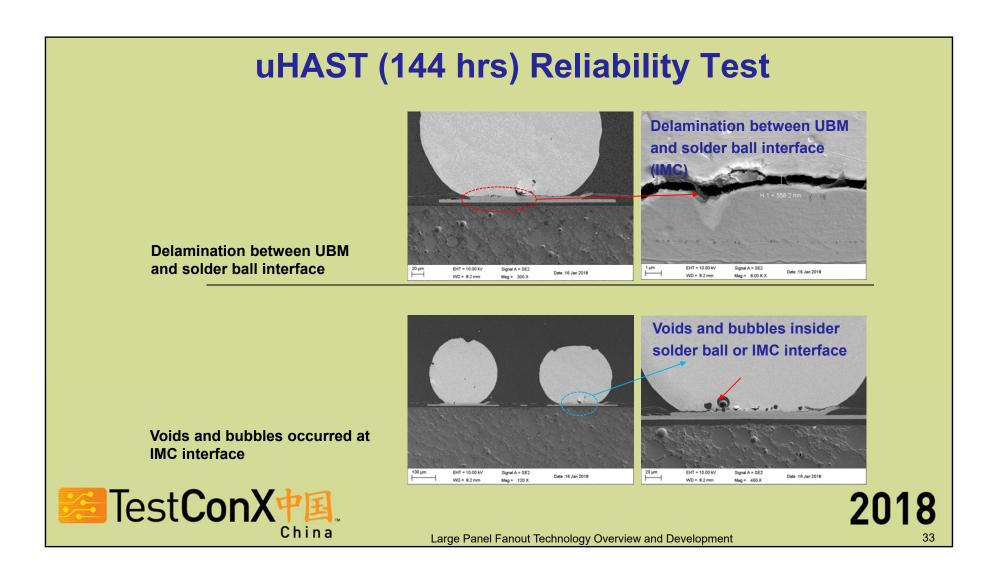

- During reliability test, we found solder ball drop off and big voids are observed after HTS-1008 hrs and TC-750 cycles, it is confirmed that reflow profile needs to be optimized.

- 2. After pre-conditioning. There are delamination found between PI materials, it is confirmed process of PI curing needs to be optimized.

- 3. For TC test, it is found that delamination occurred between PI and die, process and material are needed to be evaluated and optimized.

- 4. For uHAST-144h, it is found that delamination happened between UBM and solder ball, plating and reflow process must be evaluated and optimized.

Large Panel Fanout Technology Overview and Development

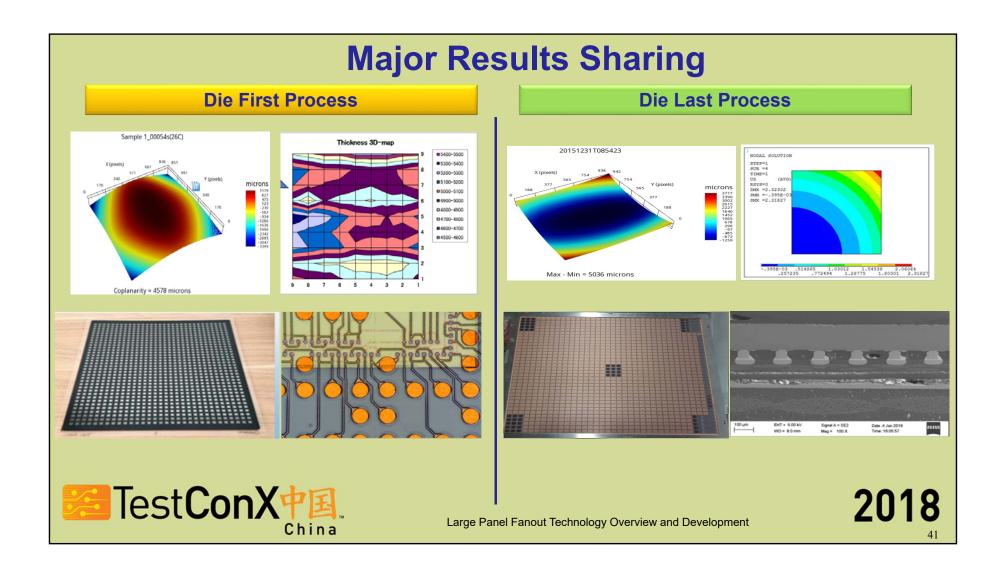

1st Run Reliability Test

Based on eWLB fan out packaging, daisychain dies are used for packaging, and reliability assessment is done for Pre-con, Thermal Cycles (TC), HTS and uHAST according to JEDEC requirements. The major results are shown below.

| Types of tests                 | JEDEC<br>standard | conditions                                                | Test<br>points | failures | Failure modes                                               | Root causes           |

|--------------------------------|-------------------|-----------------------------------------------------------|----------------|----------|-------------------------------------------------------------|-----------------------|

| Pre-con test                   | JESD22-A113       | 120°C, 24hrs;<br>30°C/60%RH, 96hrs;<br>260°C, 3x reflows; | I              | 29/248   | Delamination<br>between PI                                  | Process and materials |

|                                |                   | -40°C~125°C,10°C/min                                      | 320cycles      | 5/77     | -                                                           |                       |

| Thermal JES cycles             | JESD22-A104       |                                                           | 750cycles      | 59/77    | Delamination<br>between PI and<br>dies                      | Materials             |

| High temperature storage (HTS) | JESD22-A103       | 150°C,1008hrs                                             | 1008hrs        | 4/45     | EMC filling in and delamination between PI                  | Process               |

| uHAST JESD22-A11               |                   | 130℃,85%RH, 96hrs                                         | 96hrs          | 5/77     | -                                                           |                       |

|                                | JESD22-A110       |                                                           | 144hrs         | 22/77    | Voids and<br>delamination<br>between solder ball<br>and UBM | Process               |

Large Panel Fanout Technology Overview and Development

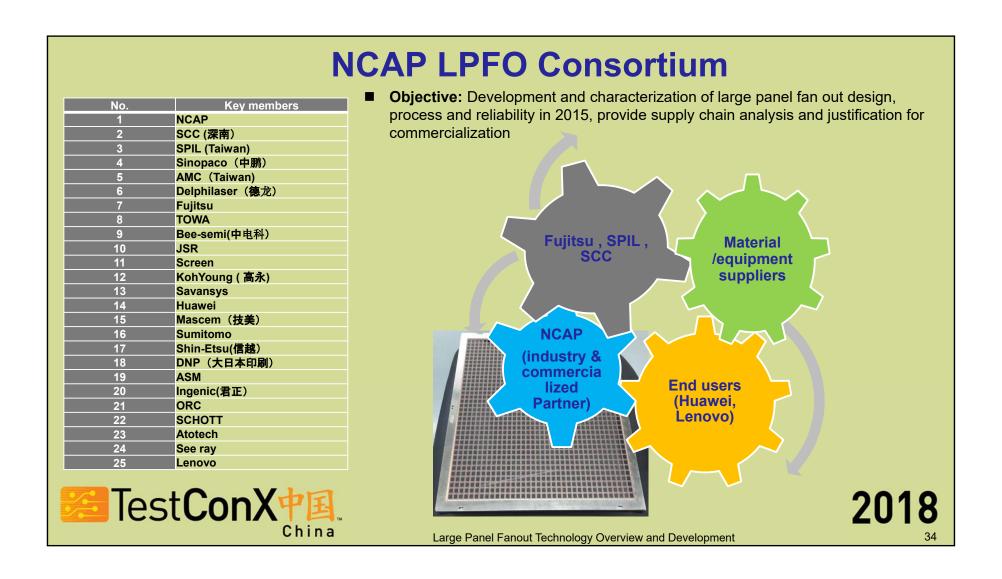

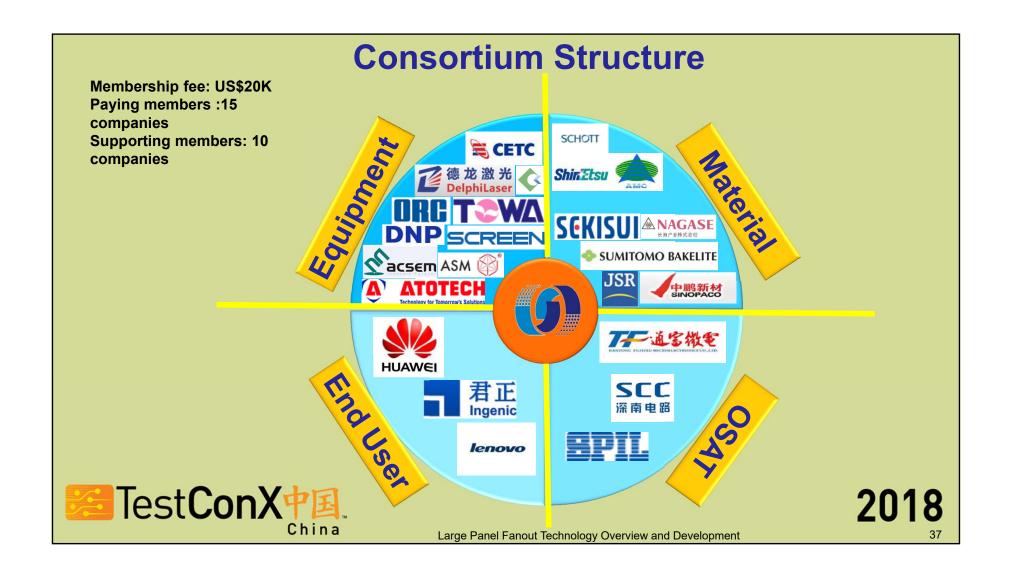

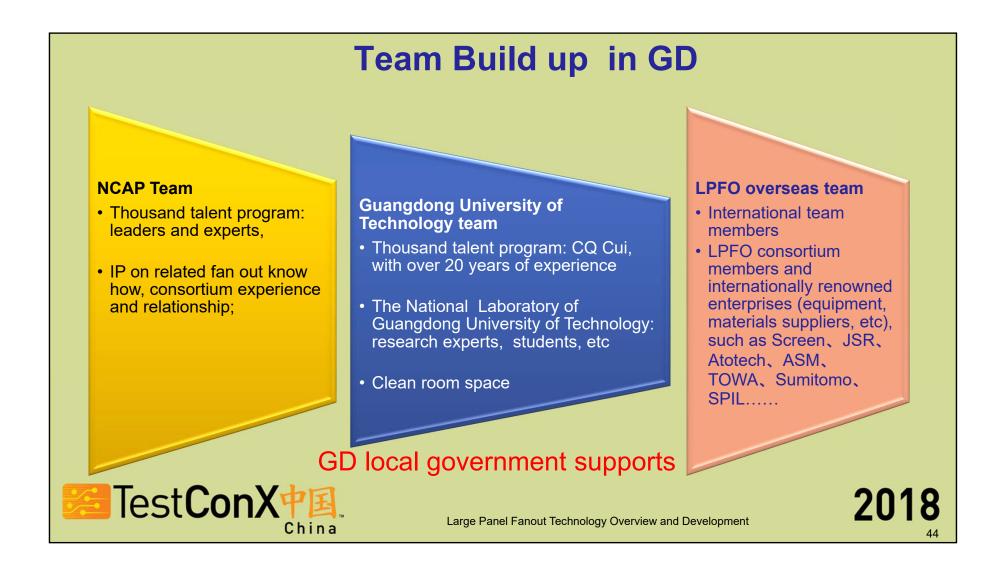

### **Consortium Updates and Complimentary**

NCAP has won the "Twelfth (2017) China Semiconductor Innovative Products and Technology" for "Integrated Large Panel Fan-out Advanced Packaging Technology".

Thanks to the supports of all the members of NCAP LPFO Consortium!

Large Panel Fanout Technology Overview and Development

2018

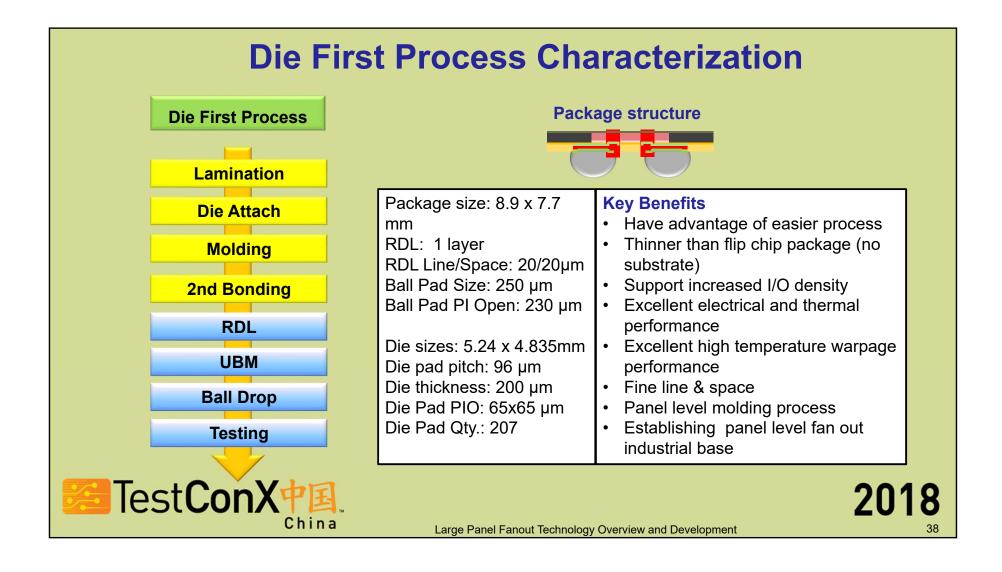

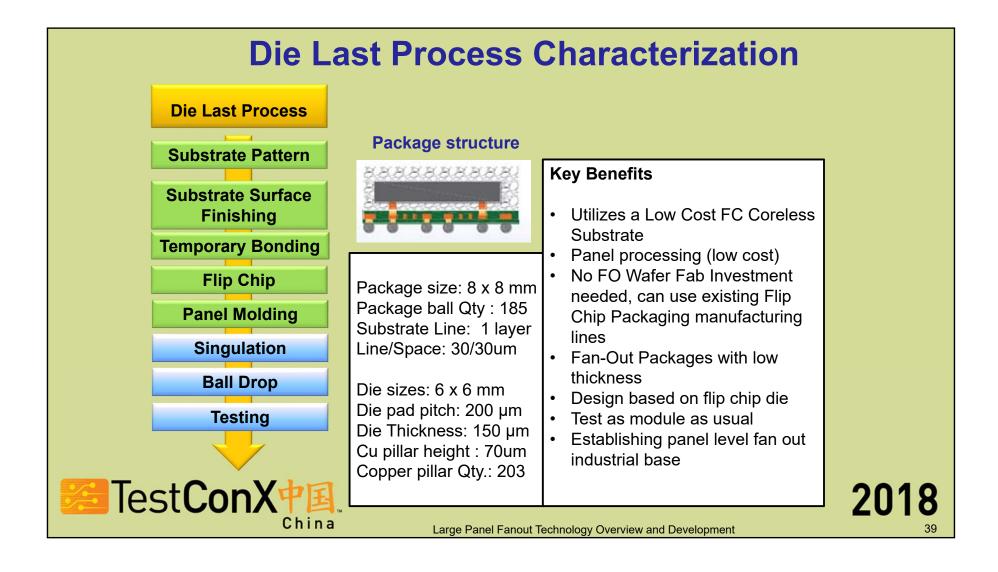

#### **Consortium Summary**

#### **Consortium**

on Low Cost Panel Level Fan-out Technology Development

- 25 International Companies joined the Consortium

- Target single die fan-out (one layer RDL) development & demonstration (Phase 1)

- Establish design, simulation, process capability and panel level fanout supply chain build up

- Complete single die fan-out lesson learnt and preliminary process & reliability qualification

- Drive low cost solutions & commercialization

- Establish panel level fan-out technology Industry chain embryonic in China

2018

Large Panel Fanout Technology Overview and Development

#### **TestConX China 2018**

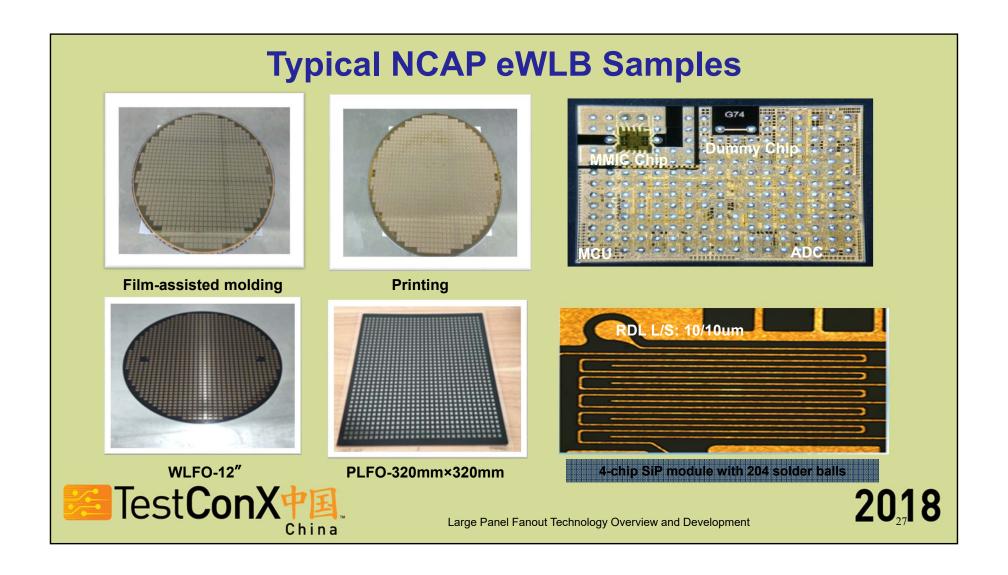

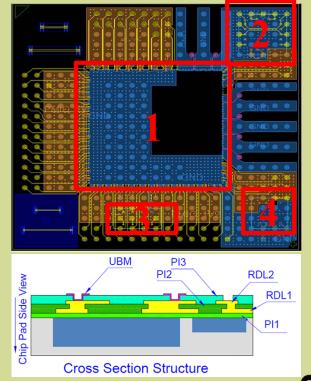

### The Design Of NCAP Phase II FOPLP Consortium

| No.          | 1    | 2         | 3     | 4         |

|--------------|------|-----------|-------|-----------|

| Chip<br>Type | MMIC | LDO<br>02 | Flash | LDO<br>01 |

| Size<br>(mm) | 6*6  | 2*2       | 2*1   | 1.5*1.5   |

- Panel Size: 600mmX600mm

- Package Size:12mmX12mm

- Min. Line Width/Space:10um/10um

- Min Chip to Chip Space: 200um

- **Integrated Chips Count: 4**

- Solder Ball Counts: >300

- RDL Layers: 2 Layers

Large Panel Fanout Technology Overview and Development

#### **Future Major Works to Be Done in GD**

1. Establishing large panel fan out engineering line and promote domestic equipment capability build up

In the next one year, large panel fan out line will be built up; some critical equipment will be built up, like die bonding, plating, PVD, de-bonding equipment;

2. Equipment and Material Evaluation and Verification

Critical panel level fan out equipment and material will be evaluated and verified;

- 3. Become partnership with GD semiconductor packaging equipment

- a. Work together and develop new equipment together;

- b. Provide engineering service to important customers;

- c. Provide training centre for universities and institute.

Large Panel Fanout Technology Overview and Development

#### **Conclusions**

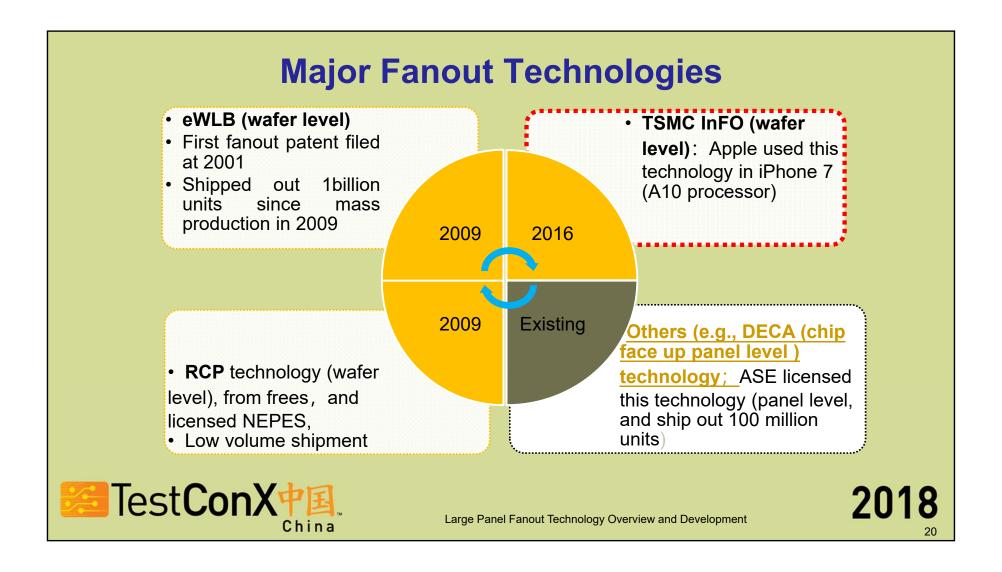

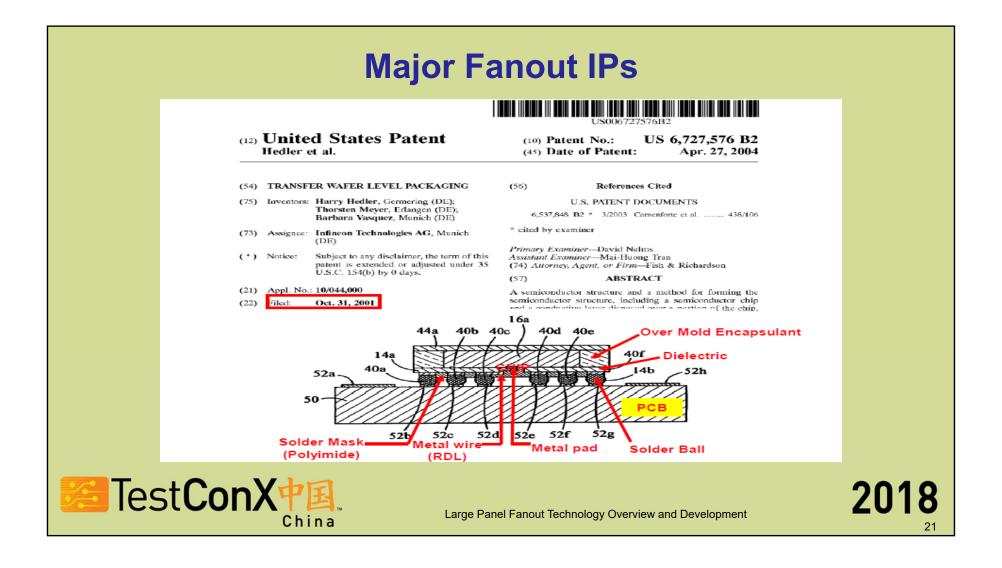

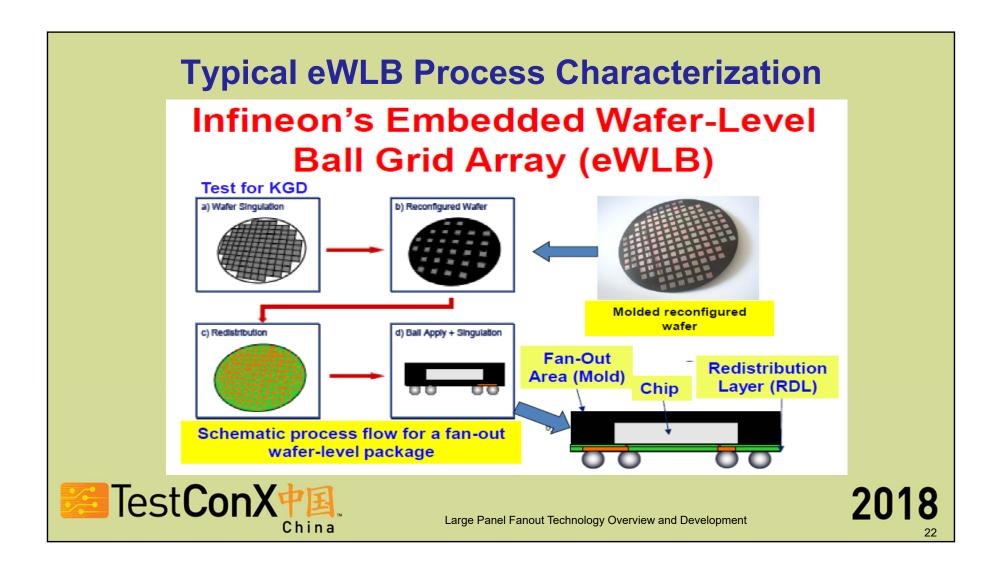

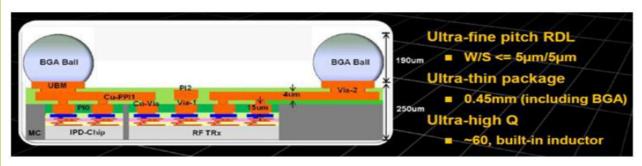

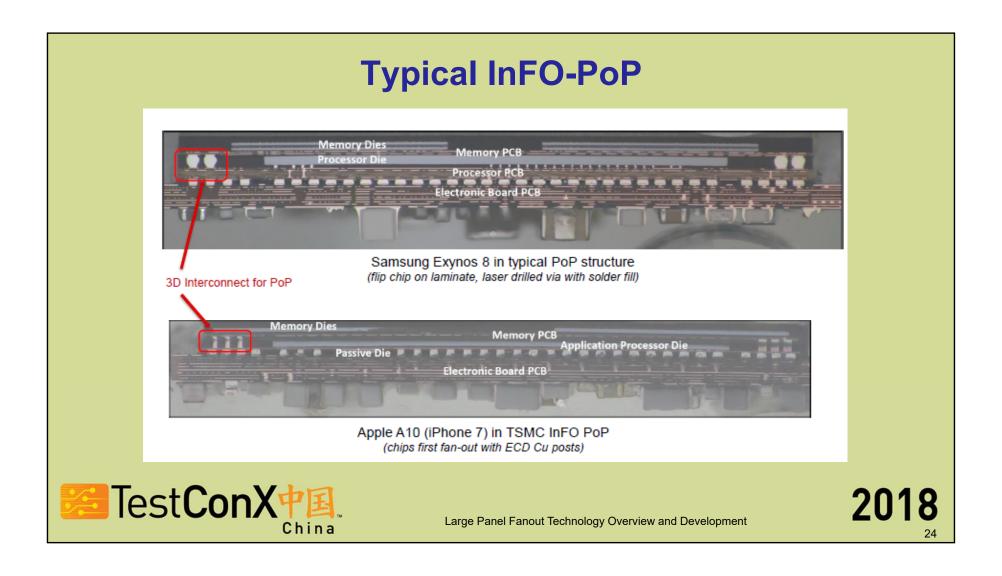

- 1. Fan out technologies are commercialized in the major forms of eWLB, RCP, InFO, and other mixed technologies.

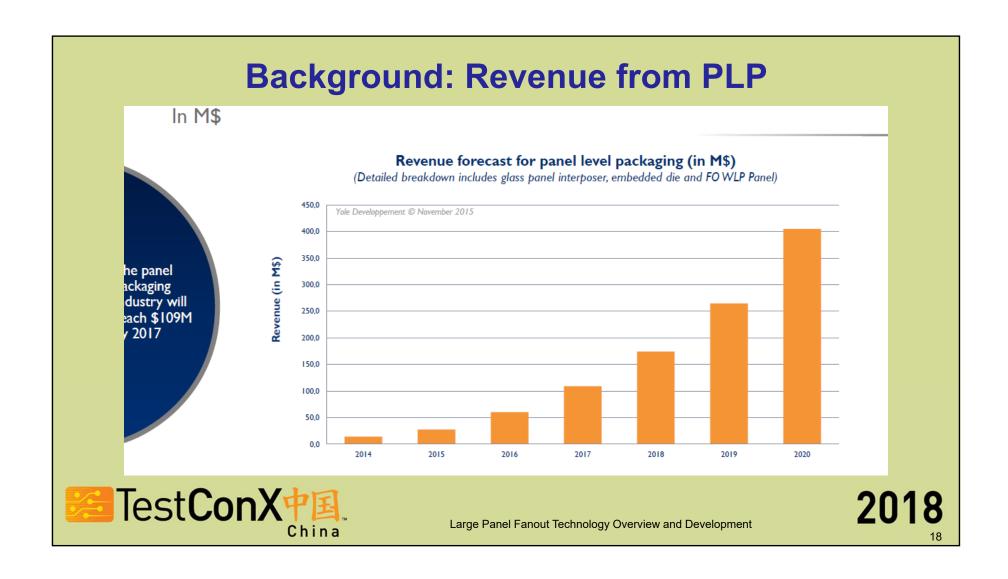

- 2. The market will be booming for fan out especially after Apple iPhone 7 was using InFO technologies. LPFO will be commercialized soon.

- 3. NCAP has established WLP Fan out and LPFO capability and pass relevant reliability test. LPFO engineering lines will be in GD province.

- 4. FoZhixin microelectronics Pte Ltd will be a critical window in GD province to show LPFO equipment capability and becoming solution providers.

Large Panel Fanout Technology Overview and Development 2018

### **Acknowledgements**

- 1. Thanks to NCAP 02 National Project supports, which support basic research and commercialized packaging environment build up.

- 2. Thanks to NCAP LPFO Consortium and provide huge process and reliability assessment, especially thanks to contributions of 25 key members of consortium.

- 3. Appreciate NCAP senior leadership team and their vision on LPFO.

- 4. Appreciate GDUT leaders to supports the LPFO engineering lines build up in GD.

2018

Large Panel Fanout Technology Overview and Development