# UNIVERSITY OF CALIFORNIA, IRVINE

# Out-of-order Parallel Discrete Event Simulation for Electronic System-Level Design

DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Weiwei Chen

Dissertation Committee: Professor Rainer Doemer, Chair Professor Daniel D. Gajski Professor Brian Demsky

2013

© 2013 Weiwei Chen

## DEDICATION

To my parents.

# Contents

| LI | ST O | F FIGURE   | S                                                  |     |   |     | vi    |

|----|------|------------|----------------------------------------------------|-----|---|-----|-------|

| LI | sт о | F TABLES   | 6                                                  |     |   |     | viii  |

| A  | CKNO | )WLEDGM    | 1ENTS                                              |     |   |     | xii   |

| CI | JRRI | CULUM V    | ΙΤΑΕ                                               |     |   |     | xiv   |

| AI | BSTR | ACT OF 1   | THE DISSERTATION                                   |     |   |     | xviii |

| 1  |      | oduction   |                                                    |     |   |     | 1     |

|    | 1.1  | •          | vel Design                                         |     |   |     | 4     |

|    |      |            | vels of Abstraction                                |     |   |     | 6     |

|    |      |            | le Y-Chart                                         |     |   |     | 7     |

|    |      | U          | stem-level Design Methodologies                    |     |   |     | 8     |

|    | 1.0  |            | ectronic System-Level Design Process               |     |   |     | 11    |

|    | 1.2  |            | and Simulation                                     |     |   |     | 14    |

|    |      |            | nguage Support for System-level Design             |     |   |     | 14    |

|    |      |            | stem Simulation Approaches                         |     |   |     | 17    |

|    | 1.0  |            | screte Event Simulation                            |     |   |     | 18    |

|    | 1.3  |            | on Goals                                           |     |   |     | 21    |

|    | 1.4  |            | on Overview                                        |     |   |     | 22    |

|    | 1.5  |            | Vork                                               |     |   |     | 23    |

|    |      |            | e SpecC Language                                   |     |   |     | 24    |

|    |      |            | e SystemC Language                                 |     |   |     | 31    |

|    |      |            | e System-on-Chip Environment (SCE) Design Flow     |     |   |     | 32    |

|    |      |            | ulti-core Technology and Multithreaded Programming |     |   |     | 35    |

|    |      | 1.5.5 Eff  | ficient Model Validation and Simulation            | • • | • | • • | 37    |

| 2  | The  | Concurren  | C Model of Computation                             |     |   |     | 40    |

|    | 2.1  | Motivation | •                                                  |     |   |     | 40    |

|    | 2.2  | Models of  | Computation (MoCs)                                 |     |   |     | 42    |

|    | 2.3  |            | $\operatorname{MoC}$                               |     |   |     | 44    |

|    |      |            | lationship to C-based SLDLs                        |     |   |     | 45    |

|    |      | 2.3.2 Co   | ncurren $\hat{C}$ Features                         |     |   |     | 46    |

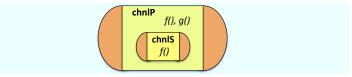

|    |      | 2.3.3 Co   | mmunication Channel Library                        |     |   |     | 47    |

|                                                  |     | 2.3.4 Relationship to KPN and SDF                                                                                                    |  |

|--------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                  | 2.4 | Case Study                                                                                                                           |  |

| 3 Synchronous Parallel Discrete Event Simulation |     |                                                                                                                                      |  |

|                                                  | 3.1 | Traditional Discrete Event Simulation                                                                                                |  |

|                                                  | 3.2 | SLDL Multi-threading Semantics                                                                                                       |  |

|                                                  |     | 3.2.1 Cooperative multi-threading in SystemC                                                                                         |  |

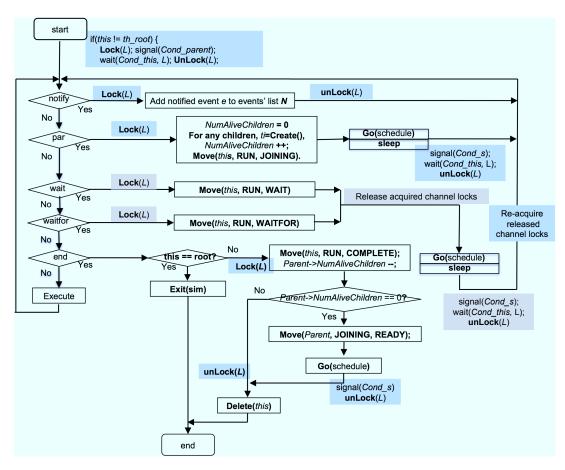

|                                                  |     | 3.2.2 Pre-emptive multi-threading in SpecC                                                                                           |  |

|                                                  | 3.3 | Synchronous Parallel Discrete Event Simulation                                                                                       |  |

|                                                  | 3.4 | Synchronization for Multi-Core Parallel Simulation                                                                                   |  |

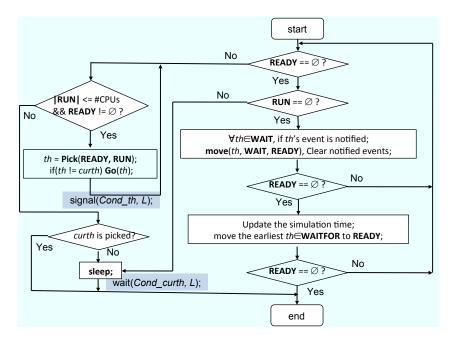

|                                                  | 0.1 | 3.4.1 Protecting Scheduling Resources                                                                                                |  |

|                                                  |     | 3.4.2 Protecting Communication                                                                                                       |  |

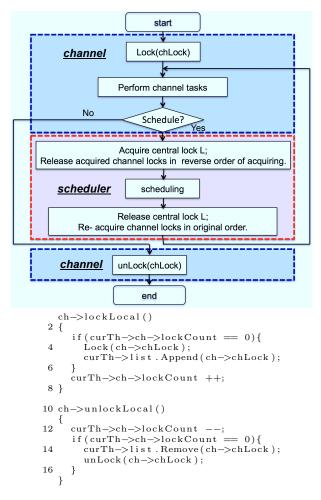

|                                                  |     | 3.4.3 Channel Locking Scheme                                                                                                         |  |

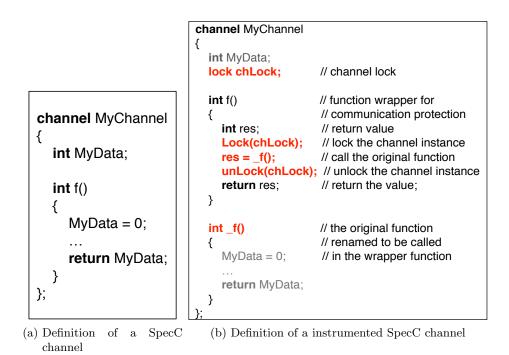

|                                                  |     | 3.4.4 Automatic Code Instrumentation for Communication Protection 63                                                                 |  |

|                                                  | 3.5 | Implementation Optimization for Multi-Core Simulation                                                                                |  |

|                                                  | 3.6 | Experiments and Results                                                                                                              |  |

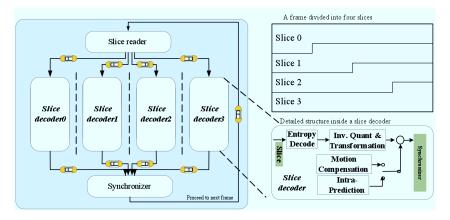

|                                                  | 5.0 | 3.6.1 Case Study on a H.264 Video Decoder                                                                                            |  |

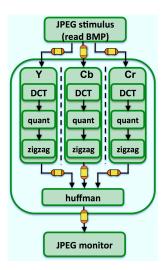

|                                                  |     | 3.6.2 Case Study on a JPEG Encoder                                                                                                   |  |

|                                                  |     | 5.0.2 Case Study on a JPEG Encoder                                                                                                   |  |

| 4                                                | Out | -of-order Parallel Discrete Event Simulation 74                                                                                      |  |

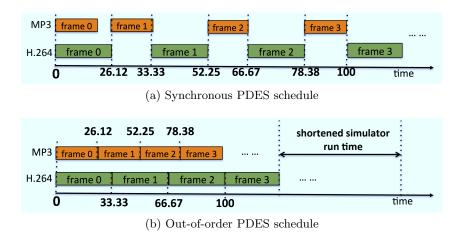

|                                                  | 4.1 | Motivation                                                                                                                           |  |

|                                                  | 4.2 | Out-of-order Parallel Discrete Event Simulation                                                                                      |  |

|                                                  |     | 4.2.1 Notations                                                                                                                      |  |

|                                                  |     | 4.2.2 Out-of-order PDES Scheduling Algorithm                                                                                         |  |

|                                                  | 4.3 | Out-of-order PDES Conflict Analysis                                                                                                  |  |

|                                                  |     | 4.3.1 Thread Segments and Segment Graph                                                                                              |  |

|                                                  |     | 4.3.2 Static Conflict Analysis                                                                                                       |  |

|                                                  |     | 4.3.3 Dynamic Conflict Detection                                                                                                     |  |

|                                                  | 4.4 | Experimental Results                                                                                                                 |  |

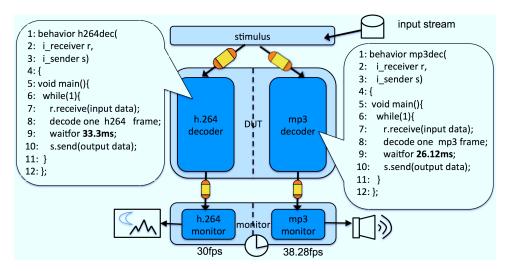

|                                                  |     | 4.4.1 An Abstract Model of a DVD Player                                                                                              |  |

|                                                  |     | 4.4.2 A JPEG Encoder Model                                                                                                           |  |

|                                                  |     | 4.4.3 A Detailed H.264 Decoder Model                                                                                                 |  |

|                                                  |     |                                                                                                                                      |  |

| 5                                                | Opt | imized Out-of-order Parallel Discrete Event Simulation 97                                                                            |  |

|                                                  | 5.1 | Optimized Compiler Using Instance Isolation                                                                                          |  |

|                                                  |     | 5.1.1 Motivation $\dots \dots \dots$ |  |

|                                                  |     | 5.1.2 Instance Isolation without Code Duplication                                                                                    |  |

|                                                  |     | 5.1.3 Definitions for the Optimized Static Conflict Analysis 103                                                                     |  |

|                                                  |     | 5.1.4 Algorithm for Static Conflict Analysis                                                                                         |  |

|                                                  |     | 5.1.5 Experimental Results                                                                                                           |  |

|                                                  | 5.2 | Optimized Scheduling Using Predictions                                                                                               |  |

|                                                  |     | 5.2.1 State Prediction to Avoid False Conflicts                                                                                      |  |

|                                                  |     | 5.2.2 Static Prediction Analysis                                                                                                     |  |

|                                                  |     | 5.2.3 Out-of-order PDES scheduling with Predictions                                                                                  |  |

|                                                  |     |                                                                                                                                      |  |

|    |       | 5.2.4 Optimized out-of-order PDES Scheduling Conflict Checking with a Com- |     |

|----|-------|----------------------------------------------------------------------------|-----|

|    |       | bined Prediction Table                                                     |     |

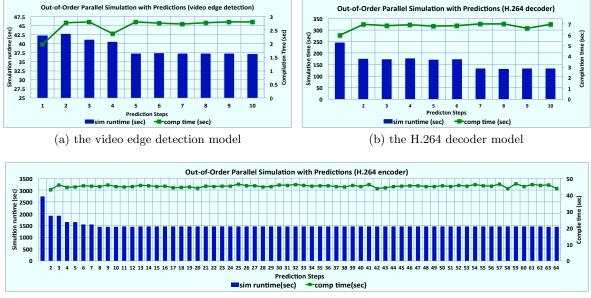

|    |       | 5.2.5 Experimental Results                                                 | 119 |

| 6  | Con   |                                                                            | 123 |

|    | 6.1   | Experimental Setup                                                         | 123 |

|    |       | 6.1.1 Experimental Environment Setup                                       | 123 |

|    |       | 6.1.2 The Parallel Benchmark Models                                        | 125 |

|    |       | 6.1.3 The Embedded Applications                                            |     |

|    | 6.2   | Parallel Discrete Event Simulation Overlook                                | 131 |

| 7  | Utili | zing the Parallel Simulation Infrastructure                                | 136 |

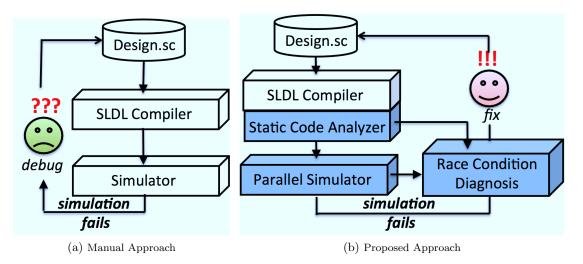

|    | 7.1   | Introduction                                                               | 137 |

|    | 7.2   | Overview and Approach                                                      | 138 |

|    |       | 7.2.1 Creating Parallel System Models                                      | 138 |

|    |       | 7.2.2 Shared Variables and Race Conditions                                 | 139 |

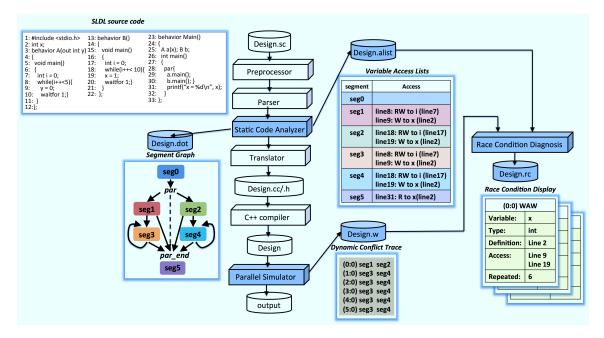

|    | 7.3   | Automatic Race Condition Diagnosis                                         | 141 |

|    | 7.4   | Race Condition Elimination Infrastructure                                  | 143 |

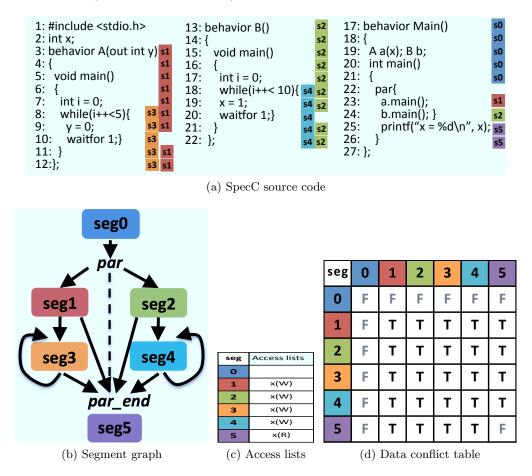

|    |       | 7.4.1 Static Code Analysis                                                 | 143 |

|    |       | 7.4.2 Dynamic Race Condition Checking                                      | 146 |

|    | 7.5   | Experiments and Results                                                    | 147 |

|    |       | 7.5.1 Case study: A Parallel H.264 Video Decoder                           | 147 |

|    |       | 7.5.2 Case study: A Parallel H.264 Video Encoder                           | 149 |

|    |       | 7.5.3 Additional Embedded Applications                                     | 150 |

|    | 7.6   | Conclusions                                                                | 151 |

| 8  | Con   | lusions                                                                    | 152 |

|    | 8.1   | Contributions                                                              | 153 |

|    |       | 8.1.1 A model of computation for system-level design                       | 153 |

|    |       | 8.1.2 A synchronous parallel discrete event simulator                      | 153 |

|    |       | 8.1.3 An advanced parallel discrete event simulation approach              | 154 |

|    |       | 8.1.4 An infrastructure for increasing modeling observability              | 156 |

|    | 8.2   | Future Work                                                                | 156 |

|    |       | 8.2.1 Model Parallelization                                                | 156 |

|    |       | 8.2.2 Multithreading Library Support                                       | 157 |

|    |       | 8.2.3 Extension to the SystemC SLDL                                        | 157 |

|    |       | 8.2.4 Parallel Full System Validation                                      | 157 |

|    | 8.3   | Concluding Remarks                                                         |     |

| Bi | bliog | aphy                                                                       | 159 |

# List of Figures

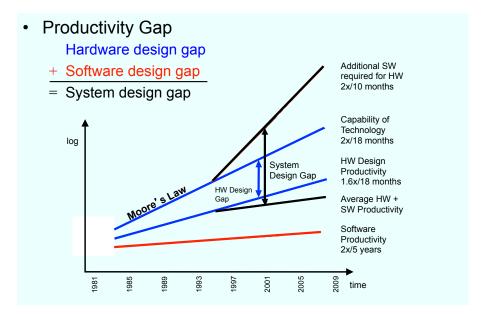

| 1.1  | Hardware and software design gaps versus time (source [11])                     | 5   |

|------|---------------------------------------------------------------------------------|-----|

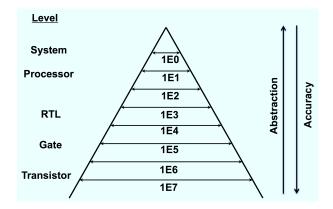

| 1.2  | Levels of abstraction in SoC design (source [18])                               | 6   |

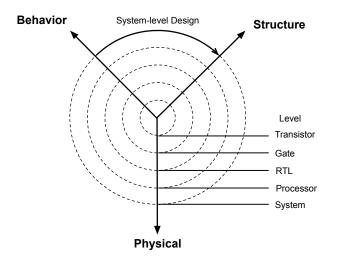

| 1.3  | System-level design in the Y-Chart (source [17])                                | 7   |

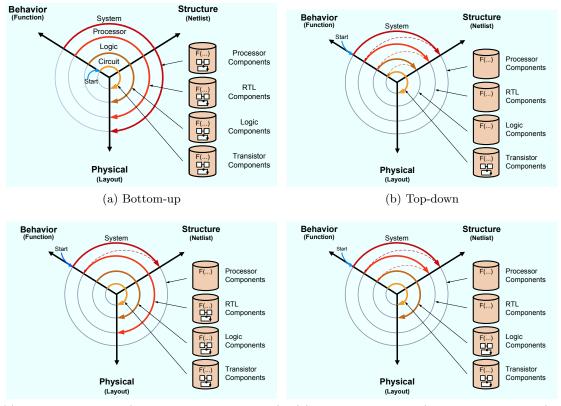

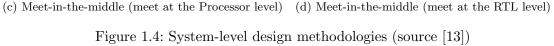

| 1.4  | System-level design methodologies (source [13])                                 | 10  |

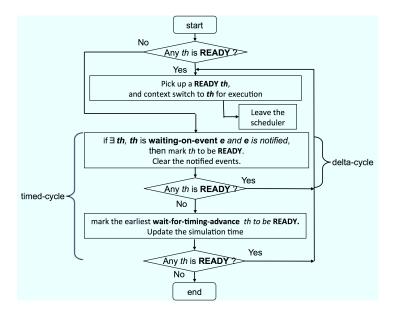

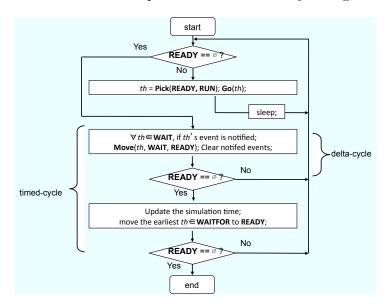

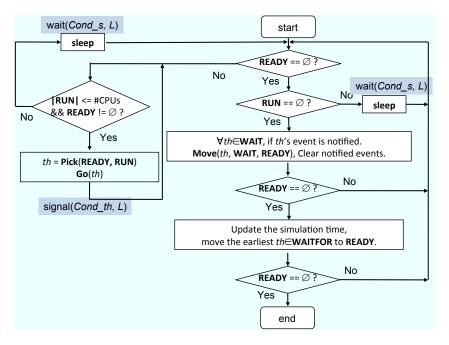

| 1.5  | Scheduler for discrete event simulation                                         | 19  |

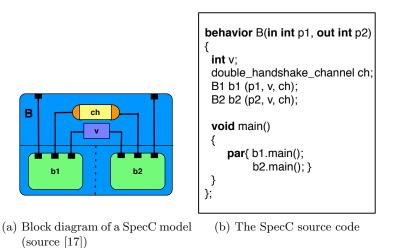

| 1.6  | The block diagram and source code of a SpecC model                              | 25  |

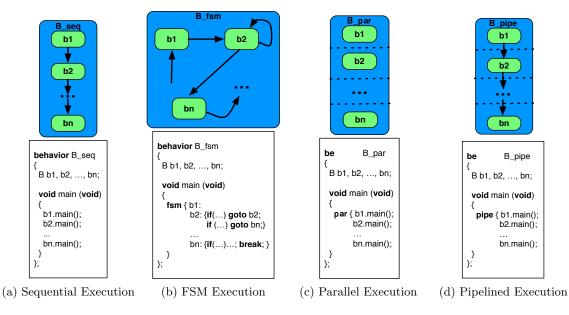

| 1.7  | SpecC behavioral hierarchy block diagram and syntax [18]                        | 26  |

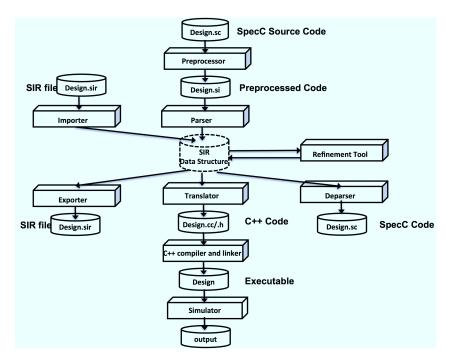

| 1.8  | Compilation flow for a SpecC Design (source [45])                               | 31  |

| 1.9  | SystemC language architecture (source [38])                                     | 32  |

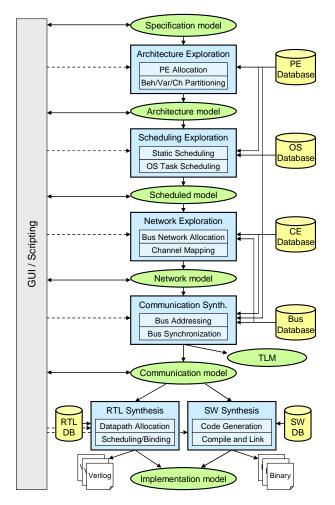

| 1.10 | Refinement-based design flow in the SCE framework (source [46])                 | 33  |

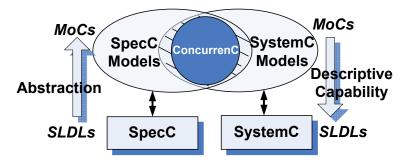

| 2.1  |                                                                                 | 45  |

| 2.2  | 1 1                                                                             | 46  |

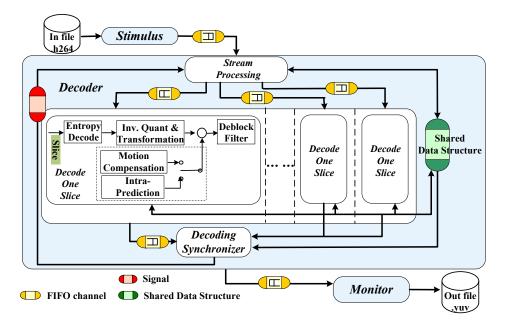

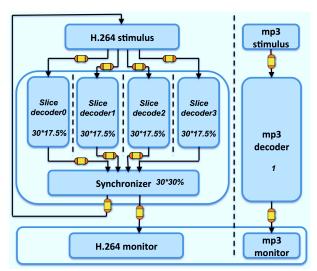

| 2.3  | Proposed H.264 Decoder Block Diagram                                            | 50  |

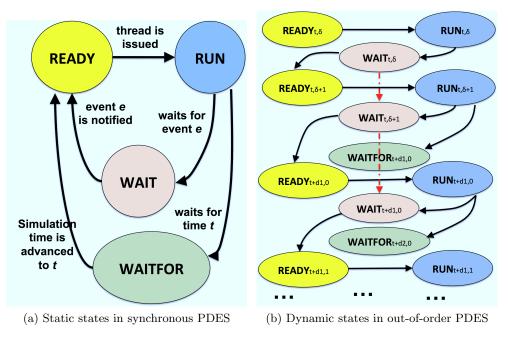

| 3.1  | 1                                                                               | 54  |

| 3.2  | J 1                                                                             | 59  |

| 3.3  |                                                                                 | 61  |

| 3.4  | J I                                                                             | 63  |

| 3.5  | 1                                                                               | 64  |

| 3.6  | U U                                                                             | 65  |

| 3.7  | I U I                                                                           | 67  |

| 3.8  | *                                                                               | 68  |

| 3.9  | Parallelized JPEG encoder model.                                                | 72  |

| 4.1  |                                                                                 | 75  |

| 4.2  |                                                                                 | 76  |

| 4.3  |                                                                                 | 77  |

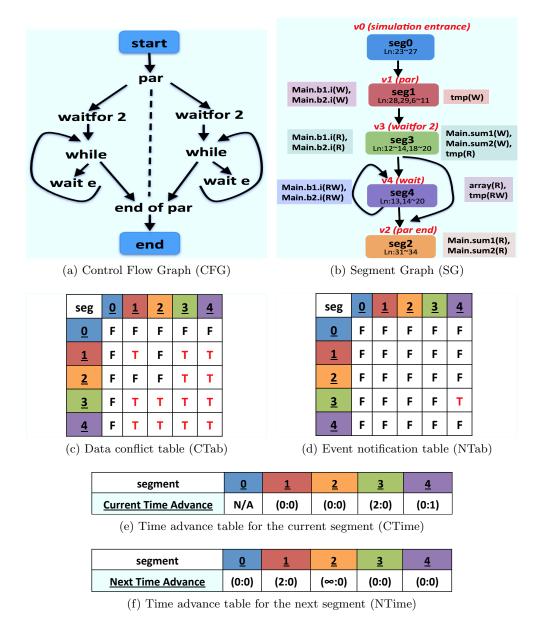

| 4.4  | 1 1                                                                             | 82  |

| 4.5  | The control flow graph, segment graph, conflict tables, and time advance tables |     |

|      |                                                                                 | 84  |

| 4.6  |                                                                                 | 87  |

| 4.7  | The abstract DVD player example                                                 | 93  |

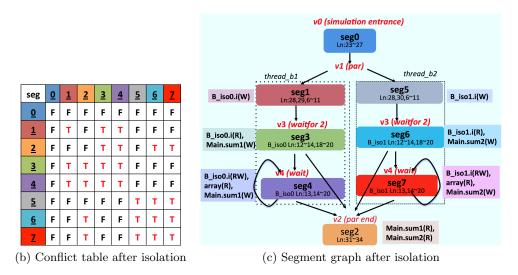

| 5.1  | 1 1                                                                             | 99  |

| 5.2  | Simple design example with isolated instances                                   | .00 |

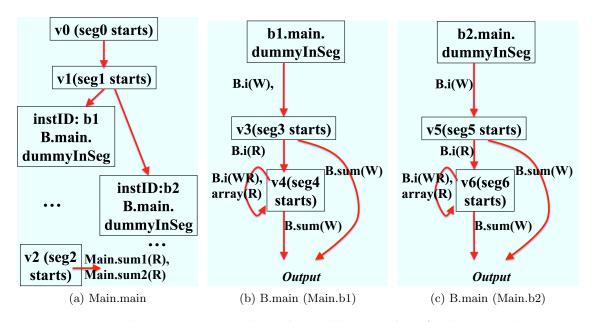

| 5.3 | Function-local segment graphs and variable access lists for the example in Fig. 5.2.106    |

|-----|--------------------------------------------------------------------------------------------|

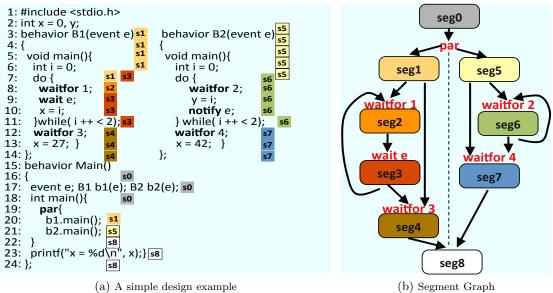

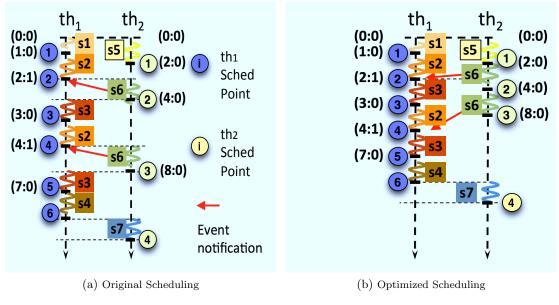

| 5.4 | Simple design example                                                                      |

| 5.5 | Out-of-order PDES scheduling                                                               |

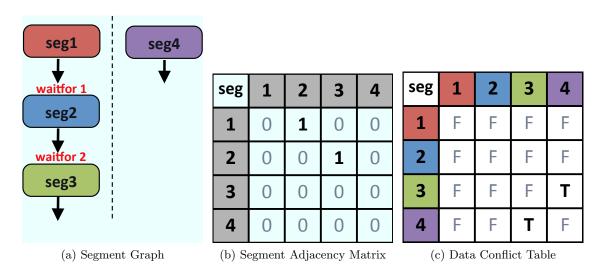

| 5.6 | A partial Segment Graph with Adjacency Matrix and Data Conflict Table 114                  |

| 5.7 | Data structures for optimized out-of-order PDES scheduling                                 |

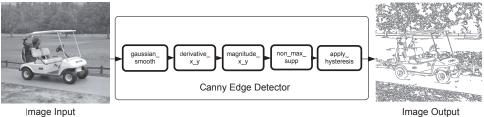

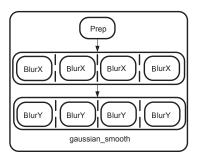

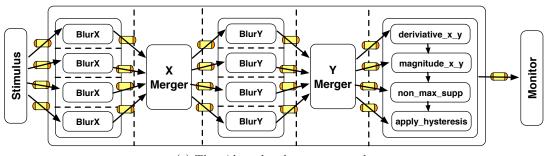

| 5.8 | An video edge detector example                                                             |

| 5.9 | Simulation run time and compilation time for OoO PDES with predictions $\ . \ . \ . \ 122$ |

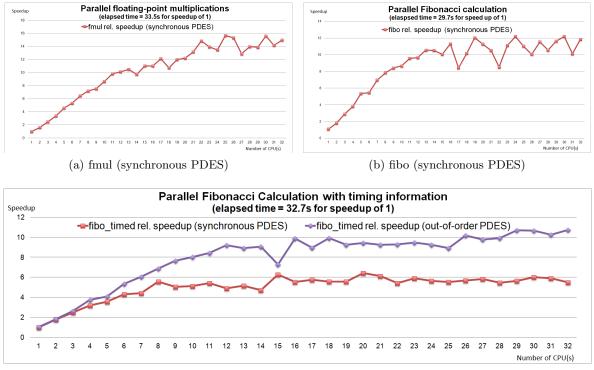

| 6.1 | Simulation results for highly parallel benchmark models                                    |

| 7.1 | Validation and debugging flow for parallel system models                                   |

| 7.2 | Reusing essential tools from a parallel simulation infrastructure to diagnose race         |

|     | conditions in parallel models                                                              |

| 7.3 | Tool flow for automatic race condition diagnosis among shared variables in par-            |

|     | allel system models                                                                        |

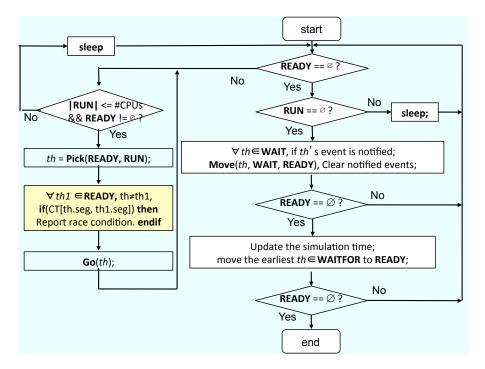

| 7.4 | A parallel design example with a simple race condition                                     |

| 7.5 | Parallel simulation algorithm with dynamic race condition checks. $\ldots$                 |

|     |                                                                                            |

# List of Tables

| $2.1 \\ 2.2$ | System-level design in comparison with the well-established RTL design 41<br>Parameterized Communication Channels                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2<br>2.3   | Simulation Results, H.264 Decoder modeled in <i>ConcurrenC</i>                                                                                                            |

| 3.1          | Simulation results of a well balanced H.264 Decoder ("Harbour", 299 frames 4 slices each, 30 fps)                                                                         |

| 3.2          | Comparison with optimized implementation                                                                                                                                  |

| 3.3          | Simulation speedup with different h264 streams (spec model)                                                                                                               |

| 3.4          | Simulation results of JPEG Encoder                                                                                                                                        |

| 4.1          | Time advances at segment boundaries                                                                                                                                       |

| 4.2          | Examples for direct and indirect timing hazards                                                                                                                           |

| 4.3          | Experimental results for the abstract DVD player example                                                                                                                  |

| 4.4          | Out-of-order PDES statistics for JPEG and H.264 examples                                                                                                                  |

| 4.5          | Experimental results for the JPEG Image Encoder and the H.264 Video Decoder examples                                                                                      |

| $5.1 \\ 5.2$ | Experimental Results for H.264 Decoder Models with Different Degree of Isolation.100<br>Compilation time for a Set of JPEG Image Encoder and H.264 Video Decoder          |

| 5.3          | Models                                                                                                                                                                    |

| 0.0          | Models.                                                                                                                                                                   |

| 5.4          | Experimental results for embedded applications                                                                                                                            |

| $6.1 \\ 6.2$ | Experimental results for embedded application examples using standard algorithms.131<br>Comparison of traditional sequential, synchronous parallel, and out-of-order par- |

| 0.2          | allel discrete event simulation                                                                                                                                           |

| 7.1          | Experimental results on tool execution time for diagnosing race conditions in                                                                                             |

| 7.2          | embedded multi-media applications                                                                                                                                         |

|              | plications                                                                                                                                                                |

## List of Acronyms

- **AHB** Advanced High-performance Bus. System bus definition within the AMBA 2.0 specification. Defines a high-performance bus including pipelined access, bursts, split and retry operations.

- **AMBA** Advanced Microprocessor Bus Architecture. Bus system defined by ARM Technologies for system-on-chip architectures.

- **ASIC** Application Specific Integrated Circuit. An integrated circuit, chip, that is custom designed for a specific application, as supposed to a general-purpose chip like a microprocessor.

- **Behavior** An encapsulating entity, which describes computation and functionality in the form of an algorithm.

- **BFM** Bus Functional Model. A pin-accurate and cycle-accurate model of a bus (see also PCAM).

- **CAD** Computer Aided Design. Design of systems with the help of and assisted by computer programs, i.e. software tools.

- **CE** Communication Element. A system component that is part of the communication architecture for transmission of data between PEs, e.g. a transducer, an arbiter, or an interrupt controller.

- **Channel** An encapsulating entity, which abstractly describes communication between two or more partners.

- **DE** Discrete Event Simulation.

- **DFG** Data Flow Graph. An abstract description of computation capturing operations (nodes) and their dependencies (operands).

- **DSP** Digital Signal Processor. A specialized microprocessor for the manipulation of digital audio and video signals.

- **EDA** Electronic Design Automation. A category of software tools for designing electronic systems.

- **ESL** Electronic System Level. Electronic system level design and verification is an emerging electronic design methodology that focuses on the higher abstraction level concerns first and foremost.

- **FPGA** Field Programmable Gate Array. An integrated circuit composed of an array of configurable logic cells, each programmable to execute a simple function, surrounded by a periphery of I/O cells.

- **FSM** Finite State Machine. A model of computation that captures an algorithm in states and rules for transitions between the states.

- **FSMD** Finite State Machine with Datapath. Abstract model of computation describing the states and state transitions of an algorithm like a FSM and the computation within a state using a DFG.

- **GPU** Graphics Processing Unit.

- **HCFSM** Hierarchical Concurrent Finite State Machine. An extension of the FSM that explicitly expresses hierarchy and concurrency.

- **HDL** Hardware Description Language. A language for describing and modeling blocks of hardware.

- HW Hardware. The tangible part of a computer system that is physically implemented.

- **ISO** International Organization for Standardization

- **ISS** Instruction Set Simulator. Simulates execution of software on a processor at the ISA level.

- **KPN** Kahn Process Network. A deterministic model of computation where processes are connected by unbounded FIFO communication channels to form a network

- **MoC** Model of Computation. A meta model that defines syntax and semantic to formally describe any computation, usually for the purpose of analysis.

- **MPSoC** Multi-Processor System-on-Chip. A highly integrated device implementing a complete computer system with multiple processors on a single chip.

- **OoO PDES** Out-of-order Parallel Discrete Event Simulation.

- **OS** Operating System. Software entity that manages and controls access to the hardware of a computer system. It usually provides scheduling, synchronization and communication primitives.

- **PCAM** Pin-accurate and Cycle-Accurate Model. An abstract model that accurately captures all pins (wires) and is cycle timing accurate.

- **PDES** Parallel Discrete Event Simulation.

- **PE** Processing Element. A system component that provides computation capabilities, e.g. a custom hardware or generic processor.

- **PSM** Program State Machine. A powerful model of computation that allows programming language constructs to be included in leaf nodes of a HCFSM.

- **RTL** Register Transfer Level. Description of hardware at the level of digital data paths, the data transfer and its storage.

- **RTOS** Real-Time Operating System. An operating system that responds to an external event within a predictable time.

- **SCE** SoC Environment. A set of tools for the automated, computer-aided design of SoC and computer systems.

- **SHIM** Software/hardware integration medium. A concurrent asynchronous deterministic model which is essentially an effective KPN with rendezvous communication for heterogeneous embedded systems.

- **SLDL** System-Level Design Language. A language for describing a heterogeneous system consisting of hardware and software at a high level of abstraction.

- **SIR** Syntax-Independent Representation. The intermediate representation of SpecC SLDL.

- **SoC** System-On-Chip. A highly integrated device implementing a complete computer system on a single chip.

- SW Software.

- **TLM** Transaction Level Model. A model of a system in which communication is described as transactions, abstract of pins and wires.

## Acknowledgements

The six years for Ph.D. study is such a wonderful and enjoyable journey which makes me a much better person in every possible way. I would like to take this opportunity to thank my professors, family, colleagues and friends who have encouraged and supported me in this process.

First and foremost, I would like to gratefully and sincerely thank my advisor, Prof. Rainer Doemer, for his guidance, understanding, patience and support during my doctorate study at UC Irvine. His technical insights, organization talents, amiable personality, and witty sense of humor have tremendously inspired and shaped me to be a good scholar and person. I enjoy our meetings and conversations which always bring me the morale, courage, and new ideas to identify and solve research and teaching problems. I also appreciate our discussions on philosophical topics in terms of research, teaching, work and living which I believe will benefit me for my whole life.

I would like to thank Prof. Daniel D. Gajski for serving on my committee and supporting me to pursue my career goal. His critical and visionary opinions and expertise has provided me a thorough and comprehensive view in the area of embedded computer systems. It is also so pleasant to have Prof. Gajski around in the same working area who cheers us up every day. In addition, I would also like to thank Prof. Brian Demsky for serving on my committee and for his valuable suggestions to improve this dissertation.

I would like to thank the members from the Laboratory for Embedded Computer Systems (LECS) in the Center for Embedded Computer Systems (CECS). In particular, I would like to thank Xu Han, Che-Wei Chang and Yasaman Samei for the group discussions and their contributions on the experimental models that have been used in this work. Many thanks to Tim Schmidt and Steffen Peter for the great research discussions, serving as the critical readers of this dissertation, and providing many constructive critiques. Also, special thanks to the CECS "Game Night" group, including Tim, Xu, Che-Wei, Steffen, Yasaman and I, which grants us the opportunity to know each other outside of the normal work setting and undoubtedly improves our nerdy social life. I am so fortunate to have their support and friendship in these years.

I would like to thank Dr. Christopher O'Neal from the Teaching, Learning and Technology Center (TLTC) at UC Irvine who has supervised me in the Pedagogical Fellowship (PF) program. His knowledge, passion and enthusiasm has opened my eyes towards the scholarship of teaching. I am grateful to his trust and support which encourages me to push myself out of my comfort zone to pursue excellence. I would also like to thank my fellow Pedagogical Fellows (PFFs) for their brilliant diverse mind sets which has greatly enriched my PF experience and their precious friendship. This work has been supported in part by funding from the National Science Foundation (NSF) under research grant NSF Award #0747523 led by Prof. Doemer. I would like to thank the NSF for the valuable support.

Last but not least, I would like to express my deepest gratitude to my parents, Guoyao and Xiuhua, for their unconditional and endless love and faith in me, the very source of motivation to the pursuit of my dream.

## CURRICULUM VITAE

# Weiwei Chen

| EDUCATION                                                                                                                                                            |                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| <b>Ph.D. in Electrical and Computer Engineering</b><br>University of California, Irvine                                                                              | 2013                           |

| M.S. in Computer Engineering<br>Shanghai Jiao Tong University, China                                                                                                 | 2007                           |

| <b>B.Eng. in Computer Science and Engineering</b><br>Department of Computer Science and Engineering<br>Teaching Reform Class, Shanghai Jiao Tong University, China   | 2004                           |

| <b>International Exchange Student</b><br>School of Electrical and Computer Engineering<br>Purdue University, West Lafayette, Indiana                                 | 2003                           |

| High School Graduation                                                                                                                                               | 2000                           |

| EXPERIENCE                                                                                                                                                           |                                |

| University of California, Irvine<br>Graduate Student Researcher<br>Center for Embedded Computer Systems<br>Department of Electrical Engineering and Computer Science | Irvine, CA<br>2007 - 2013      |

| <b>Pedagogical Fellow</b><br>Teaching, Learning and Technology Center (TLTC)<br>The Henry Samueli School of Engineering                                              | 2012 - 2013                    |

| <b>Teaching Assistant</b><br>Department of Electrical Engineering and Computer Science                                                                               | 2008 - 2013                    |

| Shanghai Jiao Tong University<br>Graduate Research Assistant<br>School of Microelectronics                                                                           | Shanghai, China<br>2004 - 2007 |

| <b>Teaching Assistant</b><br>School of Microelectronics                                                                                                              | 2005 - 2006                    |

| <i>Microsoft</i><br>Software Development Engineer Intern                                                                                                             | Seattle, WA 2011               |

| IBM China System and Technology Lab (CSTL)<br>R&D Engineer Intern                                                                                                    | Shanghai, China<br>2006 - 2007 |

#### PUBLICATIONS

#### Journal Articles (peer reviewed)

- **J3. Weiwei Chen**, Xu Han, Che-Wei Chang, Rainer Doemer, "Out-of-Order Parallel Discrete Event Simulation for Transaction Level Models", in preparation for submission to *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* (*TCAD*)

- J2. Weiwei Chen, Xu Han, Che-Wei Chang, Rainer Doemer, "Advances in Parallel Discrete Event Simulation for Electronic System-Level Design", accepted for publication in *IEEE Design & Test of Computers*, vol.30, no.1, pp.45-54, January/February 2013

- J1. Weiwei Chen, Xu Han, Rainer Doemer, "Multi-Core Simulation of Transaction Level Models using the System-on-Chip Environment", *IEEE Design & Test of Computers*, vol.28, no.3, pp.20-31, May-June 2011

#### Conference Papers (peer reviewed)

- C12. Xu Han, Weiwei Chen, Rainer Doemer, "Designer-in-the-Loop Recoding of ESL Models using Static Parallel Access Conflict Analysis", in Proceedings of the Workshop on Software and Compilers for Embedded Systems (SCOPES), St. Goar, Germany, June 2013

- C11. Weiwei Chen, Rainer Doemer, "Optimized Out-of-Order Parallel Discrete Event Simulation Using Predictions", in Proceedings of the Design, Automation and Test in Europe Conference (DATE), pp.3-8, Grenoble, France, March 2013

- C10. Weiwei Chen, Che-Wei Chang, Xu Han, Rainer Doemer, "Eliminating Race Conditions in System-Level Models by using Parallel Simulation Infrastructure", in Proceedings of the IEEE International High Level Design Validation and Test Workshop (HLDVT), pp.118-123, Huntington Beach, USA, November 2012

- C9. Weiwei Chen, Xu Han, Rainer Doemer, "Out-of-order Parallel Simulation for ESL design", in Proceedings of the Design, Automation and Test in Europe Conference (DATE), pp.141-146, Dresden, Germany, March 2012

- C8. Rainer Doemer, Weiwei Chen, Xu Han, "Parallel Discrete Event Simulation of Transaction Level Models", invited paper, in Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASP-DAC), pp.227-231, Sydney, Australia, January 2012

- C7. Weiwei Chen, Rainer Doemer, "An Optimizing Compiler for Out-of-Order Parallel ESL Simulation Exploiting Instance Isolation", in Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASP-DAC), pp.461-466, Sydney, Australia, January 2012

- C6. Rainer Doemer, Weiwei Chen, Xu Han, Andreas Gerstlauer, "Multi-Core Parallel Simulation of System-Level Description Languages", invited paper, in Proceedings of

the 16th Asia and South Pacific Design Automation Conference (ASP-DAC), pp.311-316, Yokohama, Japan, January 2011

- C5. Weiwei Chen, Xu Han, Rainer Doemer, "ESL Design and Multi-Core Validation using the System-on-Chip Environment", in Proceedings of the 15th IEEE International High Level Design Validation and Test Workshop (HLDVT), pp.142-147, Anaheim, USA, June 2010

- C4. Weiwei Chen, Rainer Doemer, "A Fast Heuristic Scheduling Algorithm for Periodic ConcurrenC Models", in Proceedings of the 15th Asia and South Pacific Design Automation Conference (ASP-DAC), pp.161-166, Taipei, Taiwan, January 2010

- C3. Rongrong Zhong, Yongxin Zhu, Weiwei Chen, Mingliang Lin, Weng Fai Wong, "An Inter-core Communication Enabled Multi-core Simulator Based on SimpleScalar", in Proceedings of the 21st International Conference on Advanced Information Networking and Applications Workshops (AINAW), pp.758-763, Niagara Falls, Canada, April 2007

- C2. Guoyong Shi, Weiwei Chen, C.-J. Richard Shi, "A Graph Reduction Approach to Symbolic Circuit Analysis", in Proceedings of the 12th Asia and South Pacific Design Automation Conference (ASP-DAC), pp.197-202, Yokohama, Japan, January 2007

- **C1. Weiwei Chen**, Guoyong Shi, "Implementation of a Symbolic Circuit Simulator for Topological Network Analysis", in Proceedings of the IEEE Asia Pacific Conference on Circuit and System (APCCAS), pp.1368-1372, Singapore, December 2006

#### **Book Chapters**

- B2. Weiwei Chen, Rainer Doemer, "ConcurrenC: A New Approach towards Effective Abstraction of C-based SLDLs", Analysis, Architectures and Modeling of Embedded Systems (ed. A. Rettberg, M. Zanella, M. Amann, M. Keckeisen, F. Rammig), Springer, 2009, ISBN 978-3-642-04283-6

- B1. Weiwei Chen, Guoyong Shi, "Symbolic Analysis of Analog Integrated Circuits", Embedded Systems and Materials Research for Advanced Applications, the 1st Chinese-German Summer School in Shanghai, September, 2006, ISBN-10: 3-00-019576-9 / ISBN-13: 978-3-00-019576-1

#### **Technical Reports**

- TR5. Xu Han, Weiwei Chen, Rainer Doemer, "A Parallel Transaction-Level Model of H.264 Video Decoder", TR-11-03, Center for Embedded Computer Systems, UC Irvine, June 2011

- TR4. Weiwei Chen, Rainer Doemer, "A Distributed Parallel Simulator for Transaction Level Models with Relaxed Timing", TR-11-02, Center for Embedded Computer Systems, UC Irvine, May 2011

- **TR3.** Weiwei Chen, Rainer Doemerr, "ConcurrenC: A Novel Model of Computation for Effective Abstraction of C-based SLDLs", *TR-09-07*, Center for Embedded Computer

System, UC Irvine, May 2009

- TR2. Weiwei Chen, Siwen Sun, Bin Zhang, Rainer Doemer, "System Level Modeling of a H.264 Decoder", TR-08-10, Center for Embedded Computer System, UC Irvine, August 2008

- **TR1. Weiwei Chen**, Rainer Doemer, "System Specification of a DES Cipher Chip", *TR-08-01*, Center for Embedded Computer System, UC Irvine, January 2008

#### **Poster Presentations**

- P3. Weiwei Chen, Rainer Doemer, "Out-of-order Parallel Simulation for Electronic System-Level Design", in the EDAA/ACM SIGDA PhD Forum at the Design, Automation and Test in Europe Conference (DATE), Grenoble, France, March 2013

- P2. Weiwei Chen, Rainer Doemer, "Out-of-order Parallel Discrete Event Simulation for ESL Design", Graduate Student Poster Presentation, Faculty Retreat, Department of Electrical Engineering and Computer Science, UC Irvine, September 2012

- P1. Weiwei Chen, Rainer Doemer, "Parallel Discrete Event Simulation for ESL Design", in SIGDA Ph.D. Forum at the Design Automation Conference (DAC), San Francisco, USA, June 2012

#### HONORS AND AWARDS

- Pedagogical Fellowship, UC Irvine, 2012-13 academic year

- Henry Samueli Endowed Fellowship, The Henry Samueli School of Engineering, UC Irvine, 2007

- Travel grants, Design Automation Conference (DAC) 2012 and Asia and South Pacific Design Automation Conference (ASP-DAC) 2010

- Young Student Support Award, Design Automation Conference (DAC), Anaheim, CA, 2010

- Excellent Teaching Assistant Award, School of Microelectronics, SJTU, 2006

- National Scholarship for Academic Excellence, China, 2006

- Morgan Stanley Scholarship, Infineon Scholarship, SJTU, 2006

- Guanghua Scholarship, SJTU, 2005

- First-round and second-round Exceptional Undergraduate Student, SJTU, 2001, 2003

- People's Scholarship for Academic Excellence, SJTU, 2000 2003

- Pan Wen-yuan Foundation Scholarship, China, 2001

- Shuping Scholarship, 7 years since the 9th grade

### ABSTRACT OF THE DISSERTATION

### **Out-of-order Parallel Discrete Event Simulation**

for Electronic System-Level Design

By

Weiwei Chen

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine, 2013

#### Professor Rainer Doemer, Chair

The large size and complexity of the modern embedded systems pose great challenges to design and validation. At the so called electronic system level (ESL), designers start with a specification model of the system and follow a systematic top-down design approach to refine the model to lower abstraction levels step-by-step by adding implementation details. ESL models are usually written in C-based System-level Description Languages (SLDLs), and contain the essential features, such as clear structure and hierarchy, separate computation and communication, and explicit parallelism. The validation of ESL models typically relies on simulation. Fast yet accurate simulation is highly desirable for efficient and effective system design.

In this dissertation, we present *out-of-order parallel discrete event simulation (OoO PDES)*, a novel approach for efficient validation of system-level designs by exploiting the parallel capabilities of todays multi-core PCs for system level description languages. OoO PDES breaks the global simulation-cycle barrier of traditional DE simulation by localizing the simulation time into each thread, carefully delivering notified events, and handling a dynamic management of simulation sets. Potential conflicts caused by parallel accesses to shared variables and out-of-order thread scheduling are prevented by an advanced predictive static model analyzer in the compiler. As such, OoO PDES allows the simulator to effectively exploit the parallel processing capability of the multi-core system to achieve fast speed simulation without loss of simulation and timing accuracy.

We perform simulation experiments on both highly parallel benchmark examples and realworld embedded applications, including a JPEG image encoder, an edge detector, a MP3 audio decoder, a H.264 video decoder, and a H.264 video encoder. Experimental results show that our approach can achieve significant simulation speedup on multi-core simulation hosts with negligible compilation cost.

Based on our parallel simulation infrastructure, we then propose a tool flow for dynamic race condition detection to increase the observability for parallel ESL model development. This helps the designer to quickly narrow down the debugging targets in faulty ESL models with parallelism. This approach helps to reveal a number of risky race conditions in our in- house embedded multi-media application models and enabled us to safely eliminate these hazards. Our experimental results also show very little overhead for race condition diagnosis during compilation and simulation.

Overall, our work provides an advanced parallel simulation infrastructure for efficient and effective system-level model validation and development. It helps embedded system designers to build better products in shorter time.

## **1** Introduction

Embedded computer systems are special purpose information systems that are embedded in larger systems to provide operations without human intervention [1]. They are pervasive and ubiquitous in our modern society with a wide application domain, including automotive and avionic systems, electronic medical equipments, telecommunication devices, industrial automation, energy efficient smart facilities, mobile and consumer electronics, and others. Embedded computer system is one of the most popular computational systems in our current information era [1]. In 2002, more than 98 percent of all the microprocessors produced worldwide are used for embedded computer systems [2]. The global market for embedded technologies is also tremendously big and increasing rapidly. Ebert et al. stated in [3] that "the worldwide market for embedded systems is around 160 billion euros, with an annual growth of 9 percent". We can expect that more and more products we use in our daily life will be based on embedded computer systems in the future.

Following the "Dortmund" definition of embedded computer systems in [1], both hardware and software are critical for embedded system design.

The hardware for embedded systems is usually less standard than general purpose computer systems [1]. Embedded computer systems often consist of a large set of input devices, heterogeneous processors, and customized memory components. A huge range of input devices are used in embedded systems to collect the information from the user and the external environment. To name a few, *sensor* devices detect the physical qualities of the external environment, such as

temperature, humidity, velocity, acceleration, brightness, etc; analog-to-digital converters discretize continuous physical quantities into values in the discrete domain; and sample-and-hold circuits convert continuous time into discrete signals [1]. The input information is then sent to the processing units in the system for computation and decision making to generate system intelligence and automation.

Modern embedded system platforms usually compose various types of processing elements into the system, including general-purpose CPUs, application-specific instruction-set processors (ASIPs), digital signal processors (DSPs), dedicated hardware accelerators implemented as application-specific integrated circuits (ASICs), and intellectual property (IP) components. Moreover, embedded systems usually use customized memory hierarchies due to its tight performance, power, and size constraints. Since embedded systems are usually designed to a specific target application, the memory system is allowed to be tailored accordingly by using customized memory components and architectures, such as caches with different configurations and management strategies, scratch-pad memory, streaming buffers, DRAM, and multiple SRAMs [4]. As a whole system, the hardware components are connected in a network and communicate with each other via different communication protocols, such as time triggered protocol (TTP/C) [5] for safety-critical systems, controller area network (CAN) for automation systems [6], AR-INC 629 for civil aircraft databuses [7], FlexRay for automotive communication network [8], Advanced Micro-controller Bus Architecture (AMBA) for system-on-chip design [9], and Time-Triggered Ethernet (TTEthernet) for predictable and deterministic real-time communication [10]. With the advance in semiconductor technology, many embedded systems can now be integrated entirely onto a single die which result in complex System-on-Chip (SoC) architectures [11, 12].

The software of modern embedded computer systems is often tightly coupled with the underlying heterogeneous hardware platform and external physical processes [13]. Timeliness, concurrency, and constraints on the available resources are several most important features for embedded software. In order to interact with the physical world, embedded software usually needs to process and response in real-time. Correctness is not only depends on the functionality but also on the time frame. With multiple components integrated in one system and the external physical processes which are fundamentally running in parallel, embedded software also needs to handle concurrency of the whole system, such as monitoring multiple sensors to get inputs and processing information on different computational components at the same time. Furthermore, embedded software also need to take resource constraints into consideration in order to meet the product requirement. Resource constraints include power consumption, memory size, thermal sensitivities, available computing capabilities, and so on.

The general embedded software stack usually consists of multiple components including application software, middleware or adapter layer, operating system or real-time operating system (RTOS), device drivers, boot firmware, communication protocol stacks, and hardware abstraction layer [11]. Compared to the traditionally constraint embedded applications, large application software, which is written in complex programming languages such as C/C++ and Java, is commonly used in today's embedded systems. The programming flexibility introduced by the high-level programming languages results in higher software productivity as well as product innovation. Embedded operating systems enable and manage the concurrency, process scheduling, and resource sharing in the whole system. A real-time operating system (RTOS), which is widely used in nowadays' embedded systems, facilitates the construction of the systems under certain real-time constraints in line with the timeliness requirement of the design. The rest of the software components are often categorized as Hardware-depend Software (HdS) due to the fact that they interact closely with the underlying hardware platform to provide configurability and flexibility. As was defined in [11] by Ecker et al., HdS is specifically built for a particular hardware block, implements a system's functionality together with the hardware, and provides the application software with an interface to easily access the hardware features.

### 1.1 System-level Design

The large size, complexity and heterogeneity of today's embedded systems imposes both theoretical and engineering challenges on system modeling, validation, debugging, synthesis, and design space exploration, in order to build up a satisfying system within a short time-to-market design period.

Fig. 1.1 shows the design challenge statistically . Moore's law predicts that the capability of hardware technology doubles every eighteen months, whereas the hardware design productivity in the past few years is estimated to increase at 1.6x over the same period of time. On the other hand, since the hardware productivity improved over he last several years by putting multiple cores on to a single chip, the additional software required for hardware (HdS) doubles over every ten months. However, the productivity especially for HdS is far behind which is doubling only every five years. There are growing gaps between the technology capabilities and the real hardware and software productivities over the years. This tells that System-on-Chip design productivity cannot follow the pace of the nano-electronics technology development which is characterized by Moore's Law. Hence, design methodologies become a popular research topic to tackle those design challenges of embedded systems in the recent decade.

System-level Design is a promising solution to improve the design productivity [14]. The 2004 edition of the International Technology Roadmap for Semiconductors (ITRS) places systemlevel as "a level above RTL including both hardware and software design" [15]. Here, "Hardware" (HW) consists processing elements, buses, hardwired circuits and reconfigurable cells. It implements the circuit element in the system. "Software" (SW) includes embedded codes in programming languages, configuration data, etc. It defines the functionality that is performed on the underlying hardware. ITRS also states that there are two independent degrees of design freedom in system-level, behavior which defines the system functionality and architecture which defines the system platform [16].

Figure 1.1: Hardware and software design gaps versus time (source [11])

System-level design is a holistic approach to address the design challenges that are brought by the radical increase in the complexity of both embedded hardware and software. At the system-level, the designer treats the intended system as a whole entity and focuses on the functional specification or algorithm which is independent from the hardware platform or software implementations. With a complete picture of the entire system, the hardware and software can be designed jointly (co-design) at the same time. It also makes global system optimization possible and more efficient. Moreover, system-level design can often rely on guided automatic approaches to add more details to get the final implementation. For instance, the designer can map a functional module in the system-level model to a processor and run it as regular software program or synthesize the module into a specific hardware unit by using high-level synthesis tools. With the help of designer guided refinement tools, system-level design can therefore increase productivity dramatically.

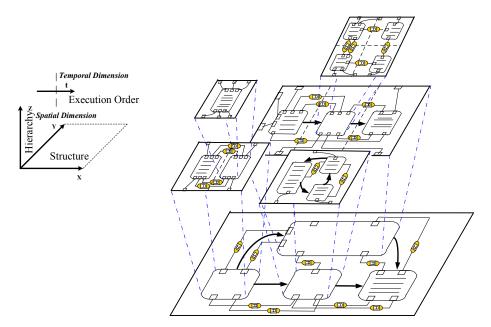

#### 1.1.1 Levels of Abstraction

Abstraction is a natural process in system-level design which allows the designers to handle the complexity of the entire system without the distraction of the low-level implementation details. According to Doemer in [17], "a well-known solution for dealing with complexity is to exploit hierarchy and to move to higher levels of abstraction".

Figure 1.2: Levels of abstraction in SoC design (source [18])

As shown in Fig. 1.2, raising the level of abstraction results in fewer numbers of components to handle. In particular, an implemented system may contain tens of millions of transistors. Gate-level abstracts the transistor-level by using logic gates and flip-flops which are composed of specific sets of transistors. Then, register-transfer level (RTL) typically reduces the number of components to several thousands. This may further be represented by a couple of processor elements which construct one system. The reducing number of components in higher abstraction levels helps to maintain a system-level overview in a simple way. Ideally, the designer can start at the pure functional level and gradually refine the design to lower abstraction levels with more implementation details with the help of system-level design tools.

The idea of abstraction levels is realized by using *models* in the design process. *Models* are the abstraction of the reality. They are built for different abstraction levels to reflect the features that are critical to the corresponding level.

The advantage of having different levels of abstraction allows the designer to only focus on the critical features of a certain abstraction level and ignore the unneeded lower-level details. However, this cannot be achieved without cost. Hiding more implementation details can in turn cause the loss of *accuracy*, such as timing, number of pins and interrupts. It is a trade-off between more focused view of design and accuracy for timing and physical design metrics.

### 1.1.2 The Y-Chart

Gajski's Y-Chart [19] is a conceptual framework to coordinate the abstraction levels in three design domains (the axes), i.e. behavior (functionality), structure (architecture), and physical layout (implementation). The **behavioral** domain defines the functionality of the system, i.e. the output in terms of the input over time. The **structural** domain describes the architecture of the hardware platform including processing elements (PEs) and communication elements (CEs). The **physical** domain specifies the implementation details of the structure, such as the size and position of the components, the printed circuit board, and the port connection between components.

Figure 1.3: System-level design in the Y-Chart (source [17])

The level of abstractions are identified by the dashed concentric circles, increasing from tran-

sistor level to system-level in the *Y*-Chart. They are orthogonal to the design domains which are instead represented as axes.

Design flows are illustrated as paths in the *Y*-*Chart*. For instance, the behavior of the design can first be mapped to the structure description at the system-level, and then be refined to lower abstraction levels along the *structure* axis to a final implementation. Another design flow may start from the system-level function description in programming, refine the design to behavioral processor-level first with controllers and datapaths, and follow the structural synthesis flow down to physical layouts.

The heart of system-level design is the platform mapping from the behavior onto the structure [20]. This is illustrated as the arrow on the outmost circle in Fig. 1.3.

#### 1.1.3 System-level Design Methodologies

Computer Aided Design (CAD) tools are introduced to automate the design process which is too complex for the designers to do manually due to the advances in technologies. CAD tools usually follow sets of stringent rules and use dedicated component libraries to make the design process more efficient and manageable. The aggregation of models, components, guidelines and tools is called design *methodology* [13]. Design methodologies evolve with technologies, applications, as well as design group foci.

The **bottom-up** design methodology starts from the lowest abstraction level, and generates libraries for the next higher level by each level (Fig. 1.4a). For example, the *transistor* level generates the library for the logic gates and flip-flops in the *logic* level with N-type and P-type transistors. Floorplan and layout are needed for all the levels by using this approach. The advantage of this methodology is that each abstraction level has its own library with accurate metric estimation. The disadvantage is that optimal library for a specific design is difficult to achieve since parameters need to be tuned for all the library components at each level. The **top-down** design methodology starts with the highest abstraction level to convert the functional description of the system into a component netlist at each abstraction level (Fig. 1.4b). Component functions are decomposed with further details step by step down to the lower abstraction levels. System layout is only needed at the lowest transistor level. The advantage of this approach is that high-level customization is relatively easy without implementation details, and only a specific set of transistors and one layout is needed for the whole process. The disadvantage is that it is difficult to get the accurate performance metrics at the high abstraction levels without the layout information.

The meet-in-the-middle design methodology is a combination of the *bottom-up* and *top-down* approaches. In this flow, the three design aspects, i.e. behavior, structure, and physical, meet at different abstraction levels. For example, as shown in Fig. 1.4c, the functional specification is synthesized down into processor components; whereas RTL components from the library construct the processor components up with a system layout. The RTL components from the library are generated through a bottom-up process with their own structure and layout. Therefore, the three design domains meet at the *processor* level. Physical design and layout are required for three times in this flow: first for the standard cells, second for RTL components, and last for the system.

Fig. 1.4d shows an alternative flow where the three domains meet at the *RTL* level. In this flow, the system behavior description is mapped onto a certain architecture with PEs and CEs; then the behavior models of the PEs and CEs are synthesized into RTL components; whereas the RTL components are synthesized with logic components. The system layout can be generated by combining the logic components through floor planing and routing, since logic components has already have their own layout with standard cells. This flow requires physical design and layout for two times, one for the standard cells, and the other for the system.

The advantage for the *meet-in-the-middle* design methodology is that it can provide more accurate metrics at high abstraction levels than the *top-down* approach; and requires less layout and libraries than the *bottom-up* one. The disadvantage is that while the metrics accuracy is increasing, the easiness for optimization decreases; and more than one layout and libraries are still required.

Other design methodologies, such as *platform methodology*, *system methodology*, and *FPGA methodology* that have been discussed in [13] are more product oriented. These methodologies are commonly used in companies and design groups for building products with their own platform components.

#### 1.1.4 Electronic System-Level Design Process

In this dissertation, we will focus on the so called *Electronic System-Level (ESL) Design* which aims at a systematic *top-down* design methodology to successively transform a given high-level system description into a detailed implementation. There are three backbone aspects for ESL design: *specification, validation, and refinement*.

The starting point for ESL design is the *specification* of the system. The specification is a pure functional model in which the algorithm of the intended design is captured and encapsulated in computation modules, i.e. *behaviors*, and the communication between the behaviors is described through abstract communication modules, i.e. *channels*. The specification model should be *complete* with all features that are essential to system-level design, but also *abstract* without unnecessary implementation details such as timing and interrupts. It also needs to be *executable* so that the designer can verify the model with the design expectations. Typically, specification models are written in programming languages and can be compiled for execution. As the initial formal description of the system, the specification model serves as the golden reference to the other models that will be refined at lower abstraction levels.

Once having the system specification, *validation* is needed to check its correctness. Typically, ESL design models are validated through *simulation*. *Simulation* is a dynamic process to validate the functionality and the metrics of the model in terms of the execution output for given input vectors. The speed of simulation on the simulation host is often slower than the execution speed of the real implemented system. Moreover, since simulation is driven by input vectors, unless exhaustive simulation with all the possible input vectors are performed, simulation based validation cannot cover all the cases.

*Validation* can also be performed through static model analysis, which is often called *verification*. Verification usually refers to the approach of using formal methods to prove certain characteristics of the model. In contrast to *simulation*, *verification* can yield 100% coverage on

all the possible cases. However, the complexity of verification can grow exponential while the size of the model grows. Thus, it is only possible to verify small designs.

**Refinement** is the process of adding more implementation details into the model, including architecture mapping, scheduling strategies, network connections, communication protocols, and so on. In ESL design, *refinement* is often guided by the designers' decisions and performed automatically with the help of CAD tools.

A sequence of ELS model refinement at different abstraction levels is described in the following paragraphs.

After building and validating the *specification* model, the architecture of the system will be determined with respect to the number and types of processing elements, memory components, and their connectivities. PEs include programmable and nonprogrammable component. Programmable PEs are generic embedded processors like ARM [21], MIPS [22], LEON [23], ColdFire [24], Blackfin [25], and MicroBlaze [26] processors, as well as digital signal processors (DSPs). Non-programmable elements are customized hardware accelerators or non-instruction set computer components [27]. In the *architecture mapping* step, the designer first decide the HW/SW partition among the functional modules. Performance-critical modules are usually implemented as dedicated HW units and the rest of them are compiled and executed as SW on programmable PEs. It is a trade-off between high-speed high-cost HW implementation and low-cost less efficient SW execution. Also, the parameters for the PEs, including clock frequency, memory size, width of the address bus, are adjusted in this step for specific applications.

The second refinement step is to decide the *scheduling strategies* on programmable processing elements. Multiple behaviors can be mapped onto a single host PE and run as software. Proper scheduling mechanism is needed to decide the execution order of the tasks on the PEs since the computational resources available can be fewer than the number of mapped behaviors. Scheduling can be static or dynamic. In case of static scheduling, the constraints such as behavior workload and dependencies should be known by analyzing the model beforehand and will not change during execution time. In case of dynamic scheduling, operating system is often used to map behaviors onto tasks and manage them under priority-based or round-robin style scheduling schemes.

The third refinement step is *network* allocation. This step determines the connectivities among the PEs in the system. For example, there is a generic processor and several HW accelerators in the system. They communicate with each other via the CPU bus of the processor. Thus, the processor will be specified as the master of the bus while the HW accelerators as the slaves. Port interfaces also need to be allocated for each PEs so as to properly connect to the bus.

The next refinement is for *communication*. The communication of the system is described and encapsulated in the *channel* modules in the *specification* model, and is mapped to virtual buses in the *architecture* model. In this step, the virtual buses are replaced with actual ones for specific protocols. The communication protocols are then implemented by inlining the communication code into the PEs, i.e. bus drivers in the operating system. If two buses with different protocols need to exchange data, transducers need to be inserted to bridge the gap between them.

The system refinement process is completed with the *backend* tasks. The goal of the *backend* is to create a final optimized *implementation* for each component in the design. The customized hardware units and transducers need to be synthesized into RTL netlists written in *VHDL* or *Verilog*. The software code needs to be generated, either in C or assembly, and compiled for the corresponding processors. The *implementation* model is at the lowest abstraction level and contains all the information, including functionality, structure, communication and timing with respect to the actual implementation. It is bus-cycle accurate for the communication and clock-cycle accurate for the computation on the processors.

Moreover, in ESL design, *estimation* techniques are often used to measure the metrics of the system models, such as timing, power consumption, workload, etc. Similar to *validation*, *estimation* can be performed statically by model analysis, or dynamically by simulation and profiling. There is also a trade-off between the estimation accuracy and speed. Estimation is faster but

less accurate on the models at higher abstraction levels than on the ones at lower abstraction levels. It should be emphasized that *validation* and *estimation* needs to be performed at the end of each aforementioned refinement step to ensure that the refined model still meets the design requirements.

### 1.2 Validation and Simulation

In system-level design, abstract models are built for better understanding on the system, and refinement and optimization for the final implementation. *Simulation* is critical in the design process for both *validation* and *estimation* which check the models according to the intended design constraints.

#### 1.2.1 Language Support for System-level Design

System-level models need to be executable for efficient *validation* and *estimation*. They are typically described in programming languages. Programming languages are designed for the convenience of making the computer systems behave according to human beings' thoughts. Various languages are proposed to improve the work of system design. We will review some of those design languages for embedded system in this section.

#### Hardware Description Languages (HDLs)

The goal of a hardware description language is to concisely specify the connected logic gates. It is originally targeted at simulation and a mixture of structural and procedural modeling.

**VHDL** [28, 29] and **Verilog** [30, 31] are the most popular languages for hardware modeling and description. Both of them have discrete event semantics and ignore the idle portions of the system for efficient simulation. They describe the hardware system in hierarchy by partitioning the

system into functional blocks which could be primitives, other blocks, or concurrent processes. HDLs often describe the system as finite-state machines (FSMs), datapath and combinatorial logic. The described system could be simulated to verify its correctness and be synthesized into real hardware circuits.

HDLs support the lower level description of an embedded system. However, they could not ignore those implementation details like pins, wires, clock cycles. Thus, it is too complicated to describe a whole system and the simulation will take a very long time.

#### Software Languages

Software languages describe sequences of instructions for a processor to execute. Most of them use sequences of imperative instructions which communicate through the *memory*, an array of numbers that hold their values until changed.

Machine instructions are typically limited to do simple work, say, adding two numbers. Therefore, high-level software languages aim to specify many instructions concisely and intuitively. The *C* programming language [32] provides expressions, control-flow constructs, such as conditionals, loops and recursive functions. The C++ programming language [33] adds classes to build new data types, templates for polymorphic code, exceptions for error handling, and a standard library for common data structures. The Java programming language [34] provides automatic garbage collection, threads, and monitors for synchronization. It is quite suitable for writing applications on different embedded system platforms [35].

However, software language does not have the ability to explicitly describe hardware behaviors like signals, events, and timing.

#### System-level Description Languages (SLDLs)

System-level description languages (SLDLs), such as **Spec**C [36, 18, 37], **System**C [38, 39, 40] and **SystemVerilog** [41], are available for modeling and describing an embedded system at different abstraction levels.

SpecC is a system-level description language as well as a system level design methodology. It is based on the C language and a true superset of ANSI-C [42]. In addition to the constructs in ANSI-C, SpecC has the a minimal set of extensions to support the requirements of system-level modeling, such as structural and behavioral hierarchy, concurrency, communication, synchronization, timing, exception handling, and explicit state transitions.

SpecC uses the same discrete-event simulation semantics as *Verilog* and *VHDL* [43]. It is executable and synthesizable [18].

System C is a C++ library which facilitates both system and RTL modeling. It builds systems from *Verilog-* and *VHDL*-like modules, each of which has a collection of I/O ports, instances of other modules or processes written in C++. SystemC is the de-facto language for system-level design in industry.

SystemC and SpecC are conceptually equivalent. However, the two languages have some distinctions in semantics and implementation details. We will discuss the SpecC and SystemC SLDLs in more detail in Section 1.5.

System Verilog is the industry's first unified hardware description and verification language (HDVL) standard. It is a major extension of the Verilog language. System Verilog supports modeling and verification at the "transaction" level of abstraction by the support of assertion-based verification (ABV). It also provides a set of extensions to address advanced design requirements, like modeling interfaces, removing os restrictions on module port connections, allowing any data type on each side of the port, etc. Object-oriented techniques are new features for modeling

hardware and testbenches.

#### 1.2.2 System Simulation Approaches

Typically, system-level design validation is based on simulation. The functional behavior of the model is defined by the software semantics of the underlying C/C++ language, and the synchronization and communication is defined by the execution constructs for the system-level or hardware description language.

Simulation is an approach to perform experiments using the computer implementation of a model. There are three types of computer-based simulation in classical thinking: *discrete event*, *continuous*, and *MonteCarlo*. Nance articulated the definitions of these simulations in [44] as follows:

"Discrete event simulation utilizes a mathematical/logical model of a physical system that portrays state changes at precise points in simulated time. Both the nature of the state change and the time at which the change occurs mandate precise description.

Continuous simulation uses equational models, often of physical systems, which do not portray precise time and state relationships that result in discontinuities [...]. Examples of such systems are found in ecological modeling, ballistic reentry, or large scale economic models.

Monte Carlo simulation [...] utilizes models of uncertainty where representation of time is unnecessary [...]. Typical of Monte Carlo simulation is the approximation of a definite integral by circumscribing the region with a known geometric shape, then generating random points to estimate the area of the region through the proportion of points falling within the region boundaries."

In short, the notion of time is emphasized and the simulation states evolve only at discrete time