#### Phase Change Memory

#### Chief Technology Office Carnegie Mellon, Sept 23rd, 2009

Page 1 Copyright © 2009 Numonyx B.V.

## Agenda

- Background / Why PCM

- What is PCM and How it Works

- Technology Characteristics and Trends

- Application: Storage Input / Output Acceleration

- Application: Directly Addressable NVRAM

## Agenda

- Background / Why PCM

- What is PCM and How it Works

- Technology Characteristics and Trends

- Application: Directly Addressable NVRAM

- Application: Storage Input / Output Acceleration

#### Phase Change Memory

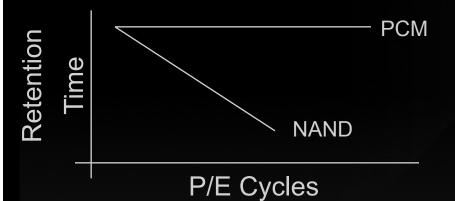

"New Memory" Motivation (Recognized ~1999) :

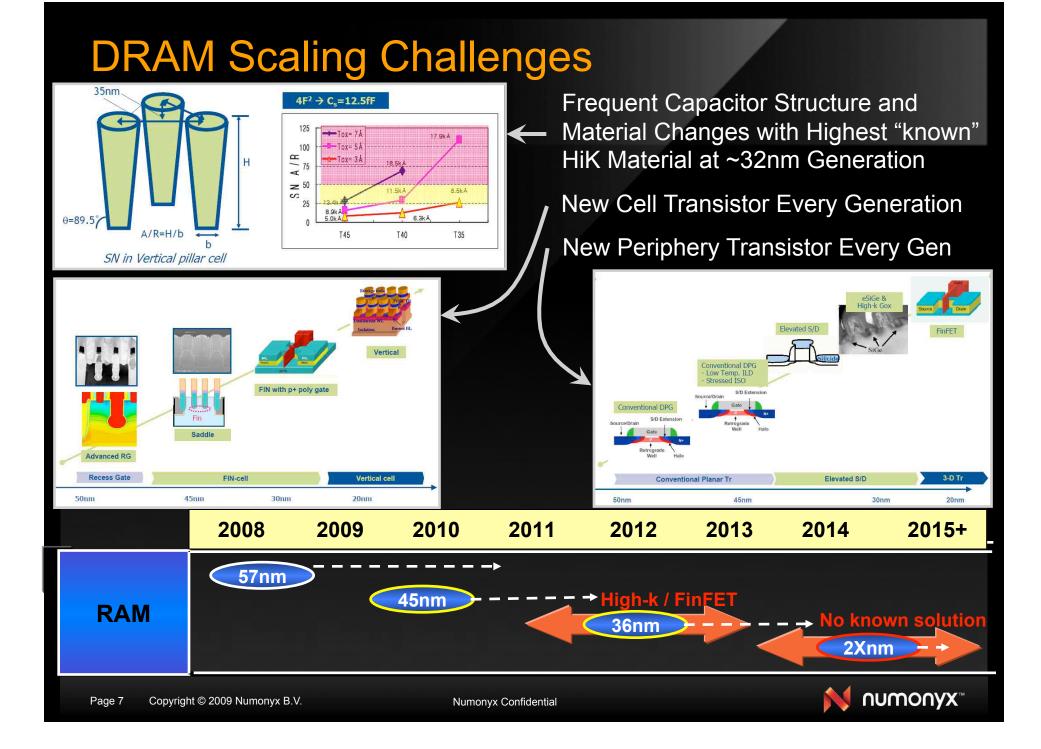

- Current NVM (and DRAM) are becoming Electrostatics Limited

- MOS Transistor Based Cell; Charge Storage Memory Effect

- Starting to Encounter Physical Scaling Limitations

- Manifesting First as Degradation in Reliability (Endurance/Retention)

#### Realization:

- Next Generation NVM will Exploit New Storage Physics

- Significant Innovation Will take Time (History says ~10yr "Gestation")

#### • Response:

- Phase Change Memory Identified as the Best Candidate

- Research Efforts Validated Assumptions and Initiated Development

- Phase Change Memory Moving into Production Today

#### • We Believe PCM Features Enable New Usage Models

#### **NOR Scaling Challenges** 10\_S 10 D T<sub>t</sub> floating-gate traps tunnel oxide Silicon **NOR Reliability:** Write / Erase Tox NOR (ETOX & NROM) Scaling: traps leading to TAT or de-trapping 3.2ev required to surmount Si-SiO2 barrier $\rightarrow$ Limits Cell Gate of trapped oxide electrons Length Scaling 2008 2009 2010 2011 2012 2013 2014 2015 +**65nm** NOR --- > ROI given channel length limits 45nm 32nm numonyx™ Copyright © 2008 Numonyx B.V. Numonyx Confidential

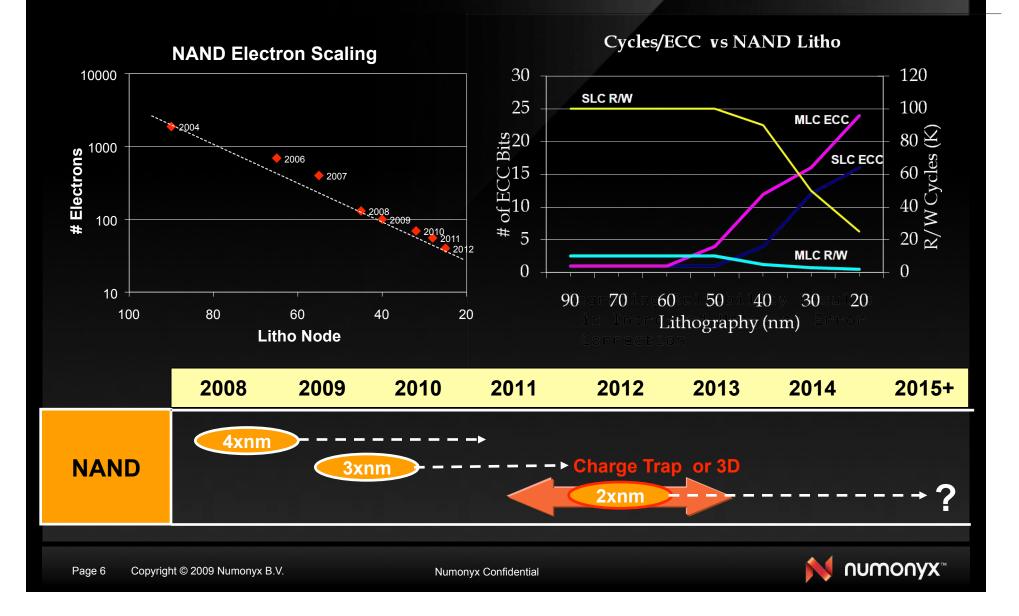

#### **NAND Scaling Challenges**

#### **Theoretical Chip Cost Factors**

| Silicon Cost Component       |                             | SLC PCM | DRAM | SLC NAND |

|------------------------------|-----------------------------|---------|------|----------|

| Die Size                     | Cell Size (F <sup>2</sup> ) | 5.5     | 6.0  | 5.0      |

|                              | 4G Prod Example             | 1.0x    | 1.2x | 1.0x     |

| Wafer<br>Complexity          | Total Process<br>Mask Count | ~35     | ~34  | 30       |

|                              | 300mm<br>cost structure     | 1.2x    | 1.2x | 1.0x     |

| Theoretical Die Cost Summary |                             | 1.2x    | 1.4x | 1.0x     |

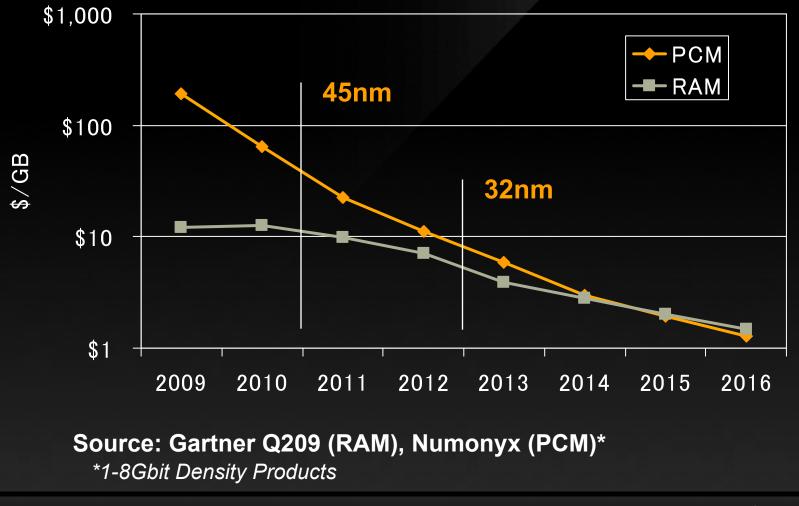

- PCM will be cheaper than DRAM at lithography parity

- PCM scales to lower densities better than NAND

- 300mm infrastructure required to get lowest cost

- PCM attributes can also save cost at system level

## High Density PCM vs RAM Comparisons

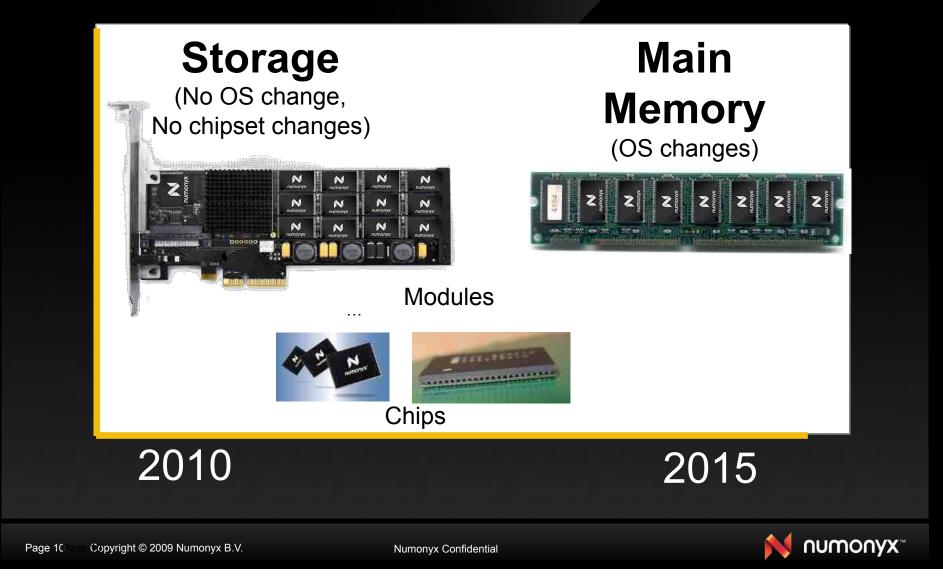

#### Landscape: Where do we go first?

Trying to figure out who will pay what \$/GB

## Agenda

- Background / Why PCM

- What is PCM and How it Works

- Technology Characteristics and Trends

- Application: Directly Addressable NVRAM

- Application: Storage Input / Output Acceleration

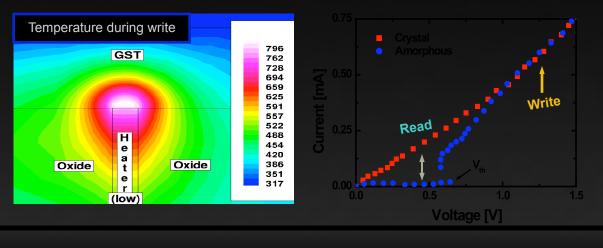

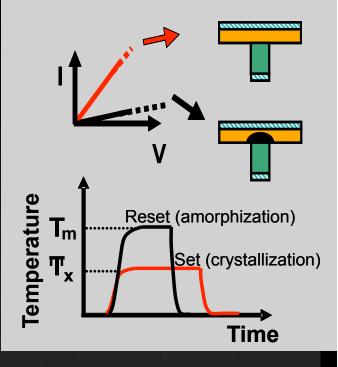

#### Phase Change Memory Mechanisms

#### Storage

- GST: Germanium-Antimony-Tellurium Chalcogenide glass

- Cell states varying from amorphous (high resistance) to crystalline (low resistance) states

- Read Operation

- Measure resistance of the GST

- Write Operation

- Heat GST via current flow (Joule effect)

- Time at critical temperature determines cell state

#### Amorphous

**NUMONYX**<sup>™</sup>

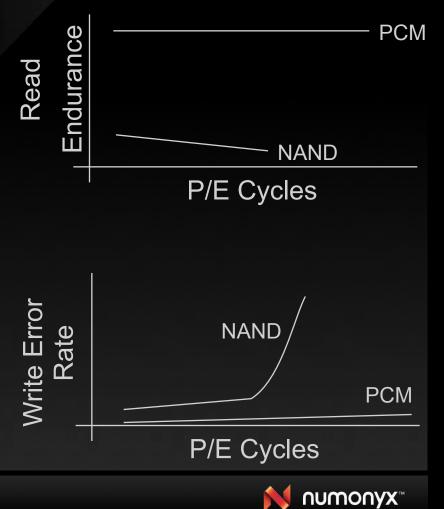

# Summary of Key PCM Reliability Metrics

Result:

Greatly simplified management No software overhead for some apps Post-stress shelf-life problem solved Endurance can be increased significantly through management of bit errors Data is stable once successfully written

No issue with Read disturb

## 128Mb Reliability Data

## Use Condition Sensitivities by Technology

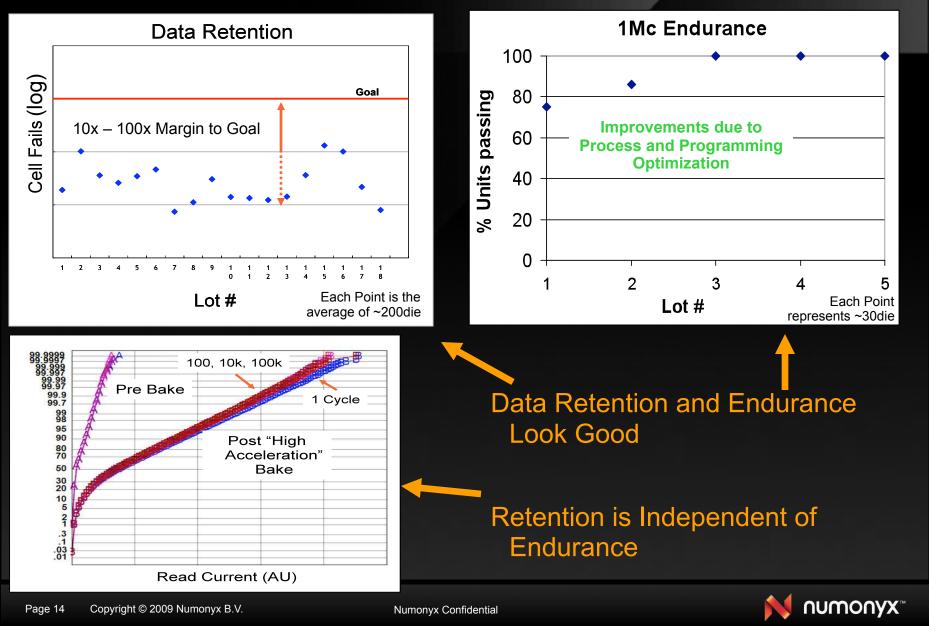

|                                                | NAND                                  | NOR/NROM                               | PCM                |

|------------------------------------------------|---------------------------------------|----------------------------------------|--------------------|

| Program / Erase Cycles                         | SBC: 1e5<br>MLC: 1e4<br>Trending Down | 1e5<br>Long term downward trend        | 1e6<br>Trending up |

| Write Amplification                            | Very Important for data applications  | Important                              | N/A                |

| Cycling Temperature                            | Important                             | Important                              | Unimportant < 85C  |

| Retention Temperature                          | Important                             | Important                              | Unimportant < 85C  |

| Reads between cycles                           | SBC: 1e6<br>MLC: 1e5<br>Trending down | >1e13 / page<br>Trending down slightly | Infinite           |

| Partial Page Program Cycles 1-4, trending to 1 |                                       | N/A                                    | N/A                |

| Tolerable Bad Block Rate                       | 2%                                    | N/A                                    | N/A                |

| System ECC Capability Important                |                                       | N/A                                    | N/A                |

| Solder Temperature Not Important               |                                       | Not Important                          | Important          |

#### **Reliability Concerns for Large Arrays**

#### • Persistent Errors

- DRAM and SRAM susceptible to silent data corruption of memory cells caused by radiation effects

- PCM storage element immune to these radiation effects

- With a thermally activated storage mechanism, PCM cells will tend to change state at high temperatures. Techniques similar to "Scrubbing" used in high-end DRAM applications can serve to extend the PCM operating range.

#### Non-Persistent Errors

- Logic and interface errors expected to be common mode between DRAM and PCM

- Use of ECC to fix these errors, however, is straightforward

- PCM does not require refresh of idle banks

- DRAM refresh rates expected to increase with scaling

#### PCM may prove to be much more manageable at very large densities

numonyx

## Agenda

- Background / Why PCM

- What is PCM and How it Works

- Technology Characteristics and Trends

- Application: Directly Addressable NVRAM

- Application: Storage Input / Output Acceleration

#### Performance & Density Comparisons Circa 2011, 45nm Silicon

| Attributes            | DRAM             | PCM                     | NAND                    | HDD                   |

|-----------------------|------------------|-------------------------|-------------------------|-----------------------|

| Non-Volatile          | No               | Yes                     | Yes                     | Yes                   |

| Idle Power            | ~100mW/GB        | ~1 mW/GB                | ~10 mW/GB               | ~10W/TB               |

| Erase / Page Size     | No / 64Byte      | No / 64Byte             | Yes / 256KB             | No / 512Byte          |

| Write Bandwidth*      | ~GB/s<br>per die | 50-100 MB/s<br>per die  | 5-40 MB/s<br>per die    | ~200MB/s<br>per drive |

| Page Write<br>Latency | 20-50 ns         | ~1 us                   | ~500 us                 | ~5 ms                 |

| Page Read<br>Latency  | 20-50 ns         | ~50 ns                  | ~25 µs                  | ~5 ms                 |

| Endurance             | ø                | $10^6 \rightarrow 10^7$ | 1000x → 10 <sup>4</sup> | 8                     |

| Maximum Density       | 4Gbit            | 4Gbit                   | 04Gbit                  | 2TByte                |

|                       |                  |                         |                         |                       |

\*Assumes multiple banks

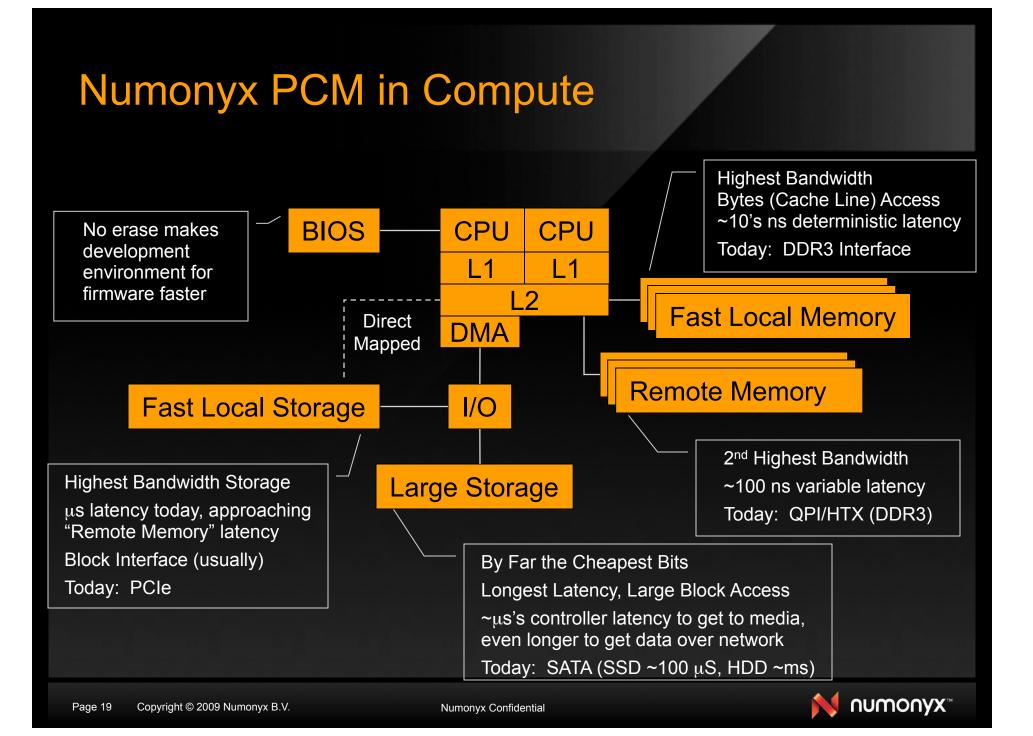

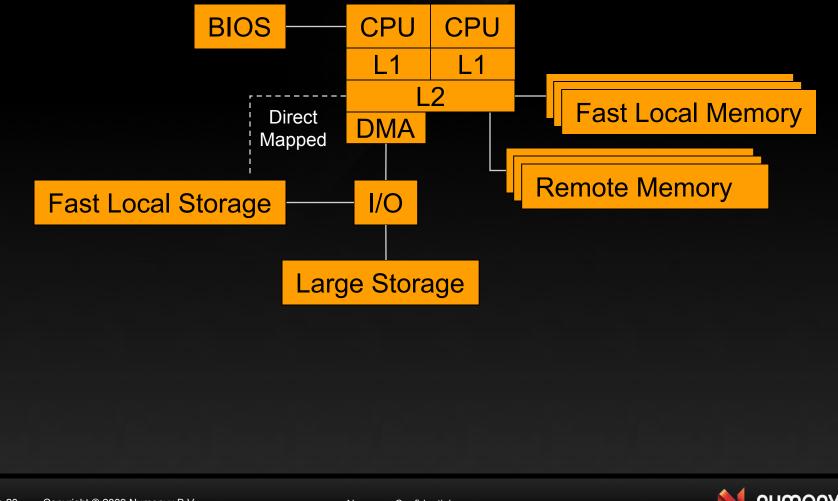

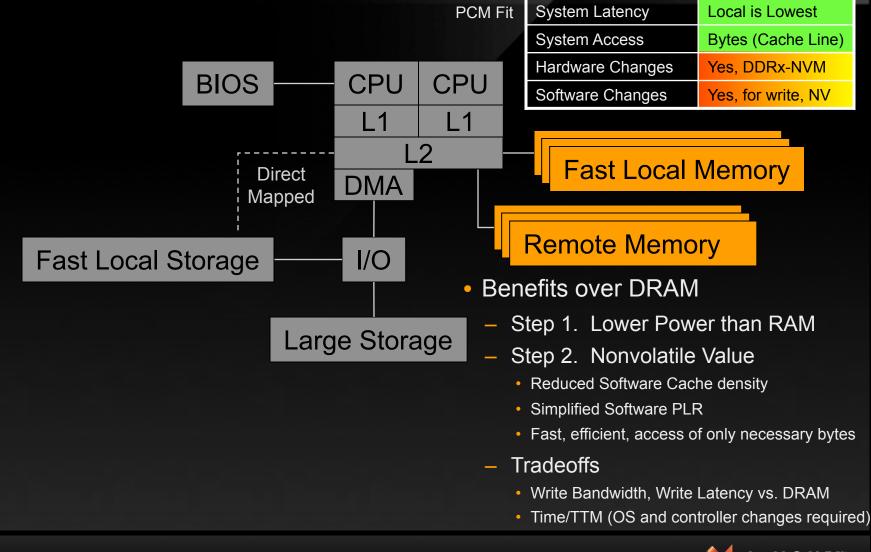

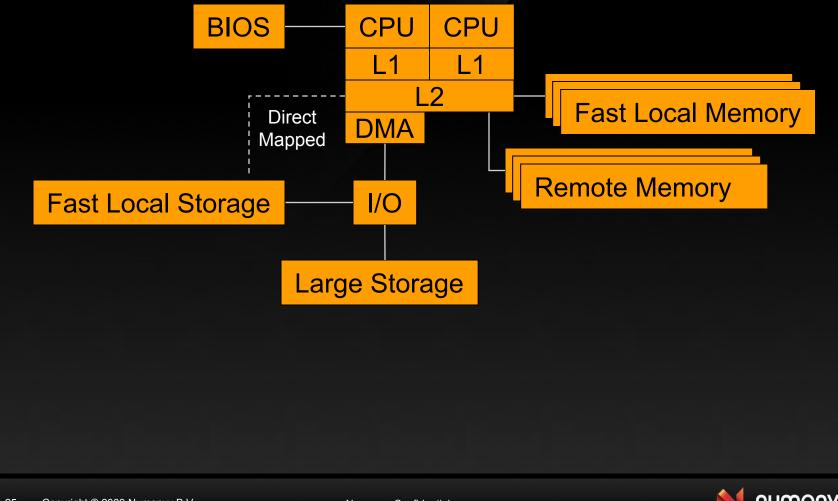

#### Numonyx PCM in Compute

#### Numonyx PCM in Memory

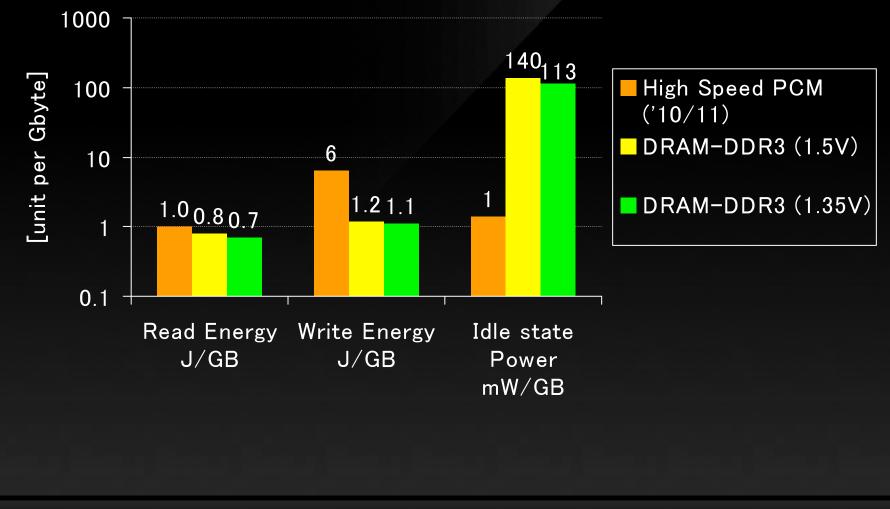

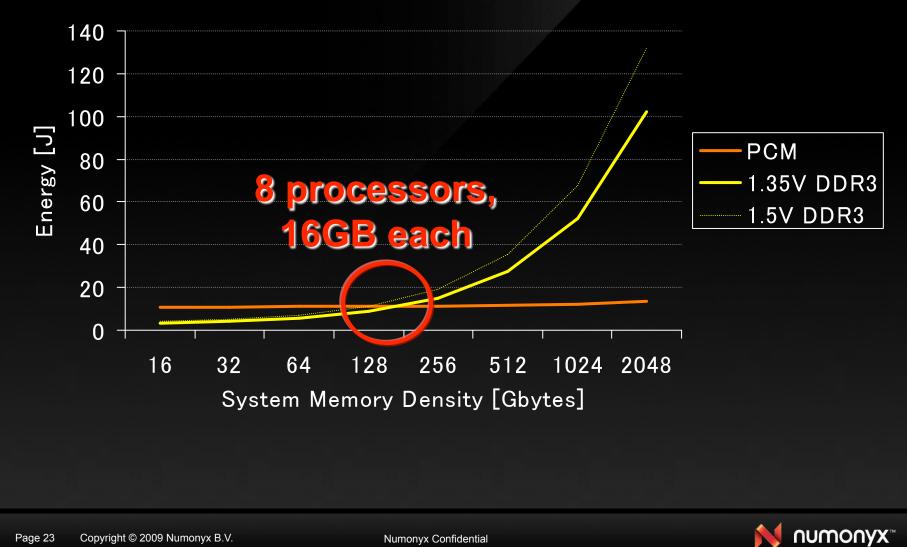

#### **Power and Energy**

#### **Energy Crossover Example**

Assumptions: 25.6GB/s Bandwidth, 50% bus utilization; 70% read, 30% write)

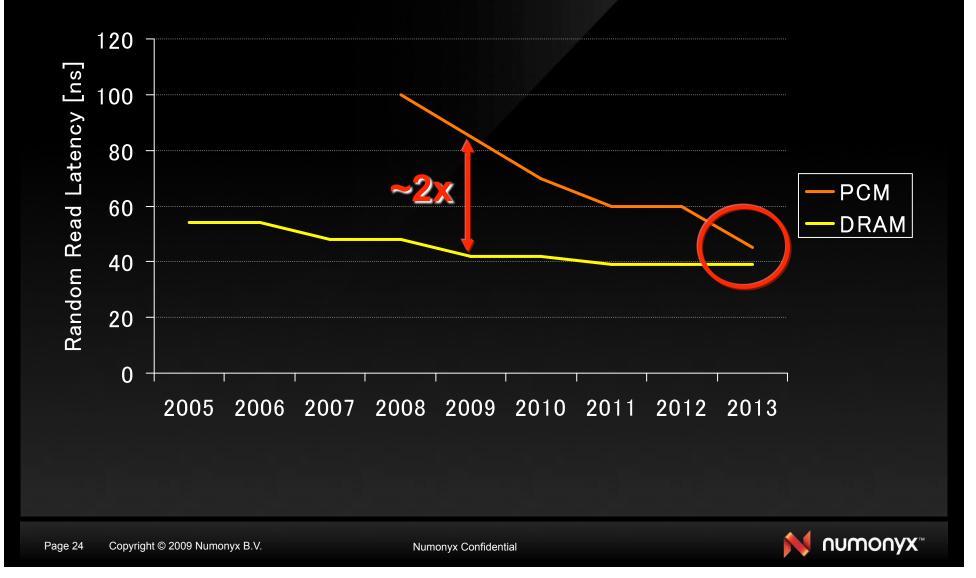

#### Latency: Random Read

#### Numonyx PCM in Compute

Page 25 Copyright © 2009 Numonyx B.V.

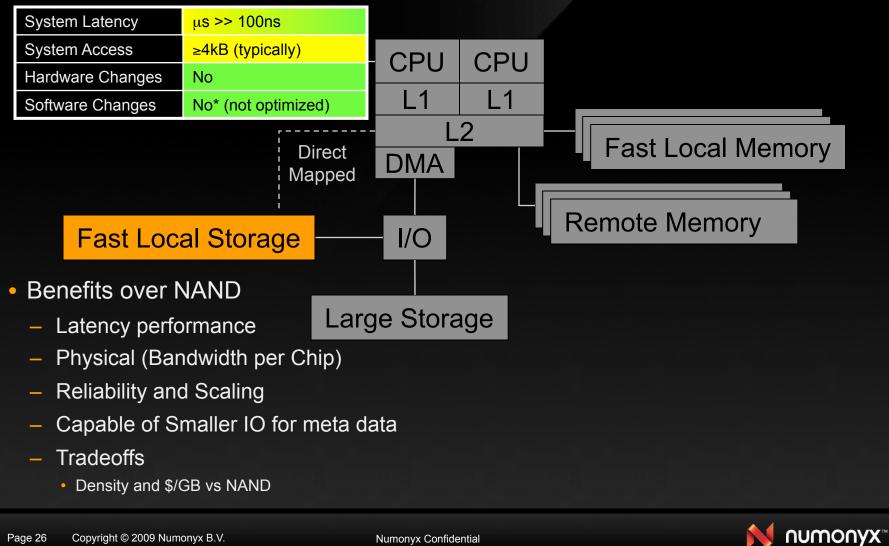

# Numonyx PCM in Storage

#### PCM Fit

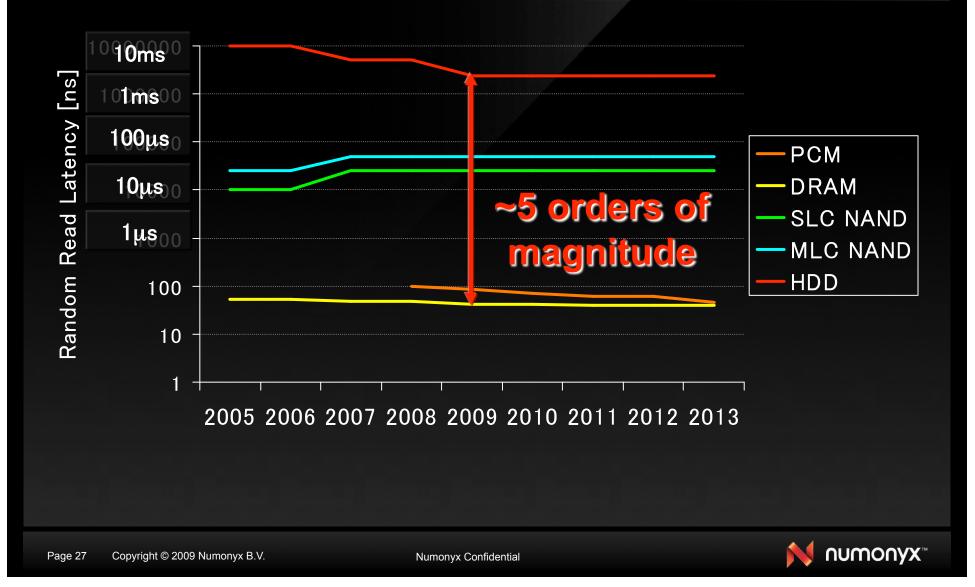

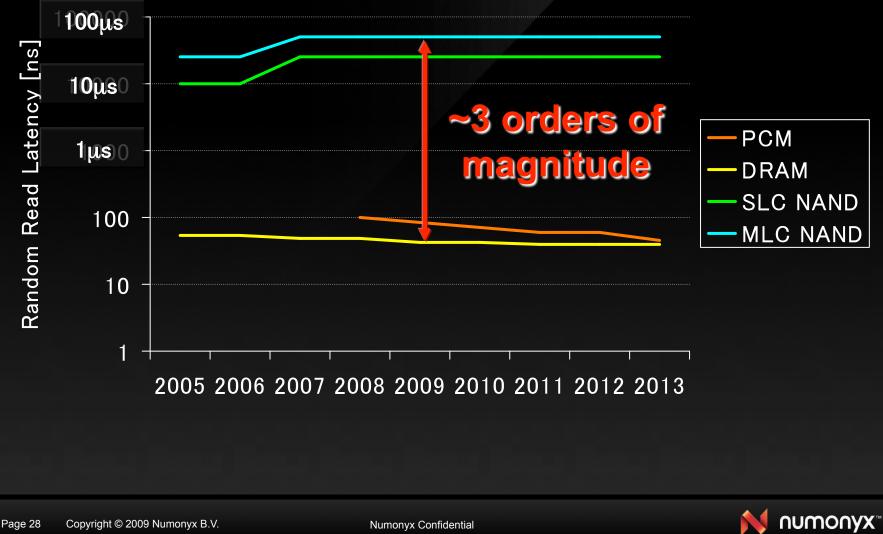

## Latency: Random Read

## Latency: Random Read

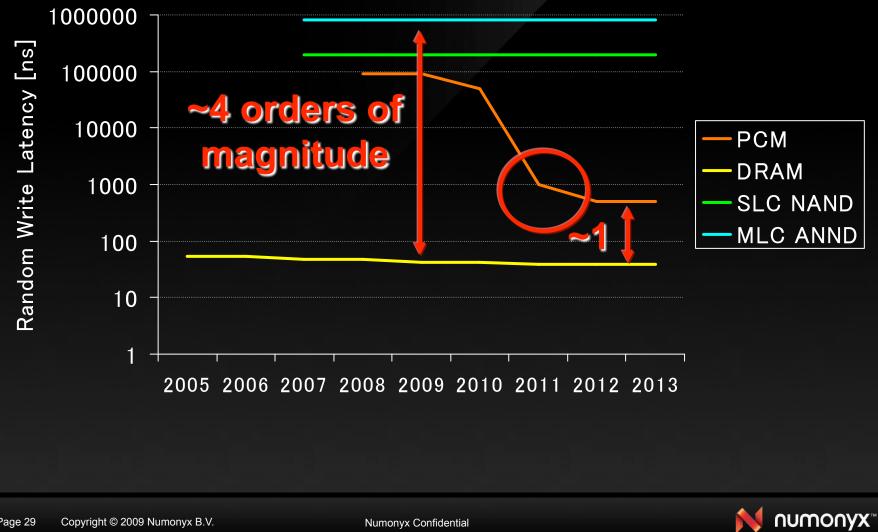

#### Latency: Random Write

Copyright © 2009 Numonyx B.V. Page 29

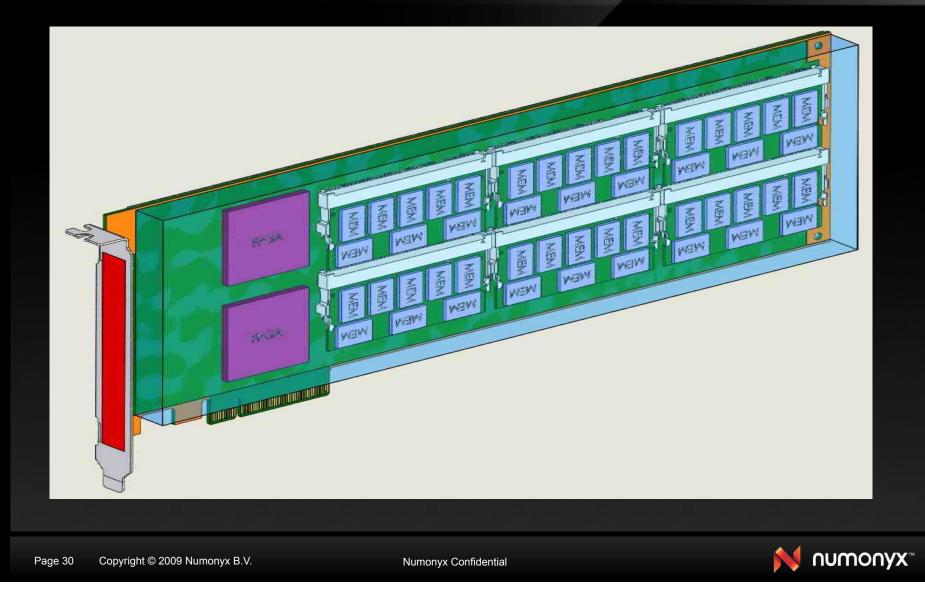

## PCIe Form Factor – Pre-Production Vehicle \*mechanical concept

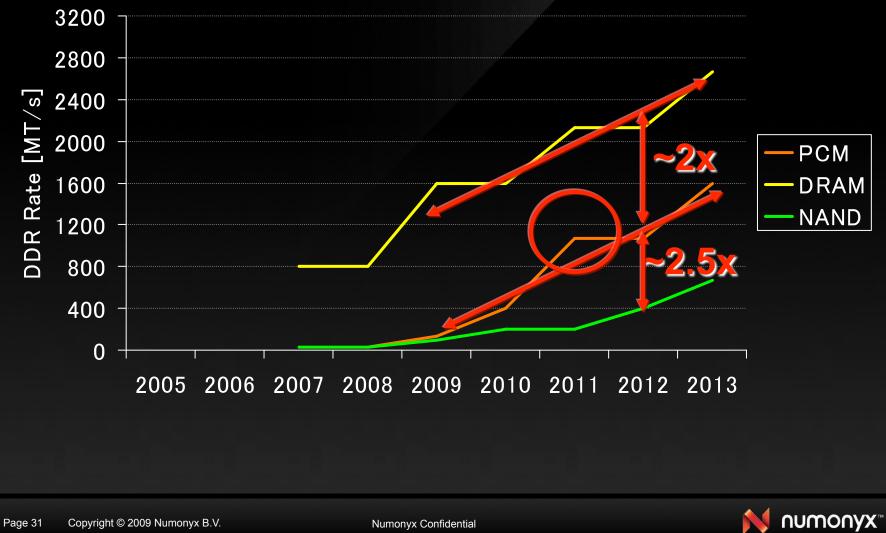

#### **Bandwidth Per Chip: Read**

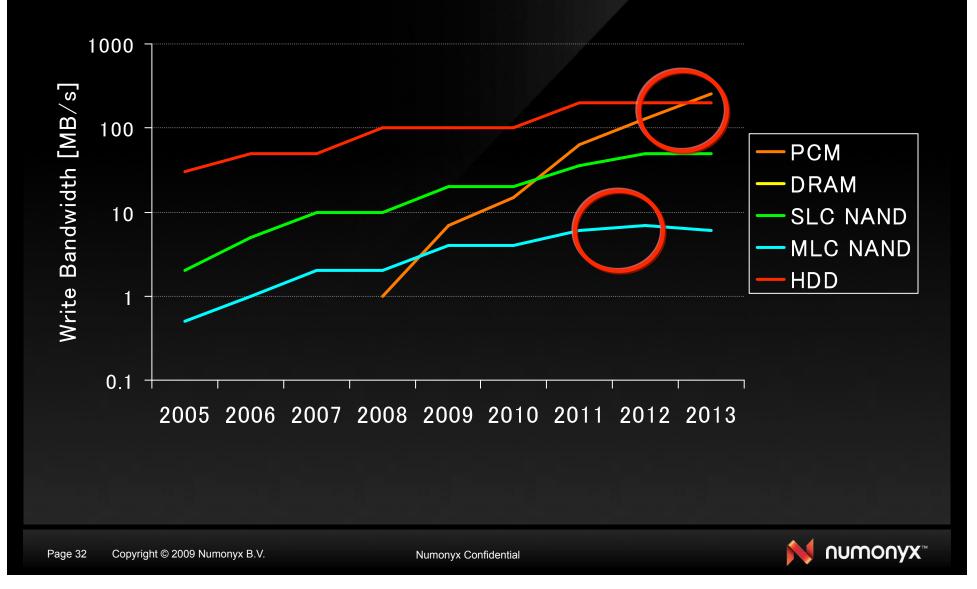

#### Bandwidth per Chip: Write

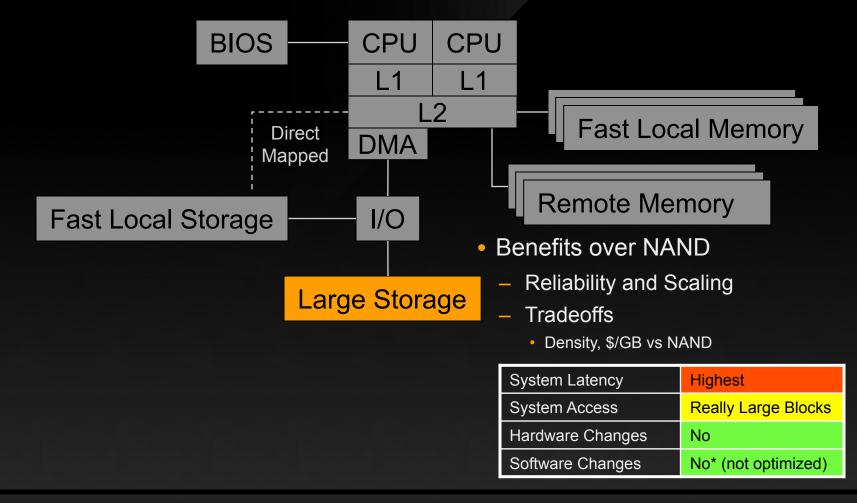

# First (Easiest) Use Model: IO cache Cards

|                        | 2010                |  |

|------------------------|---------------------|--|

| Min Density            | 64GB                |  |

| Max Density            | 512GB               |  |

| Interface              | PCIe 2.0x8          |  |

| Read Bandwidth         | 4.0 GB/s            |  |

| Write Bandwidth        | 400 MB/s            |  |

| Input Voltage          | Up to 12V           |  |

| Power                  | 20W                 |  |

| Read Latency           | 5µS (hw)            |  |

| Write Latency          | 150μS               |  |

| Physical<br>Dimensions | Full Size PCIe Card |  |

| Temperature            | 0°to +55°C          |  |

#### Numonyx PCM in Compute

Page 34 Copyright © 2009 Numonyx B.V.

## Numonyx PCM in Storage

#### Random Performance also seems valuable

"Even in HPC, high IOPS is becoming a necessity. Multicore computing means structured data access is becoming randomized, since I/O now tends to be performed across multiple threads. In particular, metadata is becoming the choke point for large clustered file systems since it tends to be accessed randomly."

Source: July 01, 2009, "A Trio of HPC Offerings Unveiled at ISC" by Michael Feldman, HPCwire Editor

#### In Summary

- We think PCM Power has value in Memory

- But it will take a while for software to catch up

- We think PCM Latency has value in a subset of storage

- Up to ~50-100x faster than the SSD's today

- Small IO access performance (for databases) gets more interesting as Fast Storage and Remote Memory Latencies converge

- We think PCM will out scale (outlast) existing technologies

- More opportunities will open up if technologies start to have difficulty

# **Questions?**

# **NUMONYX**™

## innovative. memory. solutions.