# Physical limits of silicon transistors and circuits

This article has been downloaded from IOPscience. Please scroll down to see the full text article.

2005 Rep. Prog. Phys. 68 2701

(http://iopscience.iop.org/0034-4885/68/12/R01)

The Table of Contents and more related content is available

Download details:

IP Address: 193.205.222.52

The article was downloaded on 30/03/2009 at 15:01

Please note that terms and conditions apply.

doi:10.1088/0034-4885/68/12/R01

# Physical limits of silicon transistors and circuits

# Robert W Keyes

IBM Research Division, Yorktown, NY 10598, USA

Received 27 April 2005, in final form 11 August 2005 Published 19 September 2005 Online at stacks.iop.org/RoPP/68/2701

#### **Abstract**

A discussion on transistors and electronic computing including some history introduces semiconductor devices and the motivation for miniaturization of transistors. The changing physics of field-effect transistors and ways to mitigate the deterioration in performance caused by the changes follows. The limits of transistors are tied to the requirements of the chips that carry them and the difficulties of fabricating very small structures. Some concluding remarks about transistors and limits are presented.

(Some figures in this article are in colour only in the electronic version)

# **Contents**

|    |                       |           |                                | Page |

|----|-----------------------|-----------|--------------------------------|------|

| 1. | Intro                 | duction   | ı                              | 2703 |

|    | 1.1.                  | Adven     | at of the transistor           | 2704 |

|    | 1.2.                  | Electro   | onic computation               | 2705 |

|    | 1.3.                  | Integra   | ated electronics               | 2705 |

| 2. | Sem                   | iconduc   | etor devices                   | 2708 |

|    | 2.1.                  | The pr    | n junction                     | 2708 |

|    | 2.2.                  | The tra   | ansistor                       | 2710 |

|    | 2.3.                  | Compu     | uting with transistors         | 2712 |

| 3. | Field                 | l-effect  | transistors                    | 2713 |

|    | 3.1.                  | Model     | s of the FET                   | 2713 |

|    | 3.2.                  | Additi    | onal FET considerations        | 2715 |

|    | 3.3.                  | The in    | verted layer                   | 2715 |

| 4. | Mini                  | aturizat  | 2716                           |      |

|    | 4.1.                  | Scaling   | 2717                           |      |

|    | 4.2.                  | Subthr    | reshold current                | 2719 |

|    | 4.3.                  | Miniat    | turized MOSFETs                | 2720 |

|    |                       | 4.3.1.    | Short channel effects          | 2720 |

|    |                       | 4.3.2.    | Drain-induced barrier lowering | 2721 |

|    |                       | 4.3.3.    | Gate tunnelling                | 2721 |

|    |                       | 4.3.4.    | Drain currents                 | 2723 |

|    |                       | 4.3.5.    | Short channel experiments      | 2723 |

|    |                       | 4.3.6.    | Mobility                       | 2724 |

|    | 4.4.                  | Novel     | FET designs                    | 2725 |

| 5. | The                   | chip      | 2726                           |      |

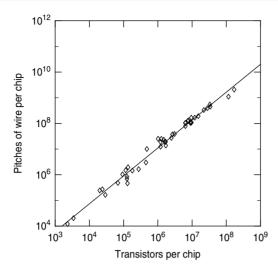

|    | 5.1.                  | Wires     |                                | 2726 |

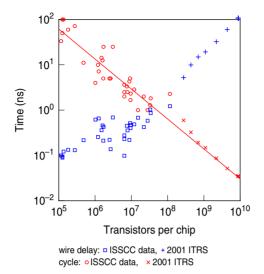

|    | 5.2.                  | Propag    | gation of pulses on wires      | 2727 |

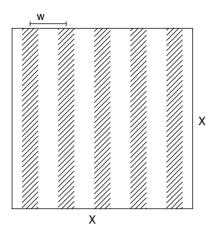

|    |                       | 5.2.1.    | Space for wires                | 2728 |

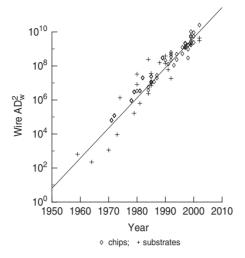

|    | 5.3.                  | Wire le   | 2729                           |      |

|    | 5.4. Nonlocality      |           |                                | 2731 |

|    | 5.5. Long wire delays |           |                                | 2731 |

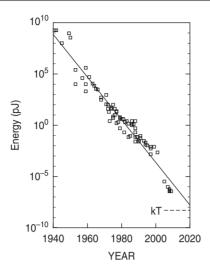

|    | 5.6.                  | Power     | on a chip                      | 2733 |

|    | 5.7.                  | The bi    | Illion transistor chip         | 2735 |

| 6. | Fabr                  | ication   |                                | 2735 |

|    | 6.1.                  | The lit   | thographic process             | 2736 |

|    | 6.2.                  | Proces    | 2737                           |      |

|    | 6.3.                  | New tr    | 2738                           |      |

|    | 6.4.                  | Defect    | 2739                           |      |

|    | 6.5.                  | Additi    | onal factors                   | 2741 |

| 7. | The                   | transisto | 2741                           |      |

| 8. | Limi                  | 2743      |                                |      |

|    | Refe                  | rences    | 2744                           |      |

## 1. Introduction

Readers may be surprised to find a paper on transistors in a physics journal. However, the transistor was invented by physicists and the subject of transistors is permeated with physics. The early studies of transistors were recognized as physics and published in physics journals, but a half-century of use of transistors in electronics has passed the subject into technology and engineering. Physics, however, continues to be an essential part of the continuing development of electronics by providing the basic understanding needed to deal with phenomena that gain importance and must be incorporated in models as the dimensions of transistors are decreased.

In return, by becoming the foundation on which major industries are based, transistors have given a powerful stimulus to the growth of solid state physics. The computational capabilities provided by transistorized computers have greatly expanded the range of techniques available to experimental science and have made whole new fields of physics possible. Many aspects of the manufacturing technology developed by the transistor industry have been adapted to experimental physics. The symbiosis of physics and technology, of basic science and semiconductor engineering, has enabled both to thrive.

The capacity of transistor electronics to reshape our world continues to astonish both observers of and participants in its development. The power to process information provided by electronics has given new abilities to and caused great changes in commerce, entertainment, warfare and communication, in addition to all aspects of engineering and science. Although information processing with machines had been practiced since the late nineteenth century, first with punch card machines and relays and later with vacuum tube computers, the invention of the transistor was the trigger that released the latent power of automated information processing and led to the vital role of electronic computing facilities in modern society. The demand for expansion of that role through lowering the cost and increasing the speed of information processing systems continues.

The rapid advancement of transistor electronics has relied on miniaturization, making transistors and their adjuncts smaller. Decade after decade of reducing the size of transistors naturally leads one to wonder how long that can go on. Thus the search for limits is a search for an answer to the question: 'how small can useful devices be made?' Seeking a limit to miniaturization is not a physics experiment, however, the quest must keep in mind 'useful' or 'why smaller and smaller?' Pushing transistor technology to its limits serves an economic purpose: it lowers the cost of transistors and of the computing power of the systems that use transistors.

The limits of silicon technology have long provided fuel for speculation among those with some acquaintance with the subject, both casual and serious. Regarding the former, the late Rolf Landauer is reported to have said 'Anyone can write E=h/t on a napkin and persuade you over lunch that it imposes a fundamental limit on the power-delay product. The trouble begins when people publish their napkins' (Sandberg 1999). The more thoughtful assessments have been the subject of a good number of excellent reviews (Thompson *et al* 1998, Frank *et al* 2001, Meindl *et al* 2001, Plummer and Griffin 2001, Solomon *et al* 2002). These pertinent reviews are written by experts intimately involved with continued development of the technology, published in engineering journals, and necessarily lead into details that are most conveniently discussed with the specialized vocabulary that has grown up in the industry. The author does not here attempt to compete with these comprehensive and authoritative reviews, our aim will be to convey the essential physics of the topic for scientists not closely aligned with the development of the technology.

The early sections here are devoted to the history and development of transistor technology and the computer industry that supports it in order to clarify the environment that constrains and motivates the quest for miniaturization. Following that, semiconductor devices and transistors

are treated in a little detail with the aim of furnishing a background that will enable one with some acquaintance with solid state physics to follow the subsequent discussion of the changes in transistor characteristics as sizes are reduced. Miniaturization of transistors stresses the environment in which they are used and drives modifications of that. Thus, further sections discuss limitations imposed by the hardware that hosts transistors. Finally, the ability of the industry to manufacture ever-smaller devices in a way that meets the goal of reducing the cost of information processing must be considered.

#### 1.1. Advent of the transistor

The telephone industry was a major user of relays and vacuum tubes in the first half of the twentieth century. Both were prone to failure and used large amounts of power. In 1946 the need for a better switch led the director of the Bell Telephone Laboratories, Mervin Kelly, to assemble a group of physicists charged with finding a solid state replacement for the vacuum tube and relay switches used in the Bell system (Brinkman et al 1997, Riordan and Hoddeson 1997). Germanium and silicon were chosen as working materials because they were readily available through their use as detectors of high frequency electromagnetic radiation during the war. The group was successful and transistor action was soon found in germanium (Bardeen and Brattain 1948, 1949). The novel phenomena that were discovered by the group opened an expanded window on to the solid state and the work was honoured by the award of the 1956 Nobel prize in physics. The promise of small size and high reliability from the newly discovered device immediately attracted widespread attention as an obvious candidate to replace the vacuum tube in many applications. Commercial adoption of the new invention was fast: transistor radios were brought into the market in 1954 and 100 000 were sold. Both vendors of vacuum tube computers and academic engineers were stimulated to explore computing with transistors, and Bell Labs built a 700 transistor computer for the Air Force in 1954 (Riordan and Hoddeson 1997).

The discovery of transistor action promoted the study of the solid state from a poor relation to a major part of physics. Reproducible transistor action depended on the use of good quality materials, leading to the development of methods of producing single crystals of high purity and major advances in material science. Research soon led to the discovery and exploitation of many other semiconductors, including the group III–group V compounds and additional novel effects. Efficient light emission and lasing action found in semiconductors added another dimension to semiconductor physics and spawned new industries. The photovoltaic effect was put to use as a source of electrical energy in solar cells.

Although transistor action was first discovered in germanium, transistors have since been demonstrated in many other semiconductors. Germanium persisted as the favoured transistor material until about 1960, when it became apparent that for a number of reasons silicon was preferable as a vehicle for manufacturing transistors. The oxide SiO<sub>2</sub> has such a prominent place in the list that it has been called 'nature's gift to the integrated circuit industry'. The oxide is easily formed by oxidation of silicon and is an excellent electrical insulator. The SiO<sub>2</sub> has a benign interface with silicon with a low concentration of interfacial electron traps and forms a tenacious chemically resistant coating on silicon that has been used to great advantage in the fabrication of devices. Silicon is a plentiful element at the surface of the earth.

Further, a number of other silicon compounds (metal silicides, silicon nitride) have favourable properties that aid the continued advance of silicon electronics. Silicon also has a desirable set of physical attributes for a room temperature transistor. Its energy gap of about 1.1 eV is large enough to allow a silicon chip to be heated to 100 °C without carriers thermally excited across the gap affecting transistor action. Yet the gap is not too large; in higher band

gap semiconductors acceptor and donor dopants are frequently so far from the band edges that they trap holes and electrons in immobile states at room temperature. (The effective masses of semiconductors tend in a rough way to increase with increasing energy gap and large masses lead to large binding energies of charge carriers to donors and acceptors (Kohn 1957).) The very high solubilities of both acceptor and donor atoms in silicon are advantageous in allowing low resistivity regions to be formed.

The dependence of computer technology on unique properties of silicon have earned that element the appellation 'new steel'. The global semiconductor industry is now an annual quarter-trillion euro behemoth that thrives on the continuing advancement of transistor technology.

#### 1.2. Electronic computation

Computers use binary digital representation of information. Physical entities that represent binary information ideally must be in one of the two possible states, described as appropriate by 1 and 0, ON and OFF, or as a switch being CLOSED or OPEN. The earliest electrical computers used relays as switches. Computers only attracted commercial interest after vacuum tubes, much faster components than relays, were introduced to computing in the ENIAC, demonstrated in 1946. The ENIAC was the first successful general purpose computer, and was a large machine with 18 000 tubes that occupied a  $10 \times 15 \,\mathrm{m}^2$  room. The ENIAC spawned a small industry that manufactured vacuum tube computers. A decade after the transistor became known transistorized computers began to replace vacuum tube machines. The IBM 7000 series computers, announced in 1958, with up to 30 000 transistors were the first large machines to be based on transistors.

Switches are readily adapted to the electrical implementation of binary digital logic operations with zeros and ones. Switches are nonlinear, they are in either one position or the other. The early electrical computers were built with relays, electrically controlled switches and the electronic logic devices that succeeded them, vacuum tubes and transistors, emulate relays, turning the flow of electrons that represent information ON and OFF with electrical signals. The signals that exercise control in electronic computation do so by erection and removal of potential barriers. The voltages that create the barriers must be much larger than the thermal spread of electron energies to effectively simulate an on–off switch:  $qV \gg kT$  or  $V \gg kT/q$ , 30 mV at 350 K. Small signals evoke only a linear response and do not suffice for digital operations.

The kT/q voltage scale can be used to find the order of magnitude of other electrical quantities involved in electrical logic. The impedance of simple structures is determined by geometrical factors times  $\epsilon_0$  and  $\mu_0$ , the electrical and magnetic permittivities of space and is not too far removed from the so-called 'impedance of free space',  $Z_0 = (\mu_0/\epsilon_0)^{1/2} = 377~\Omega$ . A basic measure of current in logic is therefore  $kT/qZ_0 = 70~\mu$ A. Similarly, the scale of power is  $((kT/q)^2/Z_0) = 2~\mu$ W (Keyes 1969, 1975b). While such a semiquantitative argument leaves quite a bit of room to play in, electronics at 300 K cannot do fast logic with submicrowatt power and does not need to command watts or kilowatts to power a logic gate. In fact voltage V of 10-100~kT/q is needed for an adequate approximation to on–off switching, while dielectric and geometric factors usually cause impedances to be only  $0.1-0.3~Z_0$  so the power is expected to be a few orders of magnitude larger than the basic value.

# 1.3. Integrated electronics

It soon became obvious that more devices permitted more computing power, but transistors in their first decade were limited by being manufactured and handled and wired one by one.

The integrated circuit, invented in 1960, by making it possible to make and handle many devices in a single operation opened a door to cost reduction in electronics and increasingly larger systems. Manufacturing integrated circuits was a planar process; devices and their interconnections could be made by performing operations on a single surface of silicon. The modern integrated circuit is a small (several mm² to several cm² in area) thin slice of silicon that contains many transistors and other components and is known as a chip (Reid 1984). The introduction of the 4004 microprocessor with 2300 transistors on a single chip in 1970 was a milestone in the story of the transistor in information processing; it represented more computing power than the ENIAC on a single chip.

The efforts of the information processing industry to satisfy an insatiable demand for more and more computing power per dollar continues to motivate increasing integration. Applications that would have once been impractical become reasonable. Scientific and engineering users seize greater power to increase the depth of detail by decreasing the mesh size in simulations and to attack larger problems and employ more physically realistic models. Sophisticated computer games provide complex actions with increasingly realistic figures. Consumers find convenience in cash registers that can read a bar code and look up a price and ATMs that check a customer's balance and count out money.

Striving to meet the demand for more computing power drives silicon technology towards ever-greater levels of integration, the number of devices that can be placed on a single chip of silicon. The cost of manufacturing a chip is only weakly dependent on the content of the chip, and more devices on a chip means less cost per device and it is devices that provide the computing power.

Chips are actually made by handling wafers, thin slices of a single crystal cylinder of silicon that are large enough to contain a few hundred chips into which they are eventually separated. The size of chips has grown during the era of integrated electronics and the size of wafers has grown to accommodate hundreds of chips. Using numbers typical of the present time, a 200 mm diameter wafer might contain 200 chips each of which holds 25 million transistors; the cost of making a wafer full of devices is shared by  $5 \times 10^9$  transistors.

The need to produce devices at ever-lower cost also leads memory towards increased integration, multigigabit chips are entering the market. Faster, more powerful computers handle larger problems and need rapid access to increasingly larger collections of data. The measure of memory is simply cost per bit rather than the criteria applied to logic chips that include a measure of performance. The well-established magnetic core memories continued to be used in computers for a decade after transistors were introduced for logic. The demonstration of a 1000 bit memory chip in 1970 marked the beginning of cost dominance by semiconductor memory. Since then supplying the demand for more data storage with semiconductor memory through higher and higher levels of integration has been another major thrust of the integrated circuit industry.

The phrase 'Moore's Law' has been rendered threadbare through incessant repetition in the popular and the technical press. In 1965, Moore (1965), a pioneer in the silicon industry as one of the founders of Intel observed that for some time the silicon electronics industry had doubled the number of devices on a chip each year. Moore (1978) went on to attribute the steady growth in the number of devices on a chip to three factors: smaller devices that allow more devices per unit area, larger chips and 'cleverness' or 'compaction'. The last factor refers to making better use of available space on a chip by reducing the area per device by innovations in processing and device design rather than miniaturization. For example, a capacitor might be made by depositing a conductive layer, an insulating film and another conductor on the chip surface. Space can be saved by doing this with several layers, one atop another. Still less space is used by etching a deep hole in the substrate and depositing layers on the surface of

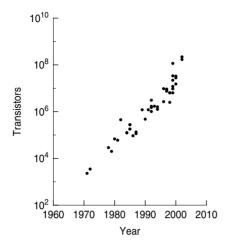

Figure 1. The increasing number of transistors on microprocessor chips.

the hole. Figure 1 shows the results of these inputs as the growing number of transistors on a microprocessor chip since the Intel 4004 in 1970.

The transistor must be considered in the context of the chip. A variety of aspects of a many-transistor chip must be adapted to an increasing chip content. Devices must be connected into functioning circuits by wires; the larger the number of devices, the more the amount of wire needed. Electrical power must be supplied to the circuits and means for removing the heat produced by the power are needed. The chip must be connected to other components which supply the power and which can exchange information-bearing signals with the chip. Smaller, more densely packed devices rather obviously stress the technology that provides these other functions.

Integrated electronics today fabricates the transistors, wires and other components that appear on a chip by subjecting wafers to a long series of process steps in large factories. Patterns of materials are deposited and/or removed in specific areas. Optical (broadly interpreted) radiation passing through masks selects the areas to be affected at each step. The series of operations and the tools that control them must be frequently modified to accommodate smaller features and greater component densities.

By the end of the 1980s the industry view of miniaturization of electronics matured and changed. More than a decade of constant progress towards smaller structures and more devices per chip created the confidence that the development of even more powerful, lower cost electronics could be continued into an indefinite future. Circuits that used field-effect transistors (FETs) were replacing the high power bipolar circuits that had dominated high speed computing. Microprocessors were becoming a major product of the semiconductor industry and playing an increasing part in computing hardware. The evolving device requirements and continued progress towards reduced dimensions and higher levels of integration required new generations of equipment to deal with obstacles that were appearing in the road to continued miniaturization. The dimensions of structures on a chip were falling below the wavelength of visible light—new light sources with shorter wave length were needed. Monochromatic light sources with lenses designed to minimize aberrations and maximize resolution for lithography became essential (Singh *et al* 1997). A new light source meant other new optical equipment with new lenses, and new photoresist materials sensitive to the shorter wavelength had to be found. Shorter times and lower temperatures were required to reduce the distances that

dopants diffused during processing. Smaller defects became important, demanding more rigorous standards of cleanliness. At the same time technology allowed increased chip sizes, helping to increase the number of devices per chip, but calling for larger wafers. Larger wafers meant new apparatus for the growth of larger crystals and for new processing tools that could handle the larger wafers. The transitions to smaller device dimensions and larger substrates pervaded all aspects of a manufacturing facility.

The new tooling requirements had to be communicated to the equipment manufacturers and material suppliers at an early date. The Semiconductor Industry Association was formed to make periodic assessments of the state of the semiconductor art and present quantitative visions of future semiconductor technology. The studies were made publicly available as 'Roadmaps' for the guidance of the suppliers of materials, supplies and semiconductor manufacturing equipment, of the semiconductor industry and of pre-competitive research efforts in university and government laboratories. The forecasts continue today as the International Technology Roadmaps for Semiconductors (ITRS)—international efforts based on inputs from hundreds of volunteers drawn from several national semiconductor associations. The Roadmaps transcend simple extrapolation to examine possible technological directions through the coming fifteen years in detail and identify barriers to progress and potential avenues of research for avoiding them as well as problems for which no solution can be seen at the present time (ITRS 2001, 2003).

However, the history of the integrated circuit industry is one of the discovery of unexpected difficulties and solving them by research and development efforts. A pessimistic view would be that the 'no known solution' barriers seen in the Roadmaps announce a set of limits with dates at which the limits would be felt. However, the view of the Roadmaps and of the institutions that support them is that these are challenges that will be mastered with new ideas and inventions. The Roadmaps have been published for over a decade, and usually technology has advanced more rapidly than anticipated by the Roadmaps.

#### 2. Semiconductor devices

The action of transistors and diodes depends on the existence in semiconductors of mobile charges, both electrons in the conduction band and holes, unfilled states in the valence band (Sze 1981, Taur and Ning 1998, Hess 2000, Seeger 2002). The electrons are introduced by the addition of donor elements, those with one more valence electron than the host atom that it replaces, as phosphorus in silicon, and the holes by acceptor elements, usually boron, from Group III of the periodic table, with one less electron replacing a host atom. Transistors have p-type regions containing acceptors and holes and n-type regions doped with donors and containing electrons, both also containing small numbers of minority carriers of the opposite sign.

#### 2.1. The pn junction

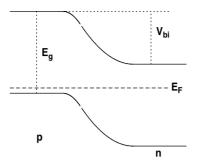

The contact between n and p regions is a pn junction and its properties are important in transistor action. Figure 2 shows how the Fermi level and the band edges are related in a pn junction. The Fermi level is constant throughout and the conduction band edge is near it in the electron-containing region and near the valence band in the p region. The Fermi level in the zone between the n and p regions is far from either band edge, meaning that there are few electrons and few holes present. Dopant concentrations are conveniently referred to the intrinsic concentration,  $n_i$ , the concentration of holes and electrons that would be present by being thermally excited from the valence band to the conduction band in the absence of

impurities:

$$n_{\rm i}^2 = C \exp(-E_{\rm g}/kT). \tag{2.1}$$

The constant C depends on the densities of states near the band edges and  $E_g$  is the gap in energy between the valence band and the conduction band. The intrinsic concentration of silicon at 300 K is  $n_i = 1.45 \times 10^{10}$  cm<sup>-3</sup>. The Fermi level corresponding to the intrinsic case is designated by  $F_i$ .

The variation of the potential between the n and p semiconductors is treated in an excellent approximation (based on the rapid decrease of carrier concentrations as a band edge moves away from the Fermi level) by assuming that the region between the two is entirely depleted of mobile charge carriers and thus is determined by the charge of the donor and acceptor atoms (Shockley 1949). The potential,  $\phi$ , in the depleted region varies in accordance with the Poisson equation

$$\frac{\mathrm{d}^2 \phi}{\mathrm{d}x^2} = \frac{-N_\mathrm{D}q}{\epsilon} \tag{2.2}$$

in the region dominated by donors. Here  $N_{\rm D}$  is the net concentration of positively charged donor atoms and a similar equation holds when acceptors, concentration  $N_{\rm A}$ , dominate. Also  $\epsilon$  is the electric permittivity of the silicon.

Also, although the donor and acceptor doping atoms bind the added carriers at low temperatures, essentially all are ionized at 300 K in silicon and the electron and hole concentrations are equal to the numbers of donor and acceptor atoms in, respectively, n-type and p-type material. Then the number of donor atoms,  $N_{\rm D}$ , equal to the number of electrons, n, in equilibrium may be expressed as  $n=N_{\rm D}=n_{\rm i}\exp((F_{\rm c}-F_{\rm i})/kT))$ , where  $F_{\rm c}$  is the Fermi level in n-type material. A similar equation applies in p-type semiconductor:  $p=N_{\rm A}=n_{\rm i}\exp\left((F_{\rm i}-F_{\rm v})/kT\right)$ , where  $N_{\rm A}$  is the concentration of acceptor atoms and  $F_{\rm v}$  is the Fermi level. Holes and electrons can recombine to reach an equilibrium state in which the Fermi level controls the concentrations of both carriers and the minority carrier concentrations can be determined from the reaction np =  $n_{\rm i}^2$ . In a p-type semiconductor  $n=n_{\rm i}^2/p=n_{\rm i}/N_{\rm A}$  and similarly in n-type material  $p=n_{\rm i}^2/N_{\rm D}$ . The magnitude of the change in  $\phi$  from the conduction band to the valence band is known as the built-in voltage of a junction, shown in figure 2, and is determined by the energy gap of the semiconductor and the doping by donors and acceptors. The built-in voltage  $V_{\rm bi}$  is  $F_{\rm c}-F_{\rm v}$ , the displacement of the energy bands that aligns the Fermi levels across the junction (figure 2) and can also be written as

$$V_{\rm bi} = kT \log \left( \frac{N_{\rm D} N_{\rm A}}{n_{\rm i}^2} \right),\tag{2.3}$$

by using the preceding expressions for  $N_A$  and  $N_D$ . In reasonably conductive materials where the Fermi level in each type is close to the respective band edge  $V_{bi}$  approaches the energy gap.

The application of a voltage to the junction shown in figure 2 creates a difference in the position of the Fermi level between the n and p regions. A positive voltage V applied to the p region, forward bias, lowers the barrier between the two sides of the junction by an amount qV and attracts electrons into that region and forces holes in the opposite direction. The number of carriers that can pass over the barrier is thermally activated, the current is proportional to  $(\exp^{qV/kT}-1)$ , vanishing when V=0. A voltage in the reverse direction, of opposite sign, raises the barrier to a current of majority carriers in each direction. A small current which is still governed by  $(\exp^{qV/kT}-1) < 0$  flows in the opposite direction and saturates rapidly with increasing reverse voltage, V<0.

There are frequent interesting cases in which the doping on one side of the junction is much larger than on the other side, the one-sided junction case. Let the p side of the junction,

**Figure 2.** The variation of the band energies through a pn junction in the absence of an applied voltage.  $V_{bi}$  is known as the 'built-in voltage'. The p side of the junction is more heavily doped than the n side.

doping  $N_A$ , be the lightly doped side. Figure 2 is drawn with asymmetric doping to suggest the nature of this case. The more rapid variation of the potential on the heavily doped side means that almost all of the depleted layer lies on the lightly doped side of the junction where the potential varies as

$$\phi = \left(\frac{N_{\rm A}q}{\epsilon}\right)(x^2 - 2xw_{\rm D}). \tag{2.4}$$

The extent of the depleted space is  $w_D$  and since most of the potential drop is on the lightly doped side the built-in voltage becomes nearly  $V_{\rm bi} = \phi$  (equation (2.4)) and

$$w_{\rm D} = \left(\frac{2\epsilon V_{\rm bi}}{N_{\rm A}q}\right)^{1/2}.\tag{2.5}$$

The widening of the depleted layer under reverse bias is another aspect of the pn junction. The extent of the layer is found by substituting  $(V + V_{bi})$  for  $V_{bi}$  in equation (2.5). As the reverse voltage applied increases the width of the layer increases, but only as the square root of the voltage (equation (2.4)) and the electric field in the layer increases. At sufficiently high reverse bias the electric field in the depleted region can accelerate charge carriers to the point at which they can lose energy by exciting an electron from the valence band into the conduction band, creating a free electron and a hole. These again gain energy from the field and may excite more charge carriers and create an avalanche of current, dielectric breakdown. The field needed to cause dielectric breakdown in silicon is approximately  $4 \times 10^5 \,\mathrm{V\,cm^{-1}}$  and limits the voltage that can be used in semiconductor devices.

Heavy doping thins the depleted layer of the junction. Both sides of the junction can be doped so heavily that the depleted layer is reduced to the point at which holes and electrons can pass through it by tunnelling. When biased in the forward direction the tunnelling currents can produce a negative resistance, a device known as the Esaki diode or tunnel diode (Esaki 1958), which has found applications, though not in logic circuits (section 7). Tunnelling currents play no role in transistor action and are not welcome in logic with transistors.

#### 2.2. The transistor

The principle of the transistor is simple (Sze 1981, Taur and Ning 1998, Hess 2000, Seeger 2002). Potential barriers hold charge carriers of one sign in place while charge neutrality in the

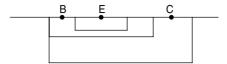

Figure 3. A planar npn bipolar transistor showing contacts to Emitter, Base and Collector.

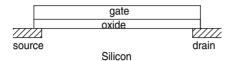

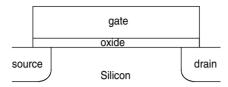

Figure 4. Schematic drawing of a FET.

device is maintained by mobile carriers of the opposite sign. The mobile charge can then carry currents under the influence of electric fields and concentration gradients. Large quantities of electric charge can be carried through the transistor by the mobile charge with only a minuscule current needed to replace any leakage of the fixed charge.

The first transistors were of the bipolar type. The two signs of charge in semiconductors permit the construction of two kinds of transistors, npn, where electrons are the mobile carriers, and pnp. The earliest transistors used point contacts to inject and to collect charges but modern bipolar transistors, like the planar transistor illustrated in figure 3, use pn junctions for the same purpose. Potential barriers formed by pn junctions confine holes in an npn transistor and mobile electrons occupy the same space as the confined holes. Biasing the base of an npn transistor positively with respect to the emitter draws electrons into the base where their charge is compensated by holes supplied through the base contact. The electrons diffuse through a concentration gradient from the emitter across the base to the collector where they are captured by a positively (reverse) biased collector junction, while escape of the holes is prevented by the junction barriers. The concentration of donors in the emitter is made much larger than that of acceptors in the base to make the emitter current mostly an electron current. Electron current can continue to flow from emitter to collector while only a small base current is needed to replace holes lost to the base through the emitter current and by recombination of holes and electrons in the base. Bipolar transistor action depends on the hole-electron recombination lifetime being much longer than the time needed for the electrons to cross the base and enter the collector.

A very thin insulating layer separates the fixed and mobile charges in the FET, illustrated in figure 4. Again there are two kinds of FET, designated as n-type and p-type depending on whether electrons or holes are the mobile charge carriers. A layer of charge attracted to the surface by a positive voltage applied to the gate in an n-type FET forms a connection between the source and drain regions, mimicking the action of a mechanical relay. The advent of commercially useful FETs followed that of bipolar transistors by more than a decade because of the formation of a large concentration of charge trapping states at the interface between the semiconductor and the insulator. Charge on the gate would induce charge in the traps rather than mobile carriers in the semiconductor. Reproducible production of highgain FETs had to await the development of a refined silicon-SiO<sub>2</sub> technology which could produce interfaces between the silicon and the oxide insulator with a low trap density. The difficulty persists in field-effect devices in material systems other than silicon-SiO<sub>2</sub>. The silicon FET dominates contemporary electronics and is the focus of current concern with limits.

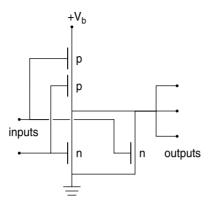

**Figure 5.** A CMOS NOR circuit. If either input is positive the outputs are connected to ground through the n transistors. When both inputs are low the p transistors are turned on and connect the output to  $V_D$ .

The widespread use of silicon-SiO<sub>2</sub> field-effect transistors has earned them their own name: MOSFET. The acronym MOS means metal—oxide—semiconductor with 'metal' referring to the gate. The gate in early FETs was made of the metal aluminium and the name persists even though the gate material today is more commonly heavily doped polycrystalline silicon.

The development of CMOS (complementary MOS) circuits greatly reduced the use of power in electronic switching circuits. CMOS combines n-type and p-type FETs in a circuit in which there are two stable states. Figure 5 is an example of a CMOS circuit. Current flows only when the circuit is switching from one of the states to the other. The low power demand makes CMOS the circuit of choice for miniaturized integrated electronics.

Making both npn and pnp transistors on the same silicon surface poses a problem as the bulk semiconductor should be of opposite type in the two cases. This is managed in a p-type substrate by fabricating the p-FETs in wells doped with donor atoms.

#### 2.3. Computing with transistors

The bipolar transistors in early (before about 1985) large computers controlled large currents to achieve high speed. The density of transistors on a chip increased inversely as the square of the length variable with miniaturization while the current in a transistor remained nearly constant as dimensions were reduced (Keyes 1988). Voltages decreased only slowly if at all, so the density of power dissipation increased rapidly. Removing the heat that was produced became a serious problem as devices were made smaller and levels of integration increased. The high power and large currents limited the levels of integration of bipolar chips to values much less than those that the manufacturing technology allowed, and some large machines adopted water cooling to remove the high power densities of arrays of bipolar circuits (Blodgett 1983).

The capability of FET-based microprocessors after their introduction with the Intel 4004 increased rapidly. The improving performance of microprocessor chips that used FETs forecast the end of the dominance of bipolar transistors in large computer systems. FET circuits became competitive with bipolar logic and, aided by the invention of low power CMOS, FETs dominated large processors by 1990 and systems engineers learned how to build large supercomputers from many microprocessors.

## 3. Field-effect transistors

## 3.1. Models of the FET

First an oversimplified model is used to give a qualitative idea of the current-voltage characteristics of an FET. Referring to figure 4, an n-type FET, let  $c_i = \epsilon_i/t$  be the capacitance per unit area of the insulator that separates the gate from the semiconductor, where  $\epsilon_i$  is the dielectric constant of the insulator and t is its thickness. A positive voltage applied to the gate attracts electrons to the interface between semiconductor and insulator. A minimum gate voltage  $V_T$ , the threshold voltage, is required to cause electrons to appear at the interface. The charge per unit area in the electron channel at the interface is then

$$\rho_{\rm s} = c_{\rm i}((V_{\rm G} - V_{\rm T}) - V). \tag{3.1}$$

Here V is the voltage in the channel, which is connected at one end to the source contact and at the other end to the drain. Considering the source as the zero of potential, a current flows when there are electrons in the channel and a positive voltage is applied to the gate. The current is driven by the electric field parallel to the surface,  $\mathrm{d}V/\mathrm{d}x$ , and for a transistor of width w in the direction normal to the current is

$$i = \rho_{\rm s} v w = c_{\rm i} ((V_{\rm G} - V_{\rm T}) - V) \mu \left(\frac{\mathrm{d}V}{\mathrm{d}x}\right) w, \tag{3.2}$$

where v is electron velocity,  $\mu$  is electron mobility and x is distance from the source. Equation (3.2) is readily integrated to give

$$ix = \mu w c_{\rm i} \left[ (V_{\rm G} - V_{\rm T})V - \left(\frac{V^2}{2}\right) \right]. \tag{3.3}$$

The current through the transistor is found when x = L, the distance from source to drain and  $V = V_D$  is the voltage applied to the drain.

$$i = \left(\frac{\mu w c_{\rm i}}{L}\right) \left[ (V_{\rm G} - V_{\rm T}) V_{\rm D} - \frac{V_{\rm D}^2}{2} \right].$$

(3.4)

Equation (3.4) as a function of  $V_D$  has a maximum when  $V_D = V_G - V_T \equiv V_S$ . When  $V_D$  is increased beyond the saturation voltage  $V_S$  the current remains constant, and it is said to be saturated.

When the drain voltage is raised above  $V_S$  no charge remains at the drain to carry the current (equation (3.1)). The channel is said to be 'pinched off'. In fact, this does not happen as the carrier velocity saturates at high fields and a few carriers remain to carry the current under the influence of a very high electric field between the drain and the point of pinch-off. The field near the drain can become comparable to the fields in the depleted layers and the gradual channel approximation fails.

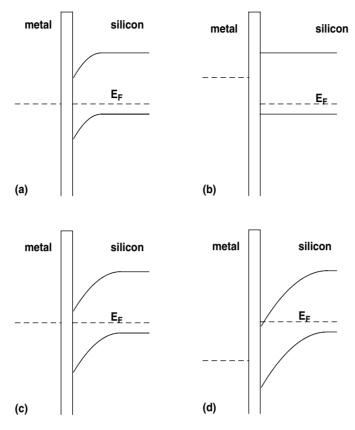

The threshold plays an important part in a discussion of limits. Figure 6 shows the variation of the energy bands of a semiconductor along a vertical line from the gate electrode through the insulator into the body of the p-type semiconductor. In these plots  $E_c$  and  $E_v$  are energies of the conduction and valence bands and  $E_F$  is the Fermi energy. The Fermi levels of the gate and the semiconductor are aligned in figure 6(a), no voltage is applied to the device. Figure 6(b) shows the 'flat-band' condition, i.e. a voltage that produces a vanishing electric field in the bulk semiconductor has been applied to the gate. The flat-band condition is a convenient starting point for a discussion of thresholds. In practice, the voltage necessary to achieve the flat-band condition must be added to the threshold. In figure 6(c) a positive voltage that lowers the energy of the conduction band to the point at which the distance of the conduction band above the bulk Fermi level is equal to the energy distance between the Fermi level and the

**Figure 6.** Energy bands at the surface of an n-type FET. (a) No voltage is applied to the metal gate. (b) Flat-band. A gate voltage has removed the variability of potential within the silicon. (c) Threshold, by convention defined as the point at which the potential difference between the bottom of the conduction band at the surface and the Fermi level is equal to the difference between the valence band in the bulk silicon. (d) Deep inversion, the Fermi level has entered the conduction band creating a thin layer of a degenerate electron gas at the surface.

valence band in the p-type substrate has been applied to the gate. The gate voltage at this point is by convention called the threshold voltage. At this threshold the concentration of electrons at the oxide–silicon interface is approximately equal to the concentration of holes in the substrate. Figure 6(d) shows the beginning of deep inversion, when the Fermi energy enters the conduction band.

The solution of Poisson's equation in the depletion approximation in the substrate where the charge is dominated by acceptor atoms is

$$\phi = -\psi + \left(\frac{N_{\rm A}q}{\epsilon}\right) \left(\frac{wx - x^2}{2}\right). \tag{3.5}$$

Here x is the distance into the substrate from its contact with the insulator,  $N_{\rm A}$  is the concentration of acceptor atoms in the depleted region,  $\phi$  is the change in potential measured from the p-type interior of the substrate,  $\psi$  is the change in potential in the semiconductor from its contact with the insulator to the bulk and w is the width of the depleted layer. The boundary conditions are  $\phi = -\psi$  at x = 0,  $\phi = 0$  at x = w and  $w = \sqrt{2\psi\epsilon/N_{\rm A}q}$  is the width of the depleted region.

At the threshold as defined above  $q\psi_t = E_G - 2(E_F - E_v)$ , where  $E_G = E_c - E_v$  is the energy gap. The electric field in the insulator at this point is determined by  $\epsilon_{\rm ox} F_{\rm ox} = \epsilon w (N_{\rm A} q/\epsilon)$  when the field in the semiconductor is found by differentiating equation (3.5). Substituting the value of w gives  $F_{\rm ox} = (2N_{\rm A} q \psi_t / \epsilon)^{1/2} / \epsilon_{\rm ox}$ . Adding the potential drop in the insulator to that in the semiconductor gives

$$V_{\rm T} = \psi_t + \left(\frac{t_{\rm ox}}{\epsilon_{\rm ox}}\right) \left(\frac{2N_{\rm A}q\psi_t}{\epsilon}\right)^{1/2},\tag{3.6}$$

as the voltage on the gate electrode at threshold.

Increasing the gate voltage above threshold attracts more electrons to the channel. The added charge on the gate is compensated by the charge in the channel and there is little change in the depleted layer. The charge in the depleted region is  $Q_{\rm d}=N_{\rm A}w$  and  $V_{\rm T}$  can also be written as  $V_{\rm T}=\psi_t+Q_{\rm d}/c_{\rm ox}$ , where  $c_{\rm ox}=\epsilon_{\rm ox}/t_{\rm ox}$  is the capacitance of the insulator per unit area.

#### 3.2. Additional FET considerations

This simple description hides various aspects of the FET which are discussed in detail in (Sze 1981, Taur and Ning 1998), which deserve brief mention.

The mobility in equations (3.2)–(3.4) is not a simple constant as assumed above but is influenced by several aspects of the conditions of operation. The mobility is less than the mobility in the bulk semiconductor because mobile carriers are scattered by the semiconductor—insulator interface. The closer the carriers are to the interface, the stronger the scattering, so that the mobility is less, the greater the transverse electric field that holds the electrons near the interface.

At high electric fields electrons and holes gain kinetic energy from the electric field so rapidly that their effective temperature rises above that of the solid silicon. The charged particle's interactions with the lattice change, and the electrons approach a limiting velocity as the field increases. At high enough fields a few of the 'hot' electrons gain enough energy to escape over the barrier that holds them in the semiconductor and escape into the oxide, where they become trapped and where their charge changes the threshold voltage of the transistor. The escape of hot electrons from the silicon to the traps in the oxide is one of the limits of the design and use of field-effect transistors.

If the source-to-drain distance becomes less than the mean free path of the electrons, charge carriers may traverse the distance without being scattered, a regime known as 'ballistic' transport.

## 3.3. The inverted layer

An effect on the threshold of an FET discovered by Fowler  $et\ al\ (1966)$  in MOSFETs in deep inversion (figure 6(d)) can be attributed to 'particle in a box' quantization in the narrow channel (Stern and Howard 1967). FETs in a state intended to carry current are operated in the deep inversion regime in which the Fermi level in the layer is above the bottom of the conduction band. The electrons are a statistically degenerate gas and a rough idea of the nature of the inversion layer can be obtained from a drastically simplified statistical view of the layer (a two-dimensional Thomas–Fermi model). Consider a layer of electrons on a p-type surface. In deep inversion the concentration of electrons is much larger than the concentration of acceptor atoms and the latter will be neglected. The electron gas can be considered degenerate. Then

the concentration of electrons at any point is

$$n = \left(\frac{8\pi}{3h^3}\right) (2me(E_{\rm F} - \phi))^{3/2}. \tag{3.7}$$

Poisson's equation must also be satisfied:

$$\frac{\epsilon d^2 \phi}{dx^2} = \left(\frac{8\pi e}{3h^3}\right) = n\epsilon = (2me(E_F - \phi))^{3/2}.$$

(3.8)

Equation (3.8) has an analytic solution:

$$(E_{\rm F} - \phi) = \frac{B}{(x+a)^4}. (3.9)$$

Here B is

$$B = \frac{400(3h^3\epsilon/8\pi e)^2}{(2me)^3}. (3.10)$$

The parameter a can be determined from  $F_S$ , the electric field in the semiconductor at the surface or from  $N_S$ , the total number of electrons in the surface layer.

$$N_{\rm S} = \frac{\epsilon F_{\rm S}}{e} = \frac{4B\epsilon}{ea^5}.\tag{3.11}$$

The electron density in the layer is given by

$$n = \frac{5N_{\rm S}a^5}{(x+a)^6}. (3.12)$$

For a field of  $3 \times 10^5$  V cm<sup>-1</sup> in silicon at the interface, for example, a is about 4 nm and the electron concentration in the channel is  $2 \times 10^{12}$  cm<sup>-2</sup>; the electrons are confined within a few nanometres of the surface. The lowest energy state of an electron in a 4 nm box in silicon is several tens of millivolts above the bottom of its well and the quantization has a significant effect on the threshold voltage of an FET (Stern and Howard 1967, Stern 1972, Tang *et al* 2004).

Much has been left out of the above cursory treatment. An effect of importance in miniaturized transistor arises from the multivalley nature of the silicon band structure (Kohn 1957). Different contributions to the conduction band and to the valence band are affected differently by the narrow channel confinement and participate differently in the channel wave functions. The splitting is dependent on crystalline orientation and is different for different crystallographic orientations of the silicon surface (Fischetti *et al* 2003). The lowest energy band and the mobility of a charge carrier therefore varies with the orientation of the surface.

#### 4. Miniaturization of field-effect transistors

Two forces propel the miniaturization of MOSFETs. Besides the obvious increase in the number of devices per chip, miniaturization allows devices to switch faster. Decreasing distances allows electrons and holes to pass through devices in shorter times and devices are closer together, reducing device—device travel time. Capacitance is dimensionally equivalent to length; smaller devices have less capacitance to charge. Performance, measured as speed of operation, is improved.

The state of miniaturization is described by a measure of the minimum dimension which the fabrication technology can define on a chip. The dimensional feature that is used as the measure of miniaturization is somewhat arbitrary and may be called such names as 'rule' and 'technology'. The Semiconductor Industry Association for purposes of its periodic Roadmaps (ITRS 2001, 2003) uses the measure half of the pitch (the line-to-line distance) of the finest conductors on a chip and calls it 'technology node'.

Table 1. Constant field scaling.

| Quantity                        | Symbol | Scaling factor |

|---------------------------------|--------|----------------|

| Dimension                       | L      | S              |

| Voltage                         | V      | S              |

| Concentration                   | n      | 1/s            |

| Electric field = $V/L$          | E      | 1              |

| Current density $ne\mu E$       | j      | 1/s            |

| $Current = jL^2$                | i      | S              |

| Capacitance $\sim L$            | C      | S              |

| Resistance $\sim 1/L$           | R      | 1/s            |

| Voltage in resistance           | i R    | 1              |

| Power = iV                      | P      | $s^2$          |

| Power/area = $iV/L^2$           | Q      | 1              |

| Time = CV/i                     | t      | S              |

| Energy = $Pt$                   | W      | $s^3$          |

| Number of dopant atoms = $nL^3$ | m      | $s^2$          |

# 4.1. Scaling

In a first approximation miniaturization reduces all dimensions of a device by the same factor in order to retain the model of the physics of the device. For that reason miniaturization is also called 'scaling' and rules have been promulgated to guide scaling. An early influential set of rules for reducing dimensions by a factor *s* is given in table 1 (Dennard *et al* 1974). Voltages are reduced in proportion to the dimensions in this scenario in order to keep electric fields constant, giving it the name 'constant field scaling'. Limiting the electric field prevents electrons from gaining enough energy to exhibit the hot electron effects mentioned above. Hot electrons may acquire enough energy to surmount barriers, even enough to escape from the channel of an FET into the gate insulator where they can become trapped and where their charge will alter the transistor characteristics or cause dielectric breakdown as described in section 2.1.

Scaling of dimensions requires that the thickness of depleted layers between n- and p-type material be reduced in the same way as other dimensions. Table 1 addresses the thinning of depleted layers: since the width of a depleted layer is proportional to the square root of the voltage supported by the layer divided by the doping concentration (equation (2.4)), increasing the doping level by a factor 1/s in addition to reducing the voltage reduces the depleted layer thickness by the factor s. The physics then controls the scaling of many other electrical characteristics of the scaled device, as shown in the table.

Table 1 illustrates how constant field scaling advances the goals of miniaturization: increased speed, the time scale is reduced by factor s, and lower power, the power per device is reduced by  $s^2$ . Of course, the density of devices on a chip is also increased by factor  $s^2$ , but the power per unit area is constant and the energy dissipated per switching event decreases by a factor  $s^3$ .

Scaling forms a convenient starting point for a discussion of miniaturization, but technology, for a variety of reasons, has found it difficult to strictly follow the scaling rules of table 1. There are certain fixed voltages that are impossible or extremely difficult to change. First is the built-in voltage which is important in determining the thickness of depleted layers, but which cannot be decreased much below the semiconductor energy gap, as seen in the p-n junction (figure 2). Thermal energy, kT, that prevents an abrupt effect of voltage barriers on electron currents is fixed by the environment and is not scaled. To change the number

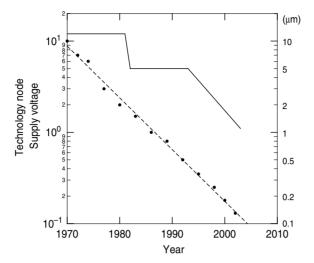

**Figure 7.** The changes in widely used power supply voltages and the minimum dimension on chips since the introduction of the microprocessor in 1970. The dots representing dimension refer to the right-hand scale.

of electrons that pass a potential barrier by orders of magnitude, as required of a switch, the height of the barrier must be changed by a voltage large compared with kT/q. Also, fabrication processes leave appreciable uncertainty in the parameters of devices that must be accounted for in circuits (Orshansky 2000).

The randomness in the position of dopant atoms in semiconductors is an inherent source of uncertainty in small devices. Table 1 shows that the number of atoms in any particular region of a device, m in the table, scales as  $s^2$ , decreasing rapidly as dimensions are reduced. The random fluctuation in m is of order  $m^{1/2}$ , becoming a larger fraction of m in smaller devices. This effect in the depleted layer under the channel causes fluctuations from device to device in the threshold voltage of FETs (Hoeneisen and Mead 1972, Keyes 1975a, 1994, De *et al* 1996). The smaller number of dopants exposes transistors to the effects of fluctuations in their number which may also have to be taken into account in signalling voltages. Voltages must overwhelm both the uncertainties of fabrication and the thermal distribution of energies and cannot in practice always be reduced as desired.

The voltage drop in the ohmic resistance inherent in devices, for example in the source and drain in figure 4, scales as a constant. Since the voltages involved in device action are reduced with dimensions the resistive drops loom larger.

For these and other reasons the full reduction in voltage suggested by table 1 has not occurred. Reducing voltage was retarded by being tied to industry-wide standards for many years. Scaling according to the rules of table 1 decreases the device current, an eventuality to be avoided to the extent that it decreases speed of response or if current also flows to entities that are not scaled, such as long wires on a chip. Circuit and device designs must respond to a business quest for greater speed, an objective that is advanced by setting voltage and the resulting currents higher than prescribed by scaling. Figure 7 shows how the most common voltage used in computer circuitry has varied with time and compares it with the progress of miniaturization as measured by the minimum dimension of features on chips.

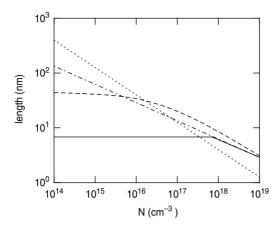

Certain length parameters characterize silicon and are not controlled by the manufacturing process and cannot be scaled. Selected length parameters of n-type silicon at 300 K are plotted

**Figure 8.** Some material parameters of n-silicon as a function of the donor concentration at 300 K. The dashed line is the electron mean free path, the dotted line is the screening radius, the dot-dash line is the average distance between donor atoms, and the solid line is the electron wavelength, determined by the temperature at low concentrations but decreasing as the electron gas becomes degenerate.

as a function of donor concentration in figure 8. The approach of the dimensions of transistors to inherent material length parameters does not mean that the devices will not work, but it does mean that new physical effects may become important and new device models may be needed. For example, device dimensions near or below the electron mean free path mean that an electron might traverse that dimension without being scattered, its motion is not controlled by a mobility parameter, and when a dimension approaches the electron wavelength quantum effects must be considered. Although hard to depict in figure 8, tunnelling probabilities increase with decreasing dimension, as will be seen later.

Therefore, as devices are miniaturized new physical effects that must be taken into account appear and models must be enlarged to include them. The availability of powerful computers permits the inclusion of complex effects in detailed numerical simulations of device operation to replace analytic models in exploring device designs. A simulation program follows the progress of an electron through a numerical model of a device structure with many small time steps. The probability of each possible kind of interaction (for example, acceleration by a field, scattering by an impurity, interaction with a phonon, recombination with a hole, loss of energy to the creation of an electron–hole pair) that may effect an electron trajectory are obtained from the basic physics of the phenomena involved. At each time step a random number generator selects an event (or lack thereof) from the known probabilities. Following many electrons (typically thousands) through a structure gives a picture of device action (Price 1978, Jacoboni and Reggiani 1983, Laux *et al* 1990). The probabilistic content of such simulations has earned them the name 'Monte Carlo' programs.

#### 4.2. Subthreshold current

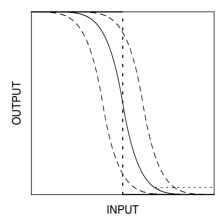

Transistors in digital computers are used as switches in computing and face a limit when they are unable to control current. No current should flow to the drain when a transistor is turned off by a voltage applied to the gate. However, an FET is never completely 'off'. As noted earlier, hole and electron concentrations reach an equilibrium described by  $np = n_i^2$ . As the gate voltage moves the conduction band upwards in energy and farther from the Fermi level to turn

the transistor off the electron concentration decreases exponentially but does not vanish. The few remaining electrons under the gate carry a small 'subthreshold current'. The subthreshold current is usually characterized by a subthreshold slope, which measures the increase in gate voltage needed to reduce the subthreshold current by a factor of 10. An expression for the subthreshold slope is (Taur and Ning 1998)

$$S = \left[\frac{\mathrm{d}(\log_{10} I_{ds})}{\mathrm{d}V_g}\right] = \left(\frac{kT \log_{10}}{q}\right) \left(1 + \left(\frac{C_\mathrm{d}}{C_\mathrm{ox}}\right)\right). \tag{4.1}$$

Here  $C_{\rm ox} = \epsilon_{\rm ox}/t_{\rm ox}$  is the capacitance per unit area of the insulator and  $C_{\rm d} = \sqrt{Nq\epsilon/(2V_{\rm d})}$  is the corresponding capacitance of the depleted layer in the semiconductor.  $V_{\rm d}$  is the voltage drop in the depleted layer and is close to the built-in voltage of the source–substrate junction. The first term in the parentheses in equation (2.1) represents the decrease in the number of thermally excited carriers when the carrier concentration decreases in the way described and has the value 2.3(kT/q) = 60 mV at 300 K. The second term accounts for the division of the gate voltage between the series-connected gate capacitance and the capacitance of the depleted layer and vanishes if  $C_{\rm ox} \gg C_{\rm d}$ . As other voltages are reduced in accordance with table 1 the subthreshold slope is nearly constant and becomes more significant.

The capacitance  $C_{\rm ox}$  really represents the capacitance between the gate electrode and the electrons in the channel and is diminished by two additional factors that gain in importance as dimensions are reduced. The quantization of the electronic states in the channel removes the electrons from the interface with the oxide (Stern 1972), and the applied voltage causes a small depletion of the heavily doped silicon which forms the gate at the oxide interface. Each of these contributes roughly 0.5 nm to the electrical distance between the gate and the channel, thereby reducing  $C_{\rm ox}$  and increasing the subthreshold slope S.

For any subthreshold slope the leakage current when the transistor is 'off' decreases with increase in the voltage. The steady reduction of the supply voltage that accompanies miniaturization reduces the voltage available to turn the transistor off, allowing leakage to become relatively more important.

# 4.3. Miniaturized MOSFETs

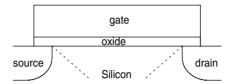

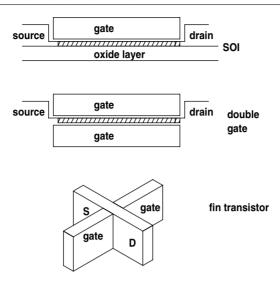

The simple model of an FET presented in connection with figure 4 becomes increasingly inaccurate as channel lengths are reduced. In a long channel MOSFET the channel length is much greater than the depletion widths. The field along the channel is much weaker than the vertical fields and may be treated as a small effect superimposed on the vertical field. The channel ceases to be long in this sense at some stage of miniaturization and the approximation fails because depletion layer widths are related to the energy gap and cannot be scaled in proportion to dimensions as called for in table 1. While in figure 4 the width of the depleted regions associated with the source and drain junctions has been neglected, when the channel length is decreased to the point at which the widths of the depleted regions approach the channel length they begin to affect the device characteristics. The depleted width is in the range from 100 to 1000 nm and when the channel length decreases below about  $1 \mu \text{m}$ , depending on substrate doping, there is a significant effect on transistor characteristics. The simple planar picture of figure 4 must be replaced by the fully two-dimensional view of figure 9.

4.3.1. Short channel effects. When the length of a gate in a miniaturized FET is decreased while leaving all other parameters the same the threshold voltage is found to decrease with gate length, the 'short channel effect'. The reason for the effect is that because of the part played

**Figure 9.** A miniaturized FET, showing how the vertical dimensions become comparable to the lateral dimensions.

**Figure 10.** The dotted lines indicate that part of the depleted layer under the gate is controlled by the source and drain, leaving less to be depleted by the gate as the channel length decrease, producing the short channel effect.

by the energy gap in the built-in voltage the extent of the depleted regions associated with the source and the drain is relatively larger in the FET of figure 9 than in figure 4. The charge in the regions depleted by the source and the drain is a significant part of the total charge under the gate. As the gate is shortened the regions depleted by source and drain remain the same, leaving less charge to be depleted by the gate and lowering the threshold voltage.

The electric field normal to the surface and the field perpendicular to the surface are considered separately in the treatment of section 3.1, an approximation that is appropriate when the gate and the channel are large compared with the thickness of the depleted layer beneath the channel. This is known as the gradual channel approximation and fails in the miniaturized devices of contemporary practice when the electric fields from source and drain intrude on an appreciable fraction of the volume beneath the gate. A 'charge sharing' model, illustrated in figure 10 (Nguyen and Plummer 1981), provides a picture of the loss of control by the gate. The point is illustrated by Poisson's equation:  $\partial F_x/\partial x + \partial F_y/\partial y = -qN_A/\epsilon$ . Increasing the horizontal field by shortening the channel steals charge from the vertical field. Overall charge neutrality reigns in the device and the charge that compensates the charge in the depleted region under the gate is shared by the gate, source and drain.

The short channel effect translates variability in channel length after fabrication into variability of threshold voltage, it adds to uncertainty in the value of the threshold and to a signal amplitude large enough to turn all transistors on and off.

- 4.3.2. Drain-induced barrier lowering. A voltage applied to the drain in the operation of the MOSFET enlarges the depleted layer at the drain and, as described above, reduces the amount of charge controlled by the gate. When a positive voltage is applied to the gate the threshold voltage is lowered. This effect is known as drain-induced barrier lowering (DIBL).

- 4.3.3. Gate tunnelling. Miniaturization aids the flow of certain currents that play no role in the intended function of a transistor. The steady reduction in voltages shown in figure 7 means that the size of the potential barriers that turn off currents is decreased. Decreasing dimensions and lower, thinner potential barriers eventually permit currents that are not an intended part of transistor action.

Figure 11. Tunnelling current through an  $SiO_2$  as a function of the oxide thickness and the voltage across the oxide, after Lo (1997).

The gate controls the inversion channel through the capacitance between channel and gate. When the transistor is scaled and the gate length is decreased the insulator is thinned along with the other dimensions as dictated by the rules of table 1 and the capacitance of the gate per unit area increases. This desirable effect is limited, however, by a current of electrons tunnelling through the insulator, which increases rapidly with decreasing thickness and eventually prevents scaling of the gate thickness. A simple geometrical model of oxide tunnelling is susceptible to quantitative analysis (Lo et al 1997) and provides the plot of current through the gate oxide to an n-type inversion layer as a function of oxide thickness presented in figure 11 for one and one-half volt potentials across the oxide. The tunnelling current does not prevent the transistor from working, the gate can still control the current between the source and the drain, but the power consumed by the gate leakage current must be supplied and then must be removed from the chip as heat. In CMOS circuits the tunnelling current can flow and consume electrical power as long as there is a voltage difference between gate and channel, even when the drain is not drawing current. Oxide tunnelling is more important in n-type MOSFETs because the larger effective mass of holes in silicon reduces hole tunnelling. Extrapolation suggests that the continuation of miniaturization will lead to more power being dissipated in gate tunnelling than in the useful action of the chip.

The Roadmap regards the acceptable amount of gate leakage as  $1 \,\mathrm{A\,cm^{-2}}$  growing to  $100 \,\mathrm{A\,cm^{-2}}$  in 2016 (ITRS 2003). Figure 11 shows that this amount of leakage will be attained with oxide thickness in the range 1.6–1.8 nm for voltage in the range 0.5–1 V, expected to be used with present technologies. However, other authors relax this strict limit (Frank *et al* 2001), and the leakage that can be tolerated depends on the application. For example, the burden of excess power would be a larger disadvantage in a portable battery-powered system than in a fixed system.

In any case, there is a point at which action to control the gate leakage current becomes necessary. Simply not scaling the gate to smaller thicknesses is one route to managing gate tunnelling and is another reason for the failure of strict adherence to table 1 in device design. However, a larger thickness decreases  $C_{ox}$  and the smaller gate capacitance limits the control of the channel by the gate, illustrated by an increase in the subthreshold slope due to a lower  $C_{ox}$  in equation (2.1) and reducing the current in the on state.

Replacement of the SiO<sub>2</sub> with a material of higher dielectric constant (a concept abbreviated as high-K) is being pursued as the solution to the gate leakage problem. The high dielectric constant means that the insulator can be thicker for a given gate capacitance, maintaining the threshold slope (equation (2.1)) while presumably allowing exponentially less tunnelling current than the oxide. Resort to the high-K route with new materials is being pursued but presents new problems (Kingon *et al* 2000, Foerst *et al* 2004). A material with much higher dielectric constant than SiO<sub>2</sub> and a high bandgap that does not react with silicon or SiO<sub>2</sub> must be found. Retention of the high dielectric constant at the high frequencies involved in the switching of contemporary logic circuits is necessary. The additional requirements are compatibility with the gate electrode material, a high-quality interface with silicon and an ability to survive the high temperatures used in silicon processing. Oxides and silicates are chief candidates (Wong 2002).

The simple one-dimensional picture of high-K insulators must be replaced with a two-dimensional view when the thickness of the insulator approaches other physical lengths in a transistor. A detailed analysis of high-K insulators suggests some constraints on their application (Frank *et al* 1998, 2001) and shows that the physical thickness of the high-K material must be less than the thickness of the depleted layer in the substrate and concludes that dielectric constants larger than 20 are not likely to be useful.

4.3.4. Drain currents. Tunnelling currents may also be found in the substrate at small device dimensions. A positively biased drain with a p-type substrate forms a reverse-biased p-n junction that can carry a small reverse current in an n-type transistor. The more heavily doped the substrate, the narrower the depleted region between drain and substrate and the larger the drain-substrate current. A significant tunnelling current will flow if the depleted region is thin enough, and sufficiently high drain voltages can lead to reverse breakdown of the drain-substrate junction with large currents from drain to substrate. Miniaturization reduces the thickness of the potential barrier in the substrate between source and drain and there is a point at which it becomes thin enough to allow appreciable tunnelling through the barrier from source to drain.

Note also that the source–substrate–drain combination in figure 9 forms an npn configuration as in a bipolar transistor in which the reverse-biased drain collects electrons from the source. Bipolar transistor action with large source–drain currents independent of the gate may occur and combinations of biases that can cause bipolar action must be avoided.

4.3.5. Short channel experiments. The compendium of effects that may limit the progress of electronics to smaller dimensions is large enough to support the conviction that there is a limit. Yet it is complex enough to leave much doubt as to where to draw a line that represents the limit. Experience with some of the problems found by actually fabricating transistors with channel lengths far less than current practice, less than 30 nm, at present sheds additional light on the expected limitations.

Transistors with very short channel lengths, to below 10 nm, have been made and studied (Deleonibus *et al* 2000, Doris *et al* 2002, Doyle *et al* 2002, Bertrand *et al* 2004). Experimental fabrication methods, not necessarily adaptable to low-cost manufacturing, are needed for the very small dimensions involved. The channel lengths are smaller than the gate lengths, but at the smallest dimensions the determination of channel length is difficult and the definition somewhat arbitrary. The smallest, shortest gate length transistors worked, having true transistor characteristics. The ITRS Roadmap anticipates that 10 nm gate lengths will be produced starting in the year 2015 (ITRS 2003).

As expected, short channel effects are considerable in sub-30 nm transistors (Doyle *et al* 2002, Bertrand *et al* 2004). Limiting high electric field effects demands continual reduction of power supply voltages with these transistors, as suggested in table 1. DIBL of 100–200 mV per volt of drain voltage were found. Drain conductance increased. Subthreshold slopes were not extreme, 90 mV per decade. Oxide thicknesses are reduced to 1 nm or less, only six times the length of the Si–O bond in SiO<sub>2</sub>, to scale with other dimensions. Oxide tunnelling currents of  $10^3$  A cm<sup>-2</sup> are to be expected at these dimensions, implying that development of high-K dielectrics will be essential to progress into the sub-30 nm scale of gate lengths (Doyle *et al* 2002). Heavy substrate doping thins depleted layers but allows increased currents between drain and substrate.

Additional processing which tailors the doping of the substrate under the transistor to minimize the above undesirable effects associated with short gates was introduced long ago during the production of much larger devices. 'Channel engineering' refers to adding dopants to the substrate under the gate and the contacts to improve transistor characteristics. Short-channel effects, series resistance and threshold voltage are all affected (Thompson *et al* 1998, Gwoziecki *et al* 1999). Many compromises are involved in the design of the contacts to the source and the drain and their extensions. Implantation of ions at an angle with the gate as a mask creates 'halos' of heavier doping at the ends of the gate where the contacts meet the channel, extending the contacts under the gate. Normal to the surface the impurity concentration is made low near the channel in order to keep threshold voltages low and the concentration increases to a peak deeper into the substrate to maintain a barrier between the source and the drain. The effect of randomness on thresholds (section 4.1) can be alleviated as part of the adjustment of the depth dependence of the impurity concentration.

If the gate tunnelling can be controlled with new gate insulation, then leakage current between the source and the drain appears to be the most serious obstacle to extreme miniaturization. The experiments with very small transistors showed source—drain leakage currents in the off state increasing at something like the inverse sixth power of the gate length (Doyle *et al* 2002). Off state leakage compromises the operation of the transistor as a switch that is intended to turn the source—drain current on and off.

4.3.6. Mobility. Maintaining high mobility of the holes and electrons is another concern in the miniaturization of transistors. Reduction of mobility would lower the speed of device response and could negate the increase in performance that is one of the incentives for miniaturization. The confinement of the charge carriers in a thin channel near the surface renders them sensitive to scattering by the surface. Surface irregularities, charges trapped at the surface and in the insulator and vibrations of ions in the gate insulator can reduce mobility.