# Physical Scaling Limits of FinFET Structure: A Simulation Study

Gaurav Saini<sup>1</sup>, Ashwani K Rana<sup>2</sup>

Department of Electronics and Communication Engineering, National Institute of Technology Hamirpur, Hamirpur, India

<sup>1</sup>gaurav.nitham@gmail.com, <sup>2</sup>ashwani\_paper@yahoo.com

#### Abstract

In this work an attempt has been made to analyze the scaling limits of Double Gate (DG) underlap and Triple Gate (TG) overlap FinFET structure using 2D and 3D computer simulations respectively. To analyze the scaling limits of FinFET structure, simulations are performed using three variables: finthickness, fin-height and gate-length. From 2D simulation of DG FinFET, it is found that the gate-length (L) and fin-thickness ( $T_{fin}$ ) ratio plays a key role while deciding the performance of the device. Drain Induced Barrier Lowering (DIBL) and Subthreshold Swing (SS) increase abruptly when ( $L/T_{fin}$ ) ratio goes below 1.5. So, there will be a trade-off in between SCEs and on- current of the device since on-off current ratio is found to be high at small dimensions. From 3D simulation study on TG FinFET, It is found that both fin-thickness ( $T_{fin}$ ) and fin-height ( $H_{fin}$ ) can control the SCEs. However,  $T_{fin}$  is found to be more dominant parameter than  $H_{fin}$  while deciding the SCEs. DIBL and SS increase as ( $L_{eff}/T_{fin}$ ) ratio decreases. The ( $L_{eff}/T_{fin}$ ) ratio can be reduced below 1.5 unlike DG FinFET for the same SCEs. However, as this ratio approaches to 1, the SCEs can go beyond acceptable limits for TG FinFET structure. The relative ratio of  $H_{fin}$  and  $T_{fin}$  should be maximum at a given  $T_{fin}$  and  $L_{eff}$  to get maximum on-current per unit width. However, increasing  $H_{fin}$  degrades the fin stability and degrades SCEs.

#### Keywords

Double Gate, Triple Gate, Underlap, Overlap, FinFET, High performance (HP), ITRS

# 1.Introduction

As technologies are scaled down in deep sub-half micron regime, the conventional bulk MOSFET faces several challenges like higher DIBL, poor subtreshold swing collectively known as SCEs [1]. Moreover, the gate oxide thickness has been reached to its physical limit with the scaling i.e. below 1nm [2] and increasing gate leakage current is one of the most challenging tasks for future scaling. It seems impossible to further scale down the gate oxide beyond the inter-atomic distance. Future transistor scaling into the 21<sup>st</sup> century requires new solutions such as high-k gated dielectric materials and shallow, ultra low resistivity junctions need to be developed [3]. To sustain scaling for the next decade, non-conventional solutions are essentially required. Fully depleted Silicon-On-Insulator MOSFETs have received considerable attention in recent years because of their various advantages such as improved isolation, reduced subthreshold slope and parasitic capacitances and increased drive current. Today, SOI CMOS has entered the mainstream technology due to their improved performance and the availability of low cost SOI wafers. However, for the present generation FDSOI MOSFETs, the problems of increased SCE, poor carrier mobility due to high channel doping and high gate leakage current remain [4]. To overcome these limitations, several innovative multiple gates SOI structures such as Double Gate (DG) MOSFET [5], fully depleted lean channel transistor (DELTA) [6] FinFET [7-10], "Gate All Around" (GAA) MOSFET [11] and Pi-gate MOSFET [12] have been

DOI: 10.5121/vlsic.2011.2103

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.1, March 2011

proposed by various researchers. It is expected that sustained scaling during the next decade will see the evolution from the single gate (SG) conventional device to the multiple gate MOSFETs (MuGFETs) [4]. Double gate FinFET is a promising candidate because of its quasiplanar structure [8], excellent roll-off characteristics, drive current and it is close to its root, the conventional MOSFET in terms of layout and fabrication [7, 8]. FinFET structure shows less short channel effects than bulk MOSFET because of its self-aligned double gate [13] structure and hence good electrostatic integrity. FinFETs have been demonstrated with both overlap and underlap regions structures [14, 15]. FinFETs with graded or abrupt gate overlaps gives a higher I<sub>off</sub> as the technologies are scaled down in deep sub-half micron regime [16], because of this, the underlap structure with optimized doping profile in the underlap regions received a considerable attention in the recent years [16, 17, 18]. The rest of the paper is organized as follows - In section-2, device structure under investigation is presented, and section-3 describes the results followed by conclusion in section-4.

# **2.Device Structure**

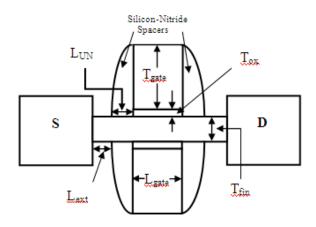

Fig. 1 shows the DG FinFET structure realized using Setaurus TCAD tool suite [19]. Table I shows the critical device parameters used to fabricate DG underlap FinFET structure given by ITRS [2] for high performance multigate devices for the year of 2015. Based on this specification DG FinFET underlap structure are fabricated and a comparison has been made to analyze the scaling limits. Spacer underlap length ( $L_{UN}$ ) and source/drain exertion regions ( $L_{ext}$ ) are kept at 10nm each in order to obtain a good On-off current ratio. Gaussian doping profile is used in underlap regions.

Fig.1 2D Double Gate (DG) FINFET Structure

Table 1 ITRS Projections For High Performance Mg Devices In The Year 2015 [2]

| Device Parameters used for DG FinFET   | ITRS 2009 Projection |

|----------------------------------------|----------------------|

| Lg: Physical Gate                      | 17 nm                |

| EOT: equivalent oxide thickness        | 0.77 nm              |

| V <sub>dd</sub> : Power supply voltage | 0.81 V               |

| Body Thickness                         | 8 nm                 |

The Gaussian profile is selected in order to obtain a fall in doping concentration from  $10^{20}$  cm<sup>-3</sup> at the source/drain to  $10^{16}$  cm<sup>-3</sup> at the gate edges. The doping density of source, drain and source/drain extensions are kept at  $10^{20}$  cm<sup>-3</sup> while channel is doped with a doping concentration of  $10^{15}$  cm<sup>-3</sup> in order to achieve high mobility in the channel [20]. Workfuction of gate material is adjusted to 4.51 eV in order to analyze the effects of gate dielectric constant variation. Table II shows the critical device parameters used to fabricate TG overlap FinFET structure. Some parameters follows the ITRS specification and some are user define. The Gaussian profile was selected for doping in source, drain and overlap regions. The simulations are performed using the Sentaurus design suite [19] with the drift-diffusion mobility, density-gradient quantum correction modes being turned on for 2D. Hydrodynamic model is used in addition to drift-diffusion mobility and density-gradient quantum correction modes for 3D.

| Device Parameters                        | Values        |

|------------------------------------------|---------------|

| Lg: Physical Gate-length                 | 47 nm         |

| L <sub>eff</sub> : Effective Gate-length | 37 nm         |

| Source and Drain overlaps                | 5 nm each     |

| EOT: equivalent oxide thickness          | 1.5 nm        |

| V <sub>dd</sub> : Power supply voltage   | 1V            |

| Lateral steepness of profile             | 3.2 nm/decade |

| Gate Workfunction                        | 4.46 eV       |

| T <sub>fin</sub>                         | 5-30 nm       |

| H <sub>fin</sub>                         | 5-30 nm       |

Table 2

Device Parameters Used For TG FinFET

# **3.Results and Discussion**

#### 3.1 Effects of gate-length variation on DG FinFET structure

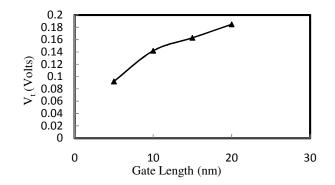

Fig. 3 depicts threshold voltage variation with the gate-length. DG underlap FinFET shows a well known effect "Threshold voltage roll-off". The distance between drain and source reduces with the gate-length and hence the channel potential is now more pronounced to the drain electric field. So, the gate potential required to invert the channel is reduced because of the drain electric field encroachment on the channel region increases with decreased gate-length.

Fig. 2 Threshold voltage variation with gate-length

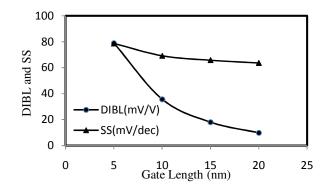

Fig. 3 Short Channel Effects variation with gate-length

Fig.3 depicts Short Channel Effects (SCEs) variation with the gate-length. DIBL increases very sharply with decreased gate-length. The drain electric field encroachment on channel region increases at shorter gate-lengths. Subthreshold swing also increases with decreased gate-length. The gate now has less control over channel in subthreshold region because of the channel barrier potential is now controlled by the drain potential also.

#### 3.2 Effects of fin-thickness variation on DG FinFET structure

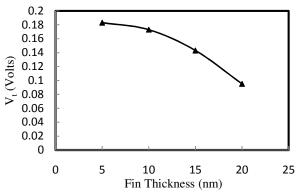

Fig. 4 shows the threshold voltage variation with the fin-thickness. Threshold voltage reduces with increased fin-thickness. At shorter channel lengths, the surface potential depends not only on capacitive coupling between the gate and the channel region but also on the capacitance of source/fin and drain/fin junction. As the fin-thickness increases, the width of the source/fin and drain/fin depletion region increases, which decreases the source/fin and drain/fin junction capacitances, as a result the gate to surface potential coupling increases [24] and hence the threshold voltage decreases with the increased film thickness.

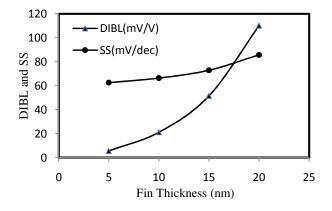

Fig.5 shows Short Channel Effects (SCEs) variation with fin-thickness. Fin-thickness plays a very important role while deciding SCEs. DIBL increases with increased fin-thickness. Drain electric field lowers the barrier of channel in case of thick silicon film devices because of reduced source/fin and drain/fin junction capacitances. Subthreshold swing also increases with

fin-thickness. The reason behind this is the gate control over channel region degrades with increased channel volume at constant drain and source proximity.

Fig. 4 Threshold voltage variation with fin-thickness

Fig. 5 Short Channel Effects variation with fin-thickness

#### **3.3 Scaling limits of DG FinFET structure**

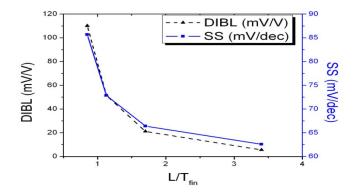

Fig. 6 shows the effect of the ratio of gate-length (L) and fin-thickness ( $T_{fin}$ ) on DIBL. This ratio limits the scaling of DG FinFET structure. DIBL and subthreshold swing (SS) increases abruptly when the L/T<sub>fin</sub> ratio fall below1.5. This ratio is a most important factor which decides the short channel effects. For DG FinFET structure fin-thickness could be a dominating factor which decides the scaling capabilities.

Fig. 6 Short Channel Effects variation with  $(L/T_{fin})$  ratio

## 3.4 Effects of fin-thickness variation on TG FinFET structure

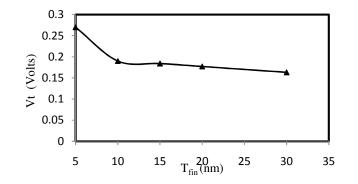

Fig. 7 depicts the threshold voltage variation with the fin-thickness. Threshold voltage reduces with fin-thickness. The drain electric field lowers the channel barrier as we increases fin-thickness because the channel area under the buried oxide (BOX) increases and hence drain electric field induce more inversion charge at the bottom of silicon fin. There is a sharp rise in the threshold voltage from 10nm to 5nm fin-thickness. It may be due to quantum mechanical effects because below 10nm quantum effects dominates and cannot be neglected [25].

Fig. 7 Threshold voltage variation with the fin-thickness at 30nm of H<sub>fin</sub>

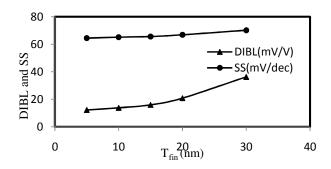

Fig. 8 Short Channel Effects variation with fin-thickness at 30nm of  $H_{fin}$

Fig. 8 shows SCEs variation with the fin-thickness. DIBL increases with fin-thickness. The drain electric field lowers the channel barrier as we increases fin-thickness because the channel area under the BOX increases and hence drain electric field coupling with the channel increases. Subthreshold swing also increases with fin-thickness. The reason is same as explained above. The major portion of subthreshold current flows through the bottom layer of silicon fin because of DIBL.

#### 3.5 Effects of fin-heights variation on TG FinFET structure

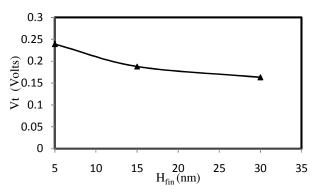

Fig.9 depicts the threshold voltage variation with the fin-height. Threshold voltage reduces with fin-height. At shorter channel lengths, the surface potential depends not only on capacitive coupling between the gate and the channel region but also on the capacitance of source/fin and drain/fin junction. As the fin-height increases, the width of the source/fin and drain/fin depletion region increases, which decreases the source/fin and drain/fin junction capacitances, as a result the gate to surface potential coupling increases and hence the threshold voltage decreases with increased fin-height.

Fig. 9 Threshold voltage variation with the fin-height at 30nm of  $T_{fin}$

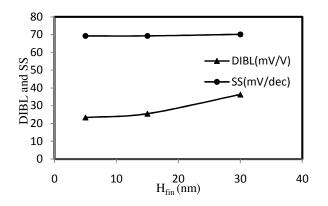

Fig. 10 Short Channel Effects variation with fin-height at 30nm of  $T_{fin}$

Fig. 10 shows SCEs variation with the fin-height. DIBL increases with the fin-height. The drain electric field lowers the channel barrier as we increases fin-height. Subthreshold swing also increases with fin-height. Gate loses its control over the channel with increased fin-height.

#### **3.6 Scaling limits of TG FinFET structure**

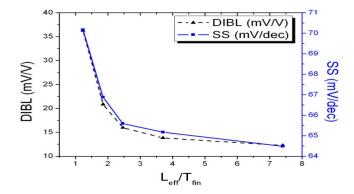

Fig. 11 shows the effects of the ratio of effective gate-length ( $L_{eff}$ ) and fin-thickness ( $T_{fin}$ ) on SCEs. DIBL and subthreshold swing (SS) increases as ( $L_{eff}/T_{fin}$ ) ratio decreases. This ratio can be reduced to less than 1.5 unlike DG FinFET for the same SCEs. However, as this ratio approaches to 1 value the SCEs can go beyond acceptable limits. So, the scaling capabilities of TG FinFET structure is more than that of DG FinFET structure.

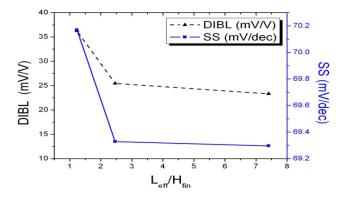

Fig. 12 shows the effects of the ratio of effective gate-length ( $L_{eff}$ ) and fin-height ( $H_{fin}$ ) on SCEs. DIBL and subthreshold swing (SS) increases as ( $L_{eff}/T_{fin}$ ) ratio decreases, however, the increment is less than that with the ratio ( $H_{eff}/T_{fin}$ ). The reason behind this is that the fin-thickness is more prone to the SCEs than the fin-height. Fin-height can be increased to achieve higher on-current than that of fin-thickness with an acceptable value of SCEs.

Fig. 11 Effects of  $(L_{eff}/T_{fin})$  ratio variation on SCEs at 30nm of  $H_{fin}$

Fig. 12 Effects of  $(L_{eff}/H_{fin})$  ratio variation on SCEs at 30nm of  $T_{fin}$

## 4.Conclusions

In this work, the scaling capabilities of DG and TG FinFET devices are analyzed using 2D and 3D simulation respectively. The ( $L_{eff}/T_{fin}$ ) ratio limits the scaling capabilities FinFET structure. This ratio is found to be less in case of TG FinFET structure for acceptable SCEs. Simulation

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.1, March 2011

results shows that TG FinFET structure is more scalable than that of DG FinFET structure. The relative ratio of  $H_{fin}$  and  $T_{fin}$  should be maximum at a given  $T_{fin}$  and  $L_{eff}$  to get maximum oncurrent per unit width. However, increasing  $H_{fin}$  degrades the fin stability, increases the difficulty of gate patterning and degrades SCEs. Carefully optimization of  $T_{fin}$  and  $H_{fin}$  is essentially required to get a good performance for scaled FinFET structure at a given gate length.

# 5.Acknowledgement

The authors would like to thank the Department of Electronics and Communication Engineering, National Institute of Technology Hamirpur (HP), Ministry of Communication and Information Technology (MCIT), Department of Science and Technology, Government of India for providing the advanced simulation tools.

# **6.References**

- E. J. Nowak, I. Aller, T. Ludwig, K. Kim, R. V. Joshi, C.-T. Chuang, K. Bernstein, and R. Puri, "Turning silicon on its edge [double gate CMOS/FinFET technology]," *IEEE Circuits Devices Mag.*, vol. 20, no.1, pp. 20–31, Jan. /Feb. 2004.

- [2] http://www.itrs.net/2009 updates.

- [3] Scott Thompson et al., "MOS Scaling: Transistor Challenges for the 21st Century," Intel Technology Journal Q3'98.

- [4] Multiple Gate MOSFETs: The Road to the Future, Amitava DasGupta, 978-1-4244-1728-5/07, 2007 IEEE.

- [5] T. Sekigawa and Y. Hayashi, "Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate," *Solid-State Electronics* 27, 827 (1984).

- [6] D. Hisamoto, T. Kaga, Y. Kawamoto, E. Takeda, "A fully depleted lean channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET," *Technical Digest of IEDM*, 833 (1989).

- [7] Xuejue Huang, Wen-Chin Lee, C. Kuo, D. Hisamoto, Leland Chang, J.Kedzierski, E. Anderson, H. Takeuchi, Yang-Kyu Choi, K. Asano, V.Subramanian, Tsu-Jae King, J. Bokor, Chenming Hu, "Sub 50-nm FinFET:PMOS," *Technical Digest of IEDM*, 67 (1999).

- [8] D.Hisamoto, W.C. Lee, J.Keidzerski, H.Takeuchi, K.Asano, C.Kuo. T.J.King, J.Bokor and C.Hu, "FinFET-a self-aligned double-gate MOSFET scalable beyond 20 nm," *IEEE Trans.Electron Devices*, vol.47, pp. 2320-2325, Dec. 2000.

- [9] Bin Yu, Leland Chang, S. Ahmed, Haihong Wang, S. Bell, Chih-Yuh Yang, C. Tabery, Chau Ho, Qi Xiang, Tsu-Jae King, J. Bokor, Chenming Hu, Ming-Ren Lin, D. Kyser, "FinFET scaling to 10 nm gate-length," *Technical Digest of IEDM*, 251 (2002).

- [10] Yang-Kyu Choi, "FinFET for Terabit era," *Journal of Semiconductor Technology and Science* 4-1, 1 (2004).

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.1, March 2011

- [11] J.P. Colinge, M.H. Gao, A. Romano, H. Maes, C. Claeys, "Silicon-on insulator 'gate-all-around' MOS device," *Technical Digest of IEDM*, 595, 1990.

- J.T. Park, J.P.Colinge and C.H. Diaz, "Pi-Gate SOI MOSFET", *IEEE Electron Device Letters*, vol. 22, pp. 405-406, Aug. 2001.

- [13] J.P. Colinge, "Multi-gate SOI MOSFETs," *Microelectronic Engineering*, vol.84, issues 9-10, pp. 2071-2076, Sept-Oct, 2007.

- [14] H.-S. P. Wong, K. K. Chan, and Y. Taur, "Self-aligned (top and bottom) double-gateMOSFET with a 25 nm thick silicon channel," *IEDM Tech.Dig.*, Dec. 1997, pp.427–430.

- [15] . Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y.-K.Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Sub-50 nm p-channel FinFET," *IEEE Trans. Electron Devices*, vol. 48, no. 5, pp. 880–886, May 2001.

- [16] V. Trivedi, J. G. Fossum, and M. M. Chowdhury, "Nanoscale FinFETs with gate-source/drain underlaps," *IEEE Trans. Electron Devices*, vol. 52, no. 1, pp. 56–62, Jan. 2005.

- [17] J. Kedzierski, M. Ieong, E. Nowak, T. S. Kanarsky, Y. Zhang, R. Roy, D. Boyd, D. Fried, and H.-S. P.Wong, "Extension and source/drain design for high-performance FinFET devices," *IEEE Trans. Electron Devices*, vol. 50, no. 4, pp. 952–958, Apr. 2003.

- [18] Angada B. Sachid et al., "Gate Fringe-Induced Barrier Lowering in Underlap FinFET Structures and Its Optimization," *IEEE Electron Device Letters*, Vol. 29, No. 1, January 2008.

- [19] Sentaurus Device User Guide Version:A-2008.09, Synopsys Inc.

- [20] D. S. Havaldar, G. Katti, N. DasGupta, and A. DasGupta, "Subthreshold current model of FinFETs Based on analytical solution of 3-D Poisson's equation," *IEEE Trans. Electron Devices*, vol. 53, no. 4, pp. 737–742, Apr. 2006.

- [21] Kedzierski J, Ieong M, Kanarsky T, Zhang Y and Wong H-S P 2004, "Fabrication of metal gated FinFETs through complete gate silicidation with Ni," *IEEE Trans. Electron Devices*, 51 2115–20.

- [22] Meng-Hsueh Chiang, C heng-Nang Lin and Guan-Shyan Lin, "Threshold voltage sensitivity to doping density in extremely scaled MOSFETs," *Semicond. Sci. Technol.* 21 (2006) 190–193.

- [23] Wenwei Yang, Zhiping Yu and Lilin Tian, "Scaling Theory for FinFETs Based on 3-D Effects Investigation," *IEEE Transactions on Electron Devices*, Vol. 54, No. 5, May 2007.

- [24] J.T. Park and J.P.Colinge, "Multiple-Gate SOI MOSFETs: DeviceDesign Guidelines", IEEE Trans. Electron Devices, vol. 49, pp.2222 -2229, Dec. 2002.

- [25] J.P. Coling, "FinFET and other multigate transistors," Springer, e-ISBN 978-0-387-71752-4, 2007.