## Program memory Consideration & Addressing Modes

# **Memory Organization**

- Program Memory

- Register File Memory

# **Program Memory**

- Used for storing compiled code

- Each location is 14 bits long

- Every instruction is coded as a 14 bit word

- Addresses H'000' and H'004' are treated in a special way

- PC can address up to 8K addresses

# **Register File Memory**

- Consist of 2 Components

- General Purpose Register (GPR) Files (RAM)

- Special Purpose Register (SPR) files

- This portion of memory is separated into banks of 128 bytes long

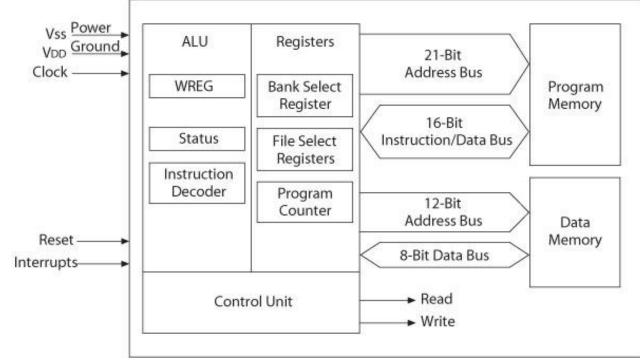

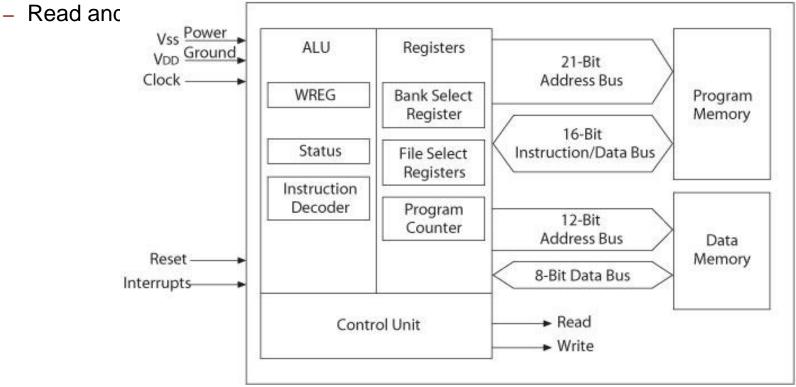

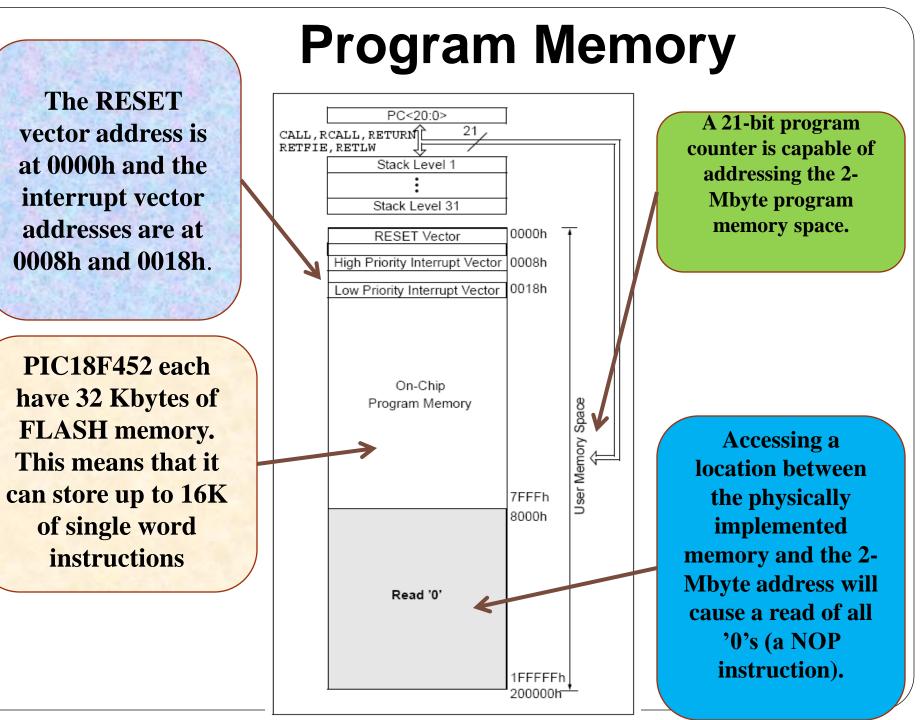

### PIC18F - Address Buses

- Address bus

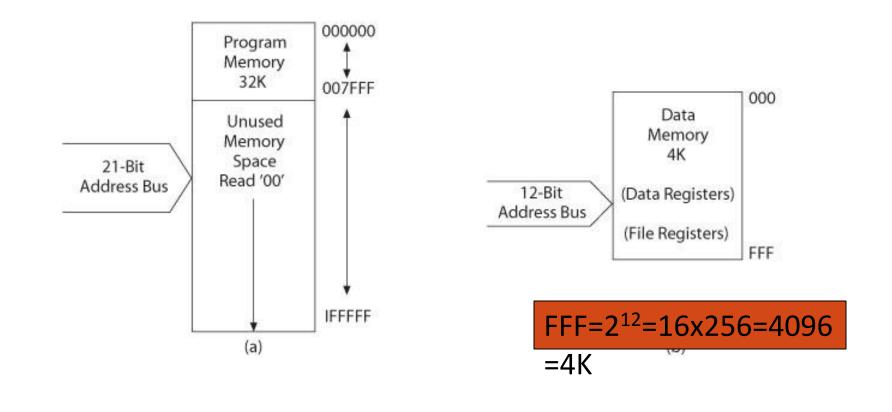

- 21-bit address bus for program memory addressing capacity: 2 MB of memory

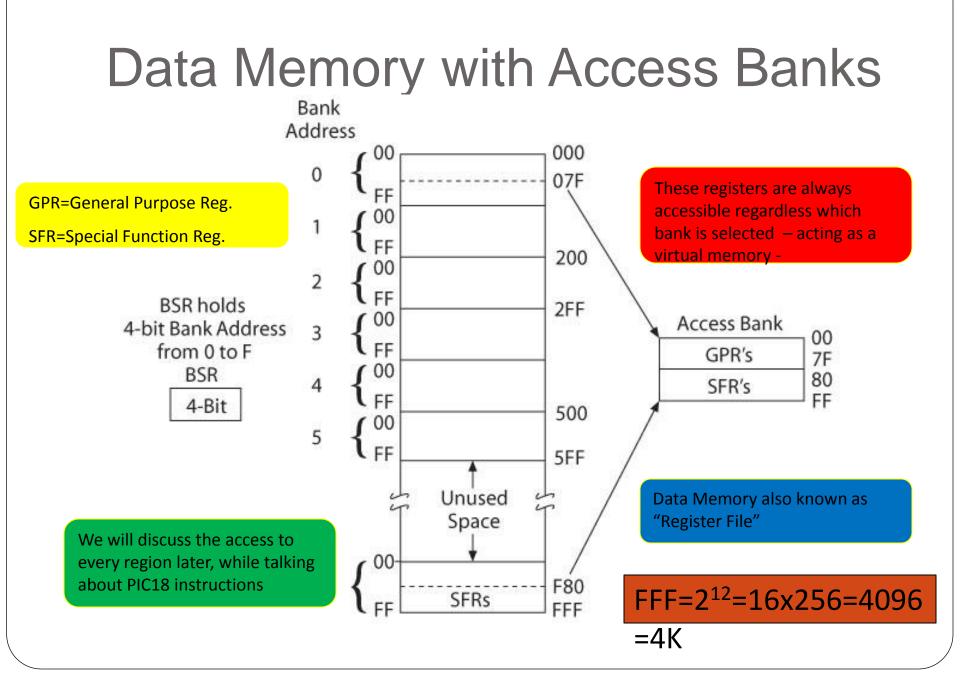

- 12-bit address bus for data memory addressing capacity: 4 KB of memory

# Data Bus and Control Signals

#### Data bus

- 16-bit instruction/data bus for program memory

- 8-bit data bus for data memory

- Control signals

### PIC18F452/4520 Memory

- Program memory with addresses (Flash)

- Data memory with addresses

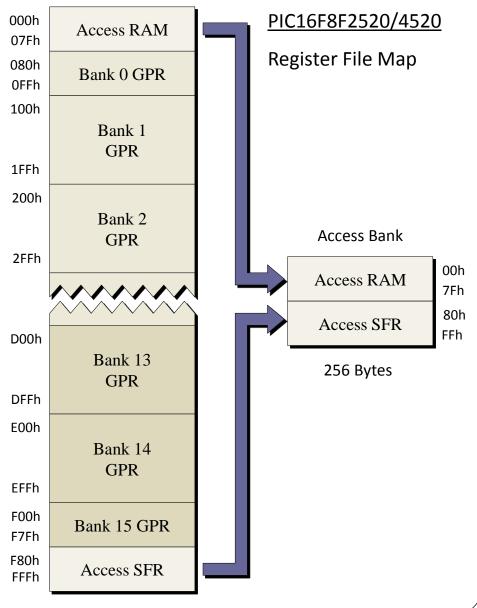

# Data Memory Organization

- Data Memory up to 4k bytes

- Divided into 256 byte banks

- Half of bank 0 and half of bank 15 form a virtual bank that is accessible no matter which bank is selected

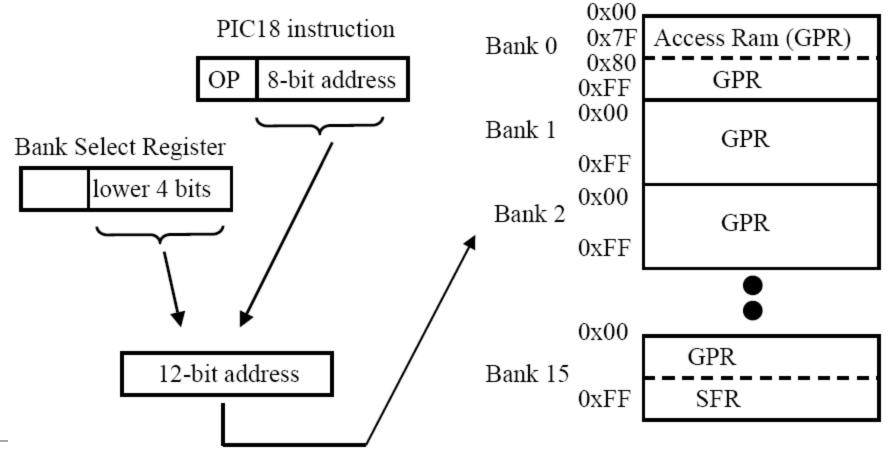

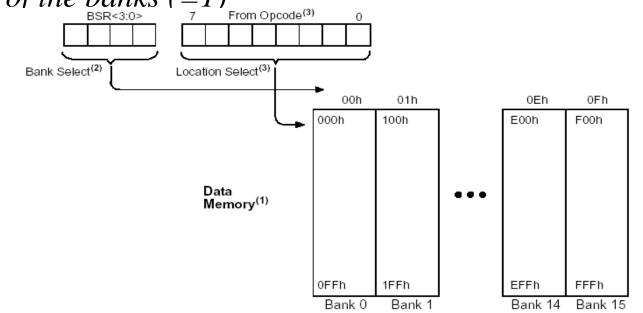

# Accessing Data Memory

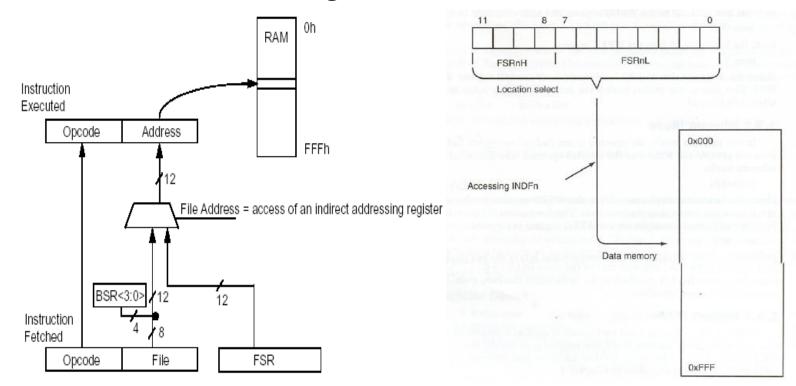

The machine code for a PIC18 instruction has only 8 bits for a data memory address which needs 12 bits. The Bank Select Register (BSR) supplies the other 4

- Direct Addressing Operand address(es) embedded in the opcode

- 8 bits of the 16-bit instruction specify any one of 256 locations

- □ The 9<sup>th</sup> bit specifies either the *Access Bank* (=0) or *one* of the banks (=1)

Direct Addressing Examples

Direct addressing (banked)

movlb 02;set BSR to Bank 2addwf 0x55, W, BANKED; add WREG with the content of; addr. 55 (f=55) in bank 2 (a=1),; save the result to WREG (d=0)

Operand is the content of data memory at add. 0x255

Mnemonic in MPASM:A (a=0) - the access bank;BANKED (a=1) - bankedW (d=0) - the WREG register; F (d=1) - the data register

> Direct Addressing Examples

Direct addressing (using access bank)

addwf 0x55, F, A

;movlb not required

- ; add WREG to content of

- ; addr. 55 (f=55) in access

- ; bank (a=0), save the result

; in the data memory at the ;address 0x55 (d=0)

Operand is the content of data memory add. 0x055

#### > Indirect Addressing

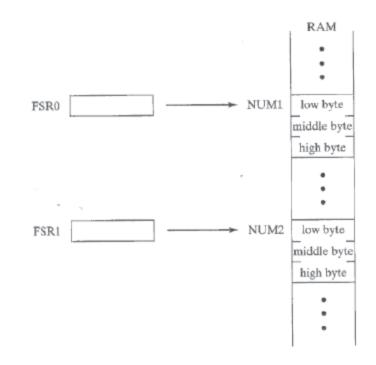

- 3 File Select Registers (FSR) as a pointer to the data memory location that is to be read or

- written. 1. FSR0: composed of FSR0H:FSR0L

- 2. FSR1: composed of FSR1H:FSR1L

- 3. FSR2: composed of FSR2H:FSR2L

- Each FSR has an INDF register associated with it

- □ The INDF<sub>n</sub> register is not a physical register. Addressing INDF<sub>n</sub> actually addresses the register whose address is contained in the FSR<sub>n</sub> register.

#### > Indirect Addressing

LFSR 02, num1 ;load FSR2 with the add. of num1 MOVWF INDF2, W ; move WREG to the register ; pointed by FSR2

#### > Indirect Addressing Operations

| Pointer registers                                                                                          | Operand names                         |                                         |                                         |                                      |                                                       |

|------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------------|-------------------------------------------------------|

| MEASUREMENT                                                                                                | Access and<br>leave FSRi<br>unchanged | Access and<br>then<br>decrement<br>FSRi | Access and<br>then<br>increment<br>FSRi | Increment<br>FSRi and<br>then access | Temporarily<br>add WREG<br>to FSRi and<br>then access |

| $\begin{array}{c c} FSR0H & FSR0L \\ FSR0 & & \\ \hline & & \\ 11 & 8 & 7 & 0 \end{array} \longrightarrow$ | INDF0<br>7 0                          | POSTDEC0<br>7 0                         |                                         | PREINC0 7 0                          | PLUSW0<br>7 0                                         |

| $FSR1 \longrightarrow 11 87 0$                                                                             | INDF1<br><br>7 0                      | POSTDEC1 7 0                            | POSTINC1 7 0                            | PREINC1 7 0                          | PLUSW1 7 0                                            |

| $FSR2 \longrightarrow 11 87 0$                                                                             | INDF2<br><br>7 0                      | POSTDEC2 7 0                            | POSTINC2<br>7 0                         | PREINC2 7 0                          | PLUSW2<br>7 0                                         |

#### > Indirect Addressing Example

count set 0x02 lfsr 0, num1 lfsr 1, num2 movlw 3 movwf count, A bcf STATUS, c Again: movf POSTINC1, W addwfc POSTINC0, F decfsz count, 1 bra Again

#### SFRs Examples

|        | 1     |         |       |

|--------|-------|---------|-------|

| Port A | 0xF80 | SPBRG   | 0xFAF |

| Port B | 0xF81 |         |       |

| Port C | 0xF82 | Timer1L | 0xFCE |

| Port D | 0xF83 | Timer1H | 0xFCF |

| Port E | 0xF84 |         |       |

|        |       | Timer0L | 0xFD6 |

| Tris A | 0xF92 | Timer0H | 0xFD7 |

| Tris B | 0xF93 |         |       |

| Tris C | 0xF94 | Wreg    | 0xFE8 |

| Tris D | 0xF95 |         |       |

| Tris E | 0xF96 | StkPtr  | 0xFFC |

# I/O Ports

### PIC18F452 I/O Ports

- Five I/O ports

- PORT A through PORT E

- Most I/O pins are multiplexed

- Generally have eight I/O pins with a few exceptions

- Addresses already assigned to these ports in the design stage

- Each port is identified by its assigned SFR

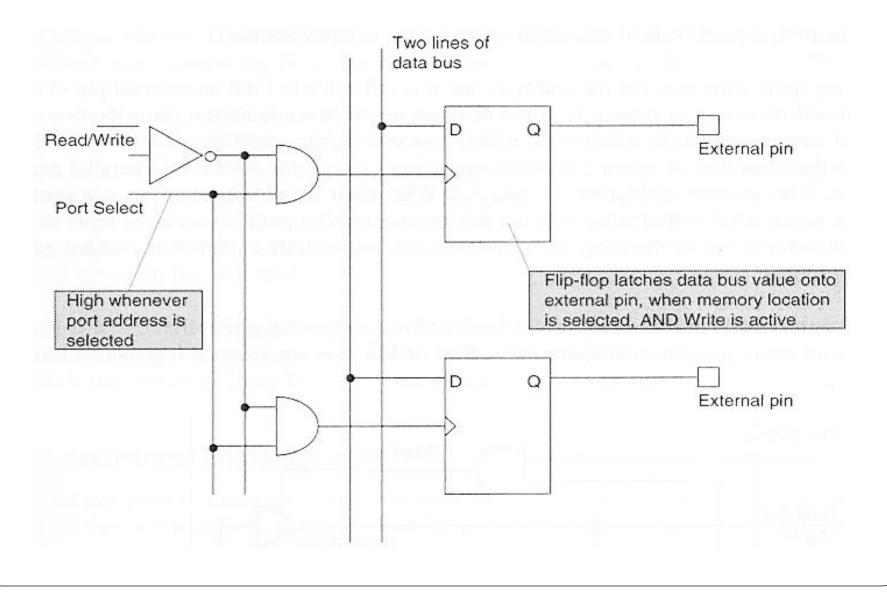

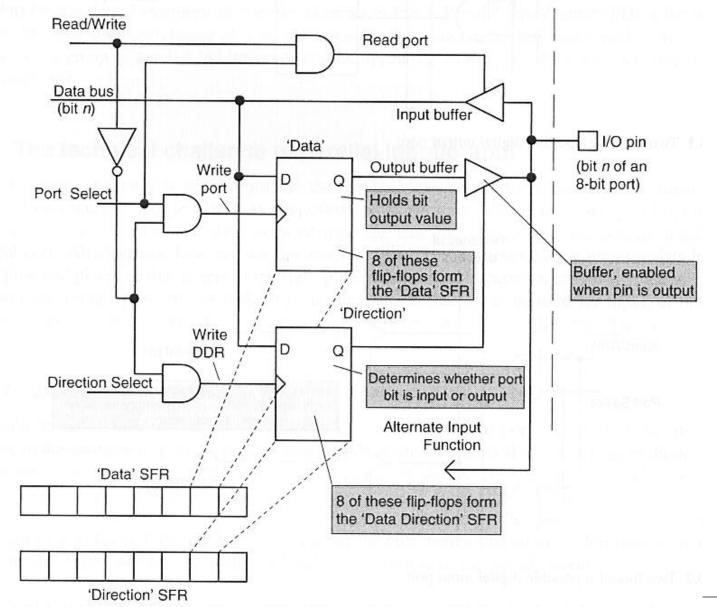

#### Parallel I/O Output Structure

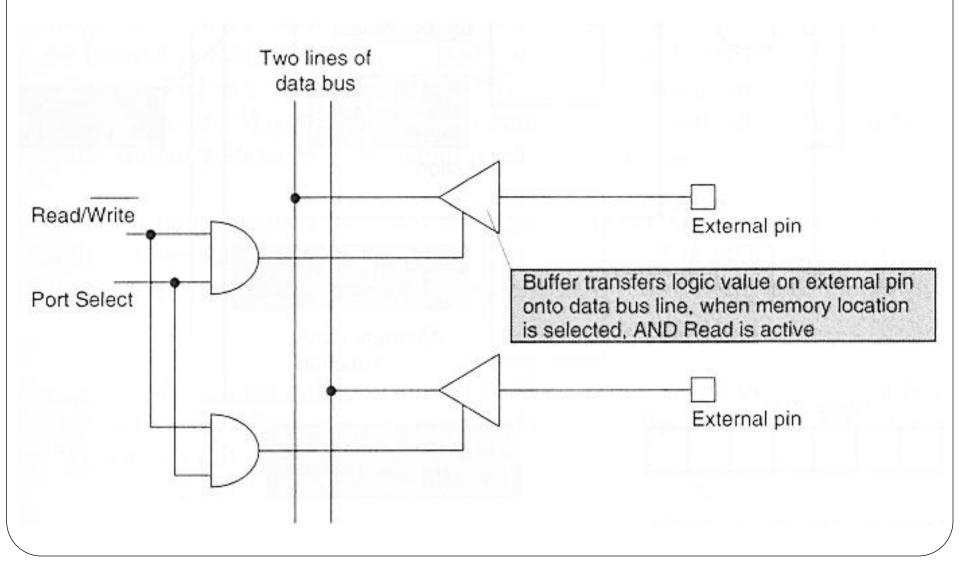

# Parallel I/O Input Structure

#### Parallel I/O Combined I/O Structure

#### Parallel I/O ports Main Features

- Simple memory mapped access

- Can be configured through software as either input or output

- Ability to set or reset individual bits

- Can have internal pull-ups

- Can drive small loads like LEDs

- Can be multifunction

- Different capability for pins (i.e. larger current)

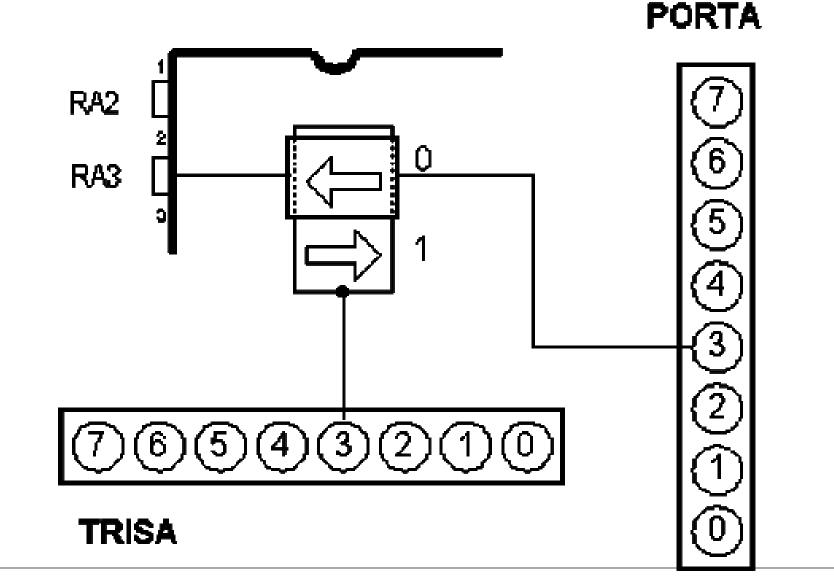

# Parallel I/O ports

- For most ports, the I/O pin's direction (input or output) is controlled by the data direction register TRISx (x=A,B,C,D,E): a '1' in the TRIS bit corresponds to that pin being an input, while a '0' corresponds to that pin being an output

- The PORTx register is the latch for the data to be output. Reading PORTx register read the status of the pins, whereas writing to it will write to the port latch.

- Example: Initializing PORTB (PORTB is an 8-bit port. Each pin is individually configurable as an input or output).

- bcfSTATUS, RP0; select bank0bcfSTATUS, RP1;clrfPORTB; clear PORTB output data latchesbsfSTATUS, RP0; select bank1movlw0xCF; value used to initialize data direction

movwf TRISB

; PORTB<7:6>=inputs, PORTB<5:4>=outputs,

; PORTB<3:0>=inputs

# Relationship between TRIS and PORT Registers

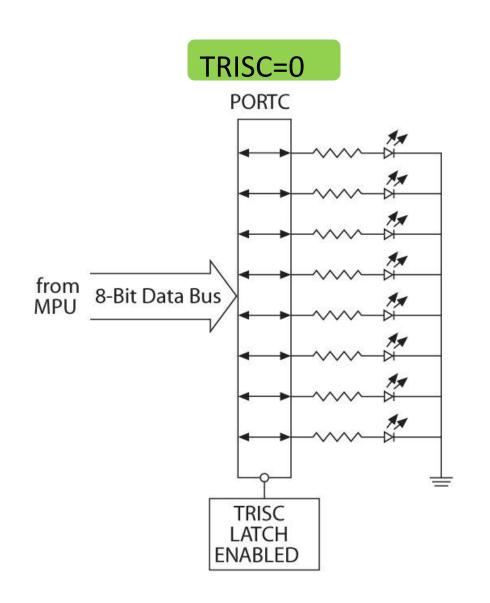

# Illustration: Displaying a Byte at an I/O Port (1 of 5)

- Problem statement:

- Write instructions to light up alternate LEDs at PORTC.

- Hardware:

- PORTC

- bidirectional (input or output) port; should be setup as output port for display

- Logic 1 will turn on an LED in Figure 2.10.

Illustration (2 of 5)

- Interfacing LEDs to PORTC

- Port C is F82H

- Note that PORT C is set to be an output!

- Hence, TRISC (address 94H) has to be set to 0

#### Illustration (3 of 5)

- Program (software)

- Logic 0 to TRISC sets up PORTC as an output port

- Byte 55H turns on alternate LEDs

- MOVLW 00 ;Load W register with 0

- MOVWF TRISC, 0

- MOVLW 0x55

- MOVWF PORTC,0

- ;Set up PORTC as output

- ;Byte 55H to turn on LEDS

- ;Turn on LEDs

- SLEEP ;Power down

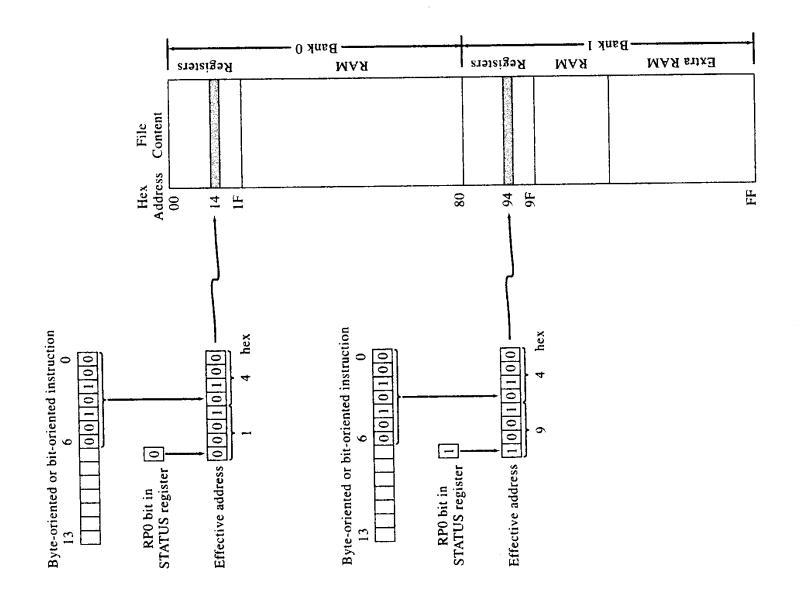

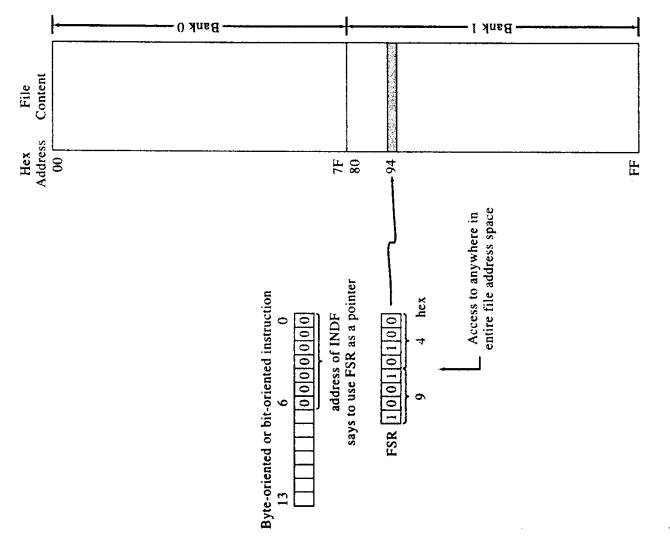

## **Register Addressing Modes**

There are 3 types of addressing modes in PIC

Immediate Addressing

Movlw H'0F'

Direct Addressing

Indirect Addressing

# **Direct Addressing**

- Uses 7 bits of 14 bit instruction to identify a register file address

- 8<sup>th</sup> and 9<sup>th</sup> bit comes from RP0 and RP1 bits of STATUS register.

- Exp:

- Zequ D'2'

btfss STATUS, Z

Figure 6 Direct addressing mode.

# Indirect Addressing

- Full 8 bit register address is written the special function register FSR

- INDF is used to get the content of the address pointed by FSR

- Exp : A sample program to clear RAM locations H'20' – H'2F'.

# Some CPU Registers

- STATUS

- PC

- W

- PCL

- PCLATH

### Instruction Set

- Every Instruction is coded in a 14 bit word

- Each instruction takes one cycle to execute

- Only 35 instructions to learn (RISC)

#### Instruction Set

- Uses 7 bits of 14 bit instruction to identify register file address

- For most instructions, W register is used as a source register

- The result of an operation can be stored back to the W register or back to source register

### Some Arithmetic Operations

- addwf FSR, w ; Add w to FSR and put result in w

- iorwf TMR0, f; Inclusive OR w with TMR0 and store result in TMR0

- addwf reg ; Add content of the reg to content of the w and store the result back into reg (source)