# Prospect for the memory Packaging technology

Nam-Seog Kim, Ph.D.

Vice President, P&T Technology Group SK hynix Inc.

## Agenda

- 1. Electronic Packaging Trend

- 2. Memory Packaging Roadmap

- 3. Innovative Packaging Technology

- Package

- Process

- Material

- 4. Conclusion

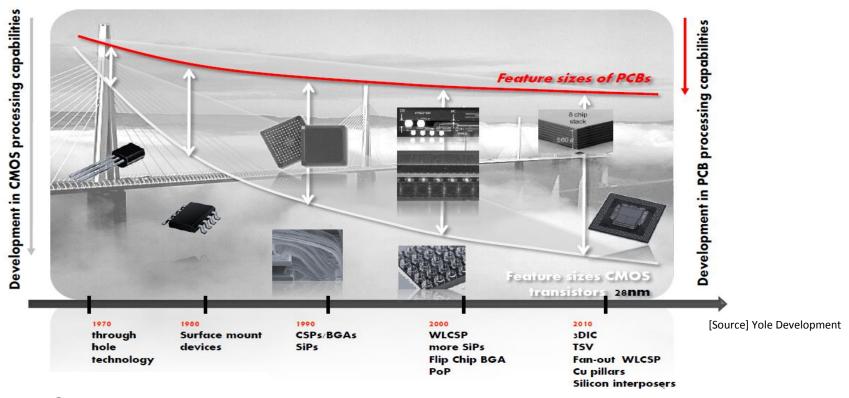

### **Electronic Packaging Development Trend**

Packaging technology is developing to compensate the technology gap between Si and PCB tech.

- O Bridging the gap between Si and PCB process capabilities

- High I/O & speed : PGA → FBGA → Flip Chip → WLP/TSV

- O Improvement by the high functionality of IT application

- High Density & Functionality, High thermal dissipation.

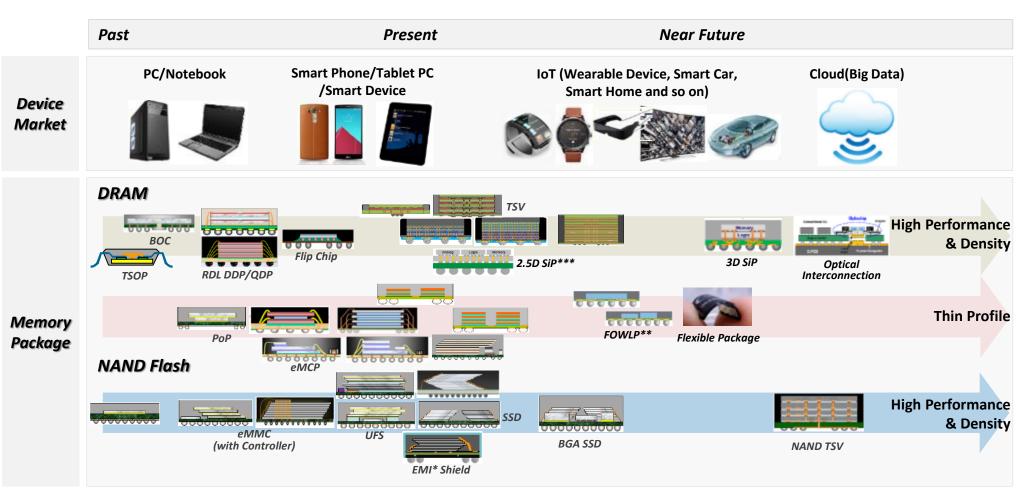

### **Memory Packaging Roadmap**

## Flip chip and TSV/WLCSP are promising technologies to satisfy faster speed, wider bandwidth and smaller/thinner package

<sup>\*</sup>EMI: Electro Magnetic Interference

<sup>\*\*</sup>FOWLP: Fan-out Wafer Level Package

<sup>\*\*\*</sup>SiP: System in Package

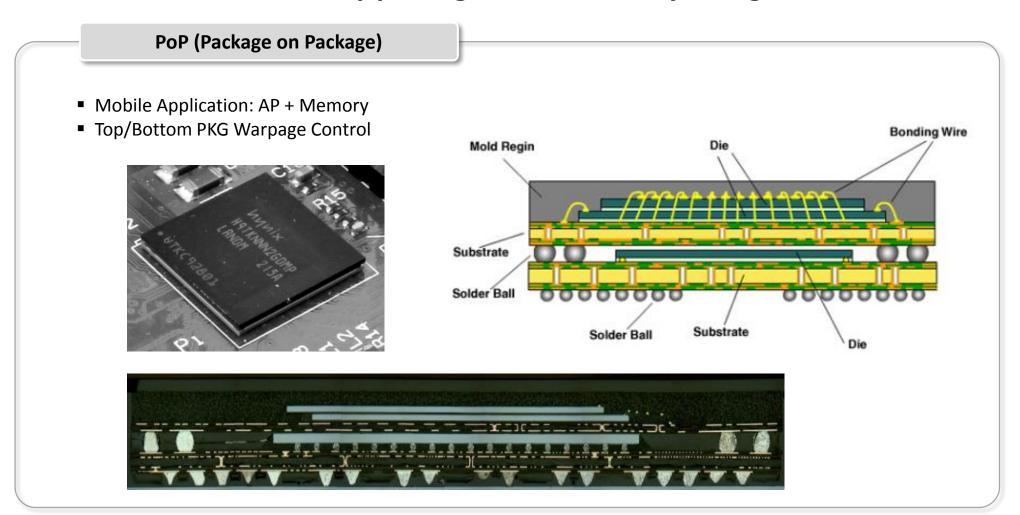

1 Package Stack

AP & Memory package stack is widely being used.

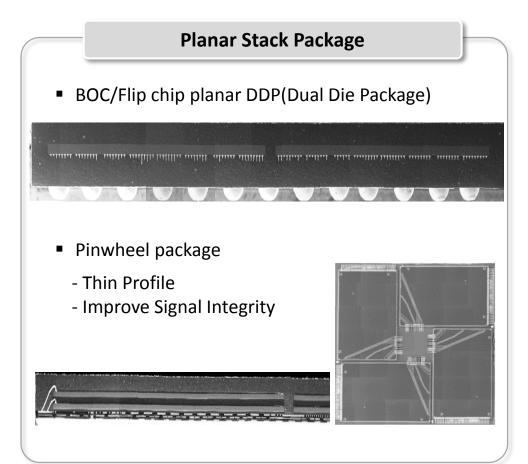

2 Chip Stack (Planar)

Planar chip stack is driven by low cost and high density requirement 2.5D SiP is a suitable solution to place memory dies near SoC

#### **2.5D SiP**

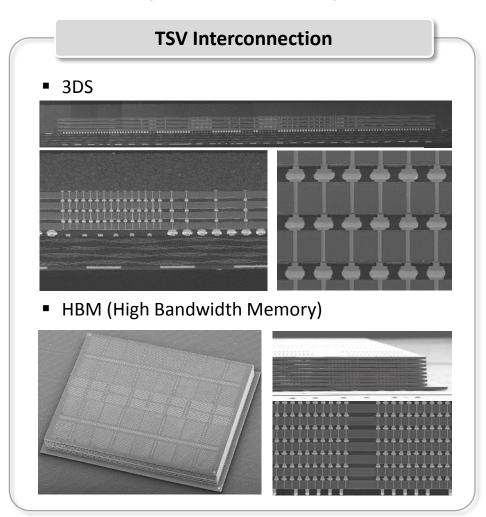

- SoC + 2/4/8 HBMs(High Bandwidth Memory) on interposer

- Various structures : CoCoS, CoWoS (TSMC), EMIB (Intel)

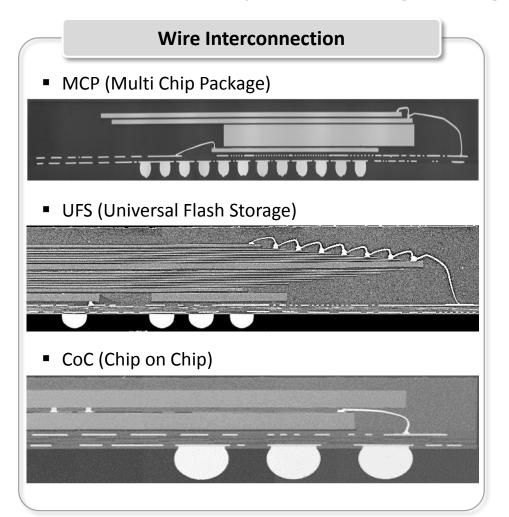

② Chip Stack (Vertical)

#### Conventional chip stack using wiring and TSV chip stack are implemented

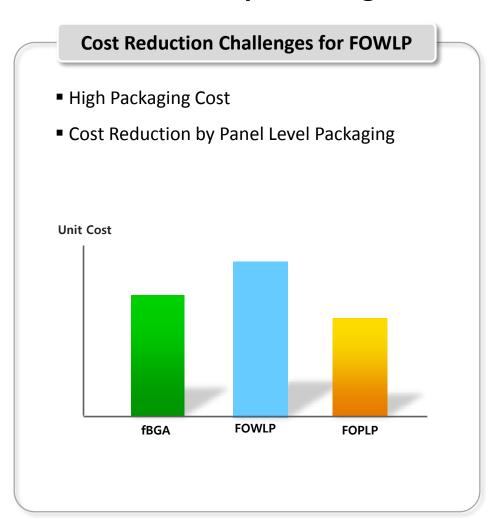

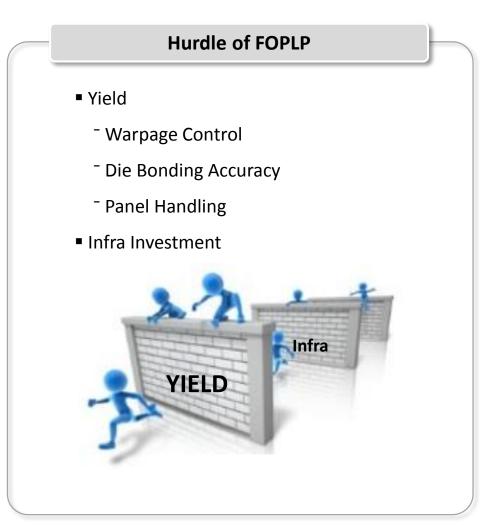

**3** Fan out package

#### FOWLP is a promising solution, but cost reduction is needed.

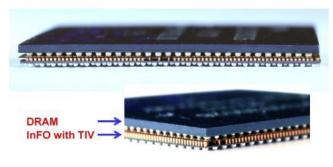

#### **Fan-out Packaging for SiP**

- PoP Bottom Package with Logic (Mobile AP)

- TSMC InFO<sup>1</sup>

- Amkor SLIM<sup>2</sup> & SWIFT<sup>3</sup>

- SPIL SLIT<sup>4</sup>

\*Source: http://gigglehd.com/zbxe/14078384

<sup>1</sup>InFO (Integrated Fan Out Wafer Level PKG), <sup>2</sup>SLIM (siliconless integrated module), <sup>3</sup>SWIFT (Silicon Wafer Integrated Fan-out Tech.), <sup>4</sup>SLIT (Silicon-less Interconnect Tech.)

**3** Fan out package

FOWLP is a promising solution, but cost reduction is needed.

#### Conclusion

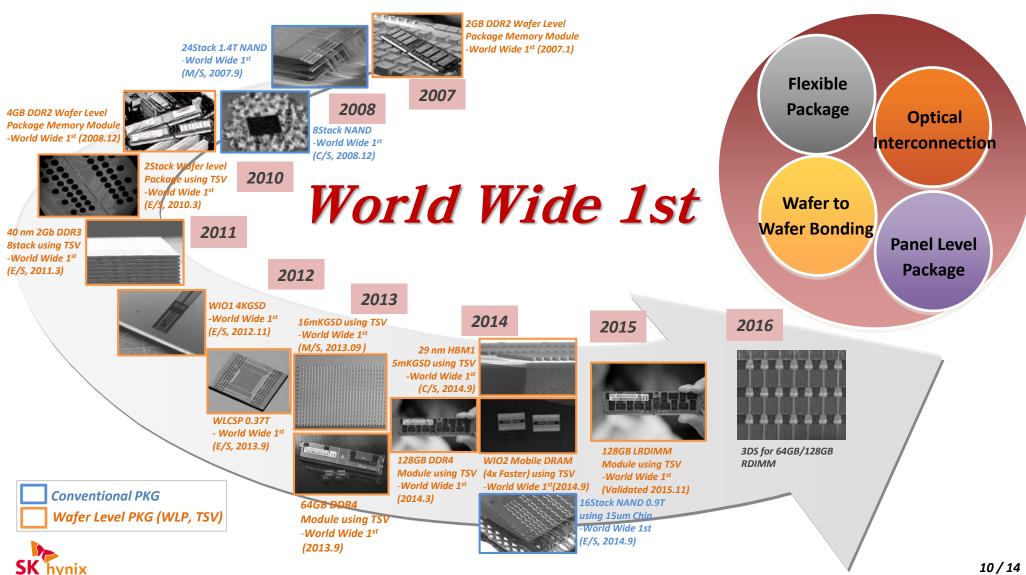

SK hynix is leading new and advanced memory package development against diverse and rapidly changing circumstances of semiconductor industry