### Review of Power Electronics Packaging and the Use of Copper Tungsten as a Heat Sink

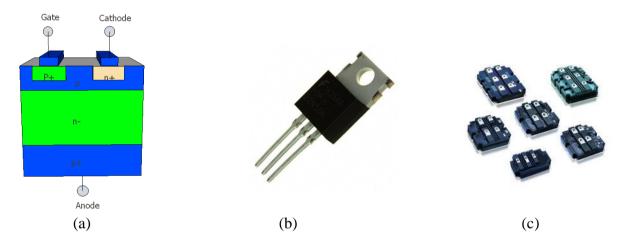

Power electronics are important in managing applications such as hybrid vehicles, power supplies, and induction heating to name a few. Power electronics mainly involve the control and conversion of an energy source from one form to another. The encasing of these devices requires design that will enhance thermal dissipation along with the improvement of electrical properties. The packaging of PE is considered everything non-electrical that is required to convert an electronic circuit design into a manufactured assembly [1]. Packaging is one of the most important factors in the efficiency of power electronics. With more sophisticated products being developed today, there are higher loads and amounts of stress that are placed upon the packaging of these semiconductor materials. Typical power electronics today include devices such as gate turn off thyristors, power MOSFETs, and insulated gate bipolar transistors (IGBTs) as seen below in Figure 1.

*Figure 1.* (a) Gate turn off thyristor representation with PN layers, turn on accomplished by positive current between gate and cathode (b) Power MOSFET (c) Insulated gate bipolar transistors

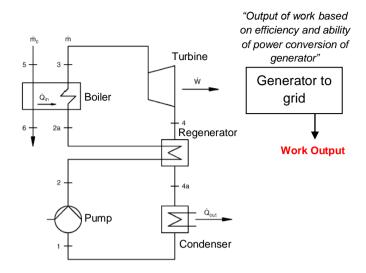

With an increase in demand and the advancement of technology, there has been an equal need for advancement in the packaging of these devices. Semiconductor packaging provides properties such as mechanical support, electrical interconnection, heat dissipation path, and protection from the outside environment. Power electronics are used when there is a need to alter a form of electrical energy. Higher currents and voltages in new systems mean higher thermal output, and they require larger interconnections. Issues such as these necessitate the advancement of packaging technology. Thermal management lends itself to problems such as the mismatch of Coefficient of Thermal Expansion (CTE) in materials, which then creates stresses and strains that negatively affect the performance of the chip, eventually leading to failure [2]. Three important factors pertaining to these devices are cost, reliability, and performance. Any small magnitude of loss is exponentially great for large systems. For example, in an energy generation system of a rankine steam cycle as seen in Figure 2, every kW of power saved at the electrical generation end (mechanical

Tel: (858) 558-6666

Figure 2. A more efficient power electronic package will create more efficient power conversions.

to electrical) is much more valuable than energy saved at the thermal conversion end [3]. As mentioned by B.G. Fernandes, there are various losses in a cycle, but with power electronics, more efficient power conversions can take place. The power electronics that are responsible for handling electricity at the generator side is just as important as the mechanical and thermal processes that precede it. Therefore, with efficient power conversions and storage, both cost and power consumption will be preserved long term. To improve the characteristics of packaging, researchers have developed innovative methods for assembly.

Three dimensional packaging allows for lower resistance, higher current handling, and more effective integration [4]. Stacking chips along the z axis can improve efficiency of power consumption as well as parasitic capacitance by up to 30%. Advantages of 3 dimensional packaging also include:

- Reduction in size and weight

- Increased quality of electrical signal due to reduced interconnection length

- Higher frequencies are able to be reached

- Maximum use of available interconnects

Other methods for assembly include: flip-chip process, pressure contact, thin film power overlay technology, metal posts interconnected parallel plate structure, and multilayer integration. These are novel concepts currently utilizing such materials as heat spreaders, DBC substrates, and 3 dimensional stacking.

## How are Power Electronic Packages Assembled?

There has been an evolution in the methods of assembling, beginning with the wire bonding methods of the 1990, leading to the flip chip technology of today [5]. 2 dimensional packaging is quickly being replaced by 3 dimensional packages as these can be produced with enhanced characteristics while maintaining low costs. 3 dimensional structures are expected to bring higher power conversion density, lower parasitics, and enhanced system

# TORREY HILLS

integration. This integration provides enhanced interconnection in devices such as power devices, driver circuitry, controls, sensors, and communication devices [5]. Methods such as wire bonding and 3D packaging are discussed below.

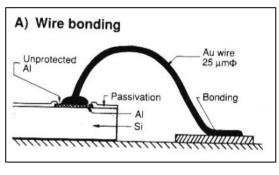

## A) Chip on Board and Conventional Wire-Bonding

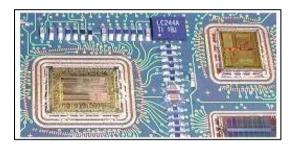

Chip-on-board (COB) is a method of assembly where the microchip is directly mounted upon and electrically connected to a circuit board. The method of COB can be described in three steps: 1) Die attach 2) Wire-bonding 3) Encapsulation of die and wires [6]. Die attach is done by mounting a chip onto the board with a type of die adhesive. After this, a sintering process is completed, using heat to allow the adhesive to fully develop. Wire-bonding is a type of interconnection used in many applications of electronics by using either gold or aluminum wiring as seen in Figure 3b. Hundreds of these wire-bonded interconnections are made within a module. The final step of encapsulation completes the process, whereas an epoxy type liquid is used to coat the wires and the chip, which allows for protection from the surroundings. This type of technology is increasing in size as more than 5000 LEDs are used in printer modules and state of the art multichip COB systems can carry over 100 chips on a single board as seen below [6].

(b)

Compared to modern flip chip technology and 3 dimensional assemblies, chip on board and wire-bonding are losing competitiveness. Wire-bonding takes up large amounts of space inside a chip module. Characteristics such as speed and electrical quality suffer due to the extended lengths of interconnection used in bonding wires.

## **B)** Flip-Chip Assembly

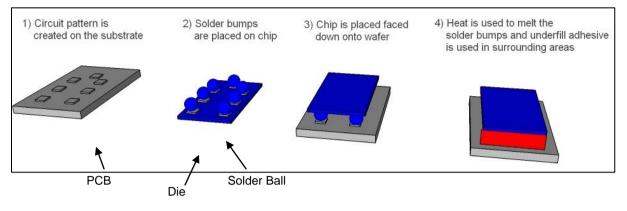

Electrical performance and size in flip chip technology are improved over conventional wire bonding and packaging. A chip with metalized bumps is placed face down on a substrate creating a direct electrical connection with the carrier [8]. A solder treatment with conductive epoxy and adhesive is done throughout the module and connections are made. The processing steps for the assembly are shown below.

www.torreyhillstech.com Tel: (858) 558-6666

Figure 4. Flip Chip Process

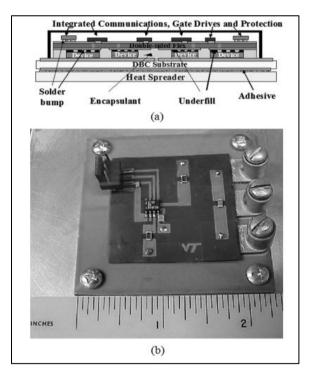

The shorter length of bonding between the devices means decreased sizes with more quality connections. The inductance of the connection is reduced up to 10 times, and the path is shortened from 25-100 times the length increasing speed [9]. A type of flip chip assembly with diagram and actual picture is shown below in Figure 5. This arrangement favors thermal dissipation with a heat spreader mounted on bottom.

*Figure 5.* (a) Cross section diagram of flip chip flex integrated power electronics module (FCOF-IPEM) (b) Half bridge FCOF-IPEM [2]

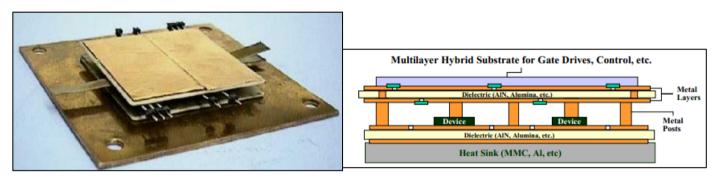

# C) Metal Posts Interconnected Parallel Plate Structure (MPIPPS)

MPIPPS is a 3 dimensional packaging technique used for power electronics that utilizes copper-bonding rather than wire-bonding. This method is a variation of the flip chip process. Copper "posts" are used to facilitate bonding, which allows for lower DC resistance than conventional aluminum wire-bonding [5]. This means less parasitic inefficiencies, resulting in improved conversions of energy. The process for this assembly begins with achieving soldered contact by a metallization process that includes thin film deposition and electrolytic plating [5]. The next step in process is the attachment of copper posts by sintering in a gas-controlled furnace. A top DBC is flipped upside down to be attached to the rest of the assembly creating a MPIPPS module as seen below. A heat spreader is also soldered onto the bottom. For thermal management, the whole module is attached to a heat sink as seen in Figure 5b.

(a)

(b)

Figure 6. (a) MPIPPS module (b) Diagram of MPIPPS device with copper posts [5]

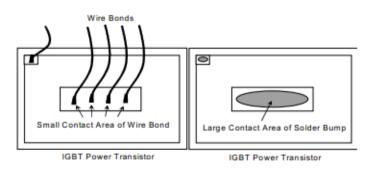

This set-up will allow more contact area for connections rather than wire bonding, as can be seen in the comparison in Figure 7. The larger contact area allows for large current handling and reduced electro migration [10]. Other advantages of MPIPPS include:

- Mechanical forces distribute over a large area, minimizing stress

- Reduced parasitic inductance and capacitance

- Better heat dissipation paths due to metal posts

- Integration of passive components is possible through stacking between metal posts and metal layers

Figure 7. Wire-bonding compared with solder bumping/posts

#### **C) Pressure Contact Assembly**

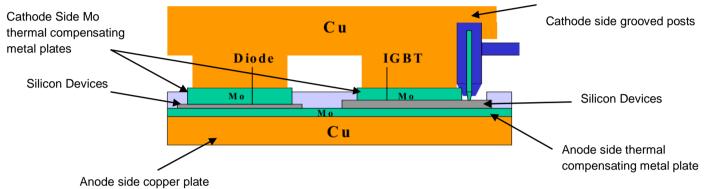

The pressure contact technique has been applied to high powered semiconductors such as diodes, thyristors, and GTOs [11]. The pressure contact method was designed to deal with the problems of wire-lifting in wire bond techniques. Wire-lifting occurs with thermal cycling and is not repairable. Pressure contact bypasses this problem by having a sandwich structure with anode and cathode sides in contact as seen in the Figure below. This method does not require any soldering process and reduces residual stress on the components [5].

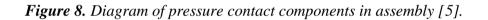

Another method of pressure contact assembly uses a spring mechanism as the interconnection method. As presented by He et. al., the process begins with a die mounting and soldering onto a substrate such as DBC. A gold-plated copper pad is placed on top of the chip die for transition. The spring wire made of beryllium copper is soldered onto the plate as shown in the diagram below. On the top there is a PCB, emitter plate, and control/ICs placed in connection.

Figure 9. Pressure contact assembly [11]

### **Disadvantages of 3D Packaging**

Some disadvantages of 3D packaging include the need of high thermal dissipation due to such large power densities. As mentioned by Sarawi et. al., methods of solution include:

- Distributing thermal energy across surface of 3D package

- Using low thermal resistance materials such as CVD (chemical vapor deposition) diamond

- Using forced air or liquid

- Using thermal vias (pathways) for dissipation

Other disadvantages include the complexity, cost, and design software for these packages. Many of these problems are being addressed with further advancement in manufacturing technologies.

## **Electrical and Physical Parameters of Packaging**

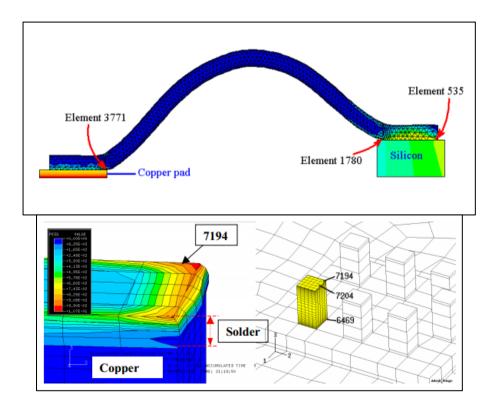

The dimensions of a package are important in the properties of the overall package. With 3 dimensional packaging, less wire-bonding length is needed and reduction in size can be achieved. The decreased size results in maximum use of raw materials. Thermal efficiency is important for creating a functioning, reliable package. Problems like delamination occur at the meeting junction of bonds with thermal cycling. Finite element thermal analysis is shown in Figure 10 of both wire-bonding and MPIPPS. Failure can occur at the solder joints where interconnection bonding takes place. Heat sinks and thermal spreaders assist in thermal cycling so that debonding does not occur.

Figure 10. Finite element software analysis of wire bonding and MPIPPS structures [5]

# TORREY HILLS

Delay is another electrical parameter used to refer to the time it takes for a signal to travel between points in a system module. Time is proportional to interconnect length [review of 3D technology [12]. With interconnection lengths being reduced, delay is also reduced. Length is an important part of an electrical parameter called noise. Noise is the unwanted disturbances that inhibit quality signal transfer. Reflection, crosstalk, simultaneous switching, electromagnetic interference are all noises that need to be reduced in magnitude for improved performance. Power consumption is also a major factor that is described in equation below.

$E = CV^2$ , energy dissipated in electronic system

$P = fCV^2$ , power consumption

Where,

$$E = energy$$

dissipated

$C = interconnect$  parasitic capacitance

$P = power$  consumption

$f = number$  of transitions

$V = voltage$  swing across C and f

The power consumption formula describes how power consumption is in direct correlation with parasitic capacitance. Packaging techniques such as flip chip or pressure contact reduce these parasitic therefore reducing the power consumption. The speed, f, is also increased by the same relationship. In analysis done by Reinhold [4], multichip 3 dimensional modules would consume 2% power as opposed to printed wire boards which would consume up to 10%. This means a reduction on thermal stresses and an associated longer lifetime.

### Integration of Copper Tungsten (CuW) as Heat Sinks for Packaging Electronics

Warping and thermal stresses are the primary factors in designing packages. Power semiconductors, optoelectronics, and high power RFs are just some devices that need thermal stressing to consider. High temperatures are such an issue that even liquid cooling have been discussed as options. This method would present problems of cost and new industry development, so it is best to work with materials that are currently being mass produced. Thermal stress occurs because of the difference in the coefficient of thermal expansion (CTE) of the materials that are bonded together. Because of this factor, materials such as the die or substrate can expand at a different rate than the device causing delamination as discussed before. The CTE of the solder being used must also be taken into account since this will be the point of contact between the two materials being bonded. The CTE of usual semiconductors and ceramics ranges from 2-7  $\frac{ppm}{K}$  [13]. As seen in the table below of heat sink materials, the CTE of tungsten fiber reinforce copper (CuW) ranges from 5.7-8.3  $\frac{ppm}{K}$ .

| www.torreyhillstech.com |  |  |  |  |  |

|-------------------------|--|--|--|--|--|

| Tel: (858) 558-6666     |  |  |  |  |  |

| Reinforcement  | Matrix             | Thermal<br>Conductivity<br>k (W/m-K) | CTE<br>(ppm/K) | Density<br>(g/cm³) | Specific Thermal<br>Conductivity (W/m-K) |

|----------------|--------------------|--------------------------------------|----------------|--------------------|------------------------------------------|

| —              | Aluminum           | 218                                  | 23             | 2.7                | 81                                       |

| —              | Copper             | 400                                  | 17             | 8.9                | 45                                       |

| —              | Invar              | 11                                   | 1.3            | 8.1                | 1.4                                      |

| _              | Kovar              | 17                                   | 5.9            | 8.3                | 2.0                                      |

| _              | Cu/l/Cu            | 164                                  | 8.4            | 8.4                | 20                                       |

| _              | Cu/Mo/Cu           | 182                                  | 6.0            | 9.9                | 18                                       |

| 2              | Cu/Mo-Cu/Cu        | 245 to 280                           | 6 to 10        | 9.4                | 26 to 30                                 |

|                | Titanium           | 7.2                                  | 9.5            | 4.4                | 1.6                                      |

| Copper         | Tungsten           | 157 to 190                           | 5.7 to 8.3     | 15 to 17           | 9 to 13                                  |

| Copper         | Molybdenum         | 184 to 197                           | 7.0 to 7.1     | 9.9 to 10.0        | 18 to 20                                 |

|                | Solder – Sn63/Pb37 | 50                                   | 25             | 8.4                | 6.0                                      |

|                | Ероху              | 1.7                                  | 54             | 1.2                | 1.4                                      |

| E-glass Fibers | Ероху              | 0.16 to 0.26                         | 11 to 20       | 2.1                | 0.1                                      |

Table 1. Thermodynamic properties of various thermal management materials

The range of 5.7-7  $\frac{ppm}{\kappa}$  matches comparatively well with the semiconductor and ceramic material. Although bare copper by itself has much higher thermal conductivity, the CTE is much too high to be matched well in an assembly. Copper's expansion rate would cause failure after only a few cycles. On the other hand, copper tungsten is well suited for reliability and long life time cycling. CuW consists of an alloy between 10 to 50 weight percent copper and the remaining is tungsten [14]. The tungsten's role in this alloy is to lower the expansion rate of copper. In commercial products, CuW is suitable for heat sink applications that provide effective thermal management and cost effectiveness compared with other materials. With increasing electrical energy production comes higher thermal output. An increase of tungsten content can lower thermal expansion rate conserving the quality of signal in power electronic modules.

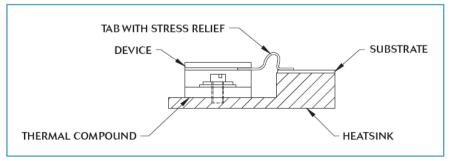

Heat sink design requires considerations in the material used in bonding as proposed by Aeroflex, a company specializing in microelectronic equipment. Some key factors to consider in mounting chip devices are:

- Flatness of mating surfaces to maximize bonding area

- Use of thermal compound to fill any microscopic voids

- Stress relief tab (as seen in Figure 11), helps with reducing mechanical stress on joints

Figure 11. Aeroflex Mounting Application [15]

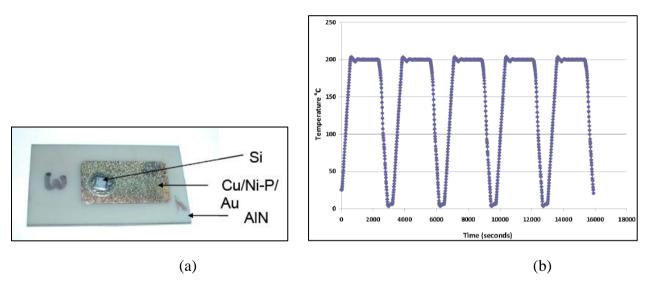

Solder joint compounds are crucial for lifetime design purposes. An increase in temperature can mean accelerated degradation of solder joint properties. The solder-SN63/Pb37 has a high CTE of  $25 \frac{ppm}{K}$  with a low thermal conductivity of  $50 \frac{W}{m-K}$ . The effects of steady state temperature and thermal cycling need to be observed in the design process as well as the thickness of the solder. Muralidharan [16] has done experiments on types of solder when joining between AlN DBC with Cu/Ni (P)/Au (fig8). The type of solder used is lead free Sn-3.5Ag. The thermal cycling process was done between 5°C and 200°C holding for 30 minutes at 200°C and for 5 minutes at 5°C. This test was for a module that would reach high temperatures up to 200°C encountered in hybrid and electric vehicles. The result showed reductions in thermal diffusivity occurred and significant damage was seen after 3000 cycles. The type of solder used in bonding is important for heat sink and power electronic connections.

*Figure 12.* (a) Chip module assembly arrangement. (b) Thermal heat cycling method. *Minimum temperature of*  $5^{\circ}$ C *and maximum temperature of*  $200^{\circ}$ C *applied.* [16]

#### **Conclusion**:

Advancement in power electronic packaging is necessary as higher power densities are achieved and thermal output is increased. Packaging is crucial in applications such as renewable energy. Optimal performance of power electronics packages is essential for harvesting renewable energy such as solar power, wind power, and fuel cells. This can also be true for the utilization of fossil fuels. The energy that is available must be preserved and not lost due to inefficiencies. Thermal dissipation is one of the key parameters in the development of packaging. For example, temperatures as high as 150°C can be seen in new 1200 V-IGBT4 modules [17]. 3 dimensional packaging techniques offer better thermal management, smaller size, lower resistance, and higher reliability. Power devices differ from other electronics in that they tend to handle large power currents and therefore require thick interconnections as well as better thermal management. CuW has the necessary properties to be applied as heat sinks for power electronic packages. The coefficient of thermal expansion

(CTE) is relatively low compared with other materials in the same class. This means cracking and failure due to expansion and contraction is no longer a problem. At the same time, thermal conductivity is of high rating and is able to dissipate heat efficiently. With proper packaging of electronics, greater generation and transmission of available energy sources is possible.

#### **References**:

<sup>3</sup> Fernandez, B.G. Power Electronics (Video). Electrical Engineering, IIT Bombay <<u>http://nptel.iitm.ac.in></u>

<sup>5</sup> Wen, Sihua, "Thermal and Thermo-Mechanical Analysis of Wire Bond vs. Three Dimensionally Packaged Power Electronics Modules". Virginia Polytechnic Institute. December 1999.

<sup>6</sup> Silicon Far East. Chip on Board. http://www.siliconfareast.com/cob.htm

<sup>8</sup> Amalu, Emeka and Ekere, Ndy. "High Temperature Reliability of Lead Free Solder Joints in a Flip Chip Assembly". Journal of Materials Processing Technology 212 (2012) 471-483.

<sup>9</sup> Ding, Fei. "Flip Chip and Lid Attachment Assembly Process Development". Auburn University Dissertation. 2006

<sup>10</sup> "Packaging of Metal Post Interconnected Parallel Plate Structure (MPIPPS) Modules"

<sup>11</sup> He, X. Zeng, X. Yang, X. Wang, Z. "A Hybrid Integrated Power Electronic Module Based on Pressure Contact Technology". Xi'an Jiaotong University.

<sup>12</sup> Johnson, R. Wayne. "3D Packaging Technology: A Review". Auburn University. 2005.

<sup>13</sup> Zweben, Carl. "Thermal Materials Solve Power Electronic Challenges". Power Electronics Technology. Webpage.

<sup>14</sup> Shaw, Michael. "Understanding of Laser, Laser Diodes, Laser Diode Packaging and its Relationship to CuW Heatsinks"

<sup>15</sup> Aeroflex. "Mounting Application Notes".

Popovich, Jelena and Ferreira, J.A. "An approach to deal with packaging in power electronics". IEEE Vol.20 No.3 May 2005.

<sup>&</sup>lt;sup>2</sup> Calata, J. Bai, J. Liu, X. Wen S., Lu, G. "3 Dimensional packaging for Power semicconductor Devices and Modules". IEEE Vol. 28 No.3, August 2005.

<sup>&</sup>lt;sup>4</sup> Sarawi, S. Abbott, D. Franzon, P. "A Review of 3D packaging Technology". IEEE Vol 21. No. 1 February 1998.

<sup>&</sup>lt;sup>7</sup> Halbo, Leif and Ohlckers, Per. "Electronics Components, Packaging, and Production". Textbook. ISBN 82-992193-2-9

<sup>&</sup>lt;sup>16</sup> Muralidharan, Govindarajan. "Solder Joints of Power Electronics". Materials Science and Technology Division. 2010.

<sup>&</sup>lt;sup>17</sup> Bayerer, Reinhold. "Advanced Packaging Yields Higher Performance and Reliability in Power Electronics". Infineon Technologies AG. Microelectronics Reliability 50 (2010) 1715-1719.