# RYFPGA:

# The Complete Course in Understanding Computer Architecture

# The Movement to Open-Source Hardware

Prof. David Patterson speaking to the RVfpga team on 6th May 2020: "RISC-V is simple, real, and will pervade every computing level in the next 5 years. The distinguishing feature is the basic Instruction Set. All the extras are in optional extensions. Openness sparks collaboration and global participation!"

## Introduction

RISC-V is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. Unlike other ISA designs, this ISA is provided under open source licenses that do not incur fees. Many companies are offering RISC-V hardware, with more to follow. Open-source operating systems with RISC-V support are available and the instruction set is supported by popular software toolchains.

The RVfpga course provides the foundation knowledge and hands-on experience that the next generation of Programmers and Engineers need to harness the potential of RISC-V. It consists of 20 Labs with detailed instructions, examples, short questions and practical exercises with solutions, giving you the teachers flexibility to choose between a practical and an exam-based structure for the course at your faculty.

The RVfpga package provides instructions, tools, and labs that show how to:

- Target a commercial RISC-V system to an FPGA

- Add more functionality to the RISC-V system

- Analyze and modify the RISC-V core and memory hierarchy

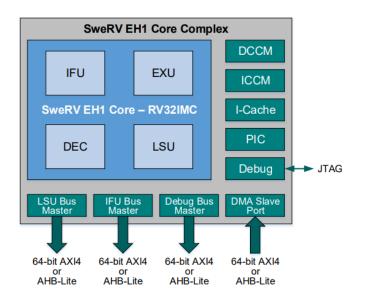

The RVfpga system uses the Chips Alliance's SweRVolf SoC, which is based on Western Digital's RISC-V SweRV EH1 core. The SweRV is a fully-verified production level processor core, that is fully open-source, and now being used by several SoC designers including Imagination Technologies, the leaders of this project, in their A series GPU.

## The Authors

The course materials were developed by Dr. Sarah Harris, Associate Professor of Electrical and Computer Engineering at University of Nevada, Las Vegas (U.S.A.). Dr. Harris co-wrote the popular book, *Digital Design and Computer Architecture*, now in its fourth edition, RISC-V version, which will be published in 2021. Dr. Daniel Chaver-Martínez, Associate Professor of Department of Computer Architecture and System Engineering at Universidad Complutense de Madrid (Spain).

# **Target Courses**

Digital Design & Microarchitectures (BSc), Computer Organisation & Architecture, Advanced Computer Architecture (BSc, MSc), SoC design (MSc), Design Verification (MSc), Embedded Systems projects (BSc, MSc) and Processor Architecture: modifications, enhancements, optimisation...(MSc, PhD)

# Duration

The complete course runs for three one-semester course to illustrate the key points and give students hands-on experience -- Computer Fundamentals (1st part), Computer Organization (2nd part) and Computer Architecture (3rd and 4th parts).

# **Tools Required**

# Software

- Xilinx Vivado 2019.2 WebPACK

- Microsoft's Visual Studio Code

- PlatformIO with Chips Alliance platform, which includes: RISC-V Toolchain, OpenOCD, Verilator HDL Simulator, WD Whisper ISS.

# Hardware

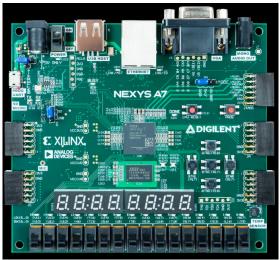

- Digilent's Nexys A7 or Nexys 4 DDR FPGA Board

- RISC-V Core & SoC:

- Core: Western Digital's SweRV EH1

- SoC: Chips Alliance's SweRVolf

Western Digital EH1 SweRV Core

Digilent Nexys A7 FPGA board with Xilinx Artix 7 XC7A100T

# Contents

| Lecture Topic | Details                                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lab 0         | Introduction<br>- Direct to Quick Start Guide or Getting Started Guide<br>- Overview of Tools<br>- Overview of Labs                                                                                                                                                                                |

| Lab 1         | <ul> <li>Vivado Project</li> <li>Simulation (Verilator).</li> <li>Creating a Vivado project using SweRVolf RTL (Verilog), generating a bitfile and downloading it onto the Nexys A7 FPGA board.</li> </ul>                                                                                         |

| Lab 2         | C Programming<br>- Example C program<br>- Boot code<br>- Exercises                                                                                                                                                                                                                                 |

| Lab 3         | Assembly Programming<br>- Simulation - using Whisper, the SweRV-ISS,<br>Instruction Set Simulator<br>- Boot code<br>- Exercises                                                                                                                                                                    |

| Lab 4         | Function Calls<br>- RISC-V ABI<br>- Procedure Calling Convention<br>- Exercises                                                                                                                                                                                                                    |

| Lab 5         | C with Assembly Code<br>- Embedding assembly code with C code<br>- Exercises                                                                                                                                                                                                                       |

| Lab 6         | Introduction to I/O<br>- Program-driven GPIO<br>- Overview of Nexys A7 I/O<br>- C and Assembly Programs<br>- Exercises                                                                                                                                                                             |

| Lab 7         | <ul> <li>7-Segment Displays</li> <li>Build 7-segment display decoder for driving Nexys A7's built-in</li> <li>7-segment displays</li> <li>Examples in C and assembly</li> <li>Exercises</li> </ul>                                                                                                 |

| Lab 8         | Interrupt-driven GPIO<br>- Introduction to SweRVolf's interrupt support<br>- Overview of the main changes to the controller<br>- Examples in C and assembly<br>- Exercises                                                                                                                         |

| Lab 9         | Timers<br>- Understand the timer controller obtained from Opencores (https://<br>opencores.org/), an online community for the development of<br>gateware IP (Intellectual Properties) Cores in the spirit of Free and<br>Open Source collaboration.<br>- Examples in C and assembly<br>- Exercises |

| Lecture Topic | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lab 10        | Serial Buses<br>- SPI, I2C, and UART<br>- Understand the serial bus controllers obtained from OpenCores.<br>The controllers that you will use in this lab are available at: <u>https://</u><br><u>opencores.org/projects/uart16550</u> (UART, which is provided inside<br>SweRVolf), <u>https://opencores.org/projects/i2c</u> (I2C) and <u>https://</u><br><u>opencores.org/projects/simple_spi</u> (SPI).<br>- Examples in C and assembly<br>- Exercises |

| Lab 11-15     | Understanding and Modifying the RISC-V Datapath - Diagram of the core structure - Instruction flow through the pipeline (Arithmetic/Logic, Memory, Jumps, and Branches) - Hazards and how to deal with them - Implement new instructions and execute them on the board (use - Understand the Branch Predictor and make some changes to it - Understand superscalar processing                                                                              |

| Lab 16-20     | <ul> <li>Understanding and Modifying the RISC-V Memory Hierarchy</li> <li>Understand the operation of the memory hierarchy including cache hits and misses.</li> <li>Test different cache sizes, configurations and management policies</li> <li>Understand the cache controller</li> <li>Understand the ICCM and DCCM</li> </ul>                                                                                                                          |

# Release Dates & Languages:

- November 2020: RVfpga Getting Started Guide, RVfpga Quick Start Guide, RVfpga Labs 1 to 10 (Parts 1 & 2)

- March 2021: MSc-level SoC Design Course Autumn 2021: RVfpga Extended Labs 11 to 20 (Parts 3 & 4)

- All materials will be delivered in English & Chinese (Spanish & Japanese in plan)

# **Complementary Materials:**

- A series of video tutorials given by Prof. Sarah Harris and Prof. Daniel Chaver-Martinez are in preparation

- A global programme of online and in-university workshops are planned for 2021

- The popular textbook *Digital Design & Computer Architecture: RISC-V Edition 2021* which provides a uniquely relevant accompaniment to RVfpga

- Computer Organisation and Design by David Patterson and John L. Hennessy remains the "bible" for these activities

- Relevant textbooks: <u>http://university.imgtec.com/resources/books/</u>

# Support:

- The RVfpga forum is specifically for technical questions about RVfpga https://university.imgtec.com/forums/rvfpga/

- For curriculum and other discussions, there is the IUP (Imagination University Programme) forum here

# Plans :

- A webinar for RVfpga is planned for 8th October 2020, register here: <u>https://hubs.ly/H0v3l-r0</u>

- Our global Workshop Schedule Programme is regularly updated at <u>University Events</u>

- Videos from these workshops will be available online in 2021

- Encouragement will be given to translators who wish to make these materials available in other languages. Please contact IUP@imgtec.com

- Joint activities with RISC-V International (formerly the RISC-V Foundation) and other partners are under discussion

# **Press Release:**

https://www.imgtec.com/news/press-release/ imagination-announces-the-first-risc-v-computerarchitecture-course/

# RISC-V Global Forum Paper by Harris & Chaver-Martinez:

https://<u>events.linuxfoundation.org/riscv-global-</u> forum/register/

# **Our Partners**

We have worked closely with 17 partners and supporters who have given outstanding support to this large and complex project.

Academic Adviser: Prof. David Patterson University of California, Berkeley

Authors: Prof. Sarah Harris University of Nevada, Las Vegas

Assoc. Prof. Daniel Chaver Martinez Complutense University of Madrid

**Contributor:** Olof Kindgren Qamcom Research & Technology Gothenburg, Sweden **Reviewer:** Prof. Roy Kravitz Portland State University, U.S.

] Imagination

Zubair Kakakgel AZKY Tech Ltd. Birmingham, UK

Zubair Kakakgel AZKY Tech Ltd. Birmingham, UK

Sponsors:

# Supporters:

## Join the IUP and access these materials:

- 1. Register online at: http://<u>university.imgtec.com/register/</u>

- 2. Complete the IUP registration form

- 3. A verification email will be sent to your inbox for activation. (Please also check your spam mailbox because occasionally the mail may be got filtered)

- To download teaching materials, visit the IUP page

Teaching Resources

<a href="http://university.imgtec.com/resources/Downloads">http://university.imgtec.com/resources/Downloads</a>

- Request the package(s) you want, accept the Licence Agreement, and give some details about how you plan to use the materials.

- 6. We then receive a request to approve the download, and normally action this within 2 working days. Once approved, you will receive an e-mail saying you can now make the download.

A simple licence agreement requires that the materials are for Educational and Non-Commercial use, which means that companies or trainers, who wish to use the materials for paid-for training, textbooks or other commercial activities must seek Imagination's prior permission.

imaginationtech.com