# SiFive E21 Core Complex Manual v1p0

© SiFive, Inc.

# **SiFive E21 Core Complex Manual**

#### **Proprietary Notice**

Copyright © 2018, SiFive Inc. All rights reserved.

Information in this document is provided "as is," with all faults.

SiFive expressly disclaims all warranties, representations, and conditions of any kind, whether express or implied, including, but not limited to, the implied warranties or conditions of merchantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation indirect, incidental, special, exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

#### **Release Information**

| Version | Date              | Changes                                                                                                  |  |  |

|---------|-------------------|----------------------------------------------------------------------------------------------------------|--|--|

|         |                   | <ul> <li>Updates to support the intitial release of the E21<br/>Standard Core</li> </ul>                 |  |  |

| v1p0    | June 29, 2018     | <ul> <li>Interrupts chapter now supports CLIC modes<br/>and CSRs</li> </ul>                              |  |  |

|         |                   | <ul> <li>Added CLIC chapter (removed PLIC and CLINT chapters)</li> </ul>                                 |  |  |

| v0p2    | February 28, 2018 | <ul> <li>Replace Peripheral Port 0 with System Port</li> </ul>                                           |  |  |

| v0p1    | February 28, 2018 | <ul><li>Initial release</li><li>Describes the functionality of the SiFive E21<br/>Core Complex</li></ul> |  |  |

# **Contents**

| 1 | Int | trodu | uction                                  | 4  |

|---|-----|-------|-----------------------------------------|----|

|   | 1.1 | E21   | Core Complex Overview                   | 4  |

|   | 1.2 | Debi  | ug Support                              | 5  |

|   | 1.3 | Tigh  | tly-Integrated Memory                   | 5  |

|   | 1.4 | Inter | rupts                                   | 6  |

| 2 | Lis | st of | Abbreviations and Terms                 | 7  |

| 3 | E2  | 21 RI | SC-V Core                               | 9  |

|   | 3.1 | Instr | uction-Fetch Unit                       | 9  |

|   | 3.2 | Exec  | cution Pipeline                         | 9  |

|   | 3.3 | Data  | Memory System                           | 10 |

|   | 3.4 | Supp  | ported Modes                            | 10 |

|   | 3.5 | Phys  | sical Memory Protection (PMP)           | 10 |

|   | ;   | 3.5.1 | Functional Description                  | 11 |

|   | ;   | 3.5.2 | Region Locking                          | 11 |

|   | 3.6 | Hard  | lware Performance Monitor               | 11 |

| 4 | Me  | emor  | у Мар                                   | 13 |

| 5 | Int | terru | pts                                     | 14 |

|   | 5.1 | Inter | rupt Concepts                           | 14 |

|   | 5.2 | Inter | rupt Operation                          | 15 |

|   | į   | 5.2.1 | Interrupt Entry and Exit                | 15 |

|   | í   | 5.2.2 | Interrupt Levels and Priorities         | 16 |

|   | í   | 5.2.3 | Critical Sections in Interrupt Handlers | 16 |

|   | 5.3 | Inter | rupt Control Status Registers           | 17 |

|   | í   | 5.3.1 | Machine Status Register (mstatus)       | 17 |

|   | ļ   | 5.3.2 | Machine Tran Vector (mt vec)            | 17 |

|   | 5                                           | 5.3.3                                                                                 | Machine Interrupt Enable (mie)                                                                                                                                                                                                                                                                                                                     | 19                               |

|---|---------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | 5                                           | 5.3.4                                                                                 | Machine Interrupt Pending (mip)                                                                                                                                                                                                                                                                                                                    | 20                               |

|   | 5                                           | 5.3.5                                                                                 | Machine Cause (mcause)                                                                                                                                                                                                                                                                                                                             | 20                               |

|   | 5                                           | 5.3.6                                                                                 | Machine Trap Vector Table (mtvt)                                                                                                                                                                                                                                                                                                                   | 22                               |

|   | 5                                           | 5.3.7                                                                                 | Handler Address and Interrupt-Enable (mnxti)                                                                                                                                                                                                                                                                                                       | 22                               |

|   | 5                                           | 5.3.8                                                                                 | Machine Interrupt Status (mintstatus)                                                                                                                                                                                                                                                                                                              | 23                               |

|   | 5.4                                         | Interr                                                                                | rupt Latency                                                                                                                                                                                                                                                                                                                                       | 23                               |

| _ | _                                           | _                                                                                     |                                                                                                                                                                                                                                                                                                                                                    |                                  |

| 6 |                                             |                                                                                       | ocal Interrupt Controller (CLIC)                                                                                                                                                                                                                                                                                                                   |                                  |

|   | 6.1                                         |                                                                                       | rupt Sources                                                                                                                                                                                                                                                                                                                                       |                                  |

|   | 6.2                                         |                                                                                       | Memory Map                                                                                                                                                                                                                                                                                                                                         |                                  |

|   | 6.3                                         | Regis                                                                                 | sters                                                                                                                                                                                                                                                                                                                                              | 25                               |

|   | 6                                           | 5.3.1                                                                                 | CLIC Interrupt Pending (clicintip)                                                                                                                                                                                                                                                                                                                 | 26                               |

|   | 6                                           | 5.3.2                                                                                 | CLIC Interrupt Enable (clicintie)                                                                                                                                                                                                                                                                                                                  | 26                               |

|   | 6                                           | 5.3.3                                                                                 | CLIC Interrupt Configuration (clicintcfg)                                                                                                                                                                                                                                                                                                          | 26                               |

|   | 6                                           | 5.3.4                                                                                 | CLIC Configuration (cliccfg)                                                                                                                                                                                                                                                                                                                       | 27                               |

|   |                                             |                                                                                       |                                                                                                                                                                                                                                                                                                                                                    |                                  |

| 7 | Do                                          | hua                                                                                   |                                                                                                                                                                                                                                                                                                                                                    | 20                               |

| 7 |                                             | •                                                                                     |                                                                                                                                                                                                                                                                                                                                                    |                                  |

| 7 | 7.1                                         | Debu                                                                                  | g CSRs                                                                                                                                                                                                                                                                                                                                             | 28                               |

| 7 | 7.1                                         | Debu<br>7.1.1                                                                         | rg CSRs  Trace and Debug Register Select (tselect)                                                                                                                                                                                                                                                                                                 | 28<br>28                         |

| 7 | 7.1<br>7                                    | Debu<br>7.1.1<br>7.1.2                                                                | rg CSRs  Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)                                                                                                                                                                                                                                                      | 28<br>28<br>29                   |

| 7 | 7.1<br>7                                    | Debu<br>7.1.1<br>7.1.2<br>7.1.3                                                       | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)                                                                                                                                                                                                                     | 28<br>28<br>29<br>30             |

| 7 | 7.1<br>7                                    | Debu<br>7.1.1<br>7.1.2                                                                | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc                                                                                                                                                                                                       | 28<br>29<br>30                   |

| 7 | 7.1<br>7<br>7                               | Debu<br>7.1.1<br>7.1.2<br>7.1.3                                                       | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)                                                                                                                                                                                                                     | 28<br>29<br>30                   |

| 7 | 7.1<br>7<br>7                               | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5                                     | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc                                                                                                                                                                                                       | 28<br>29<br>30<br>30             |

| 7 | 7.1 7.2 7.2                                 | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5                                     | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc  Debug Scratch dscratch                                                                                                                                                                               | 28<br>29<br>30<br>30             |

| 7 | 7.1 7.7 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>Breal                            | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc  Debug Scratch dscratch                                                                                                                                                                               | 28<br>29<br>30<br>30<br>30       |

| 7 | 7.1 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>Breal<br>7.2.1                   | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc  Debug Scratch dscratch  kpoints  Breakpoint Match Control Register mcontrol                                                                                                                          | 28<br>29<br>30<br>30<br>30<br>30 |

| 7 | 7.1 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>Breal<br>7.2.1<br>7.2.2          | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc  Debug Scratch dscratch  Kpoints  Breakpoint Match Control Register mcontrol.  Breakpoint Match Address Register (maddress)                                                                           | 28293030303030                   |

| 7 | 7.1 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 7.2 | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>Breal<br>7.2.1<br>7.2.2<br>7.2.3 | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc  Debug Scratch dscratch  Kpoints  Breakpoint Match Control Register mcontrol  Breakpoint Match Address Register (maddress)  Breakpoint Execution                                                      | 2829303030303232                 |

| 7 | 7.1 7.2 7.2 7.3 7.3                         | Debu<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>Breal<br>7.2.1<br>7.2.2<br>7.2.3 | Trace and Debug Register Select (tselect)  Trace and Debug Data Registers (tdata1-3)  Debug Control and Status Register (dcsr)  Debug PC dpc  Debug Scratch dscratch  Repoints  Breakpoint Match Control Register mcontrol  Breakpoint Match Address Register (maddress)  Breakpoint Execution  Sharing Breakpoints Between Debug and Machine Mode | 282930303030323232               |

| 8 | Refere | nces                                   | . 35 |

|---|--------|----------------------------------------|------|

|   | 7.3.4  | Safe Zero Address                      | .34  |

|   | 7.3.3  | Debug Flags (0x100-0x110, 0x400-0x7FF) | .34  |

# Introduction

SiFive's E21 Core Complex is an efficient implementation of the RISC-V RV32IMAC architecture. The SiFive E21 Core Complex is guaranteed to be compatible with all applicable RISC-V standards, and this document should be read together with the official RISC-V user-level, privileged, and external debug architecture specifications.

A summary of features in the E21 Core Complex can be found in Table 1.

| E21 Core Complex Feature Set |                                                            |  |  |

|------------------------------|------------------------------------------------------------|--|--|

| Feature                      | Description                                                |  |  |

| Number of Harts              | 1 Hart.                                                    |  |  |

| E21 Core                     | 1× E21 RISC-V core.                                        |  |  |

| Hardware Breakpoints         | 4 hardware breakpoints.                                    |  |  |

| Physical Memory Protection   | PMP with 4 x regions and a minimum granularity of 4 bytes. |  |  |

| Unit                         |                                                            |  |  |

**Table 1:** E21 Core Complex Feature Set

### 1.1 E21 Core Complex Overview

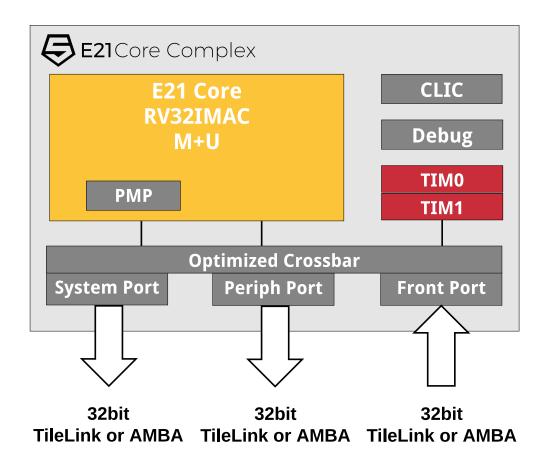

An overview of the SiFive E21 Core Complex is shown in Figure 1. This RISC-V Core IP includes a 32-bit RISC-V microcontroller core, local and global interrupt support, physical memory protection, a debug unit, one incoming Port, and two outgoing Ports.

Figure 1: E21 Core Complex Block Diagram

The E21 Core Complex memory map is detailed in Chapter 4, and the interfaces are described in full in the E21 Core Complex User Guide.

### 1.2 Debug Support

The E21 Core Complex provides external debugger support over an industry-standard JTAG port, including 4 hardware-programmable breakpoints per hart.

Debug support is described in detail in Chapter 7, and the debug interface is described in the E21 Core Complex User Guide.

# 1.3 Tightly-Integrated Memory

The E21 Core Complex has 64 KiB of Tightly-Integrated Memory (TIM) split evenly over two contiguous banks (TIM 0 and TIM 1). Having split TIMs allows for simultaneous access to both banks. When executing code solely from TIM address space, for maximum performance, it is recommended to place code in one TIM and data in the other. If executing code from an off core

complex memory device, such as a(n) AHB flash controller, the TIMs can be treated as a single contiguous address space.

The address of the Tightly-Integrated Memory is defined in the Memory Map in Chapter 4.

### 1.4 Interrupts

The E21 Core Complex supports 127 core local interrupts in addition to the RISC-V architectually defined software, timer, and external interrupts. The core local interrupt controller (CLIC) is used to set interrupt levels and priorities and can support up to 16 interrupt levels.

Interrupts are described in Chapter 5. The CLIC is described in Chapter 6.

# **List of Abbreviations and Terms**

| Term     | Definition                                                                                                                                                                                                |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ВНТ      | Branch History Table                                                                                                                                                                                      |  |

| ВТВ      | Branch Target Buffer                                                                                                                                                                                      |  |

| RAS      | Return-Address Stack                                                                                                                                                                                      |  |

| CLINT    | Core-Local Interruptor. Generates per-hart software interrupts and timer interrupts.                                                                                                                      |  |

| CLIC     | Core-Local Interrupt Controller. Configures priorities and levels for core local interrupts.                                                                                                              |  |

| hart     | HARdware Thread                                                                                                                                                                                           |  |

| DTIM     | Data Tightly Integrated Memory                                                                                                                                                                            |  |

| ITIM     | Instruction Tightly Integrated Memory                                                                                                                                                                     |  |

| JTAG     | Joint Test Action Group                                                                                                                                                                                   |  |

| LIM      | Loosely Integrated Memory. Used to describe memory space delivered in a SiFive Core Complex but not tightly integrated to a CPU core.                                                                     |  |

| PMP      | Physical Memory Protection                                                                                                                                                                                |  |

| PLIC     | Platform-Level Interrupt Controller. The global interrupt controller in a RISC-V system.                                                                                                                  |  |

| TileLink | A free and open interconnect standard originally developed at UC Berkeley.                                                                                                                                |  |

| RO       | Used to describe a Read Only register field.                                                                                                                                                              |  |

| RW       | Used to describe a Read/Write register field.                                                                                                                                                             |  |

| WO       | Used to describe a Write Only registers field.                                                                                                                                                            |  |

| WARL     | Write-Any Read-Legal field. A register field that can be written with any value, but returns only supported values when read.                                                                             |  |

| WIRI     | Writes-Ignored, Reads-Ignore field. A read-only register field reserved for future use. Writes to the field are ignored, and reads should ignore the value returned.                                      |  |

| WLRL     | Write-Legal, Read-Legal field. A register field that should only be written with legal values and that only returns legal value if last written with a legal value.                                       |  |

| WPRI     | Writes-Preserve Reads-Ignore field. A register field that might contain unknown information. Reads should ignore the value returned, but writes to the whole register should preserve the original value. |  |

# **E21 RISC-V Core**

This chapter describes the 32-bit E21 RISC-V processor core. The processor core comprises a decoupled instruction-fetch unit and a latency-optimized instruction-execution pipeline.

#### 3.1 Instruction-Fetch Unit

The E21 instruction-fetch unit issues TileLink bus requests to supply instructions to the execution pipeline. When executing straight-line code from an instruction source with single-cycle latency, the instruction-fetch unit can supply instructions at a sustained rate of one per cycle, regardless of instruction alignment.

The instruction-fetch unit issues only aligned 32-bit TileLink requests. If the execution pipeline consumes only part of the 32-bit instruction-fetch parcel, the instruction-fetch unit queues the remainder. Hence, when executing programs comprised mostly of compressed 16-bit instructions, the instruction-fetch unit is often idle, thereby reducing bus occupancy and power consumption.

The instruction-fetch unit always accesses memory sequentially. Conditional branches are predicted not-taken, and not-taken branches incur no penalty. Taken branches and unconditional jumps incur a one-cycle penalty, provided the target is naturally aligned (i.e., if the target is any 16-bit instruction, or is a 32-bit instruction whose address is divisible by 4). Taken branches and unconditional jumps to misaligned targets incur an additional one-cycle penalty.

# 3.2 Execution Pipeline

The E21 execution unit is a single-issue, in-order pipeline. The pipeline comprises three stages: Instruction Fetch, described in the previous section; Execute; and Writeback.

The pipeline has a peak execution rate of one instruction per clock cycle. Bypass paths are included so that most instructions have a one-cycle result latency. There are some exceptions:

- The number of stall cycles between a load instruction and the use of its result is equal to the number of cycles between the bus request and bus response. In particular, if a load is satisfied the cycle after it is demanded, then there is one stall cycle between the load and its use. In this special case, the stall can be obviated by scheduling an independent instruction between the load and its use.

- Integer division instructions have variable latency of at most 32 cycles. Note that in-flight division operations can be interrupted, so they have no effect on worst-case interrupt latency.

The E21 pipeline operates as follows. In the Execute stage, instructions are decoded and checked for exceptions, and their operands are read from the integer register file. Arithmetic instructions compute their results in this stage, whereas memory-access instructions compute their effective addresses and send their requests to the TileLink bus. Exceptions and interrupts are also detected in this stage: exceptional instructions do not proceed.

In the Writeback stage, instructions write their results to the integer register file. Instructions that reach the Writeback stage but have not yet produced their results will interlock the pipeline. In particular, load and division instructions with result latency greater than one cycle will interlock the pipeline.

### 3.3 Data Memory System

The E21 processor has a TileLink bus interface used by all loads, stores, and AMOs. Only one data memory access is permitted to be in flight.

Store instructions incur no stalls if acknowledged by the TileLink bus on the cycle after they are sent. Otherwise, the pipeline will interlock on the next memory-access instruction until the store is acknowledged.

## 3.4 Supported Modes

The E21 supports RISC-V user mode, providing two levels of privilege: machine (M) and user (U). U-mode provides a mechanism to isolate application processes from each other and from trusted code running in M-mode.

See *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10* for more information on the privilege modes.

# 3.5 Physical Memory Protection (PMP)

The E21 includes a Physical Memory Protection (PMP) unit compliant with *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.* PMP can be used to set memory access privileges (read, write, execute) for specified memory regions. The E21 PMP supports 4 regions with a minimum region size of 4 bytes.

This section describes how PMP concepts in the RISC-V architecture apply to the E21. The definitive resource for information about the RISC-V PMP is *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.*

#### 3.5.1 Functional Description

The E21 includes a PMP unit, which can be used to restrict access to memory and isolate processes from each other.

The E21 PMP unit has 4 regions and a minimum granularity of 4 bytes. Overlapping regions are permitted. The E21 PMP unit implements the architecturally defined pmpcfgX CSR pmpcfg0 supporting 4 regions. pmpcfg1, pmpcfg2, and pmpcfg3 are implemented but hardwired to zero.

The PMP registers may only be programmed in M-mode. Ordinarily, the PMP unit enforces permissions on U-mode accesses. However, locked regions (see Section 3.5.2) additionally enforce their permissions on M-mode.

#### 3.5.2 Region Locking

The PMP allows for region locking whereby, once a region is locked, further writes to the configuration and address registers are ignored. Locked PMP entries may only be unlocked with a system reset. A region may be locked by setting the L bit in the pmpicfg register.

In addition to locking the PMP entry, the L bit indicates whether the R/W/X permissions are enforced on M-Mode accesses. When the L bit is set, these permissions are enforced for all privilege modes. When the L bit is clear, the R/W/X permissions apply only to U-mode.

#### 3.6 Hardware Performance Monitor

The E21 Core Complex supports a basic hardware performance monitoring facility compliant with *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.* The mcycle CSR holds a count of the number of clock cycles the hart has executed since some arbitrary time in the past. The minstret CSR holds a count of the number of instructions the hart has retired since some arbitrary time in the past. Both are 64-bit counters. The mcycle and minstret CSRs hold the 32 least-significant bits of the corresponding counter, and the mcycleh and minstreth CSRs hold the most-significant 32 bits.

The hardware performance monitor includes one additional event counter, mhpmcounter3. The event selector CSR mhpmevent3 is a register that controls which event causes the corresponding counter to increment. The mhpmcounters are 40-bit counters. The mhpmcounter\_i CSR holds the 32 least-significant bits of the corresponding counter, and the mhpmcounter\_ih CSR holds the 8 most-significant bits.

The event selectors are partitioned into two fields, as shown in Table 2: the lower 8 bits select an event class, and the upper bits form a mask of events in that class. The counter increments if the event corresponding to any set mask bit occurs. For example, if mhpmevent3 is set to

0x4200, then mhpmcounter3 will increment when either a load instruction or a conditional branch instruction retires. Note that an event selector of 0 means "count nothing."

| Machine Hardware Performance Monitor Event Register |                                              |  |  |  |

|-----------------------------------------------------|----------------------------------------------|--|--|--|

| Instruction Commit Events, mhpeventX[7:0] = 0       |                                              |  |  |  |

| Bits                                                | Meaning                                      |  |  |  |

| 8                                                   | Exception taken                              |  |  |  |

| 9                                                   | Integer load instruction retired             |  |  |  |

| 10                                                  | Integer store instruction retired            |  |  |  |

| 11                                                  | Atomic memory operation retired              |  |  |  |

| 12                                                  | System instruction retired                   |  |  |  |

| 13                                                  | Integer arithmetic instruction retired       |  |  |  |

| 14                                                  | Conditional branch retired                   |  |  |  |

| 15                                                  | JAL instruction retired                      |  |  |  |

| 16                                                  | JALR instruction retired                     |  |  |  |

| 17                                                  | Integer multiplication instruction retired   |  |  |  |

| 18                                                  | Integer division instruction retired         |  |  |  |

| Mid                                                 | croarchitectural Events , mhpeventX[7:0] = 1 |  |  |  |

| Bits                                                | Meaning                                      |  |  |  |

| 8                                                   | Load-use interlock                           |  |  |  |

| 9                                                   | Long-latency interlock                       |  |  |  |

| 10                                                  | CSR read interlock                           |  |  |  |

| 11                                                  | Instruction cache/ITIM busy                  |  |  |  |

| 12                                                  | Data cache/DTIM busy                         |  |  |  |

| 13                                                  | Branch direction misprediction               |  |  |  |

| 14                                                  | Branch/jump target misprediction             |  |  |  |

| 15                                                  | Pipeline flush from CSR write                |  |  |  |

| 16                                                  | Pipeline flush from other event              |  |  |  |

| 17                                                  | Integer multiplication interlock             |  |  |  |

|                                                     | emory System Events, mhpeventX[7:0] = 2      |  |  |  |

| Bits                                                | Meaning                                      |  |  |  |

| 8                                                   | Instruction cache miss                       |  |  |  |

| 9                                                   | 9 Memory-mapped I/O access                   |  |  |  |

Table 2:

mhpmevent Register Description

# **Memory Map**

The memory map of the E21 Core Complex is shown in Table 3.

| Base        | Тор         | Attr. | Description     | Notes                     |

|-------------|-------------|-------|-----------------|---------------------------|

| 0x0000_0000 | 0x0000_00FF |       | Reserved        |                           |

| 0x0000_0100 | 0x0000_0FFF | RWX   | Debug           | Debug Address Space       |

| 0x0000_1000 | 0x01FF_FFFF |       | Reserved        |                           |

| 0x0200_0000 | 0x05FF_FFFF | RW    | CLIC            | On Cara Campley Davises   |

| 0x0600_0000 | 0x1FFF_FFFF |       | Reserved        | On Core Complex Devices   |

| 0x2000_0000 | 0x3FFF_FFFF | RWX   | Peripheral Port |                           |

|             |             |       | (512 MiB)       | Off Core Complex Address  |

| 0x4000_0000 | 0x5FFF_FFF  | RWX   | System Port     | Space for External I/O    |

|             |             |       | (512 MiB)       | Space for External 1/O    |

| 0×6000_0000 | 0x7FFF_FFFF |       | Reserved        |                           |

| 0×8000_0000 | 0x8000_7FFF | RWX   | TIM 0           |                           |

| 0x8000_8000 | 0x8000_FFFF | RWX   | TIM 1           | Tightly Integrated Memory |

| 0x8001_0000 | 0xFFFF_FFFF |       | Reserved        |                           |

**Table 3:** E21 Core Complex Memory Map. Memory Attributes: **R** - Read, **W** - Write, **X** - Execute, **C** - Cacheable, **A** - Atomics

# **Interrupts**

This chapter describes how interrupt concepts in the RISC-V architecture apply to the E21 Core Complex.

Specifically the E21 Core Complex implements 20180709 of the RISC-V Core-Local Interrupt Controller (CLIC) specification. The CLIC represents a new RISC-V interrupt specification which differs from the *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.* As of June 2018, the CLIC is currently a RISC-V draft proposal of the RISC-V foundation's Fast Interrupts Task Group. Future versions of this core may implement later versions of the CLIC specification.

### **5.1** Interrupt Concepts

The E21 Core Complex supports Machine Mode interrupts. It also has support for the following types of RISC-V interrupts: local and global.

Local interrupts are signaled directly to an individual hart with a dedicated interrupt value. This allows for reduced interrupt latency as no arbitration is required to determine which hart will service a given request and no additional memory accesses are required to determine the cause of the interrupt.

The E21 Core Complex has 127 interrupts which are delivered to the core via the Core-Local Interrupt Controller (CLIC) along with the software and timer interrupts.

Global interrupts, by contrast, are routed through a Platform-Level Interrupt Controller (PLIC), which can direct interrupts to any hart in the system via the external interrupt. Decoupling global interrupts from the hart(s) allows the design of the PLIC to be tailored to the platform, permitting a broad range of attributes like the number of interrupts and the prioritization and routing schemes.

This chapter describes the E21 Core Complex interrupt architecture.

Chapter 6 describes the Core-Local Interrupt Controller (CLIC).

The E21 Core Complex does not implement a PLIC. Instead a Machine External Interrupt input signal is exposed at the boundary of the Core Complex which can be connected to a PLIC in a larger design.

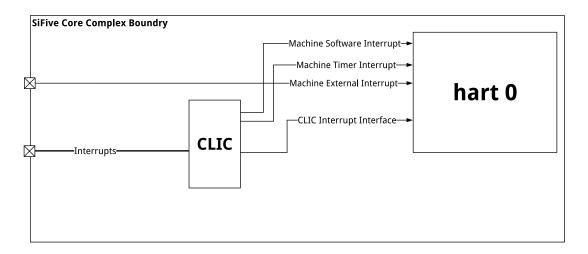

The E21 Core Complex interrupt architecture is depicted in Figure 2.

Figure 2: E21 Core Complex Interrupt Architecture Block Diagram.

### **5.2 Interrupt Operation**

If the global interrupt-enable mstatus.MIE is clear, then no interrupts will be taken. If mstatus.MIE is set, then pending-enabled interrupts at a higher interrupt level will preempt current execution and run the interrupt handler for the higher interrupt level.

When an interrupt or synchronous exception is taken, the privilege mode and interrupt level are modified to reflect the new privilege mode and interrupt level. The global interrupt-enable bit of the handler's privilege mode is cleared.

#### 5.2.1 Interrupt Entry and Exit

When an interrupt occurs:

- The value of mstatus.MIE is copied into mcause.MPIE, and then mstatus.MIE is cleared, effectively disabling interrupts.

- When in CLIC mode, the interrupted interrupt level is copied into mcause.MPIL, and the interrupt level is set to that of the incoming interrupt as defined in its clicintcfg register.

- The privilege mode prior to the interrupt is encoded in mstatus. MPP.

• The current pc is copied into the mepc register, and then pc is set to the value specified by mtvec as defined by the mtvec.MODE described in Table 6.

At this point, control is handed over to software in the interrupt handler with interrupts disabled. Interrupts can be re-enabled by explicitly setting mstatus.MIE or by executing an MRET instruction to exit the handler. When an MRET instruction is executed, the following occurs:

- The privilege mode is set to the value encoded in mstatus. MPP.

- When in CLIC mode, the interrupt level is set to the value encoded in mcause.MPIL.

- The global interrupt enable, mstatus.MIE, is set to the value of mcause.MPIE.

- The pc is set to the value of mepc.

At this point control is handed over to software.

The Control and Status Registers involved in handling RISC-V interrupts are described in Section 5.3.

#### 5.2.2 Interrupt Levels and Priorities

At any time, a hart is running in some privilege mode with some interrupt level. The hart's current interrupt level is made visible in the mintstatus register (Section 5.3.8), however, the current privilege mode is not visible to software running on a hart.

The CLIC architecture supports pre-emption of up to 16 interrupt levels for each privilege mode, where higher-numbered interrupt levels can preempt lower-numbered interrupt levels. Interrupt level 0 corresponds to regular execution outside of an interrupt handler. The CLIC also supports programmable priorities within a given level which are used to prioritize among interrupts pending-and-enabled at the same interrupt level. The highest-priority interrupt at a given interrupt level is taken first. In case there are multiple pending-and-enabled interrupts at the same highest priority, the highest-numbered interrupt ID is taken first.

The number of available pre-emption levels, and priorities within each level, is determined by the number of configuration bits in the CLIC's clicintcfg register and the value of the CLIC's cliccfg.nlbits register.

See Section 6.3.3 and Section 6.3.4 for details of the E21 Core Complex clicintcfg implementation and cliccfg registers respectfully.

#### **5.2.3** Critical Sections in Interrupt Handlers

To implement a critical section between interrupt handlers at different levels, an interrupt handler at any interrupt level can clear global interrupt-enable bit, mstatus.MIE, to prevent interrupts from being taken.

### **5.3 Interrupt Control Status Registers**

The E21 Core Complex specific implementation of interrupt CSRs is described below. For a complete description of RISC-V interrupt behavior and how to access CSRs, please consult *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10* and the RISC-V Core-Local Interrupt Controller Specification Version xx.

#### **5.3.1** Machine Status Register (mstatus)

The mstatus register keeps track of and controls the hart's current operating state, including whether or not interrupts are enabled. A summary of the mstatus fields related to interrupts in the E21 Core Complex is provided in Table 4. Note that this is not a complete description of mstatus as it contains fields unrelated to interrupts. For the full description of mstatus, please consult the *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.*

| Machine Status Register |            |       |                                   |  |

|-------------------------|------------|-------|-----------------------------------|--|

| CSR                     | mstatus    |       |                                   |  |

| Bits                    | Field Name | Attr. | Description                       |  |

| [2:0]                   | Reserved   | WPRI  |                                   |  |

| 3                       | MIE        | RW    | Machine Interrupt Enable          |  |

| [6:4]                   | Reserved   | WPRI  |                                   |  |

| 7                       | MPIE       | RW    | Machine Previous Interrupt Enable |  |

| [10:8]                  | Reserved   | WPRI  |                                   |  |

| [12:11]                 | MPP        | RW    | Machine Previous Privilege Mode   |  |

Table 4: E21 Core Complex mstatus Register (partial)

Interrupts are enabled by setting the MIE bit in mstatus and by enabling the desired individual interrupt in the mie register, described in Section 5.3.3.

Note that when operating in CLIC mode, mstatus.MPP and mstatus.MPIE are accessible in the mcause register described in Section 5.3.5.

#### **5.3.2** Machine Trap Vector (mtvec)

The mtvec register has two main functions: defining the base address of the trap vector, and setting the mode by which the E21 Core Complex will process interrupts. The interrupt processing mode is defined in the lower two bits of the mtvec register as described in Table 6.

| Machine Trap Vector Register |            |                              |                                                                                                                         |  |  |

|------------------------------|------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| CSR                          |            | mtvec                        |                                                                                                                         |  |  |

| Bits                         | Field Name | Field Name Attr. Description |                                                                                                                         |  |  |

| [1:0]                        | MODE       | WARL                         | MODE Sets the interrupt processing mode. The encoding for the E21 Core Complex supported modes is described in Table 6. |  |  |

| [31:2]                       | BASE[31:2] | WARL                         | Interrupt Vector Base Address. Requires 64-byte alignment.                                                              |  |  |

Table 5: mtvec Register

|       | MODE Field Encoding mtvec.MODE |                                                      |  |  |  |

|-------|--------------------------------|------------------------------------------------------|--|--|--|

| Value | Name                           | Description                                          |  |  |  |

| 0x0   | Direct                         | All exceptions set pc to BASE                        |  |  |  |

| 0x1   | Vectored                       | Asynchronous interrupts set pc to BASE + 4 ×         |  |  |  |

|       |                                | cause.                                               |  |  |  |

| 0x2   | CLIC Direct                    | All exceptions set pc to BASE.                       |  |  |  |

| 0x3   | CLIC Vectored                  | Asynchronous interrupts set pc to the address in the |  |  |  |

|       |                                | vector table located at mtvt + 4 × mcause.EXCCODE    |  |  |  |

**Table 6:** Encoding of mtvec.MODE

Note that when in either of the non-CLIC modes, the only interrupts that can be serviced are the architecturally defined software, timer, and external interrupts.

See Table 5 for a description of the mtvec register. See Table 6 for a description of the mtvec.MODE field. See Table 10 for the E21 Core Complex interrupt exception code values.

#### **Mode Direct**

When operating in direct mode all synchronous exceptions and asynchronous interrupts trap to the mtvec.BASE address. Inside the trap handler, software must read the mcause register to determine what triggered the trap.

#### **Mode Vectored**

While operating in vectored mode, interrupts set the pc to  $mtvec.BASE + 4 \times exception$  code. For example, if a machine timer interrupt is taken, the pc is set to mtvec.BASE + 0x1C. Typically, the trap vector table is populated with jump instructions to transfer control to interrupt-specific trap handlers.

In vectored interrupt mode, BASE must be 64-byte aligned.

All machine external interrupts (global interrupts) are mapped to exception code of 11. Thus, when interrupt vectoring is enabled, the pc is set to address mtvec.BASE + 0x2C for any global interrupt.

#### **Mode CLIC Direct**

In CLIC Direct mode the processor jumps to the 64-byte-aligned trap handler address held in the upper XLEN-6 bits of mtvec for all exceptions and interrupts.

In CLIC interrupt mode, BASE must be 64-byte aligned.

#### **Mode CLIC Vectored**

In vectored CLIC mode, on an interrupt, the processor switches to the handler's privilege mode and sets the hardware vectoring bit mcause.MINHV, then fetches an XLEN-bit handler address from the in-memory vector table pointed to by mtvt described in Section 5.3.6. The address fetched is defined in the following formula:

mtvt+4×mcause.EXCCODE.

If the fetch is successful, the processor clears the low bit of the handler address, sets the PC to this handler address, then clears mcause.MINHV. The hardware vectoring bit minhv is provided to allow resumable traps on fetches to the trap vector table.

Synchronous exceptions always trap to mtvec.BASE in machine mode.

#### 5.3.3 Machine Interrupt Enable (mie)

Individual interrupts are enabled by setting the appropriate bit in the mie register. The mie register is described in Table 7.

| Machine Interrupt Enable Register |            |                              |                                   |  |

|-----------------------------------|------------|------------------------------|-----------------------------------|--|

| CSR                               | mie        |                              |                                   |  |

| Bits                              | Field Name | Field Name Attr. Description |                                   |  |

| [2:0]                             | Reserved   | WPRI                         |                                   |  |

| 3                                 | MSIE       | RW                           | Machine Software Interrupt Enable |  |

| [6:4]                             | Reserved   | WPRI                         |                                   |  |

| 7                                 | MTIE       | RW                           | Machine Timer Interrupt Enable    |  |

| [10:8]                            | Reserved   | WPRI                         |                                   |  |

| 11                                | MEIE       | RW                           | Machine External Interrupt Enable |  |

| [31:12]                           | Reserved   | WPRI                         |                                   |  |

Table 7: mie Register

When in either of the CLIC modes, the mie register is hardwired to zero and individual interrupt enables are controlled by the clicintie[i] CLIC memory-mapped registers. See Chapter 6 for a detailed description of clicintie.

#### 5.3.4 Machine Interrupt Pending (mip)

The machine interrupt pending (mip) register indicates which interrupts are currently pending. The mip register is described in Table 8.

|         | Machine Interrupt Pending Register |       |                                    |  |  |  |

|---------|------------------------------------|-------|------------------------------------|--|--|--|

| CSR     |                                    |       | mip                                |  |  |  |

| Bits    | Field Name                         | Attr. | Description                        |  |  |  |

| [2:0]   | Reserved                           | WIRI  |                                    |  |  |  |

| 3       | MSIP                               | RO    | Machine Software Interrupt Pending |  |  |  |

| [6:4]   | Reserved                           | WIRI  |                                    |  |  |  |

| 7       | MTIP                               | RO    | Machine Timer Interrupt Pending    |  |  |  |

| [10:8]  | Reserved                           | WIRI  |                                    |  |  |  |

| 11      | MEIP                               | RO    | Machine External Interrupt Pending |  |  |  |

| [31:12] | Reserved                           | WIRI  |                                    |  |  |  |

Table 8: mip Register

In CLIC mode, the mip register is hardwired to zero and individual interrupt enables are controlled by the clicintip[i] CLIC memory-mapped registers. See Chapter 6 for a detailed description of clicintip.

#### **5.3.5** Machine Cause (mcause)

When a trap is taken in machine mode, meause is written with a code indicating the event that caused the trap. When the event that caused the trap is an interrupt, the most-significant bit of meause is set to 1, and the least-significant bits indicate the interrupt number, using the same encoding as the bit positions in mip. For example, a Machine Timer Interrupt causes meause to be set to 0x8000\_0007. meause is also used to indicate the cause of synchronous exceptions, in which case the most-significant bit of meause is set to 0.

When in either of the CLIC modes, meause is extended to record more information about the interrupted context which is used to reduce the overhead to save and restore that context for an mret instruction. CLIC mode meause also adds state to record progress through the trap handling process.

See Table 9 for more details about the mcause register. Refer to Table 10 for a list of synchronous exception codes.

|         | Machine Cause Register |       |                                             |  |  |  |

|---------|------------------------|-------|---------------------------------------------|--|--|--|

| CSR     |                        |       | mcause                                      |  |  |  |

| Bits    | Field Name             | Attr. | Description                                 |  |  |  |

| [9:0]   | Exception Code         | WLRL  | A code identifying the last exception.      |  |  |  |

| [22:10] | Reserved               | WLRL  |                                             |  |  |  |

| 23      | mpie                   | WLRL  | Previous interrupt enable, same as          |  |  |  |

|         |                        |       | mstatus.mpie. CLIC mode only.               |  |  |  |

| [27:24] | mpil                   | WLRL  | Previous interrupt level. CLIC mode only.   |  |  |  |

| [29:28] | mpp                    | WLRL  | Previous interrupt privilege mode, same as  |  |  |  |

|         |                        |       | mstatus.mpp. CLIC mode only.                |  |  |  |

| 30      | minhv                  | WIRL  | Hardware vectoring in progress when set.    |  |  |  |

|         |                        |       | CLIC mode only.                             |  |  |  |

| 31      | Interrupt              | WARL  | 1 if the trap was caused by an interrupt; 0 |  |  |  |

|         |                        |       | otherwise.                                  |  |  |  |

Table 9:

mcause Register

|           | Interrupt Exception Codes |                                        |  |  |  |  |

|-----------|---------------------------|----------------------------------------|--|--|--|--|

| Interrupt | Exception Code            | Description                            |  |  |  |  |

| 1         | 0–2                       | Reserved                               |  |  |  |  |

| 1         | 3                         | Machine software interrupt             |  |  |  |  |

| 1         | 4–6                       | Reserved                               |  |  |  |  |

| 1         | 7                         | Machine timer interrupt                |  |  |  |  |

| 1         | 8–10                      | Reserved                               |  |  |  |  |

| 1         | 11                        | Machine external interrupt             |  |  |  |  |

| 1         | 12                        | CLIC Software Interrupt Pending (CSIP) |  |  |  |  |

| 1         | 13–15                     | Reserved                               |  |  |  |  |

| 1         | 16                        | CLIC Local Interrupt 0                 |  |  |  |  |

| 1         | 17                        | CLIC Local Interrupt 1                 |  |  |  |  |

| 1         | 18–126                    |                                        |  |  |  |  |

| 1         | 143                       | CLIC Local Interrupt 127               |  |  |  |  |

| 0         | 0                         | Instruction address misaligned         |  |  |  |  |

| 0         | 1                         | Instruction access fault               |  |  |  |  |

| 0         | 2                         | Illegal instruction                    |  |  |  |  |

| 0         | 3                         | Breakpoint                             |  |  |  |  |

| 0         | 4                         | Load address misaligned                |  |  |  |  |

| 0         | 5                         | Load access fault                      |  |  |  |  |

| 0         | 6                         | Store/AMO address misaligned           |  |  |  |  |

| 0         | 7                         | Store/AMO access fault                 |  |  |  |  |

| 0         | 8                         | Environment call from U-mode           |  |  |  |  |

| 0         | 9–10                      | Reserved                               |  |  |  |  |

| 0         | 11                        | Environment call from M-mode           |  |  |  |  |

| 0         | ≥ 12                      | Reserved                               |  |  |  |  |

Table 10: mcause Exception Codes

#### 5.3.6 Machine Trap Vector Table (mtvt)

The mtvt register holds the base address of the trap vector table. mtvt must be 64-byte aligned and values other than 0 in the low 6 bits of mtvt are reserved.

| Machine Trap Vector Table Register |                 |       |                                       |  |  |

|------------------------------------|-----------------|-------|---------------------------------------|--|--|

| CSR                                | <b>CSR</b> mtvt |       |                                       |  |  |

| Bits                               | Field Name      | Attr. | Description                           |  |  |

| [31:6]                             | Base            | WARL  | Base address of the CLIC Vector Table |  |  |

| [5:0]                              | Reserved        | WARL  |                                       |  |  |

Table 11: mtvt Register

#### 5.3.7 Handler Address and Interrupt-Enable (mnxti)

The mnxti CSR can be used by software to service the next horizontal interrupt when it has greater level than the saved interrupt context (held in mcause.PIL), without incuring the full cost of an interrupt pipeline flush and context save/restore. The mnxti CSR is designed to be accessed using CSRRSI/CSRRCI instructions, where the value read is a pointer to an entry in the trap handler table and the write back updates the interrupt-enable status. In addition, accesses to the mnxti register have side-effects that update the interrupt context state.

Note that this is different than a regular CSR instruction as the value returned is different from the value used in the read-modify-write operation.

A read of the mnxti CSR returns either zero, indicating there is no suitable interrupt to service, or the address of the entry in the trap handler table for software trap vectoring.

If the CSR instruction that accesses mnxti includes a write, the mstatus CSR is the one used for the read-modify-write portion of the operation, while the exception code in mcause and the mintstatus register's mil field can also be updated with the new interrupt level. If the CSR instruction does not include write side effects (e.g., csrr t0, mnxti), then no state update on any CSR occurs.

The mnxti CSR is intended to be used inside an interrupt handler after an initial interrupt has been taken and mcause and mepc registers updated with the interrupted context and the id of the interrupt.

#### 5.3.8 Machine Interrupt Status (mintstatus)

A new M-mode CSR, mintstatus, holds the active interrupt level for each supported privilege mode. These fields are read-only. The primary reason to expose these fields is to support debug.

| Machine Interrupt Status Register |            |       |                                     |  |  |

|-----------------------------------|------------|-------|-------------------------------------|--|--|

| CSR                               | mintstatus |       |                                     |  |  |

| Bits                              | Field Name | Attr. | Description                         |  |  |

| [11:0]                            | Reserved   | WIRI  |                                     |  |  |

| [15:12]                           | mil        | WIRL  | Active Machine Mode Interrupt Level |  |  |

| [32:13]                           | Reserved   | WIRI  |                                     |  |  |

Table 12: E21 Core Complex mintstatus Register

# **5.4** Interrupt Latency

Interrupt latency for the E21 Core Complex is 6 cycles, as counted by the numbers of cycles it takes from signaling of the interrupt to the hart to the first instruction fetch of the handler.

Additionally, the hart will not abandon a Divide instruction in flight. This means if an interrupt handler tries to use a register that is the destination register of a divide instruction the pipeline stalls until the divide is complete.

# **Core-Local Interrupt Controller (CLIC)**

This chapter describes the operation of the Core-Local Interrupt Controller (CLIC). The E21 Core Complex implements 20180709 of the RISC-V CLIC specification.

### **6.1 Interrupt Sources**

The E21 Core Complex has 127 interrupt sources which can be connected to peripheral devices in addition to the standard RISC-V software and timer interrupts. These interrupt inputs are exposed at the top level via the <code>local\_interrupts</code> signals. Any unused <code>local\_interrupts</code> inputs should be tied to logic 0. These signals are positive-level triggered.

The E21 Core Complex does not include a PLIC which is used to signal External Interrupts. A machine\_external\_interrupt signal is exposed at the top level which can be used to integrate the E21 Core Complex with an external PLIC.

CLIC Interrupt IDs are provided in the in Table 13.

|         | E21 Core Complex Interrupt IDs |                            |  |  |  |

|---------|--------------------------------|----------------------------|--|--|--|

| ID      | Interrupt                      | Notes                      |  |  |  |

| 2 - 0   | Reserved                       |                            |  |  |  |

| 3       | msip                           | Machine Software Interrupt |  |  |  |

| 6 - 4   | Reserved                       |                            |  |  |  |

| 7       | mtip                           | Machine Timer Interrupt    |  |  |  |

| 10 - 8  | Reserved                       |                            |  |  |  |

| 11      | meip                           | Machine Extneral Interrupt |  |  |  |

| 12      | csip                           | CLIC Software Interrupt    |  |  |  |

| 15 - 13 | Reserved                       |                            |  |  |  |

| 16      | lint0                          | Local Interrupt 0          |  |  |  |

| 17      | lint1                          | Local Interrupt 1          |  |  |  |

|         | lintX                          | Local Interrupt X          |  |  |  |

| 143     | lint127                        | Local Interrupt 127        |  |  |  |

**Table 13:** E21 Core Complex Interrupt IDs

# 6.2 CLIC Memory Map

The CLIC memory map is separated into multiple regions depending on the number of harts which implement a CLIC; one shared region, and hart specific regions. This allows for backwards compatibility with the Core Local Interruptor (CLINT) and its msip, mtimecmp, and mtime memory-mapped registers as well as compatibility between CLIC and non-CLIC harts. The base address for all regions are provided below in Table 14.

|                      | Base Address for CLIC regions |                                                                                                            |  |  |  |  |

|----------------------|-------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Address Region Notes |                               |                                                                                                            |  |  |  |  |

| 0x0200_0000          | Shared                        | RISC-V Standard CLINT Base. The specific implementation of this region is described in detail in Table 15. |  |  |  |  |

| 0x0280_0000          | Hart 0                        | Hart 0 CLIC Base. The specific implementation of this region is described in detail in Table 16.           |  |  |  |  |

Table 14: CLIC Base Address

| CLIC Shared Region |       |       |                     |                             |  |  |  |

|--------------------|-------|-------|---------------------|-----------------------------|--|--|--|

| Offset             | Width | Attr. | Description         | Notes                       |  |  |  |

| 0x0                | 4B    | RW    | msip for hart 0     | MSIP Registers (1 bit wide) |  |  |  |

| 0x4008             |       |       | Reserved            |                             |  |  |  |

|                    |       |       |                     |                             |  |  |  |

| 0xbff7             |       |       |                     |                             |  |  |  |

| 0x4000             | 8B    | RW    | mtimecmp for hart 0 | MTIMECMP Registers          |  |  |  |

| 0x4008             |       |       | Reserved            |                             |  |  |  |

|                    |       |       |                     |                             |  |  |  |

| 0xbff7             |       |       |                     |                             |  |  |  |

| 0xbff8             | 8B    | RW    | mtime               | Timer Register              |  |  |  |

| 0xc000             |       |       | Reserved            |                             |  |  |  |

Table 15: CLIC Shared Register Map

|                         | CLIC Hart Specific Region     |            |                                        |  |  |  |  |

|-------------------------|-------------------------------|------------|----------------------------------------|--|--|--|--|

| Offset Width Name Notes |                               |            |                                        |  |  |  |  |

| 0x000                   | 1B per interrupt-id           | CLICINTIP  | CLIC Interrupt Pending Registers       |  |  |  |  |

| 0x400                   | 1B per interrupt-id CLICINTIE |            | CLIC Interrupt Enable Registers        |  |  |  |  |

| 0x800                   | 1B per interrupt-id           | CLICINTCFG | CLIC Interrupt Configuration Registers |  |  |  |  |

| 0xC00                   | 1B                            | CLICCFG    | CLIC Configuration Register            |  |  |  |  |

Table 16: CLIC Hart Specific Region Map

# 6.3 Registers

This section will describe the functionality of the CLIC's registers.

#### 6.3.1 CLIC Interrupt Pending (clicintip)

| CLIC Interrupt Pending |            |                                                                                 |   |  |  |

|------------------------|------------|---------------------------------------------------------------------------------|---|--|--|

| Address                |            | CLIC Hart Base + 1×Interrupt ID                                                 |   |  |  |

| Bits                   | Field Name | Field Name Attr. RST. Description                                               |   |  |  |

| 0                      | clicintip  | clicintip RW 0 When clicintip is set, the corresponding Interrupt ID is pending |   |  |  |

| [7:1]                  | Reserved   | RO                                                                              | 0 |  |  |

Table 17: clicintip Register

When in CLIC mode, the Machine Interrupt Pending (mip) CSR is hardwired to zero and interrupt pending status is instead presented in the clicintip memory-mapped registers.

#### 6.3.2 CLIC Interrupt Enable (clicintie)

| CLIC Interrupt Enable |            |                                         |   |                                                                  |  |

|-----------------------|------------|-----------------------------------------|---|------------------------------------------------------------------|--|

| Address               |            | CLIC Hart Base + 0x400 + 1×Interrupt ID |   |                                                                  |  |

| Bits                  | Field Name | Field Name Attr. RST. Description       |   |                                                                  |  |

| 0                     | clicintie  | RW                                      | 0 | When clicintie is set, the corresponding Interrupt ID is enabled |  |

| [7:1]                 | Reserved   | RO                                      | 0 | sponding interrupt to is enabled                                 |  |

**Table 18:** clicintip Register

When in CLIC mode, the Machine Interrupt Enable (mie) CSR is hardwired to zero and interrupt enables are instead presented in the clicintie memory-mapped registers.

#### 6.3.3 CLIC Interrupt Configuration (clicintcfg)

|         | CLIC Interrupt Configuration            |    |   |                                                                          |  |  |

|---------|-----------------------------------------|----|---|--------------------------------------------------------------------------|--|--|

| Address | CLIC Hart Base + 0x800 + 1×Interrupt ID |    |   |                                                                          |  |  |

| Bits    | Field Name Attr. RST. Description       |    |   |                                                                          |  |  |

| [3:0]   | Reserved                                | RO | 0 |                                                                          |  |  |

| [7: 3]  | clicintcfg                              | RW | 0 | clicintcfg sets the pre-emption level and priority of a given interrupt. |  |  |

**Table 19:** clicintcfg Register

The E21 Core Complex has a total of 4 bits in clicintcfg which specify how to encode a given interrupt's pre-emption level and/or priority. The actual number of bits which determine the pre-emption level is determined by cliccfg.NLBITS. If cliccfg.NLBITS is < 4, then the remaining least significant implemented bits are used to encode priorities within a given pre-emption level. If cliccfg.NLBITS is set to zero, then all interrupts are treated as level 15 and all 4 bits are used to set priorities.

See Section 5.2.2 for a description of CLIC levels and priorities.

| 6.3.4 | CLIC | Configuration ( | (cliccfg) |

|-------|------|-----------------|-----------|

|-------|------|-----------------|-----------|

|         | CLIC Configuration |                        |      |                                                             |  |

|---------|--------------------|------------------------|------|-------------------------------------------------------------|--|

| Address |                    | CLIC Hart Base + 0xC00 |      |                                                             |  |

| Bits    | Field Name         | Attr.                  | RST. | Description                                                 |  |

| [0]     | nvbits             | RW                     | 0    | When set, selective hardware vectoring is enabled.          |  |

| [3:1]   | nlbits             | RW                     | 0    | Determines the number of Level bits available in clicintcfg |  |

| [5:4]   | nmbits             | RO                     | 0    | Determines the number Mode bits available in clicintcfg.    |  |

Table 20: clicintcfg Register

The cliccfg register is used to configure the operation of the CLIC primarily by determining the function of the bits implemented in clicintcfg bits. The E21 Core Complex only supports Machine Mode interrupts, therefore cliccfg.NMBITS is set to zero.

cliccfg.NLBITS is used to determine the number of clicintcfg bits used for levels vs priorities. The CLIC supports a maximum of 16 pre-emption levels which requires 4 bits to encode all 16 levels. For values of cliccfg.NLBITS 4, the lower bits are assumed to be all 1s. The resulting encoding of cliccfg.NLBITS to interrupt levels is shown below.

| #NLBITS | encoding |     |      | in <sup>.</sup> | terrı | upt le | evels  |        |      |