# SKP Engineering College

Tiruvannamalai - 606611

A Course Material

on

**Computer Architecture**

Ву

**G.Nanda kumar**

**Assistant Professor**

**Computer Science and Engineering Department**

## **Quality Certificate**

This is to Certify that the Electronic Study Material

Subject Code: CS6303

Subject Name: Computer Architecture

Year/Sem: III/VI

Being prepared by me and it meets the knowledge requirement of the University curriculum.

Signature of the Author

Name: G.Nanda kumar

Designation: Assistant Professor

This is to certify that the course material being prepared by Mr. G.Nanda kumar is of the adequate quality. He has referred more than five books and one among them is from abroad author.

Signature of HD Signature of the Principal

Name: Dr.V.Subramania Bharathi

Seal: Seal:

#### CS6303 COMPUTER ARCHITECTURE

LTPC3003

#### **OBJECTIVES:**

- To make students understand the basic structure and operation of digital computer.

- To understand the hardware-software interface.

- To familiarize the students with arithmetic and logic unit and implementation of fixed point and floating-point arithmetic operations.

- To expose the students to the concept of pipelining.

- To familiarize the students with hierarchical memory system including cache memories and virtual memory.

- To expose the students with different ways of communicating with I/O devices and standard I/O interfaces.

#### **UNIT I OVERVIEW & INSTRUCTIONS**

9

Eight ideas – Components of a computer system – Technology – Performance – Power wall – Uniprocessors to multiprocessors; Instructions – operations and operands – representing instructions – Logical operations – control operations – Addressing and addressing modes.

#### **UNIT II ARITHMETIC OPERATIONS**

7

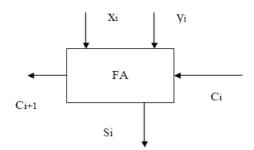

ALU - Addition and subtraction – Multiplication – Division – Floating Point operations – Subword parallelism.

#### **UNIT III PROCESSOR AND CONTROL UNIT**

11

Basic MIPS implementation – Building datapath – Control Implementation scheme – Pipelining – Pipelined datapath and control – Handling Data hazards & Control hazards – Exceptions.

#### **UNIT IV PARALLELISM**

9

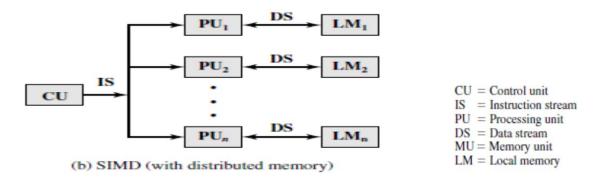

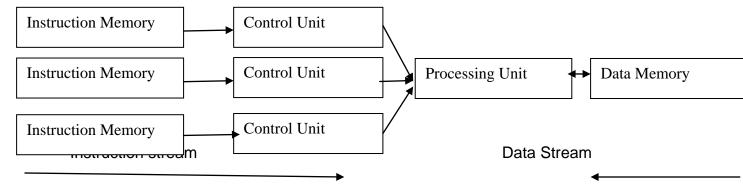

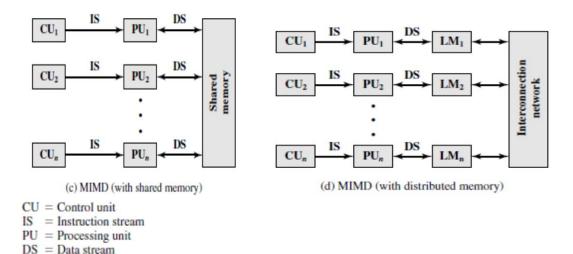

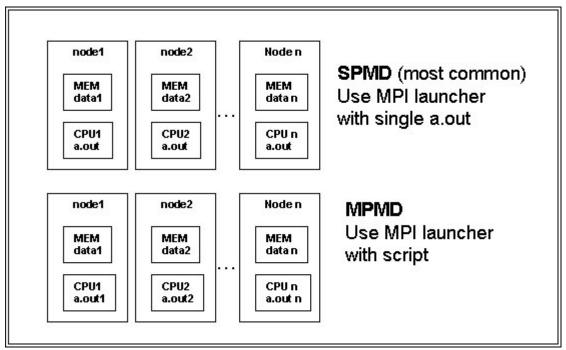

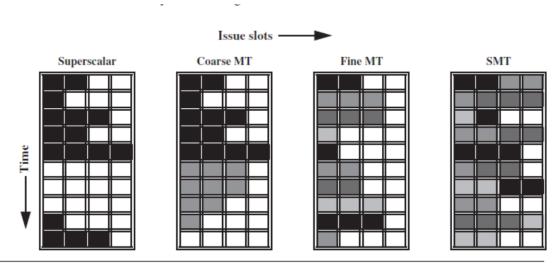

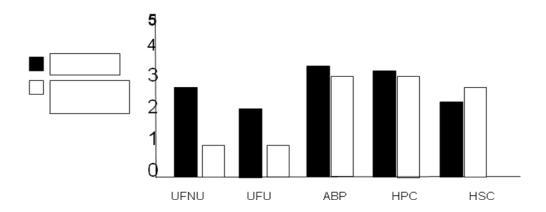

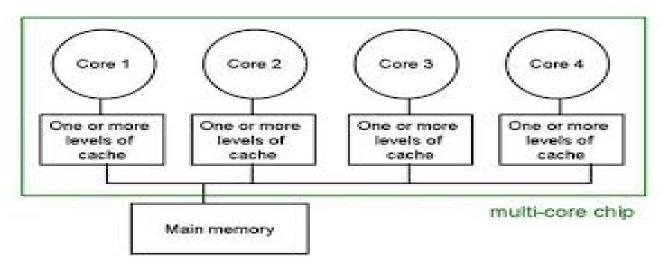

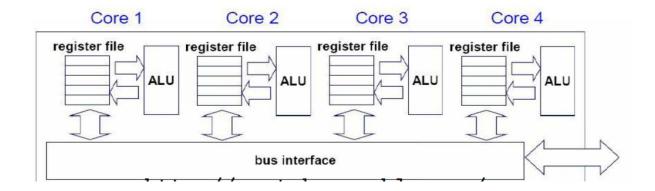

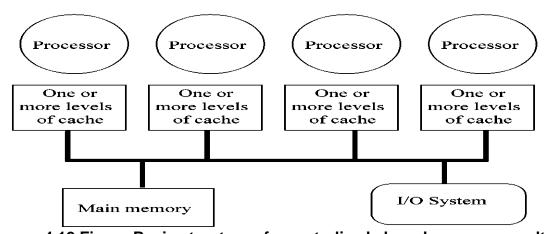

Instruction-level-parallelism – Parallel processing challenges – Flynn's classification – Hardware multithreading – Multicore processors

#### **UNIT V MEMORY AND I/O SYSTEMS**

9

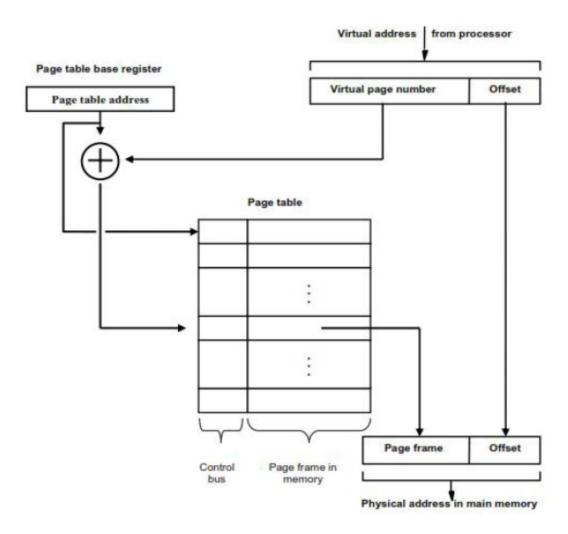

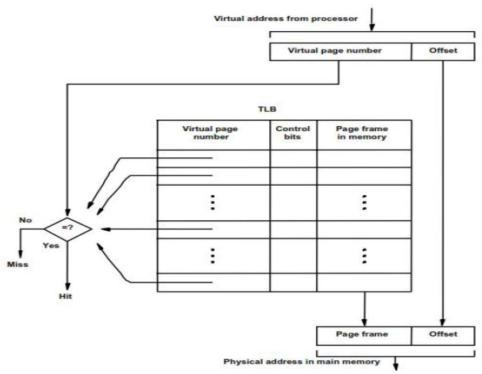

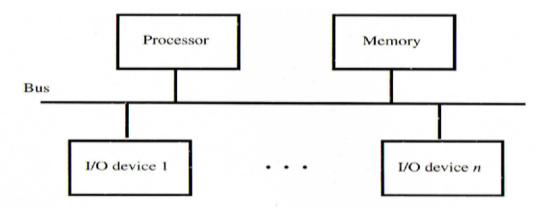

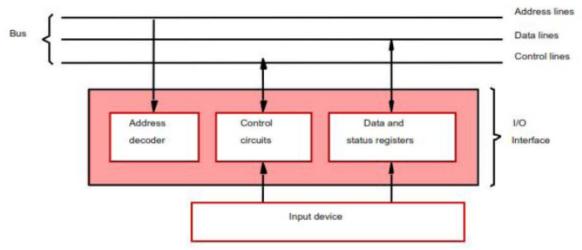

Memory hierarchy - Memory technologies – Cache basics – Measuring and improving cache performance - Virtual memory, TLBs - Input/output system, programmed I/O, DMA and interrupts, I/O processors.

## **OUTCOMES**: At the end of the course, the student should be able to:

Design arithmetic and logic unit.

- Design and anlayse pipelined control units

- Evaluate performance of memory systems.

- Understand parallel processing architectures.

#### **TEXT BOOK:**

1. David A. Patterson and John L. Hennessey, "Computer organization and design", Morgan Kauffman / Elsevier, Fifth edition, 2014.

#### **REFERENCES:**

- 1. V.Carl Hamacher, Zvonko G. Varanesic and Safat G. Zaky, "Computer Organisation", VI th edition, Mc Graw-Hill Inc, 2012.

- 2. William Stallings "Computer Organization and Architecture", Seventh Edition, Pearson Education, 2006.

- 3. Vincent P. Heuring, Harry F. Jordan, "Computer System Architecture", Second Edition, Pearson Education, 2005.

- 4. Govindarajalu, "Computer Architecture and Organization, Design Principles and Applications", first edition, Tata McGraw Hill, New Delhi, 2005.

- 5. John P. Hayes, "Computer Architecture and Organization", Third Edition, Tata Mc Graw Hill, 1998.

- 6. http://nptel.ac.in/.

# **CONTENTS**

| S.No | Particulars | Page |

|------|-------------|------|

| 1    | Unit – I    | 06   |

| 2    | Unit – II   | 39   |

| 3    | Unit – III  | 83   |

| 4    | Unit – IV   | 120  |

| 5    | Unit – V    | 148  |

#### Unit - I

#### **OVERVIEW & INSTRUCTIONS**

#### PART-A

#### 1. Define Computer Architecture.

Computer Architecture refers to the attributes of a system visible to a programmer or the attributes that have a direct impact on the logical execution of a program. Examples of architectural attribute Instruction Set The number of bits used to represent various data types (numbers, characters) IO mechanisms & techniques for addressing memory.

## 2. Define Computer Organization.

Computer organization refers to the operational units and their inter connections that realize the architectural specifications **Example** for Organizational attributes: Hardware details transparent to the programmer such as Control signals, Interface between the computer & Peripherals and the memory technology used.

### 3. What is difference between Computer Architecture and Computer Organization?

| S.<br>no | Computer Architecture                                                                                                     | Computer Organization                                                                                                             |  |

|----------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| 1.       | It refers to the attributes that have a direct impact on the logical execution of the program.                            | It refers to the operational units and their interconnections that realize the architectural specifications                       |  |

| 2.       | Architectural attributes includes the Instruction set, data types, no of bits used to represent the data, I/O mechanisms. | Organizational attributes include those h/w details such as control signals, interfaces b/w the computer memory & I/O peripherals |  |

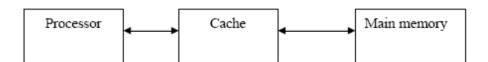

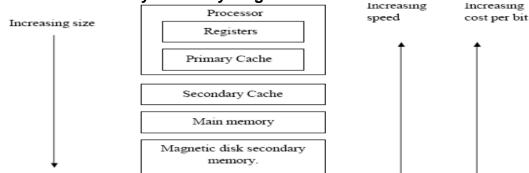

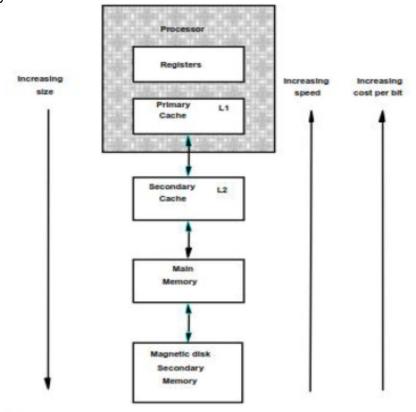

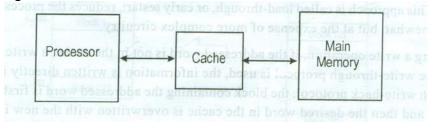

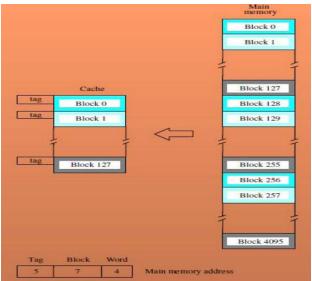

### 4. What is cache memory? (Nov/Dec-2013)

The small and fast memory is called cache memory. The frequently accessed information are transferred from main memory to cache memory. It gives fast access of data.

#### 5. What is the function of control unit?

The Control unit is the main part of the computer that coordinates the entire computer operations. Data transfers between the processor and memory controlled by the control unit through timing signal.

#### 6. What are the registers generally contained in the processor?

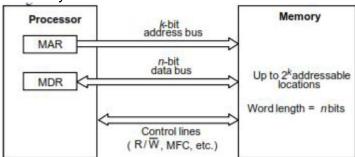

MAR - Memory Address Register.

MDR - Memory Data Register.

IR – Instruction Register.

R<sub>0</sub> – Rn – General purpose Register.PC – Program Counter.

# 7. What do you mean by Memory address register (MAR) and Memory data register(MDR)?

The MAR holds the address of the location to be accessed. The MDR contains the data to be written into or read out of the addressed location.

#### 8. What is Multiprogramming or multi tasking?

The OS manages the concurrent execution of several application programs to make the best possible uses of computer resources. This pattern of concurrent execution is called multiprogramming or multitasking.

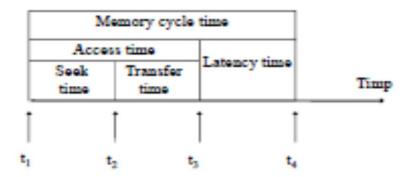

#### 9. What is elapsed time of computer system?

The total time required to execute the total program is called elapsed time. It is affected by the speed of the processor, the disk and the printer.

#### 10. What is processor time of a program?

The period during which the processor is active is called processor time of a program. It depends on the hardware involved in the execution of individual machine instructions.

#### 11. Define clock rate?

The clock rate is given by, **R=1/P,**where P is the length of one clock. It can be measure as cycles per second (Hertz).

### 12. What is meant by clock cycle?

Processor circuit is controlled by a timing signal called a clock. The clock defines regular time intervals, called clock cycle. To execute the machine instruction the processor divides the action to be performed into sequence of basic steps; each step can be completed in one clock cycle.

# 13. Write down the basic performance equation?(Apr/May-2014)

T=N\*S/R

Where T-Processor time

N-Number of machine instructions

S-Number of basic steps needed to execute one machine instruction

R-Clock rate

# 14. What is meant by addressing mode? Mention most important of them. (May/June 2013)

The addressing mode is defined as the different ways in which the location or of an operand is specified in an instruction.

The different types of addressing modes are:

Immediate addressing mode

Register addressing mode

Direct or absolute addressing mode

Indirect addressing mode

indexed addressing mode

Relative addressing mode

Auto increment, Auto decrement

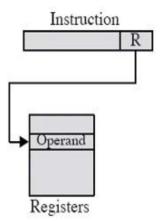

#### 15. Define Register addressing mode with an example.

In register addressing mode, the operand is the contents of a processor register. The name (address) of the register is given in the instruction. **Effective address (EA) = Ri, Where Ri is a processor register.**

#### 16. Define absolute addressing mode with an example.

In absolute addressing mode, the operand is in a memory location. The addresses of this location are given explicitly in the instruction. This is also called as direct addressing mode. **EA = Loc Where loc is the memory address.**

# 17. What is relative addressing mode? When is it used? (May/ June 2012) (Nov/Dec-14)

The effective address is determined by the index mode using program counter in place of the general purpose registersThis address is commonly used to specify the target address in branch instruction**Example: JNZ BACK.**This instruction causes program executive to go to the branch target location identified by the name BACK, if the branch condition is satisfied.

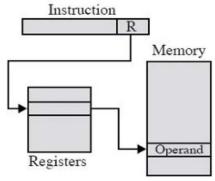

#### 18. What is indirect addressing mode?

The Effective address of the operand is the contents of a register or memory location whose address appears in the instruction **EA = [Ri] or EA = [Loc]**

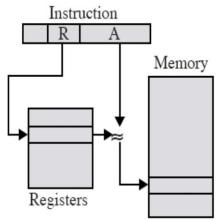

### 19. What is indexed addressing mode?

The Effective address of the operand is generated by adding a constant value to the register. EA = X + [Ri].

#### 20. Define auto increment mode of addressing?

The Effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are automatically incremented to point to the next item in the list. EA = (Ri) +

#### 21. Define auto decrement mode of addressing?

The contents of a register specified in the instruction are first automatically decremented and are then used as the effective address of the operand. **EA = - (Ri)**

#### 22. List the basic instruction types?

The various instruction types are,

Three address instructions

Two-address instructions

Single-address instructions

Zero-address instructions

#### 23. Name five parts of the computer components.

There are five parts in computer components

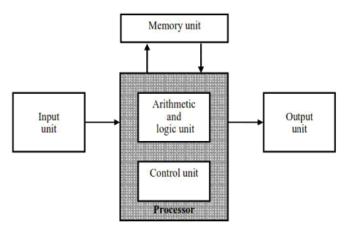

Input Memory, Arithmetic and logic, Output and Control units.

#### 24. What is register?

In a computer, a register is one of a small set of data holding places that are part of a computer <u>processor</u>. A register may hold a computer <u>instruction</u>, a storage address, or any kind of data (such as a bit sequence or individual characters). Some instructions specify registers as part of the instruction. For example, an instruction may specify that the contents of two defined registers be added together and then placed in a specified register.

# 25. List the phases, which are included in the each instruction cycle?(or). What are major steps to process an instruction.

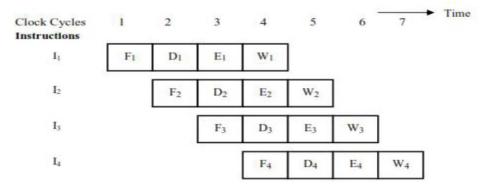

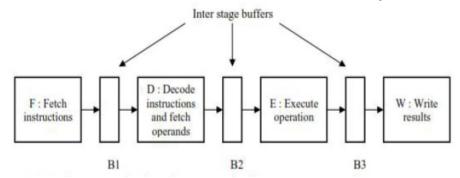

**Fetch:** fetches instruction from main memory (M)**Decode:** decodes the instruction's opcode**Load:** loads (read) from Memory any operands needed unless they are already in CPU Registers **Execute**: Executes the instruction via a register-to-register operation using an appropriate functional unit of the CPU such as a fixed–point adder.**Store:** Stores (write) the results in Memory unless they are to be retained in CPU register.

# 26. What are the speedup techniques available to increase the performance of a computer?

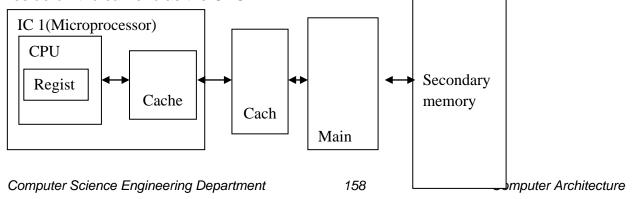

**Cache:** It is a fast accessible memory often placed on the same chip as the CPU. It is used to reduce the average time required to access an instruction or data to a single clock cycle.

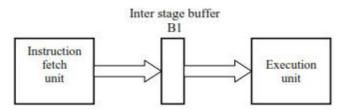

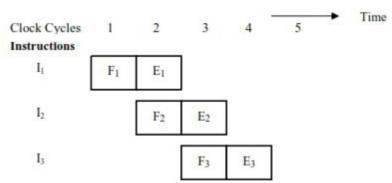

**Pipelining:** Allows the processing of several instructions to be partially overlapped. **Super scalar:** Allows processing of several instructions in parallel (full overlapping)

#### 27. What are Timing signals?

Timing signals are signals that determine when a given action is to take place. Data transfers between the processor and the memory are also controlled by the control unit through timing signals.

# 28. Distinguish between auto increment and auto decrement addressing mode. (April/May 2010)

| (7 tp: 10 to 10)                                                                                                                                                                                              | ( ip : ia : ia )                                                                                                                                                                |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Auto increment                                                                                                                                                                                                | Auto decrement                                                                                                                                                                  |  |  |  |  |  |  |

| 1) The effective address of the operand is the contents of the register specified in the instruction. After accessing the operand, the contents of the register are incremented to address the next location. | <ol> <li>The contents of a register<br/>specified in the instruction are<br/>decremented and then are used<br/>as effective address to access a<br/>memory location.</li> </ol> |  |  |  |  |  |  |

| 2) Auto increment is symbolically represented as (R <sub>i</sub> )+.                                                                                                                                          | <ol> <li>Auto decrement mode is<br/>symbolically represented as -(R<sub>i</sub>).</li> </ol>                                                                                    |  |  |  |  |  |  |

| 3) Example: move( $R_2$ ), $R_0$ +                                                                                                                                                                            | 3) Example:<br>Move R <sub>1</sub> , -(R <sub>0</sub> )                                                                                                                         |  |  |  |  |  |  |

# 29. What is an opcode? How many bits are needed to specify 32 distinct operations? (April/May 2011)

An **opcode** is the first byte of an instruction in machine language which tells the hardware what operation needs to be performed with this instruction. Every processor/controller has its own set of opcodes defined in its architecture. Opcode is the operation to be performed on data. An opcode is followed by data like address, values etc if needed. 5 bits are needed to specify 32 distinct operations.

### 30. Define word length.( Nov/Dec 2011)

In computer architecture, a word is a unit of data of a defined bit length that can be addressed and moved between storage and the computer processor. The number of bits in the word is called word length.

31. Suppose you wish to run a program P with 8.5 \* 109 instructions on a 5 Ghz machine with CPI of 0.8. What is the expected CPU time? (Nov/Dec 2010) Percentage of elapsed time=(User CPU Time + System CPU Time)/Elapsed Time Expected CPU time =0.8-0.2\*8.5\*109=1.36.

## 32. Mention the registers used for communications between processor and main memory. (May/June 2010)

MAR( Memory Address Register): The Memory Address Register (MAR) is a CPU register that either stores the memory address from which data will be fetched to the CPU or the address to which data will be sent and stored.

MDR (Memory Data Register): It is the register of a computer's control unit that contains the data to be stored in the computer storage (e.g. RAM), or the data after a fetch from the computer storage. It acts like a buffer and holds anything that is copied from the memory ready for the processor to use it.

### 33. What is SPEC? Specify the formula for SPEC rating. (May/ June 2012)(Apr/May-2014)

SPEC is a nonprofit consortium of 22 major computer vendors whose common goals are "to provide the industry with a realistic yardstick to measure the performance of advanced computer systems" and to educate consumers about the performance of vendors' products. The formula for SPEC rating is as follows:

#### SPEC rating (ratio) = TR / TC;

where.

TR = Running time of the Reference Computer;

TC = Running time of the Computer under test;

# 34. Give an example each of zero-address, one-address, two-address and threeaddress instructions. (May/June 2006)

Zero address- push (Push the value as top of stock)

One address- INC CL (If carry set, increment CL by one) Two address- Add A,B  $(A \leftarrow A+B)$

Three address- Add A,B,C  $(A \leftarrow B+C)$

### 35. Which data structures can be best supported using (a) indirect addressing mode (b) indexed addressing mode? (May/June 2006)

- (a) Indirect addressing mode Pointer data structure

- (b) Indexed addressing mode- Array data structure

# 36. What are the four basic types of operations that need to be supported by an instructor set? (May/June 2006)

Data transfer between memory and the processor register.

Arithmetic and logic operations on Data

Program sequencing and control

I/O transfer.

# 37. A memory byte location contains the pattern 00101100. What does this pattern represent when interpreted as a number? What does it represent as an ASCII Code? (Nov/Dec 2007)

Interpreted number is 44.

ASCII code is NULL/idle.

#### 38. What is Big-Endian and Little-Endian representations.(Nov/Dec-2014)

**The big-endian** is used when lower byte addresses are used for the more significant bytes(The leftmost bytes) of the word. **The little-endian** is used for the opposite ordering, where the lower byte addresses are used for the less significant bytes (the rightmost bytes) of the word.

### 39. What is the use of Instruction register?

It holds the instructions that are currently being executed.

# 40. State the basic performance equation of a computer?( Apr/May-2014)

T = (NxS)/R

Where.

N- Number of instructions

S- Average numbers of steps needed to execute one instruction.

R- Clock rate.

#### 41. How to measure the performance of the system?

Response time

Throughput.

#### 42. What is register indirect addressing mode? When is it used?(Nov/Dec-2013)

The effective address of the operand is the contents of a register or memory location whose address appears in the instruction. Ex: **Add (R2),R0**

#### 43.State Amdahl's Law.( NOV/DEC-2014)

Amdahl's Law is used to measure the performance of the multiprocessor:

Parallel- All processors fully used, which is enchanced mode. Serial- Only one

Speedup in enchanced mode is the time spent in parallel mode. Subtitute

the speedup value in equation(1)

#### 44.List the eight great ideas invented by computer architects.( NOV/DEC-2015)

Design for Moore's Law

Use abstraction to simplify design

Make the common case fast

Performance via parallelism

Performance via pipelining

Performance via prediction

Hierarchy of memories

Dependability via redundancy

#### 45. Distinguish pipelining from parallelism. (Nov/Dec-2015)

**Parallelism** means parallel computing more than one processors are running in parallel. There may be some dedicated hardware running in parallel for doing the specific task. parallelism increases the performance. **The pipelining** is an implementation technique in which multiple instructions are overlapped and also it increase the performance of the system. In pipelining there are different hazards like data hazards, control hazards etc.

#### PART-B

# 1.Explain about Eight ideas.(or) What are the great eight ideas to improve the performance of the system?

#### Eight ideas

Eight great ideas that computer architectures have been invented in the last 60 years of computer design. **Over View**

### There are eight ideas great ideas

Design for Moore's Law

Use abstraction to simplify design

Make the common case fast

Performance via parallelism

Performance via pipelining

Performance via prediction

Hierarchy of memories

Dependability via redundancy

#### **Design for Moore's Law:**

The one constant for computer designers is rapid change, which is driven largely by Moore's Law. It states that integrated circuit resources double every 18-24 months. We use an "Up and to the right " Moores Law graph to represent designing for change. Use abstraction to simplify design: It use abstractions to represent the design at different levels of representation; lower-level details are hidden to offer a simpler model at higher levels. We'll use the abstract painting icon to represent this second great idea. Make the common case fast: Making the common case fast will tend to enhance performance better than optimizing the rare case. The common case is often simpler than the rare case and hence is often easier to enhance. Ex: sports car as the icon for making the common case fast**Performance via parallelism**The instruction are executed at parallel . It increase the speed, so the performance will be improved We use multiple jet engines of a plan as our icon for parallel performance. Performance via pipelining:Instructions are overlapped during the execution of the program. It increase the speed so the performance will be improved **Performance via prediction:**The correct rediction will give accurate result, but the misprediction gives wrong result. We use the fortune - tellers crystal ball as our prediction icon Hierarchy of memories: Programmers want memory to be fast, large, and cheap , as memory speed often shapes performance , capacity limits the size of problems that can be solved , and the cost of memory today is often the majority of computer cost .We use a layered triangle icon to represent the memory hierarchy. The shape indicates speed , cost and size The closer to the top, the faster and more expensive per bit the memory The wider the base of the layer, the bigger the memory. Dependability via redundancy Computers not only need to be fast; they need to be dependable. Since any physical device can fail , we make systems dependable by including redundant components that can take over when a failure occurs and to help detect failures.

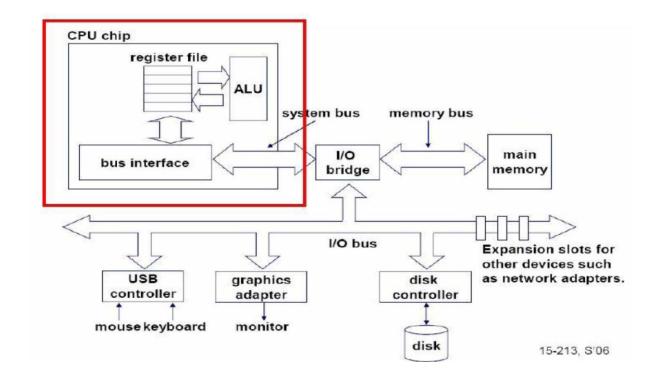

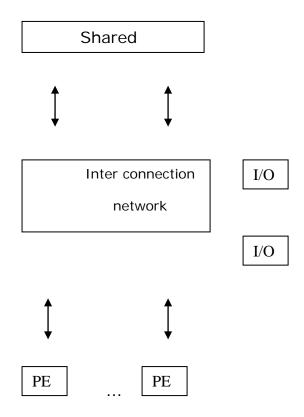

# 2.Give detail description about Components of a computer system (Nov/Dec-2014) Components of a computer system

Digital computer systems consist of three distinct units. These units are as follows:

#### **OVER VIEW:**

Input unit

Central Processing unit

Arithmetic and logic unit:

Memory unit

Output unit These units are interconnected by electrical cables to permit communication between them. This allows the computer to function as a system.

#### Input Unit (IU):

A computer must receive both data and program statements to function properly and able to solve problems. The method of feeding data and programs to a computer is accomplished by an input device.

Computer input devices read data from a source, such as magnetic disks, and translate that data into electronic impulses for transfer into the CPU. Some typical **input devices are a keyboard**, a mouse, or a scanner.

#### **Central Processing Unit (CPU):**

The brain of a computer system is the CPU.A central control section and work areas are required to perform calculations or manipulate data.

The CPU is the computing center of the system. It consists of a control section, an arithmetic-logic section, and an internal storage section (main memory). Each section within the CPU serves a specific function. The system unit also includes circuit boards, memory chips, ports and other components. A microcomputer system cabinet will also house disk drives, hard disks, etc., but these are considered separate from the CPU.

### **Control Unit (CU):**

It is the part of a CPU or other device that directs its operation. The control unit tells the rest of the computer system how to carry out a program's instructions.

It directs the movement of electronic signals between memories—which temporarily holds data, instructions and processed information—and the ALU.

It also directs these control signals between the CPU and input/output devices. The control unit is the circuitry that controls the flow of information through the processor, and coordinates the activities of the other units within it.

In a way, it is the "brain", as it controls what happens inside the processor, which in turn controls the rest of the PC.

#### **Arithmetic And Logic Unit(ALU):**

Unit usually called the ALU is a digital circuit that performs two types of operations— arithmetic and logical.  Arithmetic operations are the fundamental mathematical operations consisting of addition, subtraction, multiplication and division. Logical operations consist of comparisons. That is, two pieces of data are compared to see whether one is equal to, less than, or greater than the other.

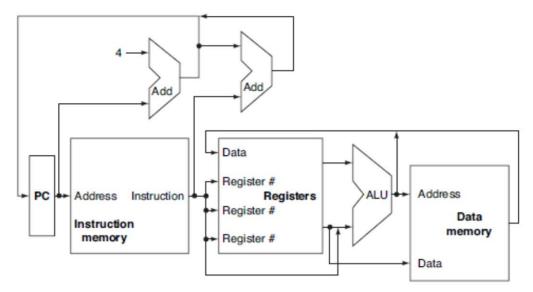

Figure 1.1. Functional Unit

#### **Memory Unit**

The function of the memory unit is to store programs and data. There are two classes of storage, called primary and secondary. Primary storage is a fast memory that operates at electronic speeds. Programs must be stored in the memory while they are being executed. The memory contains a large number of semiconductor storage cells, each capable of storing one bit of information. These cells are rarely read or written as individual cells but instead are processed in groups of fixed size called words. The number of bits in each word is often referred to as the word length of the computer. Typical word lengths range from 16 to 64 bits. The capacity of the memory is one factor that characterizes the size of a computer. Programs must reside in the memory during execution. Instructions and data can be written into the memory or read out under the controller of the processor. It is essential to be able to access any word location in the memory as quickly as possible. Memory in which any location can be reached in a short and fixed amount of time after specifying its address is called random-access Memory (RAM). The time required to access one word is called the Memory access time. This time is fixed, independent of the location of the word being accessed. It typically ranges from a few nanoseconds (ns) to about 100 ns for modem RAM units. Thus additional, cheaper, secondary storage is used when large amounts of data and many programs have to be stored, particularly for information that is access infrequently. A wide selection of secondary storage devices is available, including magnetic disks and tapes and optical disks

#### **Output Unit:**

Its function is to send processed results to the outside world.

The most familiar example of such a device is a printer. Printers employ mechanical impact heads, inkjet streams, or photocopying techniques, as in laser printers, to perform the printing. It produces printers capable of printing as **many as 10,000** lines per minute. Some units, such as graphic displays, provide both an output function and an input function. The dual role of input and output of such units are referred with single name as I/O unit in many cases. **Speakers, Headphones and projectors are some of the output devices.**

Storage devices such as hard disk, floppy disk, flash drives are also used for input as well as output.

### 3. Briefly explain about Technology of computer generations.

#### **Technology**

The Computer generations means step by step growth in the technology. There are five generations of computer. They are given below.

#### **Five types of Generation:**

#### **Over View**

First Generation Second Generation Third Generation Fourth Generation

Fifth Generation

#### **First Generation Computers:**

**Year**: 1942 – 1955

Component used: Vacuum Tube

Language used : Machine Level Language

The first generation computers used vacuum tube circuitry as such these were quite large. It was one of the high speed electronic switching devices available at that time. The generation computers used machine language (0, 1). It is difficult language and it required lot of time to write programs. No operating system is required. The first generation computers used the method of "Stored Program" concept.

#### **Advantages**

These computers were the fastest calculating device of their time.

These computers could perform computations in milli seconds.

#### **Disadvantages**

It occupies large space. High heat production High power consumption

Eg: EDSAC, EDVAC

#### **Second Generation Computers:**

**Year:** 1955 – 1964

Component Used : Transistors

Language used : Assembly Level Language

The Second generation computers used Transistors.

The storage capacity is higher than the first generation computers. Batch operating system rules the second generation computers.

#### **Advantages**

Small in size

Better speed

• Less hardware failure

#### **Disadvantages**

High cost, Frequent maintenance is required. Eg: UNIVAC-1180, IBM-1620

**Third Generation Computers:**

**Year**: 1964 – 1975

Component Used : Integrated Circuits (IC)

Language used : High Level Language

The third generation computers used Integrated Circuits(IC). The ICs were made of Silicon. The ICs provided vast internal storage and increased the operational efficiency. during the period, the mini computers were developed. Time sharing concept also introduced in this generation.

#### Advantages:

Easily portable

Less H/W failure

General purpose computer

Less heat generated.

### Disadvantages:

Highly sophisticated Technology required for the manufacture of IC chips. Need Air

conditioning.**Eg: IBM-360 series Fourth Generation Computers:**

**Year**: 1975 – 1989

**Component used**: Microprocessor (MP)

Language used: 4GL

A micro processor produces a Micro computer.

Microcomputer is a stand alone and easy to use device.

Microcomputers are relatively inexpensive.

The fourth generation language is introduced which were easy to learn and understand.

### **Advantages**

These computers had large and faster primary and secondary storage.

Object oriented languages are supported & these are general purpose computers.

#### **Disadvantages**

Highly sophisticated technology required for the manufacture of LSI chips.

Eg: Intel-400L

## Fifth Generation Computers

Year: 1989 – at present

**Concept used**: Artificial Intelligent (AI)• Computers are machines that perform only when instructed. But they are unable to act or think on their own.• Recent researches are aimed at designing the logic for the thinking computer (AI) for building expert systems and knowledge based systems.• This computer is using magnetic bubble memories and other recent developments are on the way. These computers will be based on advances in silicon technology.

#### Advantages:

The super computers fall under this generation. Supports Parallel programming

#### **Three Concepts**

Mega Chips.

Parallel Processing.

Artificial Intelligence (AI).

# 4.Explain about Performance of a computer system. Or State the CPU performance equation and discuss the factors that affect performance. (Nov/Dec-2014) Performance

For best performance, it is necessary to design the compiler, machine instruction set and hardware in a co-ordinate way. Over viewPerformance CPU Performance and Its FactorsInstruction PerformanceSPEC CPU benchmark: Implication of Amdahl's Law Performance EvalutionResponse time Also called execution time. The total time required for the computer to complete a task, including disk accesses, memory accesses, I/O activities, operating system overhead, CPU execution time, and so on.

**Throughput** Also called **bandwidth**. Another measure of performance, it is the number of tasks completed per unit time. **Elapsed Time** The total time required to execute the program is called the elapsed time. It Depends on all the units in computer system.

#### **Processor Time**

The period in which the processor is active is called the processor time. It Depends on hardware involved in the execution of the instruction. To maximize performance, we want to minimize response time or execution time for some task. Thus, we can relate performance and execution time for a computer X:This means that for two computers X and Y, if the performance of X is greater than the performance of Y, we have

$$\frac{1}{\text{Execution time}_{x}} > \frac{1}{\text{Execution time}_{y}}$$

$$\frac{1}{\text{Execution time}_{y}} > \frac{1}{\text{Execution time}_{y}}$$

Execution time<sub>y</sub>

That is, the execution time on Y is longer than that on X, if X is faster than Y.To relate the performance of two different computers quantitatively. We will use the phrase "X is n times faster than Y"—or equivalently "X is n times as fast as Y"—to mean

$$\frac{\text{Performance}_{X}}{\text{Performance}_{v}} = n$$

If X is *n* times faster than Y, then the execution time on Y is *n* times longer than it is on X:

$$\frac{\text{Performance}_{\mathbf{x}}}{\text{Performance}_{\mathbf{y}}} = \frac{\text{Execution time}_{\mathbf{y}}}{\text{Execution time}_{\mathbf{x}}} = n$$

#### **Measuring Performance:**

**Time is the** measure of computer performance:

i.e) if the computer that performs the same amount of work in the least time is the fastest. Program execution time is measured in seconds per program. However, time can be defined in different ways, depending on what we count. The most straightforward definition of time is called wall clock time, response time, or elapsed time. These terms mean the total time to complete a task, including disk accesses, memory accesses, input/output (I/O) activities, operating system overhead etc., Wall -clock time - how long it takes (typically, time in seconds) for our program to execute, from the time its is invoked to the time it completes.CPU Time- CPU execution time Also called CPU time. The actual time the CPU spends computing for a specific task. System CPU time - The CPU time spent in the operating system performing tasks on behalf of the program. I/O Time – time spend reading and writing data from/ to memory. User CPU time - The CPU time spent in a program itself.clock cycle Also called tick, clock tick, clock time for one clock period, usually of the processor clock, which runs at a constant rate. **clock period** The length of each clock cycle. CPU Performance and Its Factors: Users and designers often examine performance using different metrics. A simple formula relates the most basic metrics (clock cycles and clock cycle time) to CPU time:

Alternatively, because clock rate and clock cycle time are inverses,

$$\frac{\text{CPU execution time}}{\text{for a program}} = \frac{\text{CPU clock cycles for a program}}{\text{Clock rate}}$$

This formula makes it clear that the hardware designer can improve performance by reducing the number of clock cycles required for a program or the length of the clock cycle. **Instruction Performance:**\_The performance equations above did not include any reference to the number of instructions needed for the program. One way to think about execution time is that it equals the number of instructions executed multiplied by the average time per instruction. Therefore, the number of clock cycles required for a program can be written as

The term **clock cycles per instruction**, which is the average number of clock cycles each instruction takes to execute, is often abbreviated as **CPI**.

#### The Classic CPU Performance Equation

The basic performance equation in terms of **instruction count** (the number of instructions executed by the program), CPI, and clock cycle time:

or, since the clock rate is the inverse of clock cycle time:

$$CPU \ time = \frac{Instruction \ count \times CPI}{Clock \ rate}$$

$$CPU \ clock \ cycles = \sum_{i=1}^{n} \ (CPI_i \times C_i)$$

The CPI values can be computed by

$$CPI = \frac{CPU \text{ clock cycles}}{Instruction count}$$

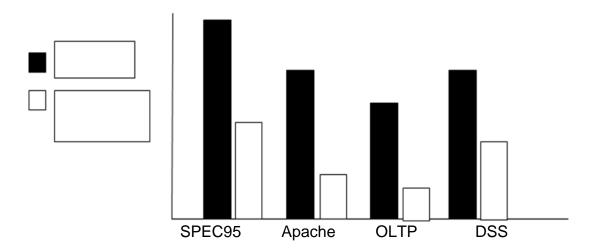

#### **SPEC CPU benchmark:**

The Performance Measure is the time it takes a computer to execute a given benchmark. A non-profit organization called SPEC(System Performance Evaluation Corporation) selects and publishes representative application program.

**Implication of Amdahl's Law** Amdahl's Law is used to measure the performance of the multiprocessor:

Assume that the program operates in two modes: Parallel- All processors fully used, which is enchanced mode. Serial- Only one processor in use. Speedup in enchanced mode is the time spent in parallel mode.

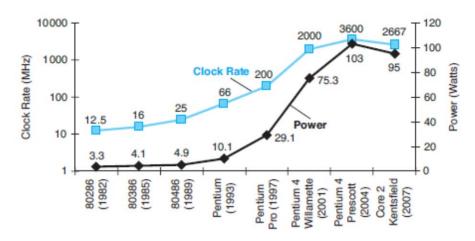

### 5. Explain about Power Wall.

#### **The Power Wall**

Figure 1.3 shows the increase in clock rate and power of eight generations of Intel microprocessors over 25 years. Both clock rate and power increased rapidly for decades, and then flattened off recently. The reason they grew together is that they are correlated, and the reason for their recent slowing is that we have run into the practical power limit for cooling commodity microprocessors.

FIGURE 1.3 .Clock rate and Power for Intel x86 microprocessors over eight generations and 25 years.

The Pentium 4 made a dramatic jump in clock rate and power but less so in performance. The Prescott thermal problems led to the abandonment of the Pentium 4 line. The Core 2 line reverts to a simpler pipeline with lower clock rates and multiple processors per chip. The dominant technology for integrated circuits is called CMOS (complementary metal oxide semiconductor). For CMOS, the primary source of power dissipation is so-called dynamic power—that is, power that is consumed during switching. The dynamic power dissipation depends on the capacitive loading of each transistor, the voltage applied, and the frequency that the transistor is switched: Power = Capacitive load × Voltage2 × Frequency switchedFrequency switched is a function of the clock rate. The capacitive load per Transistor is a function of both the number of transistors connected to an output (called the fanout) and the technology, which determines the capacitance of both wires and transistors.

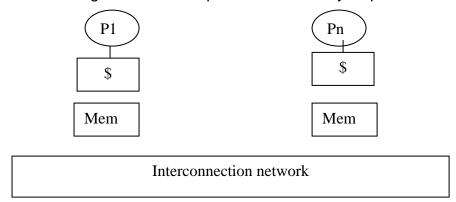

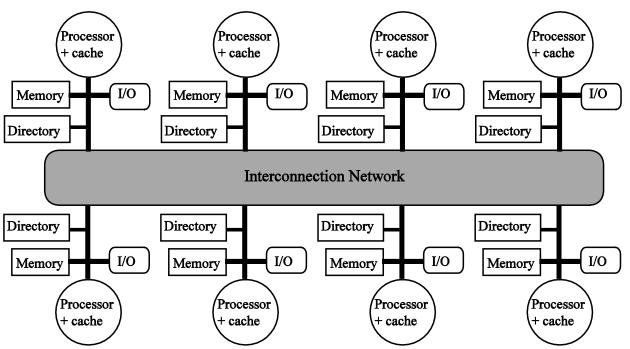

# 6. Explain about Uniprocessors to Multiprocessors Uniprocessors to Multiprocessors:

This chart plots performance relative to the VAX 11/780 as measured by the SPECint benchmarks (see Prior to the mid-1980s, processor performance growth was largely technology driven and averaged about 25% per year. The increase in growth to about

AX-11/780, 5 MHz

25%/year 1.5, VAX-11/785

Intel Xeon 4 cores 3.6 GHz (Boost to 4.0)

Intel Xeon 6 cores 3.3 GHz (Boost to 4.0)

Intel Xeon 6 cores 3.3 GHz (boost to 3.8 GHz)

Intel Xeon 6 cores 3.3 GHz (boost to 3.6 GHz)

Intel Core i7 Extreme 4 cores, 3.3 GHz (boost to 3.6 GHz)

Intel Core Duc Extreme 2 cores, 2.0 GHz

Intel Core I7 4 cores 3.4 GHz

Intel Core I7 4 co Performance (vs. VAX-11/780) IBM POWERstation 100, 150 MHz 117.

Digital 3000 AXP/500, 150 MHz HP 9000/750, 66 MHz IBM RS6000/540, 30 MHz 24 MIPS M2000, 25 MHz 18 MIPS M/120, 16.7 MHz 18 Sun-4/260, 16.7 MHz 13 52%/year VAX 8700, 22 MHz

52% since then is attributable to more advanced architectural and organizational ideas. By 2002, this growth led to a difference in performance of about a factor of seven.

FIGURE 1.4 Growth in processor performance since the mid-1980s.

Performance for floating-pointoriented calculations has increased even faster. Since 2002. the limits of power, available instruction-level parallelism, and long memory latency have slowed uniprocessor performance recently, to about 20% per year.

| Product              | AMD<br>Opteron X4<br>(Barcelona) | Intel Nehalem | IBM Power 6 | Sun<br>Ultra SPARC T2<br>(Nlagara 2) |

|----------------------|----------------------------------|---------------|-------------|--------------------------------------|

| Cores per chip       | 4                                | 4             | 2           | 8                                    |

| Clock rate           | 2.5 GHz                          | ~ 2.5 GHz ?   | 4.7 GHz     | 1.4 GHz                              |

| Microprocessor power | 120 W                            | ~ 100 W ?     | ~ 100 W ?   | 94 W                                 |

FIGURE 1.5. Number of cores per chip, clock rate, and power for 2008 multicore microprocessors

#### Why has it been so hard for programmers to write explicitly parallel programs?

The first reason is that parallel programming is by definition performance programming. which increases the difficulty of programming. Not only does the program need to be correct, solve an important problem, and provide a useful interface to the people or other programs that invoke it, the program must also be fast. Otherwise, if you don't need performance, just write a sequential program. The **second reason** is that fast for parallel hardware means that the programmer must divide an application so that each processor has roughly the same amount to do at the same time, and that the overhead of scheduling and coordination doesn't fritter away the potential performance benefits of parallelism. As an analogy, suppose the task was to write a newspaper story. Eight reporters working on the same story could potentially write a story eight times faster. To achieve this increased speed, one would need to break up the task so that each reporter had something to do at the same time. Thus, we must **schedule** the **subtasks**. If anything went wrong and just one reporter took longer than the seven others did, then the benefits of having eight writers would be diminished. Thus, we must balance the load evenly to get the desired speedup

Thus, care must be taken to *reduce communication and synchronization overhead*. For both this analogy and parallel programming, the challenges include scheduling, load balancing, time for synchronization, and overhead for communication between the parties.

#### 7. Explain about Instructions & Operation of the computer hardware.

#### **Operation of the computer hardware:**

Every computer must be able to perform arithmeticThe MIPS assembly language notation add a, b, cInstructs a computer to add the two variables b and c and to put their sum in a This notation is rigid in that each MIPS arithmetic instruction performs only one operation and must always have exactly three variables. The following code shows an equivalent MIPS code:

#### ADD \$s1,\$s2, \$s3

The sum of b and c is placed in a . here , the variables a,b and c are assumed to be stored in the register \$\$1,\$\$2 and \$\$3 all arithmetic immediate value are signed extended

# MIPS operands

| Name                            | Example                                                                                | Comments                                                                                                                                                                                      |

|---------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32 registers                    | \$s0-\$s7, \$t0-\$t9, \$zero,<br>\$a0-\$a3, \$v0-\$v1, \$gp, \$fp,<br>\$sp, \$ra, \$at | Past locations for data. In MIPS, data must be in registers to perform arithmetic, register \$zero always equals 0, and register \$at is reserved by the assembler to handle large constants. |

| 2 <sup>30</sup> memory<br>words | Memory[0], Memory[4], ,<br>Memory[4294967292]                                          | Accessed only by data transfer instructions. MIPS uses byte addresses, so sequential word addresses differ by 4. Memory holds data structures, arrays, and spilled registers.                 |

# MIPS assembly language

| Category         | Instruction                         | Example             | Meaning                                     | Comments                               |

|------------------|-------------------------------------|---------------------|---------------------------------------------|----------------------------------------|

|                  | add                                 | add \$s1,\$s2,\$s3  | \$S1 = \$S2 + \$S3                          | Three register operands                |

| Arithmetic       | subtract                            | sub \$s1,\$s2,\$s3  | \$s1 = \$s2 - \$s3                          | Three register operands                |

|                  | add Immediate                       | addi \$s1,\$s2,20   | \$s1 = \$s2 + 20                            | Used to add constants                  |

|                  | load word                           | 1w \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Word from memory to register           |

|                  | store word                          | sw \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Word from register to memory           |

|                  | load half                           | 1h \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Halfword memory to register            |

|                  | load half unsigned                  | 1hu \$s1,20(\$s2)   | \$s1 = Memory[\$s2 + 20]                    | Halfword memory to register            |

|                  | store half                          | sh \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Halfword register to memory            |

| Data<br>transfer | load byte                           | 1b \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Byte from memory to register           |

| uansiei          | load byte unsigned                  | 1bu \$s1,20(\$s2)   | \$s1 = Memory[\$s2 + 20]                    | Byte from memory to register           |

|                  | store byte                          | sb \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Byte from register to memory           |

|                  | load linked word                    | 11 \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Load word as 1st half of atomic swap   |

|                  | store condition, word               | sc \$s1,20(\$s2)    | Memory(\$s2+20]=\$s1;\$s1=0 or 1            | Store word as 2nd half of atomic swap  |

|                  | load upper Immed.                   | lui \$s1,20         | \$s1 = 20 * 2 <sup>16</sup>                 | Loads constant in upper 16 bits        |

|                  | and                                 | and \$s1,\$s2,\$s3  | \$s1 = \$s2 & \$s3                          | Three reg. operands; bit-by-bit AND    |

|                  | or                                  | or \$s1,\$s2,\$s3   | \$s1 = \$s2   \$s3                          | Three reg. operands; bit-by-bit OR     |

|                  | nor                                 | nor \$s1,\$s2,\$s3  | \$s1 = ~ (\$s2   \$s3)                      | Three reg. operands; bit-by-bit NOR    |

| Logical          | and immediate                       | andi \$s1,\$s2,20   | \$s1 = \$s2 & 20                            | Bit-by-bit AND reg with constant       |

|                  | or immediate                        | ori \$s1,\$s2,20    | \$s1 = \$s2   20                            | Bit-by-bit OR reg with constant        |

|                  | shift left logical                  | s11 \$s1,\$s2,10    | \$s1 = \$s2 << 10                           | Shift left by constant                 |

|                  | shift right logical                 | srl \$sl,\$s2,10    | \$s1 = \$s2 >> 10                           | Shift right by constant                |

|                  | branch on equal                     | beq \$s1,\$s2,25    | If (\$s1 == \$s2) go to<br>PC + 4 + 100     | Equal test; PC-relative branch         |

|                  | branch on not equal                 | bne \$s1,\$s2,25    | If (\$s1!= \$s2) go to<br>PC + 4 + 100      | Not equal test; PC-relative            |

| Conditional      | set on less than                    | s1t \$s1,\$s2,\$s3  | If (\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0 | Compare less than; for beg, bne        |

| branch           | set on less than<br>unsigned        | sltu \$s1,\$s2,\$s3 | If (\$52 < \$53) \$51 = 1;<br>else \$51 = 0 | Compare less than unsigned             |

|                  | set less than<br>Immediate          | s1ti \$s1,\$s2,20   | If (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0   | Compare less than constant             |

|                  | set less than<br>Immediate unsigned | sltiu \$sl,\$s2,20  | If (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0   | Compare less than constant<br>unsigned |

| 1                | Jump                                | j 2500              | go to 10000                                 | Jump to target address                 |

| Unconditional    | Jump register                       | jr \$ra             | go to \$ra                                  | For switch, procedure return           |

| Jump             | Jump and link                       | jal 2500            | \$ra = PC + 4; go to 10000                  | For procedure call                     |

#### Fig .1.6 : MIPS Assembly language

All arithmetic operations have exactly three operands, no more and no less, conforms have this conforms to the philosophy of keeping the hardware simple. This situation illustrates the first of four underlying principles of hardware design. **Design Principle 1:** Simplicity favors regularity. Compiling Two C Assignment Statements into MIPS Example 1: This egment of a C program contains the five variables a, b, c, d, and e. Since Java volved from C, this example and the next few work for either high-level programming language:

```

a = b + c;

d = a - e;

```

#### **Answer**

The translation from C to MIPS assembly language instructions is performed by the *compiler*. Show the MIPS code produced by a compiler. A MIPS instruction operates on two source operands and places the result in one destination operand. Hence, the two simple statements above compile directly into these two MIPS assembly language instructions:

```

add a, b, c sub d, a, e

```

#### Example 2:

A somewhat complex statement contains the five variables f, g, h, i, and j:

```

f = (g + h) - (i + j);

```

What might a C compiler produce?

#### **Answer**

The compiler must break this statement into several assembly instructions, since only one operation is performed per MIPS instruction. The first MIPS instruction calculates the sum of g and h. We must place the result somewhere, so the compiler creates a temporary variable, called t0:

```

add t0,g,h # temporary variable t0 contains g + h

```

Although the next operation is subtract, we need to calculate the sum of i and j before we can subtract. Thus, the second instruction places the sum of i and j in another temporary variable created by the compiler, called t1:

```

add tl.i.j # temporary variable tl contains i + j

```

Finally, the subtract instruction subtracts the second sum from the first and places the difference in the variable f, completing the compiled code:

```

sub f.t0.t1 \# f gets t0 - t1, which is (g + h) - (i + j)

```

#### 8. Expalin about Operands of the Computer Hardware:

Operands of the Computer Hardware Over View memory operand constant or immediate operands Index register The operands of the computer hardware using Design principal two:Design Principle 2: Smaller is faster. A very large number of registers may increase the clock cycle time simply because it takes electronic signals longer when they must travel farther. Use fewer register to conserve energy Example: Compiling a C Assignment Using Registers: It is the compiler's job to associate program variables with registers. Take, for instance, the assignment statement from our earlier example:

```

f = (q + h) - (i + j):

```

The variables f, g, h, i, and j are assigned to the registers \$s0, \$s1, \$s2, \$s3, and \$s4, respectively. What is the compiled MIPS code? **Answer**The compiled program is very similar to the prior example, except we replace the variables with the register names mentioned above plus two temporary registers, \$t0 and \$t1, which correspond to the temporary variables above:

```

add $t0,$s1,$s2 # register $t0 contains g + h

add $t1,$s3,$s4 # register $t1 contains i + j

sub $s0,$t0,$t1 # f gets $t0 - $t1, which is <math>(g + h)-(i + j)

```

### **Memory Operands**

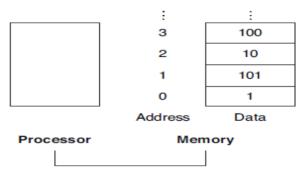

Programming languages have simple variables that contain single data elements. But they also have more complex data structures(many more data elements )—arrays and structures. Thus, MIPS must include instructions that transfer data between memory and registers. Such instructions are called **data transfer instructions**. To access a word in memory, the instruction must supply the memory **address**. Memory is just a large, **single-dimensional array**, with the address acting as the index to that array, starting at 0. For example, in Figure 1.7, the address of the third data element is 2, and the value of Memory[2] is 10

FIGURE 1.6 Memory addresses and contents of memory at those locations

The data transfer instruction that copies data from memory to a register is traditionally called *load*. The format of the load instruction is the name of the operation followed by the register to be loaded, then a constant and register used to access memory. The sum of the constant portion of the instruction and the contents of the second register forms the memory address. The actual MIPS name for this instruction is lw, standing for *load word*.

FIGURE 1.7 Actual MIPS memory addresses and contents of memory for those words.

Alignment restriction:

In MIPS, words must start at addresses that are multiples of 4. This requirement is called an **alignment restriction.** Alignment restriction A requirement that data be aligned in memory on natural boundaries .many architecture have alignment restriction **Big endian** and little Endian:8 bit bytes are divided into two parts:Address of the left most byte is called "big endian" and right most byte is called "little endian "Compiling an Assignment When an Operand Is in Memory:Example 1:Let's assume that A is an array of 100 words and that the compiler has associated the variables g and h with the registers \$\$1 and \$\$2 as before. Let's also assume that the starting address, or base address, of the array is in \$\$3. Compile this C assignment statement:MIPS CodeIn the given statement, there is a single operation. Whereas, one of the operands is in memory, so we must carry this operation in two steps:Step 1: load the temporary register(\$\$\$3\$) + 8Step 2: perform addition with h((\$\$\$2\$)), and store result in g(\$\$\$\$\$\$\$\$1\$)

```

lw $t0,8($s3) \# Temporary reg $t0 gets A[8]

add $s1,$s2,$t0 \# g = h + A[8]

```

The constant in a data transfer instruction (8) is called the *offset*, and the register added to form the address (\$s3) is called the *base register*. Example 2:Compiling Using Load and Store What is the MIPS assembly code for the C assignment statement

$$A[12] = h + A[8];$$

below?

Assume variable h is associated with register \$s2 and the base address of the array A is in \$s3.

#### MIPS code

```

lw $t0,32($s3) # Temporary reg $t0 gets A[8]

add $t0,$s2,$t0 # Temporary reg $t0 gets h + A[8]

```

The final instruction stores the sum into A[12], using 48 (4  $\times$  12) as the offset and register \$s3 as the base register

```

sw $t0,48($s3) # Stores h + A[8] back into A[12]

```

Load word and store word are the instructions that copy words between memory and registers in the MIPS architecture. Other brands of computers use other instructions along with load and store to transfer data. Constant or Immediate Operands Constant variables are used as one of the operand for many arithmetic operation in MIPS architecture. The constants would have been placed in memory when the program was loaded. To avoid load instruction used in arithmetic instruction we can use one operand is a constant This quick add instruction with one constant operand is called add immediate or addi. To add 4 to register \$\$3, we just write

Design Principle 3: Make the common case fast.

```

lw $t0, AddrConstant4($s1) # $t0 = constant 4

add $s3,$s3,$t0 # $s3 = $s3 + $t0 ($t0 == 4)

```

assuming that \$s1 + AddrConstant4 is the memory address of the constant 4.

addi

$$$s3.$s3.4$$

$# $s3 = $s3 + 4$

#### Advantage of constant operands

It uses less energy

It performs operation in more fast

#### **Index register**

The register in the data transfer instructions was originally invented to hold an index of an array with the offset used for the starting address of an array. Thus, the base register is also called the *index register*.

# 9. Discuss about the various techniques to represent instruction in computer system. ( Apr/May-2015)

### representing Instructions in the Computer

Instructions are kept in the computer as a series of high and low electronic signals and may be represented as numbers. Each instruction is used to perform some task and representing those instructions will be varied from one language to another language. To represent the instruction format need to use the specified language. Instruction format is a form of representation of an instruction composed of fields of binary numbers. Registers In computer hardware registers are referred to by almost all instructions, there must be a convention to map register names into numbers. In MIPS assembly language, registers \$s0 to \$s7 map onto registers 16 to 23, and registers \$t0 to \$t7 map onto registers 8 to 15. Hence, \$s0 means register 16, \$s1 means register 17, \$s2 means register 18, . . . , \$t0 means register 8, \$t1 means register 9, and so on. Machine language Binary representation used for communication within a computer ystem.MIPS instruction takes exactly 32 bits—the same size as a data wordInstructions used in machine language and a sequence of such instructions machine code(0,1). Example 1. Translating a MIPS Assembly Instruction into a Machine **Instruction**Let's do the next step in the refinement of the MIPS language as an example. We'll show the real MIPS language version of the instruction represented symbolically as

add \$t0,\$s1,\$s2

first as a combination of decimal numbers and then of binary numbers.

#### Answer:

The decimal representation is

| 0 | 17 | 18 | 8 | 0 | 32 |

|---|----|----|---|---|----|

Each of these segments of an instruction is called a *field*. The first and last fields containing 0 and 32 in this case) in combination tell the MIPS computer that This instruction performs addition. The second field gives the number of the register that is the first source operand of the addition operation (17 = \$s1), Third field gives the other source operand for the addition (18 = \$s2). The fourth field contains the number of the register that is to receive the sum (8 = \$t0). The fifth field is unused in this instruction, so it is set to 0. This instruction adds register \$s1 to register \$s2 and places the sum in register \$t0. This instruction can also be represented as fields of binary numbers as opposed to decimal:

| 000000 | 10001  | 10010  | 01000  | 00000  | 100000 |

|--------|--------|--------|--------|--------|--------|

| 6 hits | 5 hits | 5 hits | 5 hits | 5 hits | 6 hits |

Here 10001 is the binary value for 17 as like this remaining field value will be represented in binary

#### Hexadecimal number

Computer can use binary numbers to reading and writing data in binary numbers. We avoid that by using a higher base than binary that converts easily into binary. Since almost all computer data sizes are multiples of 4, **hexadecimal** (base 16) numbers are popular.ince base 16 is a power of 2, we can trivially convert by replacing each group of four binary digits by a single hexadecimal digit, and vice versa

| Hexadecimal      | Binary              | Hexadecimal      | Binary              | Hexadecimal      | Binary              | Hexadecimal      | Binary              |

|------------------|---------------------|------------------|---------------------|------------------|---------------------|------------------|---------------------|

| O <sub>hex</sub> | 0000 <sub>two</sub> | 4 <sub>hex</sub> | 0100 <sub>two</sub> | 8 <sub>hex</sub> | 1000 <sub>two</sub> | c <sub>hex</sub> | 1100 <sub>two</sub> |

| 1 <sub>hex</sub> | 0001 <sub>two</sub> | 5 <sub>hex</sub> | 0101 <sub>two</sub> | 9 <sub>hex</sub> | 1001 <sub>two</sub> | d <sub>hex</sub> | 1101 <sub>two</sub> |

| 2 <sub>hex</sub> | 0010 <sub>two</sub> | 6 <sub>hex</sub> | 0110 <sub>two</sub> | a <sub>hex</sub> | 1010 <sub>two</sub> | e <sub>hex</sub> | 1110 <sub>two</sub> |

| 3 <sub>hex</sub> | 0011 <sub>two</sub> | 7 <sub>hex</sub> | 0111 <sub>two</sub> | b <sub>hex</sub> | 1011 <sub>two</sub> | f <sub>hex</sub> | 1111 <sub>two</sub> |

Fig 1.8.Hexadecimal to binary conversion Example

decimal numbers with *ten*, binary numbers with *two*, and Hexadecimal numbers with *hex*. (If there is no subscript, the default is base 10.) **MIPS Fields:** Hence, we have a conflict between the desire to keep all instructions the same length and the desire to have a single instruction format. This leads us to the final hardware design principle:

#### Design Principle 4: Good design demands good compromises.

The compromise chosen by the MIPS designers is to keep all instructions the same length, thereby requiring different kinds of instruction formats for different kinds of instructions.

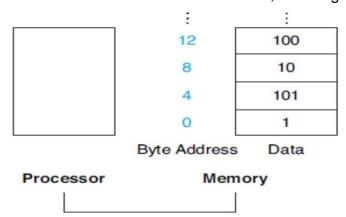

MIPS Fields has two kinds of format such asR-type or R- format( for register)I-type or I-format( for immediate)

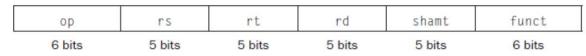

#### R-type or R- format:

MIPS fields are given names to make them easier to discuss:

Here is the meaning of each name of the fields in MIPS instructions:

- op: Basic operation of the instruction, traditionally called the **opcode**.

- *rs:* The first register source operand.

- rt: The second register source operand.

- *rd*: The register destination operand. It gets the result of the operation.

- *shamt:* Shift amount. *funct:* Function. This field, often called the *function code*, selects the specific variant of the operation in the op field.

#### I-format:

A second type of instruction format is called *I-type* (for immediate) or *I-format* and is used by the immediate and data transfer instructions.

The fields of I-format are

| ор     | rs                   | rs rt constant or a |         |

|--------|----------------------|---------------------|---------|

| 6 bits | 6 bits 5 bits 5 bits |                     | 16 bits |

#### Drawback of different format

Multiple formats complicate the hardware.

It increase the complexity.

Solution for above problem is we have to use similar format for that designers must keep all instruction in the same length.

#### **10.Explain about Logical Operations:**

**Logical Operations:Over view:**

Logical shift operation

Shift left logical (sll)

Shift right logical (srl).

**Logical AND operation**

Logical OR operation

**Logical NOT operation**

**Logical NOR operation**

–Useful to operate on fields of bit or individual bits**AND** A logical bit-by bit operation with two operands that calculates a 1 only if there is a 1 in *both* operands.**OR** A logical bit-by bit operation with two operands that calculates a 1 if there is a 1 in *either* operand.**NOT** A logical bit-by bit operation with one operand that inverts the bits; that is, it replaces every 1 with a 0, and every 0 with a 1.**NOR** A logical bit-by bit operation with two operands that calculates the NOT of the OR of the two operands. That is, it calculates a 1 only if there is a

| Logical operations | C operators | Java operators | MIPS Instructions |

|--------------------|-------------|----------------|-------------------|

| Shift left         | <<          | <<             | s11               |

| Shift right        | >>          | >>>            | srl               |

| Bit-by-bit AND     | &           | &              | and, andi         |

| Bit-by-bit OR      | 1           |                | or, ori           |

| Bit-by-bit NOT     | ~           | ~              | nor               |

Fig .1.9. .C and Java logical operators and their corresponding MIPS instructions

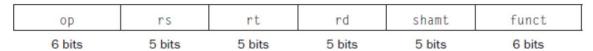

#### Logical shift operation:

Shift operation moves all the bits in a word to the left or right side and filling the emptied bits with 0 Based on the direction of shifting it can be classified in two types

Shift left, Shift right The actual name of the two MIPS shift instructions are called **shift left logical** (sll) and **shift right logical** (srl).

0 LSB

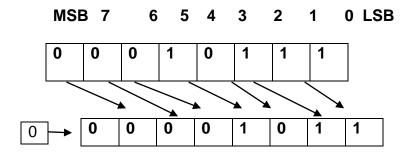

#### Shift left logical (sll):

It moves all the bits in a word to the left side and empty position is filled with 0 **Example**

MSB 7 6 5 4 3 2 1

| 0 | Λ | n | 1 | n | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|

| U | U | U | • | U | • | • | • |

|   |   |   |   |   |   |   |   |

Fig.1.10. shift left logical of a binary number by 1

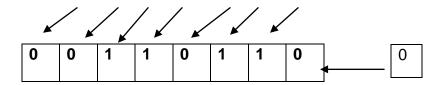

It moves all the bits in a word to the right side and empty position is filled with 0

#### **Example**

Fig.1.11. shift right logical of a binary number by 1

if register \$t2 contains

$0000\ 0000\ 0000\ 0000\ 0000\ 1101\ 1100\ 0000_{two}$

and register \$t1 contains

$0000\ 0000\ 0000\ 0000\ 0011\ 1100\ 0000\ 0000_{two}$

then, after executing the MIPS instruction

and

$$$t0.$t1.$t2$$

# reg  $$t0 = reg $t1 & reg $t2$

the value of register \$t0 would be

$0000\ 0000\ 0000\ 0000\ 0000\ 1100\ 0000\ 0000_{two}$

**Logical OR operation:** A logical bit-by bit operation with two operands that calculates a 1 if there is a 1 in *either* operand. **Example** if register \$t2 contains

$0000\ 0000\ 0000\ 0000\ 0000\ 1101\ 1100\ 0000_{two}$

and register \$t1 contains

$0000\ 0000\ 0000\ 0000\ 0011\ 1100\ 0000\ 0000_{two}$

then, after executing the MIPS

instruction

is this value in register \$t0:

$0000\ 0000\ 0000\ 0000\ 0011\ 1101\ 1100\ 0000_{two}$

#### **Logical NOT operation**

A logical bit-bybit operation with one operand that inverts the bits; that is, it replaces every 1 with a 0, and every 0 with a 1.

Example

\$t1 = 0010 1010 1100 1000 NOT \$t1 = 1101 0101 0011 0111

#### **Logical NOR operation**

A logical bit-bybit operation with two operands that calculates the NOT of the OR of the two operands. it calculates a 1 only if there is a 0 in *both* operands.

Exampleif register \$t2 contains

```

0000\ 0000\ 0000\ 0000\ 0000\ 1101\ 1100\ 0000_{two}

```

and register \$t1 contains

```

0000\ 0000\ 0000\ 0000\ 0011\ 1100\ 0000\ 0000_{two}

```

then, after executing the MIPS instruction

nor

$$$t0,$t1,$t3 # reg $t0 = ~ (reg $t1 | reg $t3)$$

is this value in register \$t0:

#### 11. Explain about Control operation with examples.

#### **Control operation**

Decision making is commonly represented in programming languages using the *if* statement, sometimes combined with *go to* statements and labels.MIPS assembly language includes two decision- making instructions, similar to an *if* statement with a *go*

to. The first instruction is

This instruction means go to the statement labeled L1 if the value in register1 equals the value in register2. The mnemonic beq stands for *branch if equal*. The second instruction bne register1. register2. L1

It means go to the statement labeled L1 if the value in register1 does *not* equal the value in register2. The mnemonic bne stands for *branch if not equal*. These two instructions are traditionally called **conditional branches**.

**conditional branches**:In MIPS language beq and bne stands for conditional branches.An instruction that requires the comparison of two values and that allows for a subsequent

transfer of control to a new address in the program based on the outcome of the comparison.

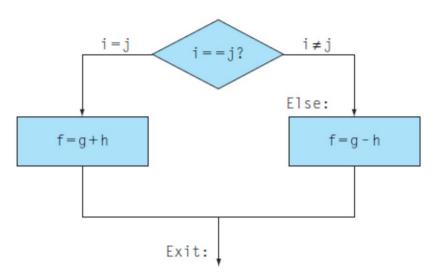

#### **Example: Compiling** *if-then-else* **into Conditional Branches:**

In the following code segment, f, g, h, i, and j are variables. If the five variables f through j correspond to the five registers \$s0 through \$s4, what is the compiled MIPS code for this C *if* statement?

if

$$(i == j)$$

$f = g + h$ ; else  $f = g - h$ ;

#### Answer

The flow chart shows what the MIPS code should do. For first instructions we have to use beq because it expresses the comparison between i and j. Second instruction we have to use bne. Generally the code will be more efficient to test the opposite condition Here the opposite condition performs the subsequent then part of the if and we use the branch if register are not equal instruction (bne)

bne

$$$s3,$s4,Else # go to Else if i \neq j$$

The next assignment statement performs a single operation, and if all the operands are allocated to registers, it is just one instruction:

add

$$\$s0,\$s1,\$s2$$

# f = g + h (skipped if i  $\neq$  j)

To distinguish between conditional and unconditional branches, the MIPS name for this type of instruction is *jump*, abbreviated as j (the label Exit is defined below).

The label Exit that is after this instruction, showing the end of the *if-then-else* compiled code:

Else:sub

$$$s0,$s1,$s2$$

# f = g - h (skipped if i = j) Exit:

#### Loops

Looping statements are used to execute the same task more than one time until certain condition gets failed. **Example: Compiling a** *while* **Loop in C**

Here is a traditional loop in C:

```

while (save[i] == k)

i += 1:

```

Assume that i and k correspond to registers \$s3 and \$s5 and the base of the array save is in \$s6. What is the MIPS assembly code corresponding to this C segment?

#### Answer

The first step is to load save[i] into a temporary register. Before we can load save[i] into a temporary register, we need to have its address. Before we can add i to the base of array save to form the address, we must multiply the index i by 4 due to the byte addressing problem. We need to add the label Loop to it so that we can branch back to that instruction at the end of the

```

Loop: s11 $t1,$s3,2 # Temp reg $t1 = i * 4 loop.

```

To get the address of save[i], we need to add \$t1 and the base of save in \$s6:

```

add t1.t1.s6 # t1 = address of save[i]

```

Now we can use that address to load save[i] into a temporary register:

```

1w $t0,0($t1) # Temp reg $t0 = save[i]

```

The next instruction performs the loop test, exiting if save[i] #

```

bne $t0,$s5, Exit # go to Exit if save[i] ≠ k

```

The next instruction adds 1 to i:

```

addi $s3,$s3,1 # i = i + 1

```

The end of the loop branches back to the *while* test at the top of the loop. We just add the Exit label after it, and we're done:

```

j Loop # go to Loop

Exit:

```

#### **Basic Block:**

A sequence of instructions without branches (except possibly at the end) and without branch targets or branch labels (except possibly at the beginning).

**Comparison instructions:**MIPS compilers use the slt, slti, beq, bne, and the fixed value of 0 (always available by reading register \$zero) to create all relative conditions: equal, not equal, less than, less than or equal, greater than, greater than or equal. This is called comparison instructions.

#### Case/Switch Statement

Most programming languages have a *case* or *switch* statement that allows the programmer to select one of many alternatives depending on a single value.

Switch statement can be implemented in two ways:

Using chain of *if-then-else* statements. Using jump address table or jump table.

# 12. What is the need for addressing in a computer system? explain the different addressing modes with suitable examples. (Apr/May-2015,Nov/Dec -2014) Addressing Modes

The different ways in which the location of an operand is specified in an instruction are referred to as addressing modes. Different types of addresses involve tradeoffs between instruction length, addressing flexibility and complexity of address calculation.

#### **OverView**

The different types of addressing modes are:

Immediate addressing mode

Direct or absolute addressing mode

Indirect addressing mode

Register addressing mode

Indexed addressing mode(Displacement)

Relative addressing mode

Auto increment

Auto decrement

Implied (Stack, and a few others

### **Immediate Addressing and Small Operands**

The operand is given explicitly in the instruction.

Example: MOVE #200, R0

The above statement places the value 200 in the register R0. A common convention is to use the sharp sign (#) in front of the value to indicate that this value is to be used as an immediate operand. A great many immediate mode instructions use small operands (8 bits). In 32 or 64 bit machines with variable length instructions space is wasted if immediate operands are required to be the same as the register size. Some instruction formats include a bit that allows small operands to be used in immediate instructions. ALU will zero-extend or sign-extend the operand to the register size

#### Instruction

| op-code operand |  |

|-----------------|--|

|-----------------|--|

#### Figure 1.12 Immediate

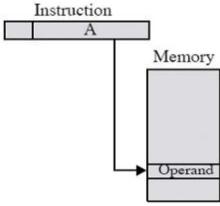

#### **Direct Addressing (Absolute addressing mode):**

The operand is in a memory location; the address of this location is given explicitly in the instruction. (In some assembly languages, this mode is called Direct.Example: **MOVE LOC**, **R2**This instruction copies the contents of memory location of LOC to register R2.

- Address field contains address of operand

- Effective address (EA) = address field (A)

- e.g. add ax, count or add ax,[10FC]

Figure 1.13. Direct Addressing

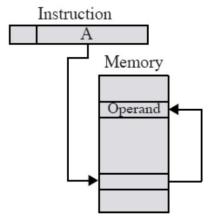

### **Memory-Indirect Addressing:**

The effective address of the operand is the contents of a register or memory location whose address appears in the instruction. Example Add (R2),R0 Register R2 is used as a pointer to the numbers in the list, and the operands are accessed indirectly through R2

The initialization section of the program loads the counter value n from memory location N into RI and uses the immediate addressing mode to place the address value NUM 1, which is the address of the first number in the list, into R2.

Figure.1.14. Memory-Indirect Addressing

#### **Register Direct Addressing:**

The operand is the contents of a processor register; the name (address) of the register is given in the instruction. Example: **MOVE R1,R2**This instruction copies the contents of register R2 to R1. Operand(s) is(are) registers EA = R• There are a limited number of registers Therefore a very small address field is neededShorter instructions Faster instruction fetch.

Figure 1.15. Register Direct Addressing:

# **Register Indirect Addressing:**

Similar to memory-indirect addressing;

EA = (R)

Operand is in memory cell pointed to by contents of register R Large address space (2n)

One fewer memory access than indirect Addressing

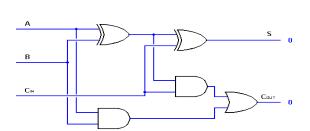

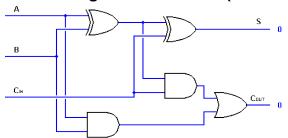

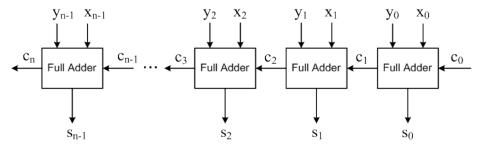

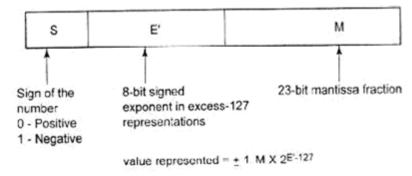

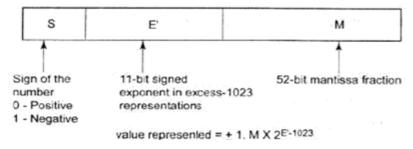

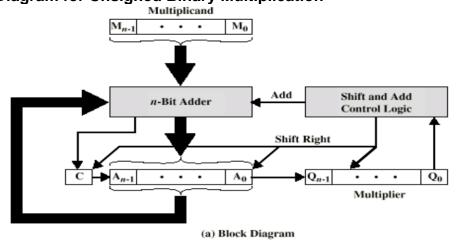

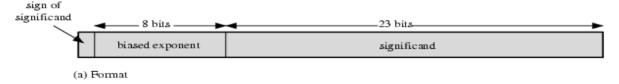

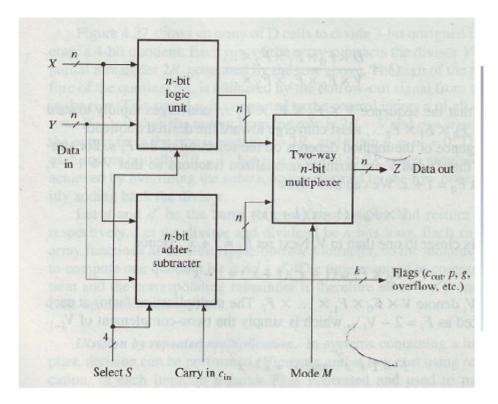

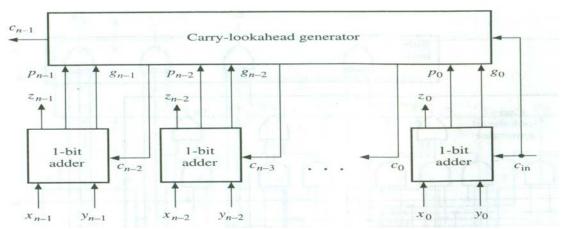

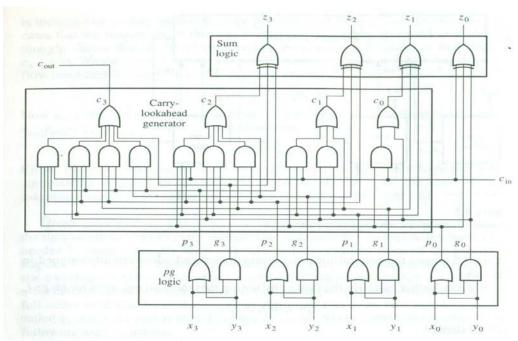

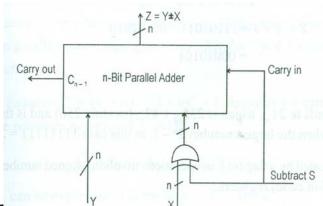

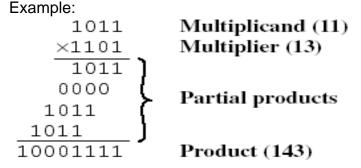

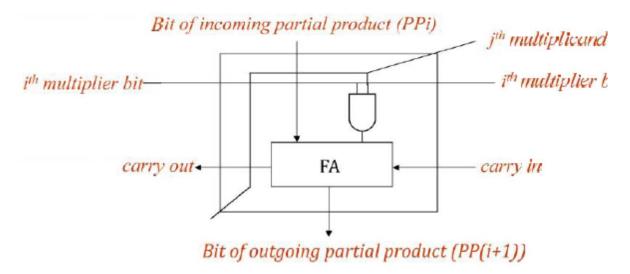

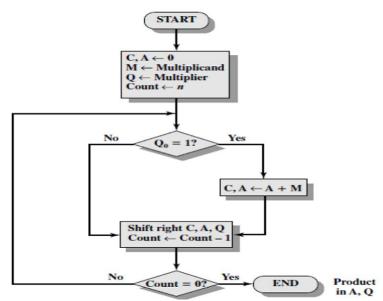

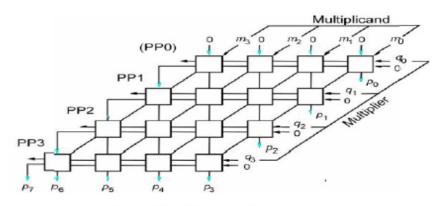

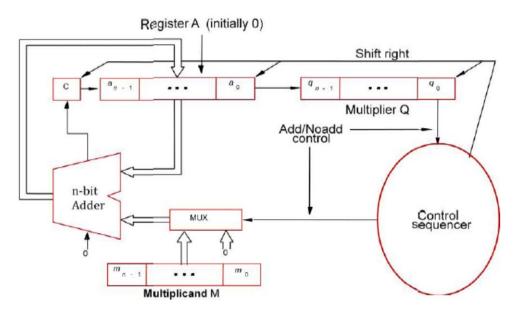

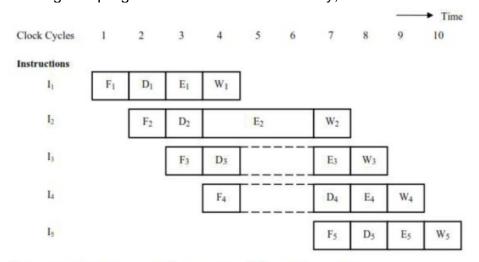

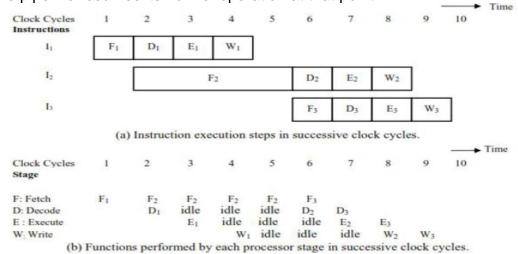

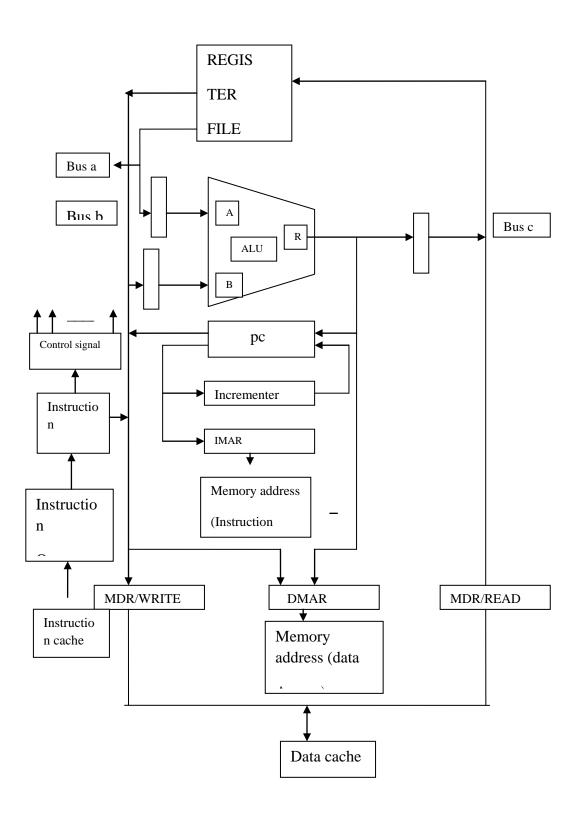

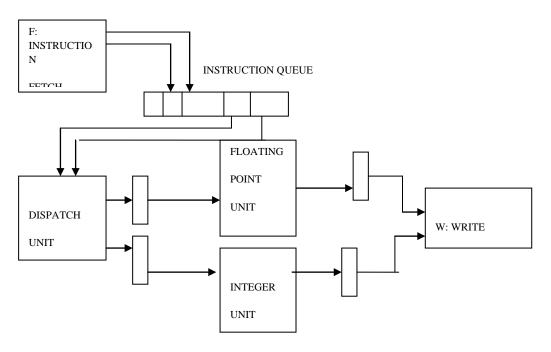

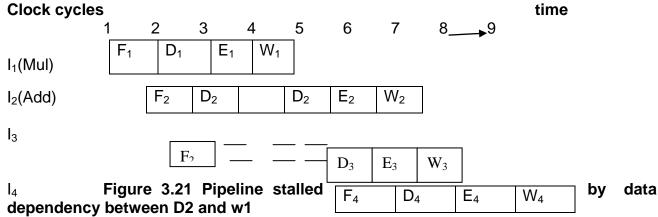

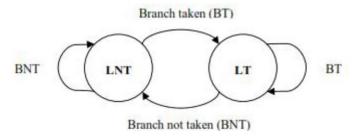

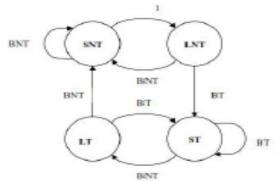

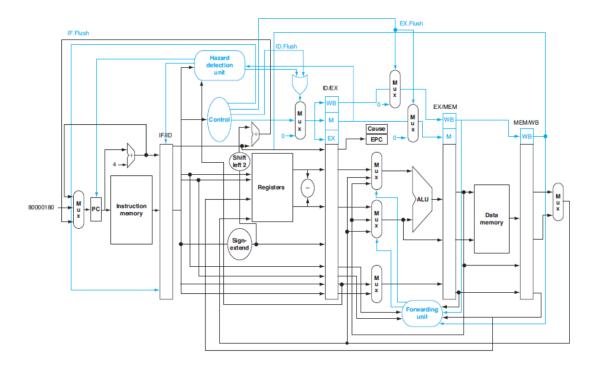

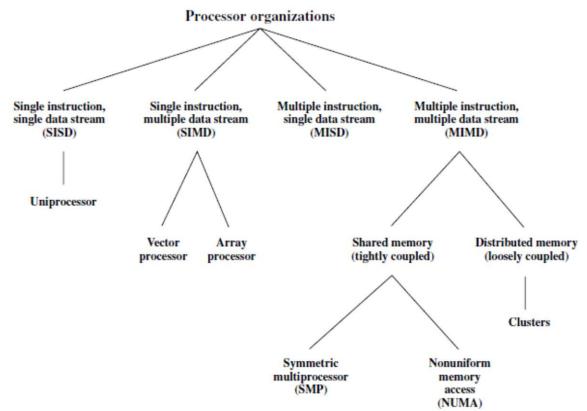

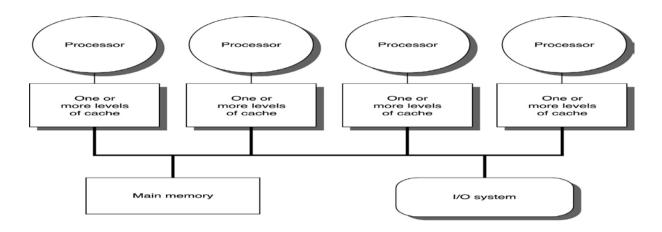

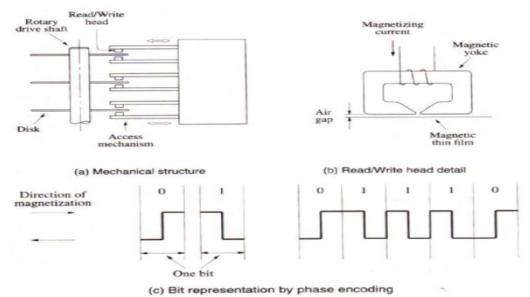

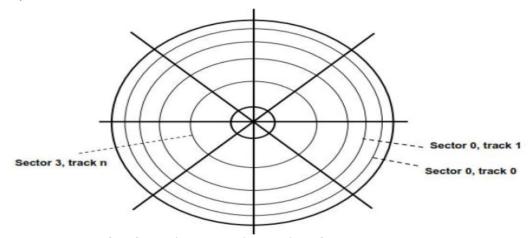

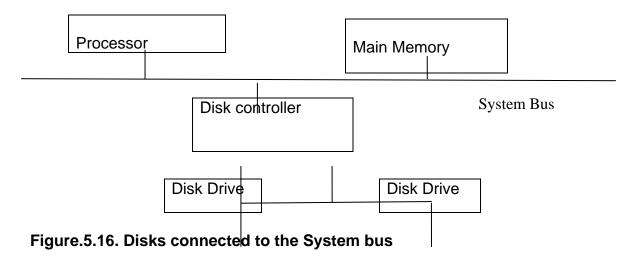

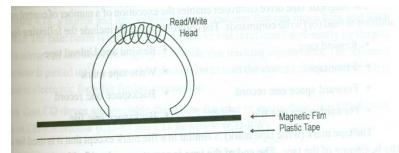

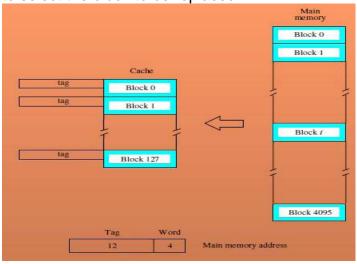

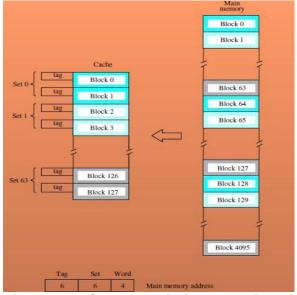

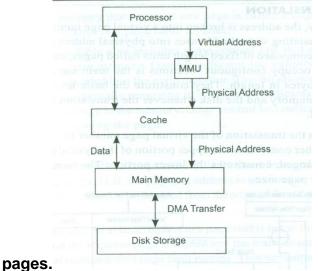

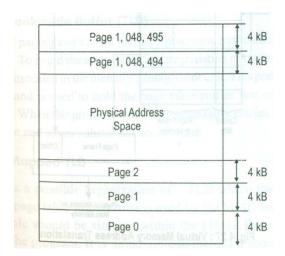

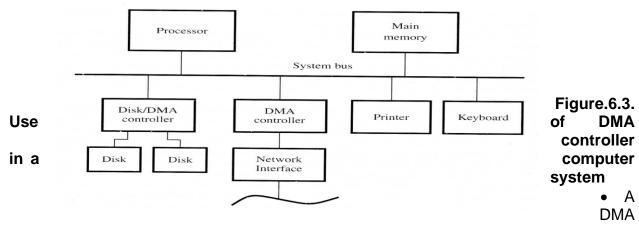

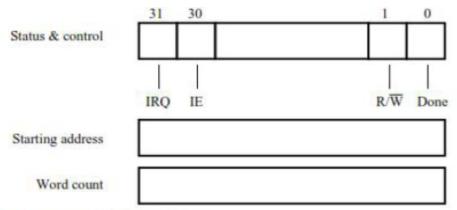

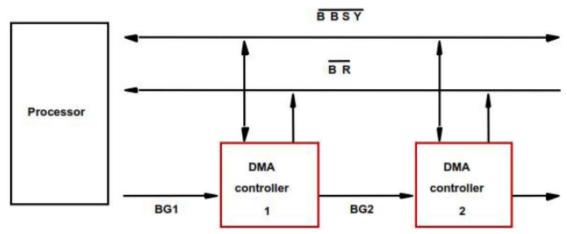

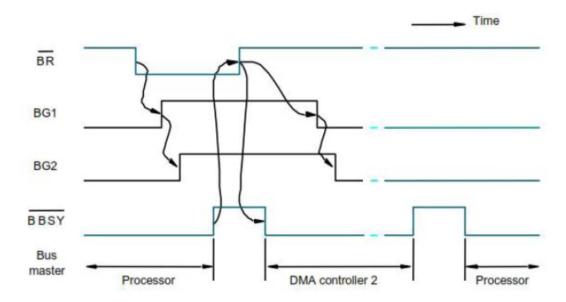

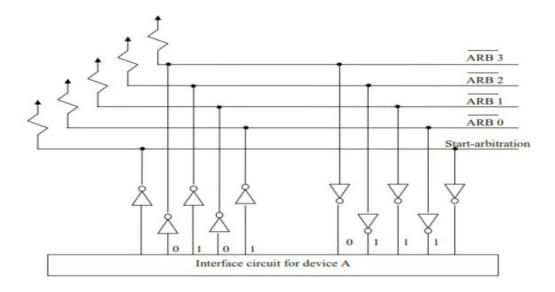

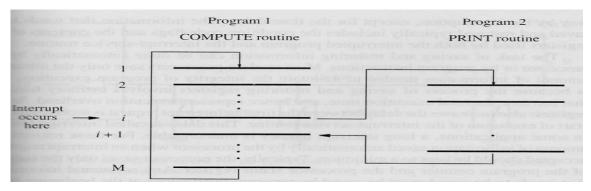

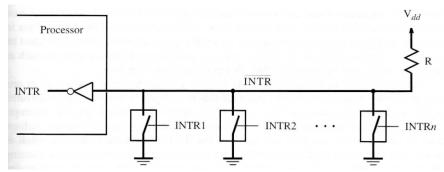

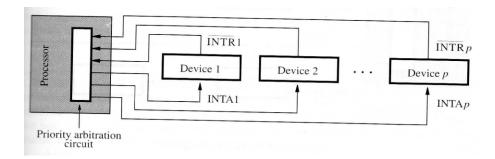

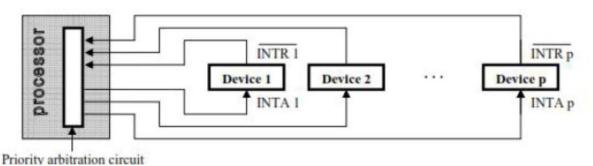

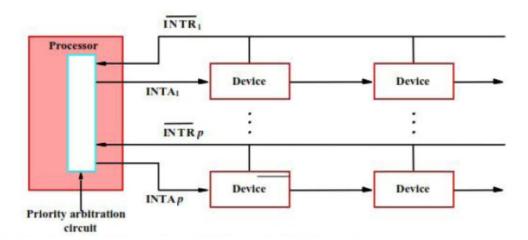

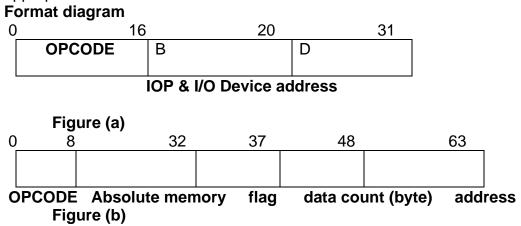

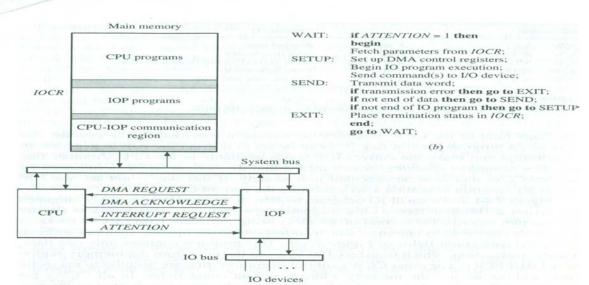

Figure 1.16. Register Indirect Addressi Displacement Addressing(Index addressing mode)