# MATLAB EXPO 2019

SoC Blockset 소개

정승혁

#### Agenda

### • What is SoC Blockset?

- Traditional Workflow and New Workflow for SoC Design

- Features of SoC Blockset

- Simulate SoC Architectures

- Analyze System Performance

- Deploy to SoC and FPGA Devices

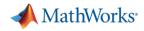

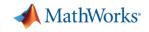

#### Model Based Design Workflow for SoC

**Deploy to Hardware with Coders and Hardware Support Packages**

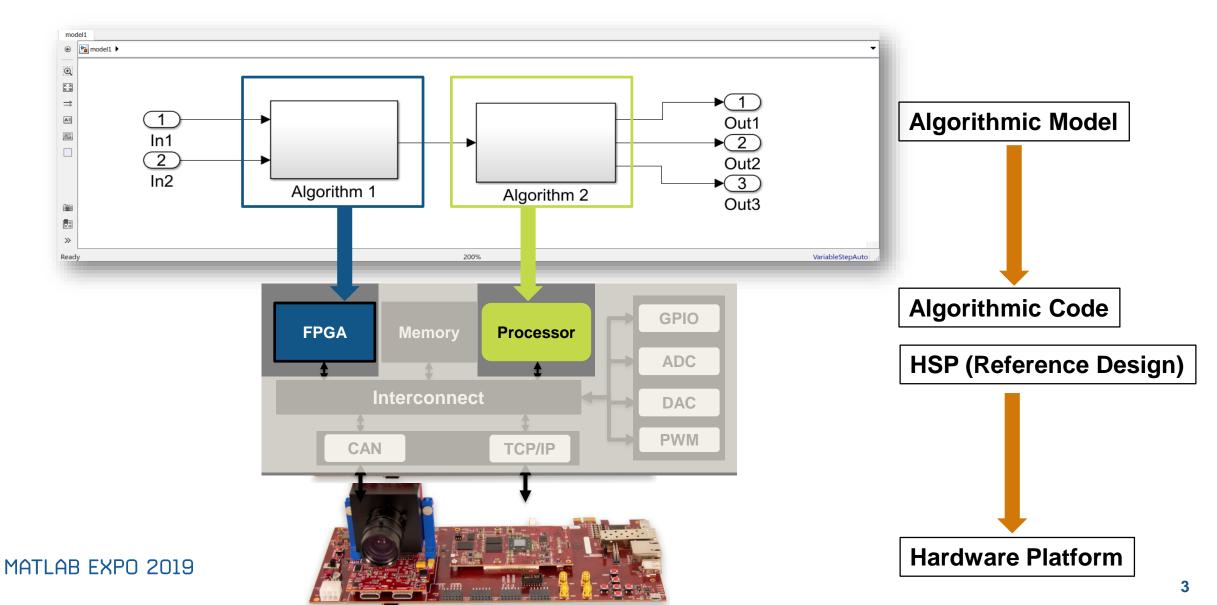

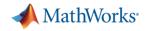

#### **Actual Data Exchange Between FPGA and Processor**

## Model Based Design Workflow for SoC

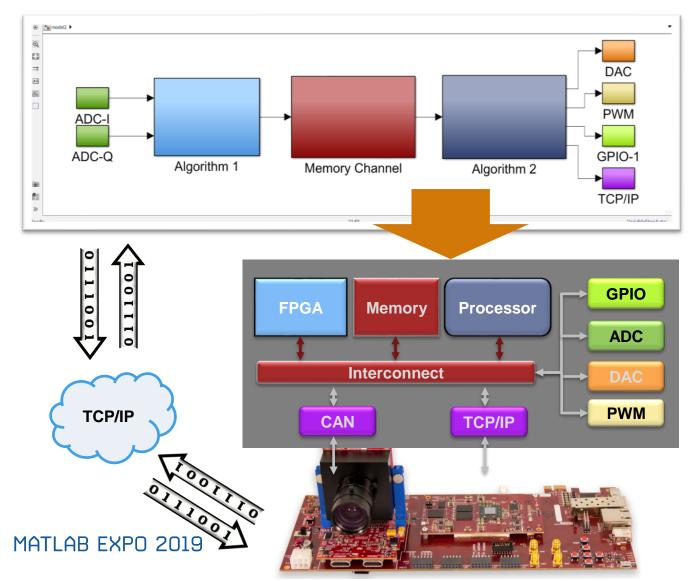

Hardware Architecture Simulation with SoC Blockset

- Simulate algorithms as well as hardware/software architecture

- ✓ Memory

- ✓ Internal/external connectivity

- ✓ I/O

- ✓ Task scheduling

- Deploy on support hardware

- Profile performance using external mode

#### **Short Demo Video**

#### Agenda

- What is SoC Blockset?

- Pains and the new solution

- Features of SoC Blockset

- Simulate SoC Architectures

- Analyze System Performance

- Deploy to SoC and FPGA Devices

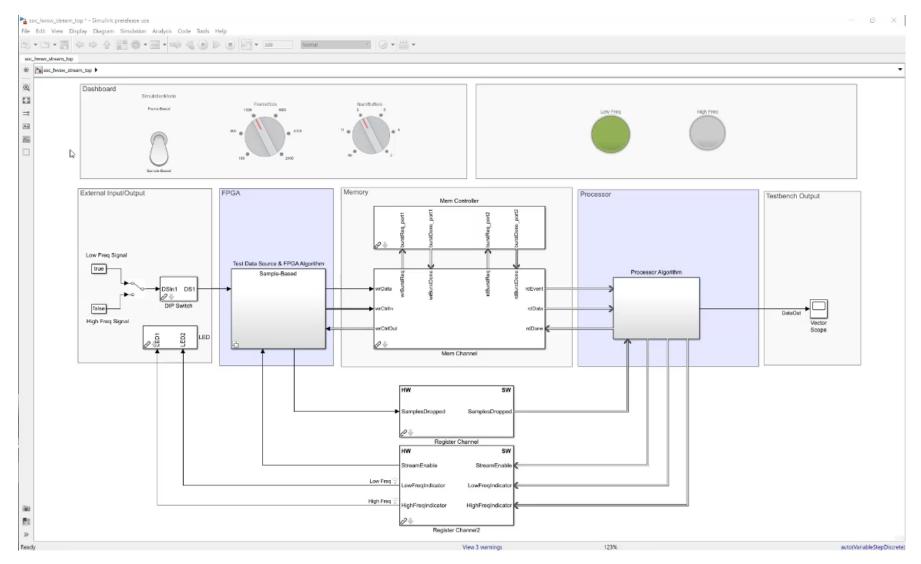

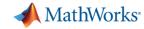

## **Simulate SoC Architectures**

- Memory channel blocks

- Register

- Shared memory

①①

Memory Channel

rdCtrlOut 🕨

rdCtrlln 🕻

**w**rCtrlln

wrCtrlOut

#### Multiple protocols

- AXI4-Stream to Software via DMA

- AXI4-Stream FIFO

- AXI4-Stream Video FIFO

- AXI4-Stream Video Frame Buffer

- AXI4-Random Access

- Memory channel blocks

- Register

- Shared memory

- Multiple protocols

- AXI4-Stream to Software via DMA

- AXI4-Stream FIFO

- AXI4-Stream Video FIFO

- AXI4-Stream Video Frame Buffer

- AXI4-Random Access

| uttons.<br>arameters |           | ng Move Up and |                    |  |

|----------------------|-----------|----------------|--------------------|--|

| Registers            |           |                |                    |  |

| Filter table (       | contents  |                |                    |  |

| Register             | Direction | Data Type      | Dimension          |  |

| reg1                 | Read      | uint32         | 1                  |  |

|                      |           |                | 1                  |  |

| reg2                 | Write     | uint32         | 1                  |  |

|                      |           |                | 1<br>2 Down Delete |  |

| New                  | Edit      |                |                    |  |

| New                  | Edit      | Move Up Move   |                    |  |

|          | e board:<br>plementatior | <u>n info</u> | 4         | <u>ZedBoard</u> |   |

|----------|--------------------------|---------------|-----------|-----------------|---|

| Main     | Signal Att               | ributes       | Perform   | ance            |   |

| Channe   | type: AXI4               | -Stream       | to Softwa | are via DMA     | - |

| Region s | size (bytes):            | 8192          |           |                 |   |

| Buffer s | ize (bytes):             | 1024          |           |                 |   |

| Number   | of buffers:              | 8             |           |                 |   |

| Adva     | nced                     |               |           |                 |   |

|          |                          |               |           |                 |   |

|          |                          |               |           |                 |   |

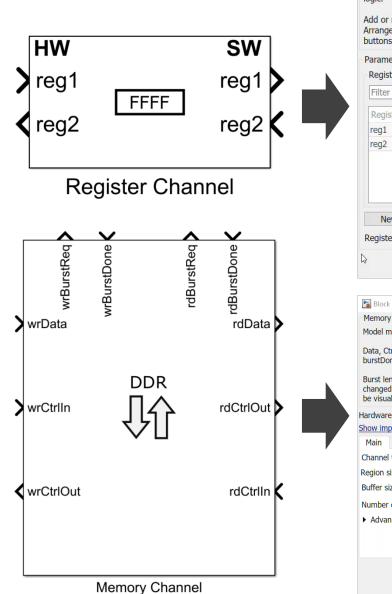

#### Memory controller block

- Arbitrate access to shared memory

- Support multiple channels

- Support various arbitration protocols

- Log and display performance data

- Latency, Burst, Bandwidth

- Visualize internal state via Logic Analyzer

| 🔛 soc_hwsw_stream_top - Logic An                                                                                                                                                                                                                       | alyzer                           |          |             |            |                         |                      |        |             |          |            |            | — C         | ) ×                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------|-------------|------------|-------------------------|----------------------|--------|-------------|----------|------------|------------|-------------|----------------------|

| LOGIC ANALYZER TRIGGER                                                                                                                                                                                                                                 |                                  |          |             |            |                         |                      |        |             | SHAN.    |            | (X) X (=   | 14 % I      | ?                    |

|                                                                                                                                                                                                                                                        | 4                                | ⇒ 🔒      | Lock        | Q. Q       | 4. 🕒                    |                      | Q      | ٢           |          |            |            |             |                      |

|                                                                                                                                                                                                                                                        | dd Previous<br>rsor Transition T | Next 🗐   | Delete      | 🖤 ્ 🔳      | Stepping Run<br>Options | Step Stop<br>Forward | Find   | Settings    |          |            |            |             |                      |

| EDIT                                                                                                                                                                                                                                                   | CURS                             | ORS      |             | ZOOM & PAN | SIM                     |                      | FIND   | GLOBAL      |          |            |            |             | -                    |

| Memory Controller/log/Master01/ <r< td=""><td></td><td>-1</td><td><u>)</u>-1</td><td><u>¥-1</u></td><td><u>¥-1</u></td><td>χ-1</td><td></td><td><u>)</u>-1</td><td>χ-1</td><td>1-1</td><td><u>γ-1</u></td><td><u></u>Υ-1</td><td><u>(</u>-1)</td></r<> |                                  | -1       | <u>)</u> -1 | <u>¥-1</u> | <u>¥-1</u>              | χ-1                  |        | <u>)</u> -1 | χ-1      | 1-1        | <u>γ-1</u> | <u></u> Υ-1 | <u>(</u> -1)         |

| Memory Controller/log/Master02/ <t< td=""><td></td><td>0</td><td>i</td><td></td><td></td><td></td><td></td><td><i>*</i></td><td></td><td></td><td>- ^</td><td>,</td><td>· ·</td></t<>                                                                  |                                  | 0        | i           |            |                         |                      |        | <i>*</i>    |          |            | - ^        | ,           | · ·                  |

| Memory Channel/log/Reader/ <buff< td=""><td></td><td>5090</td><td></td><td></td><td>5091</td><td></td><td></td><td></td><td></td><td>5092</td><td></td><td></td><td></td></buff<>                                                                      |                                  | 5090     |             |            | 5091                    |                      |        |             |          | 5092       |            |             |                      |

| Memory Controller/log/Master01/ <t< td=""><td></td><td>20357</td><td>20358</td><td>20359</td><td>20360</td><td>20361</td><td></td><td>20362</td><td>20363</td><td>20364</td><td>20365</td><td>20366</td><td>203</td></t<>                              |                                  | 20357    | 20358       | 20359      | 20360                   | 20361                |        | 20362       | 20363    | 20364      | 20365      | 20366       | 203                  |

|                                                                                                                                                                                                                                                        |                                  | 0        |             |            |                         |                      |        |             |          |            |            |             |                      |

|                                                                                                                                                                                                                                                        |                                  | 0        |             |            |                         |                      |        |             |          |            |            |             |                      |

|                                                                                                                                                                                                                                                        |                                  | 5090     |             |            |                         | 5091                 |        |             |          |            | 5092       |             |                      |

|                                                                                                                                                                                                                                                        |                                  | 20357000 | 2035800     | 0 (20359   |                         | 000 203610           | 00     | 20362000    | 20363000 | 20364000   | 20365000   | 20366000    | 0 <mark>(</mark> 203 |

|                                                                                                                                                                                                                                                        |                                  | 4        |             |            | )(5                     |                      |        |             |          | 16         |            |             |                      |

|                                                                                                                                                                                                                                                        |                                  | 1        |             |            | )(2                     | (1                   |        |             |          | 2 (1       |            |             |                      |

| Memory Channel/log/Writer/<br>                                                                                                                                                                                                                         |                                  | 4        |             |            | )(5                     |                      |        |             |          | <b>)</b> 6 |            |             |                      |

| Memory Channel/log/Writer/<br>                                                                                                                                                                                                                         |                                  | 5089     |             |            | 5090                    |                      |        |             |          | 5091       |            |             |                      |

| Memory Channel/log/Reader/<br>                                                                                                                                                                                                                         |                                  | 3        |             |            |                         | (4                   |        |             |          | (5         | 90         |             |                      |

| Memory Channel/log/Reader/<br>bufT<br>Memory Channel/log/Writer/ <icfif< td=""><td></td><td>5088</td><td></td><td>Yo</td><td>Yo</td><td>(5089<br/>Y0</td><td></td><td>Yō</td><td>Yo</td><td>150</td><td><u>Y0</u></td><td>Yo</td><td>Ve</td></icfif<>  |                                  | 5088     |             | Yo         | Yo                      | (5089<br>Y0          |        | Yō          | Yo       | 150        | <u>Y0</u>  | Yo          | Ve                   |

| Memory Channel/log/Writer/ <icfii< td=""><td></td><td>0</td><td>10</td><td>10</td><td>10</td><td>10</td><td></td><td>10</td><td>10</td><td></td><td>10</td><td>χυ</td><td>70</td></icfii<>                                                             |                                  | 0        | 10          | 10         | 10                      | 10                   |        | 10          | 10       |            | 10         | χυ          | 70                   |

| Memory Channel/log/Writer/ <icfif< td=""><td></td><td>0</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></icfif<>                                                                               |                                  | 0        |             |            |                         |                      |        |             |          |            |            |             |                      |

| Memory Channellog/Whitel/~icFiFV                                                                                                                                                                                                                       |                                  | 0        |             |            |                         |                      |        |             |          |            |            |             |                      |

|                                                                                                                                                                                                                                                        |                                  | 508      | 395 ms      | 50898 r    | ns 509                  | 01 ms 5              | 0904 m | ns 50!      | 907 ms   | 50910 ms   | 50913 ms   | 50916       | ms                   |

|                                                                                                                                                                                                                                                        |                                  |          |             |            |                         |                      |        |             |          |            |            |             |                      |

|                                                                                                                                                                                                                                                        |                                  |          |             |            |                         |                      |        |             |          |            |            |             |                      |

| Cursor 3                                                                                                                                                                                                                                               | 22780.00 m                       | 15       |             |            |                         |                      |        |             |          |            |            |             |                      |

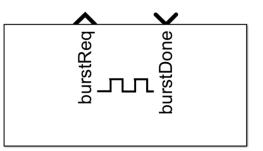

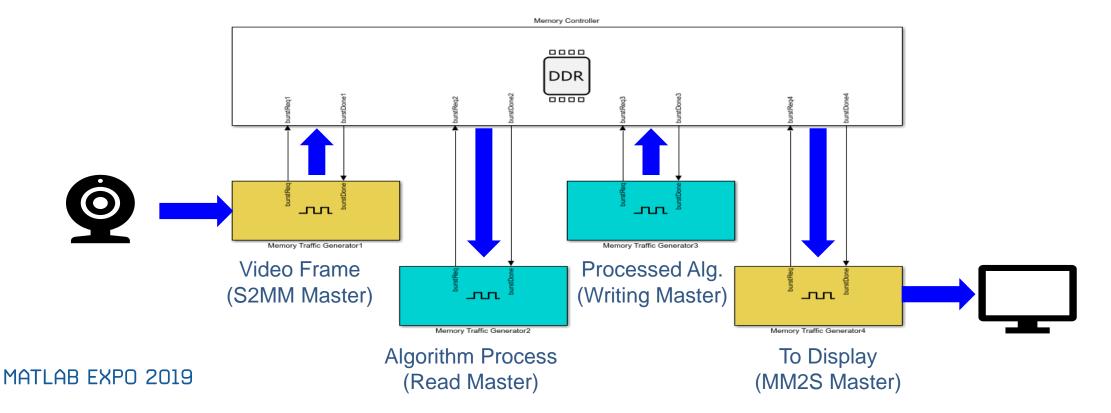

- Memory traffic generator

- Generate read or write requests to the memory

- Model the impact of a master's memory accesses

- Characterize performance of memory subsystem under contention

Memory Traffic Generator

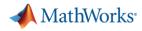

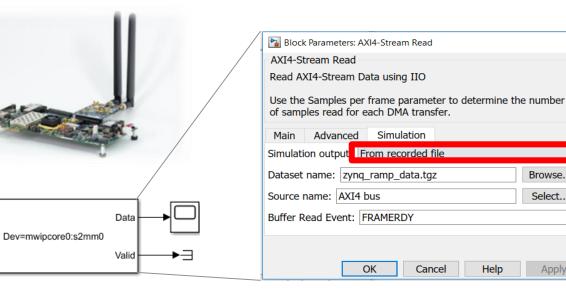

#### Modeling I/Os

- Processor I/O

- TCP Read/Write

- UDP Read/Write

- Register Read/Write

#### Hardware Logic I/O

- DIP Switch, LED, Pushbutton

- I2C Master

#### Simulation with real I/O data

- Record real I/O data

- Simulate with record data

$\times$

Browse...

Select...

Apply

Help

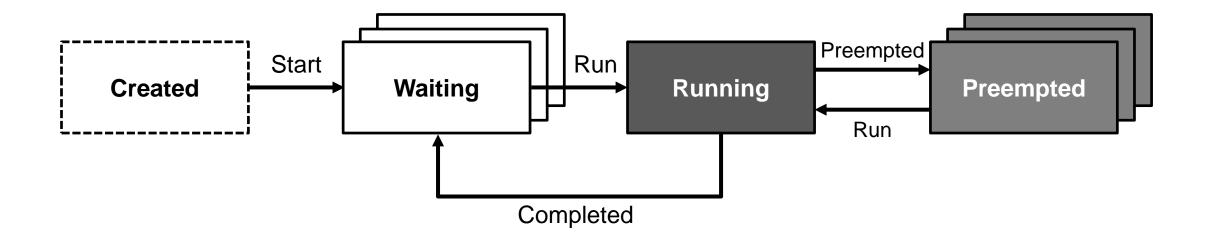

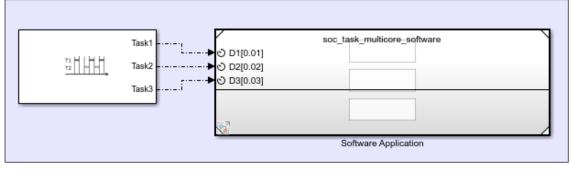

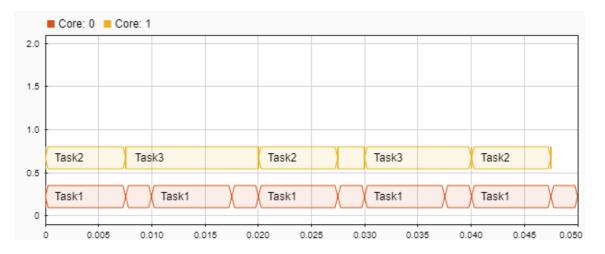

#### **Modeling Task Execution**

- Task execution on hardware is managed by Operating System

- Task is a portion of Simulink model contained within a sample rate or function-call subsystem

#### **Modeling Task Execution**

- Task manager block

- Timer-Driven, Event-driven

- Probability model

- From a data file recording

- Input ports on the block

- Parameters

- Task Period, Task Duration

- Priority

- Processor core

- Task Visualization in SDI\*

\*SDI: Simulation Data Inspector

#### **Modeling Software Algorithm**

- Detect task overruns and implement countermeasures

- Visualize task priority and preemption

- Simulate multicore task execution

- Record and playback task execution in simulation

ARM Processor

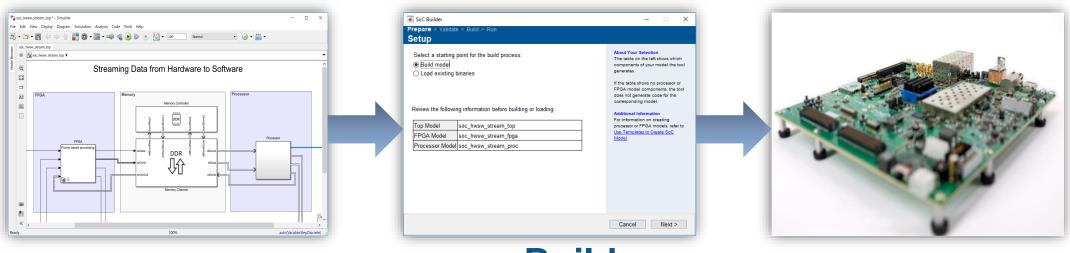

## **Deploy to SoC and FPGA Devices**

#### **Deploying Architecture on Hardware Boards**

- Generate reference designs for FPGAs and SoCs from Xilinx and Intel

- Generate HDL for hardware algorithm (require HDL Coder)

- Generate C/C++ for processor algorithm (require Embedded Coder)

### Implementing on Xilinx SoC and FPGA Platforms

#### Tools

- Vivado Design Suite 2018.2

- Boards

- FPGA: Artix-7 35T Arty, Kintex-7 KC705

- Zynq 7000: ZC706, ZedBoard

- Zynq UltraScale+: ZCU102

- I/O modules

- HDMI Tx/Rx

- AD9361 Rx/Tx

- ADAU17612 codec

### **Implementing on Altera SoC and FPGA Platforms**

#### Tools

- Intel Quartus Prime Standard Edition 18.0

- Intel SoC FPGA Embedded Development Suite (EDS) 18.0

- Boards

- Arria 10 SoC Development Kit

- Cyclone V SoC Development Kit

- I/O modules

- None

#### socBuilder

**SoC Builder** tool steps through the various stages for building and executing an SoC model on FPGA/SoC

- Review the model information and memory map

- Choose build actions (Build, Load, Run)

- Build the model using Xilinx or Intel tools

- Configure the Ethernet connectivity

- Load the programming file to your FPGA board

- Run the application

#### socBuilder

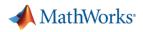

### **Customizing OS on Embedded Processor**

- Libraries added

- Audio

- Video capture

- Data inspector

- SDL Display

- File transfer

- Register read/write

- AXI stream

- OS Customizer

- Support for Debian, Yocto, PetaLinux, and BuildrootLinux distributions.

- Support for OS with Package Management System

- Support for external OS firmware image build systems (host or remote)

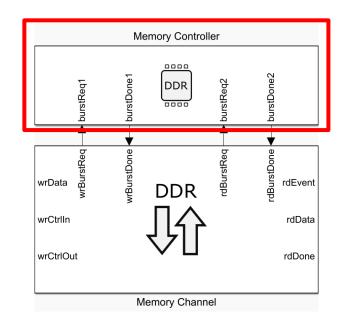

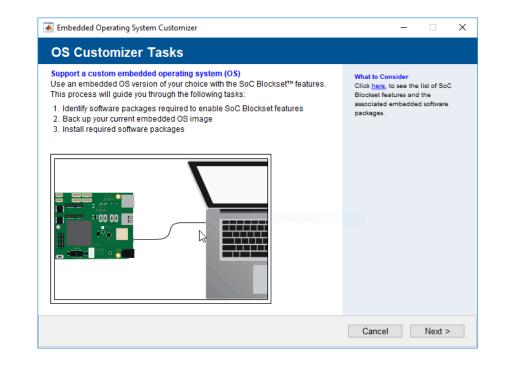

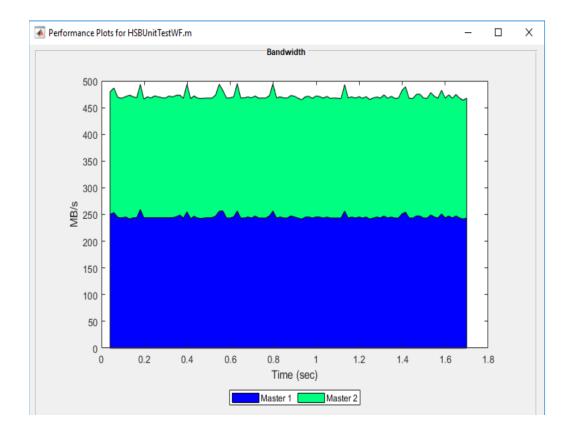

## Analyze System Performance (On-Device Profiling)

### **Profiling on Hardware Devices**

#### Code instrument profiler

- Record the start and stop times of each task on the processor

- Infer instantaneous state of each task

- Does not record Kernel latency

- Light instrument code

- Negligible impact on task execution

- Running in external mode

- Task execution data and statistics are recorded in files

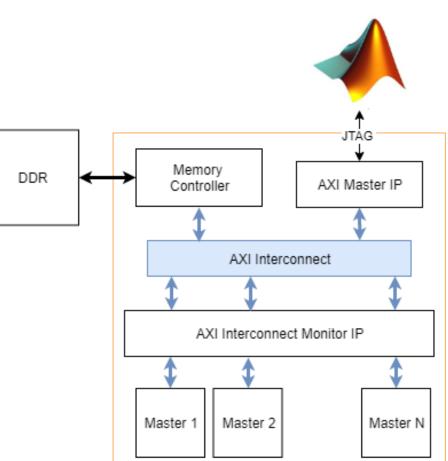

#### **AXI Interconnect Monitor**

- All memory masters in FPGA are connected to AXI Interconnect Monitor IP

- Data queried from MATLAB using JTAG

- Collect memory interconnect traffic

- Capture transaction information

#### **Configuration for Profiling** *Hardware Implementation Pane*

| Hardware board: Xilinx Zynq Ultras  | Scale+ MPSoC ZCU102 Evaluation Kit            | ▼                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Code Generation system target file: | ert.tlc                                       |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Device vendor: ARM Compatible       | ▼ Device type                                 | : ARM 64-bit (LP64) ▼                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Device details                      |                                               |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Hardware board settings             |                                               |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Task profiling in simulation        | <ul> <li>Target hardware resources</li> </ul> |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Show in SDI                         | Groups                                        |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| ✓ Save to file                      | Board Parameters                              | View/Edit Memory Map                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                                     | Build options                                 |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                     | Clocking                                      | <ul> <li>Include 'MATLAB as AXI Master' IP for host-based interaction</li> <li>Include processing system</li> <li>Interrupt latency (s): 0.00001</li> <li>Register configuration clock frequency (MHz): 50</li> <li>IP core clock frequency (MHz): 100</li> </ul> |  |  |  |  |  |  |

|                                     | External mode                                 |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                     | FPGA design (top-level)                       |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                     | FPGA design (mem controllers)                 |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                     | EBCA design (mem channels)                    |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                     | FPGA design (mem channels)                    |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

#### **Profiling on Hardware Devices**

- Bring real-time hardware diagnostics back to Simulink

- Task execution profiling

- Memory traffic monitoring

- DMA buffer usage

- CPU utilization

- Analyze and tune SoC model to meet your desired system performance

- Run the SoC model in external mode

- Interact in real time with an SoC device

#### Conclusion

#### With SoC Blockset, you can

- **Simulate** your hardware architecture with algorithms

- **Profile** software performance and hardware utilization on hardware devices

- **Deploy** on Xilinx and Intel devices

#### **Learn More**

## SoC Blockset Design, evaluate, and implement SoC hardware and software architectures

- SoC Blockset Webpage

- SoC Blockset Examples

- SoC Blockset Product Requirement

- Supported Hardware Boards: Xilinx, Intel

# MATLAB EXPO 2019

데모부스와 상담부스로 질문 하시기 바랍니다.

감사합니다