SRC JUMP 2.0 Proposers Workshop January 25, 2022

Theme 6: Advanced Monolithic and Heterogeneous Integration

## Advanced Heterogeneous Integration

Prepared by Johanna Swan, Fellow, Intel Corporation

Adapted and presented by Henning Braunisch, Principal Engineer, Intel Corporation

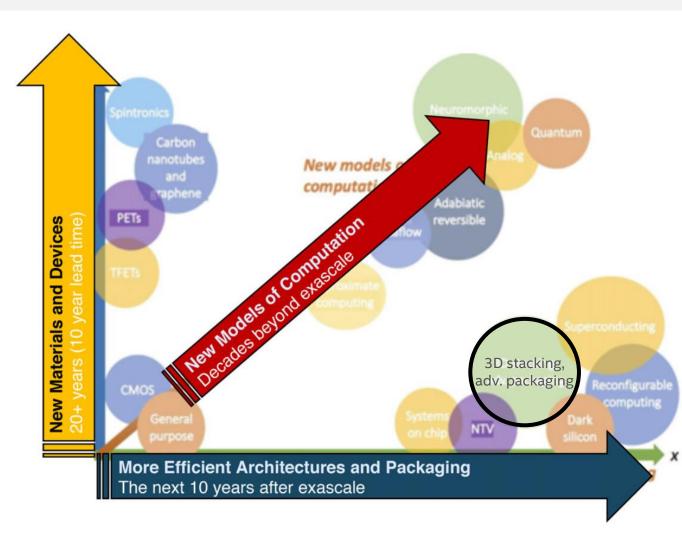

## The Future of Compute Performance

- Three Vectors

- More efficient architectures and packaging leveraged for advanced heterogeneous integration

- 3D Stacking & Advanced Packaging

- Focus on functional densification with performance, power, area, and cost

Ref.: J. Shalf, "The future of computing beyond Moore's Law," *Philosophical Transactions. Series A, Mathematical, Physical, and Engineering Sciences,* 378 (2166), March 1, 2020.

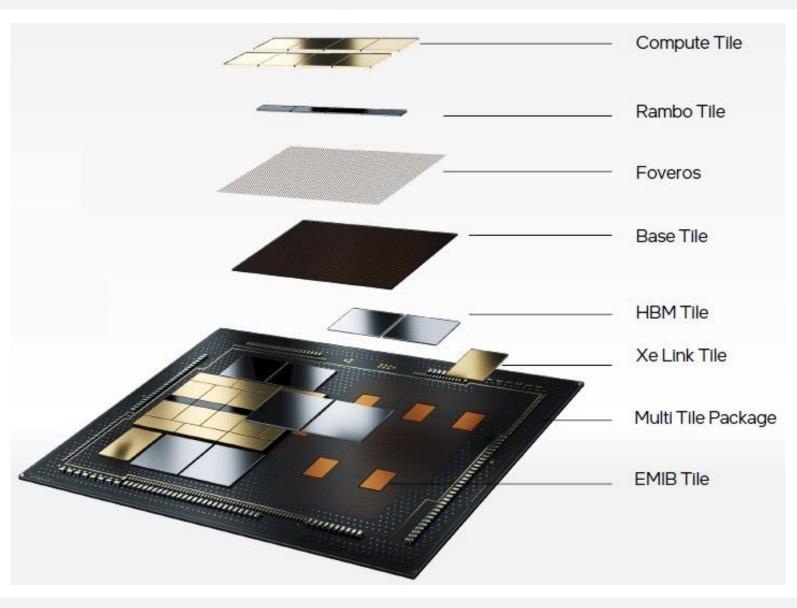

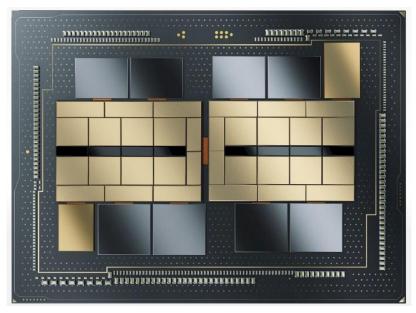

## Functional Densification: Intel's Ponte Vecchio

- 47 Tiles

- Five Process Nodes

- Foveros and EMIB

Integration in the Same

Package

### Challenge1: Harness & Exploit Increasing Design Complexity

Ref.: ARM & GF, IEDM 2020 with adaptation

| Full Stack Reference Designs      | At Scale                   |

|-----------------------------------|----------------------------|

| With Performance Validation       | i.e. mix-n-match ICs       |

| Physical Implementation Flow with | Production Class Solutions |

| IEEE 1838 3DIC DFT Standard       | Agnostic to Vendor         |

| 3D Design Space &                 | Opportunity to Drive       |

| System Level Co-Optimization      | Best In Class Solutions    |

| Interface Standards               | Proprietary & Open         |

|                                   |                            |

Solutions Needed

More tiles means even more complexity

• Opportunity to leverage the Intel university shuttle program and driving the ecosystem with circuit, design & validation innovations

## Imagine... Al Driven System Design

#### Article

## A graph placement methodology for fast chip design

#### https://doi.org/10.1038/s41586-021-03544-w

Received: 3 November 2020

Accepted: 13 April 2021

#### Published online: 9 June 2021

Check for updates

Azalia Mirhoseini<sup>1,4</sup>, Anna Goldie<sup>1,3,4</sup>, Mustafa Yazgan<sup>2</sup>, Joe Wenjie Jiang<sup>1</sup>, Ebrahim Songhori<sup>1</sup>, Shen Wang<sup>1</sup>, Young-Joon Lee<sup>2</sup>, Eric Johnson<sup>1</sup>, Omkar Pathak<sup>2</sup>, Azade Nazi<sup>1</sup>, Jiwoo Pak<sup>2</sup>, Andy Tong<sup>2</sup>, Kavya Srinivasa<sup>2</sup>, William Hang<sup>3</sup>, Emre Tuncer<sup>2</sup>, Quoc V. Le<sup>1</sup>, James Laudon<sup>1</sup>, Richard Ho<sup>2</sup>, Roger Carpenter<sup>2</sup> & Jeff Dean<sup>1</sup>

Chip floorplanning is the engineering task of designing the physical layout of a computer chip. Despite five decades of research<sup>1</sup>, chip floorplanning has defied automation, requiring months of intense effort by physical design engineers to produce manufacturable layouts. Here we present a deep reinforcement learning approach to chip floorplanning. In under six hours, our method automatically generates chip floorplans that are superior or comparable to those produced by humans in all key metrics, including power consumption, performance and chip area.

- Could a similar approach be leveraged to design & package heterogeneous systems? Considerations include...

- Physical Design

- Timing/Clocking Schemes

- Thermal Management

- Power Delivery

- Mechanical Robustness through

Process & Reliability Testing

### Challenge 2: Find & Eliminate Impact of < 100 nm Defects

Non-destructive, fast methods to find organic & inorganic defects before & after bonding to ensure yield and quality

## Imagine... 3D Imaging Through Multi-Layer Metals

Articles https://doi.org/10.1038/s41928-019-0309-z

electronics

## Three-dimensional imaging of integrated circuits with macro- to nanoscale zoom

Mirko Holler<sup>®</sup><sup>1\*</sup>, Michal Odstrcil<sup>1</sup>, Manuel Guizar-Sicairos<sup>®</sup><sup>1</sup>, Maxime Lebugle<sup>1</sup>, Elisabeth Müller<sup>1</sup>, Simone Finizio<sup>®</sup><sup>1</sup>, Gemma Tinti<sup>1</sup>, Christian David<sup>1</sup>, Joshua Zusman<sup>2</sup>, Walter Unglaub<sup>2</sup>, Oliver Bunk<sup>®</sup><sup>1</sup>, Jörg Raabe<sup>®</sup><sup>1</sup>, A. F. J. Levi<sup>2</sup> and Gabriel Aeppli<sup>1,3,4</sup>

The imaging of integrated circuits across different length scales is required for failure analysis, design validation and quality control. At present, such inspection is accomplished using a hierarchy of different probes, from optical microscopy on the millimetre length scale to electron microscopy on the nanometre scale. Here we show that ptychographic X-ray laminography can provide non-destructive, three-dimensional views of integrated circuits, yielding both images of an entire chip volume and high-resolution images of arbitrarily chosen subregions. We demonstrate the approach using chips produced with 16 nm fin field-effect transistor technology, achieving a reconstruction resolution of 18.9 nm, and compare our results with photolithographic mask layout files and more conventional imaging approaches such as scanning electron microscopy. The technique should also be applicable to other branches of science and engineering where three-dimensional X-ray images of planar samples are required.

Need large-area scanning at production ready speeds with nano-scale resolution through multiple metal layers without impacting device performance

### Challenge 3: Place 20k+ Tiles per Hour at < 200 nm Accuracy

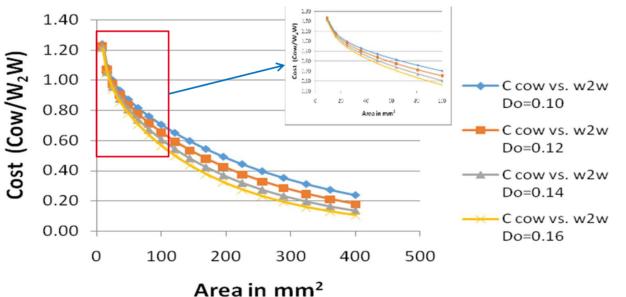

From Bose Einstein (BE) model

Ref.: D. Gitlin et al., "Generalized cost model for 3D systems," 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S)

- Die to wafer bonding may be cost effective at large die sizes relative to wafer bonding especially at high defect densities

- As the die size reduces to less than ~30 mm<sup>2</sup> or the number of tiles per base tile increases, the cost of assembly increases unfavorably without further assembly advancements

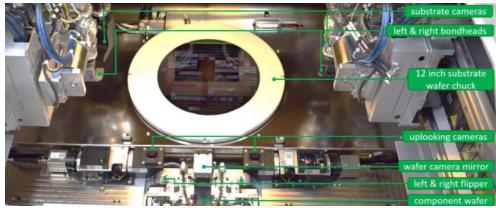

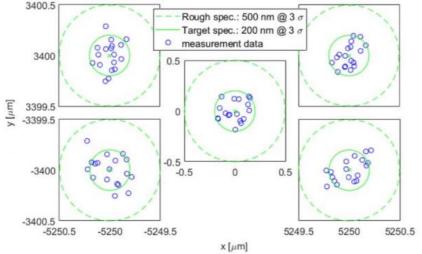

#### **Die-to-Wafer Equipment**

#### Nearly 200 nm Accuracy at 2000 Units Per Hour

Ref.: B. Brandstätter et al., "High-speed ultra-accurate direct C2W bonding," 2020 IEEE 70<sup>th</sup> Electronic Components and Technology Conference (ECTC)

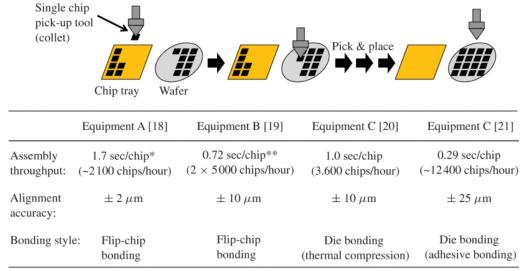

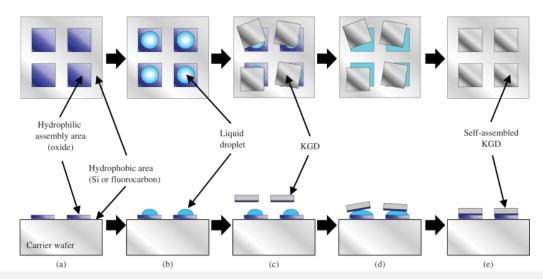

### Imagine... Nanoscale Self-Assembly of Dies in Batch

1873

IEEE TRANSACTIONS ON COMPONENTS, PACKAGING AND MANUFACTURING TECHNOLOGY, VOL. 1, NO. 12, DECEMBER 2011

#### Multichip Self-Assembly Technology for Advanced Die-to-Wafer 3-D Integration to Precisely Align Known Good Dies in Batch Processing

Takafumi Fukushima, *Member, IEEE*, Eiji Iwata, Yuki Ohara, Mariappan Murugesan, Jichoel Bea, Kangwook Lee, *Member, IEEE*, Tetsu Tanaka, *Member, IEEE*, and Mitsumasa Koyanagi, *Fellow, IEEE* An advanced die-to-wafer 3-D integration using a surface-tension-driven multichip self-assembly technology was proposed to 3-D stack a large number of known good dies (KGDs) in batch processing. The parallel self-assembly with a unique multichip pick-up tool was newly applied to die-to-wafer 3-D integration to overcome throughput and yield problems in conventional 3-D integration approaches. In addition, novel batch transfer of chips self-assembled on a carrier wafer to the corresponding target wafer was demonstrated. By using the multichip self-assembly, many KGDs can be precisely aligned and temporarily placed on a carrier wafer all at once, and then, the self-assembled KGDs can be simultaneously transferred to another target wafer in a face-to-face bonding manner at the wafer level. Average alignment accuracy was found to be approximately 400 nm when a hundred 3-mm-square chips were self-assembled on carrier wafers with small droplets of an aqueous solution. The alignment accuracy was experimentally proven to be fairly dependent on liquid surface tension as a self-assembly parameter.

Equipment & material advancements in combination with self-assembly are needed to achieve 10x faster die placements

\* This cycle time dose not include processing time such as loading, bonding, and vacuum release. \*\*This equipment having two bond heads can offer two machines in just one compact module.

## Summary & Conclusions

- We are at the beginning of a period where the future of compute performance relies on efficient advanced 3D packaging of extremely heterogeneous systems

- Numerous challenges face the industry. A sampling includes:

- 1. Harnessing & exploiting increasing design complexity

- 2. Finding and eliminating the impact of < 100 nm defects non-destructively

- 3. Placing 20k+ tiles per hour at < 200 nm accuracy

- This is an exciting time when fab processes & methodologies are colliding with traditional packaging know-how

- JUMP 2.0 Theme 6 provides an excellent opportunity for impactful research in this space

SRC JUMP 2.0 Proposers Workshop January 25, 2022

Theme 6

## Advanced Monolithic and Heterogeneous Integration

Marko Radosavljevic, Principal Engineer, Intel Corporation

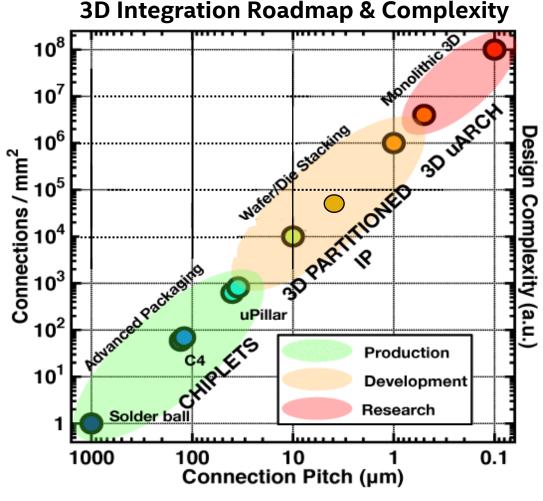

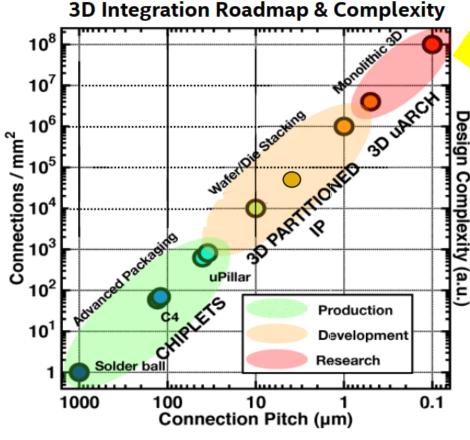

## Exploding design complexity of the future

Ref.: ARM & GF, IEDM 2020 with adaptation

Monolithic 3D provides most connections

- Makes tiles more complex but perhaps reduces number of tiles

- Correct choice for each application set?

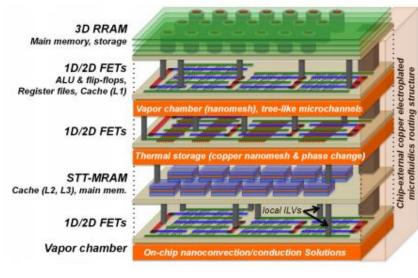

## Monolithic 3D with heterogeneous materials for heterogeneous applications

Ref.: Stanford SystemX

- Monolithic 3D but each layer virtually independent

- Thermal budget considerations

- Bottom up integration or layer transfer techniques

- Is there tight pitch requirement → good interlayer alignment

- Infinite choice of applications

- Differentiate vs. packaging techniques

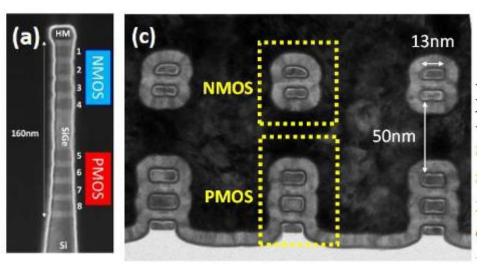

## Monolithic 3D

Ref.: Intel, 2021 IEDM

Layers co-processed simultaneously

- High aspect considerations (etching, filling,...)

- Potentially self-aligned layers

- Layer re-use/dual role

- Combination with bottom up techniques and layer transfer

- Compatible with multiple applications on same tile

## Summary & Conclusions

- Exciting time to develop technologies that bring 3D integration to ultimate scaling limit

- Challenges abound:

- Efficiently designing complex systems with novel functionalities

- Utilizing new materials to enable multiple applications on same tile or in system

- Utilizing novel techniques to enable high aspect ratio and inter-layer tight pitch

- JUMP 2.0 Theme 6 provides excellent opportunity for impactful research in this space

#