## STRUCTURED ANALOG CMOS DESIGN Based on the Device Inversion Level

**Danica Stefanovic**

- $\rightarrow$  No general analog design methodology.

- $\rightarrow$  No general **design approach**.

- $\rightarrow$  CAD tools for simulation, layout generation and post layout verification.

- $\rightarrow$  Large number of **analog design automation** tools,

- but only in the university domain!

- $\rightarrow$  Few analog design automation tools in industry.

- $\rightarrow$  Deal with increasing circuit **complexity** ?

- $\rightarrow$  Deal with very **demanding specifications** sets ?

- $\rightarrow$  Estimate **technology limits** ?

- $\rightarrow$  Bridge the gap between **hand-calculations** and simulations ?

- $\rightarrow$  Use the **device physics understanding** for analog design ?

- $\rightarrow$  Optimize analog circuits and find the best trade-offs ?

- $\rightarrow$  Develop CAD tools for **analog design assistance** ?

- → Encapsulate analog design knowledge ?

#### Analog design approach

$\rightarrow$  Structured analog design

$\rightarrow$  Procedural design

**Transistor level design**

→ the device inversion level as a key variable

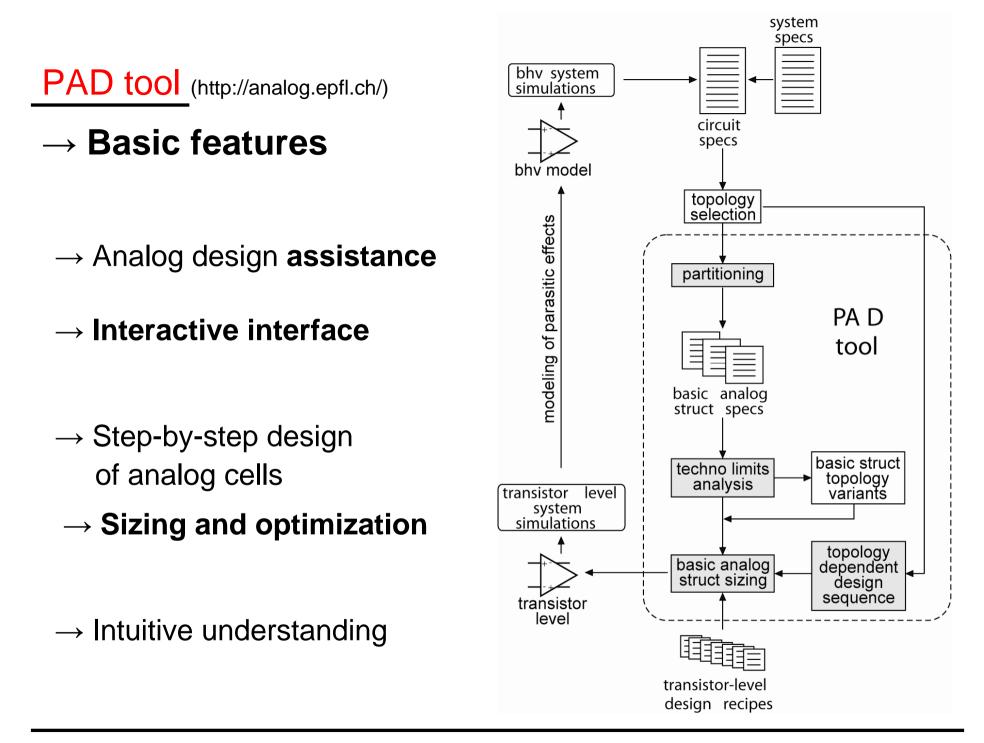

CAD tool for analog design assistance

$\rightarrow$  PAD tool

$\rightarrow$  BSIM2EKV converter

## **BASIC CONCEPT**

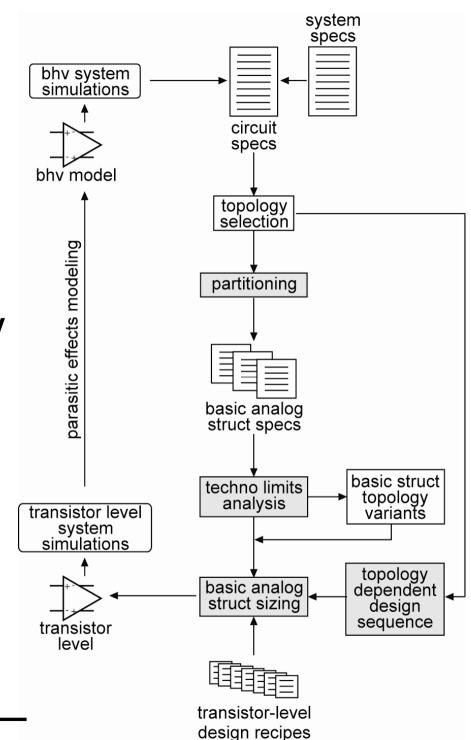

- → Circuit-level specifications from system-level simulations

- $\rightarrow$  Basic analog structures library

- $\rightarrow$  Procedural design scenarios

- → Sizing and optimization on the level of basic analog structures

- $\rightarrow$  Topology variants

### STRUCTURED ANALOG DESIGN

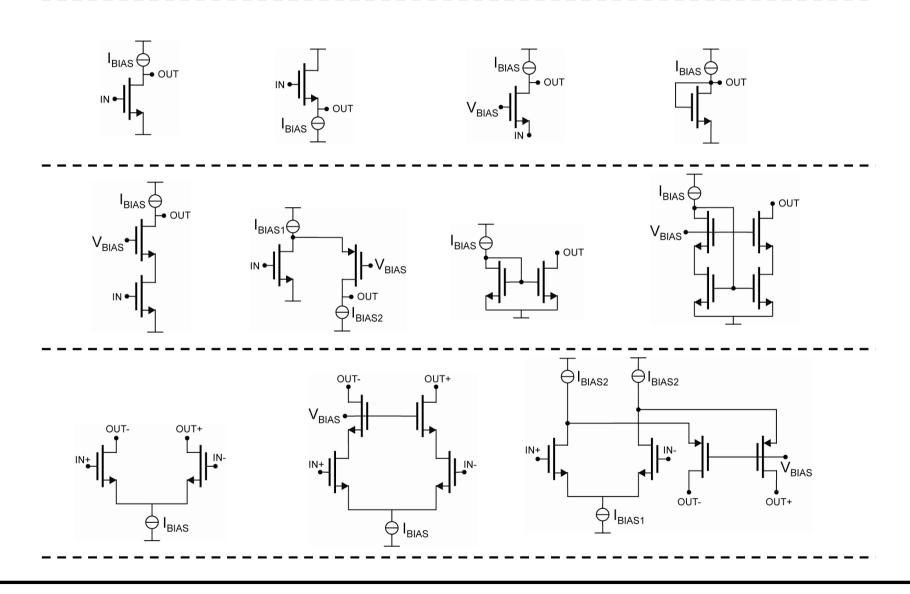

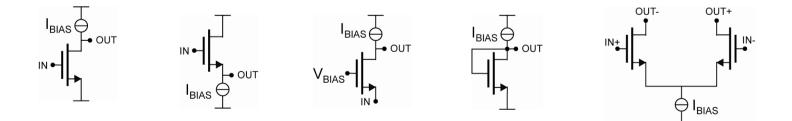

## BASIC ANALOG STRUCTURES LIBRARY

## BASIC ANALOG STRUCTURES LIBRARY

## $\rightarrow$ Classification

#### **Transconductance structures:**

CS, CD, CG, cascode, differential pair

#### Load structures:

simple and cascode current mirror

#### **Bias structures:**

simple and cascode current mirror

## BASIC ANALOG STRUCTURES LIBRARY

#### $\rightarrow$ Design parameters

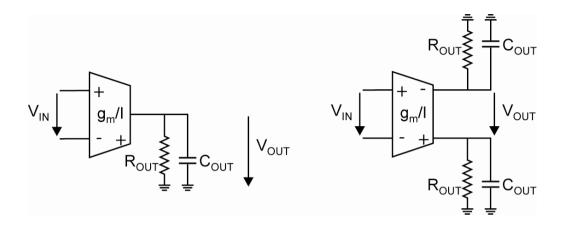

#### **Transconductance structures:**

transconductance, input range, noise, voltage mismatch (offset) output resistance, output swing, parasitic capacitances

#### Load structures:

output resistance, saturation voltage, parasitic capacitances, noise, current mismatch

#### **Bias structure:**

output resistance, saturation voltage, current mismatch

### **BEHAVIORAL MODEL OF ANALOG CELL**

#### **TRANSISTOR DESIGN CASES**

### $\rightarrow$ Good MOS model

- $\rightarrow$  Based on physical behavior

- $\rightarrow$  Covers all significant physical effects

- $\rightarrow$  Global, compact, accurate

- $\rightarrow$  Covers all geometry ranges

- $\rightarrow$  Correct I-V characteristics, correct current derivatives

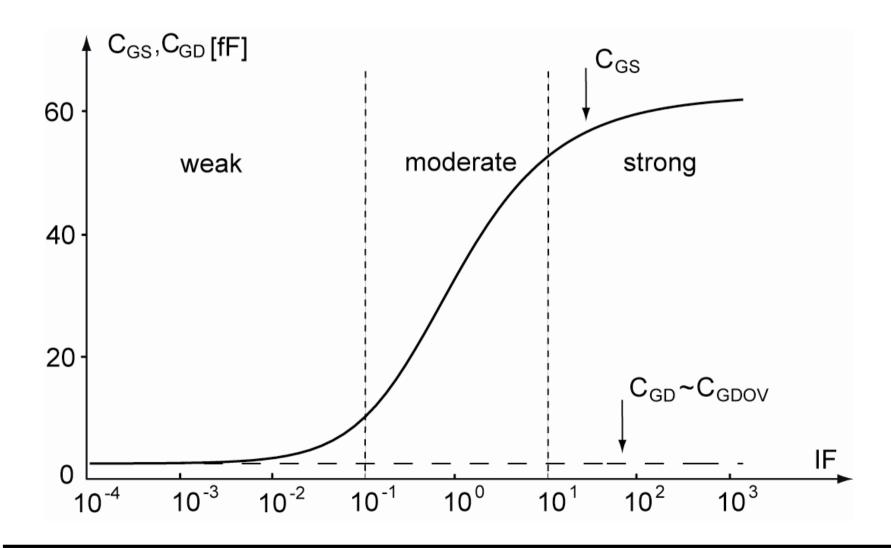

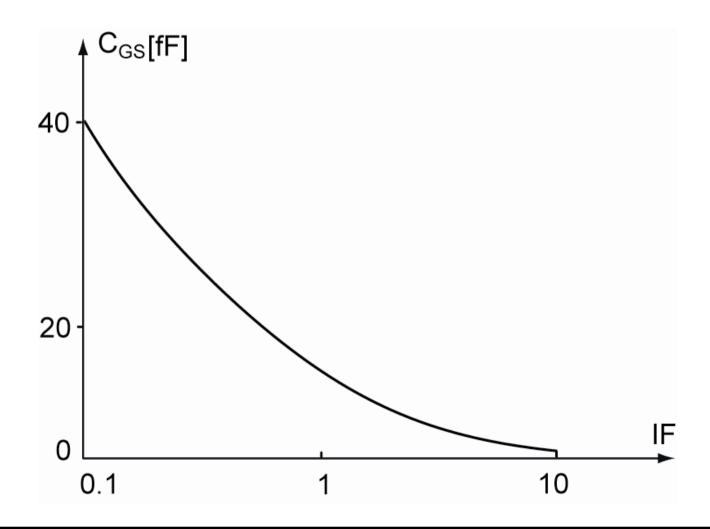

- $\rightarrow$  Accurate modeling of the intrinsic capacitances

- $\rightarrow$  Simple and fast extraction procedure

- $\rightarrow$  Easy implementation, no convergence problems

## $\rightarrow$ MOS model dedicated to analog design

- → Small number of parameters with physical meaning

- $\rightarrow$  Hierarchical structure

- $\rightarrow$  Model equations **approximations** without a great loss of accuracy

- $\rightarrow$  **Continuous expressions** of current derivatives

## $\rightarrow \text{EKV MOS model} \rightarrow \text{its basic concept makes it possible to develop} \\ \text{(http://legwww.epfl.ch/ekv/)} \quad a \text{ design approach at the transistor level} \\ \end{array}$

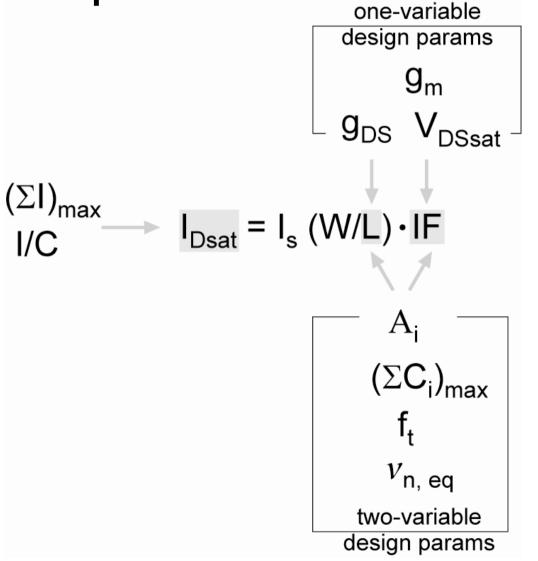

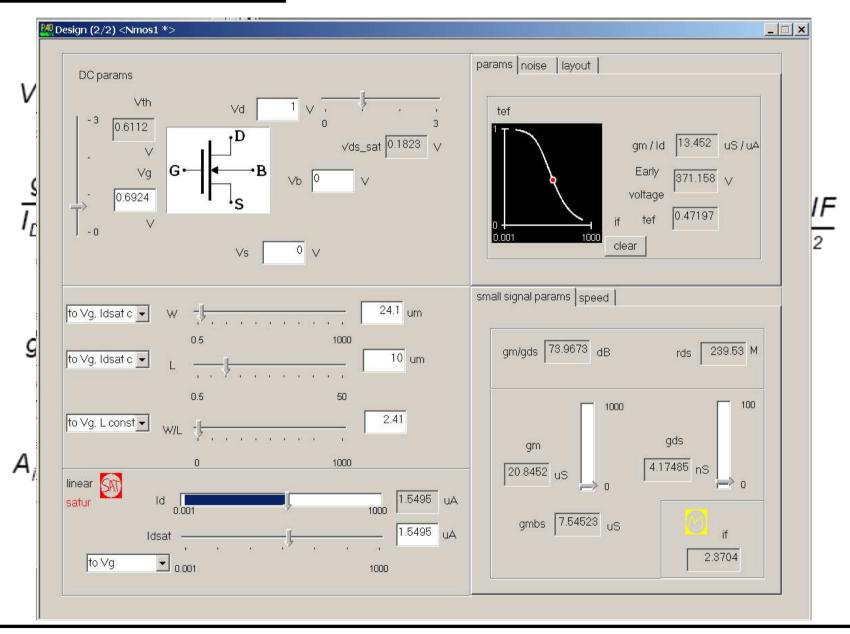

#### $\rightarrow$ Design parameters vs. design variables

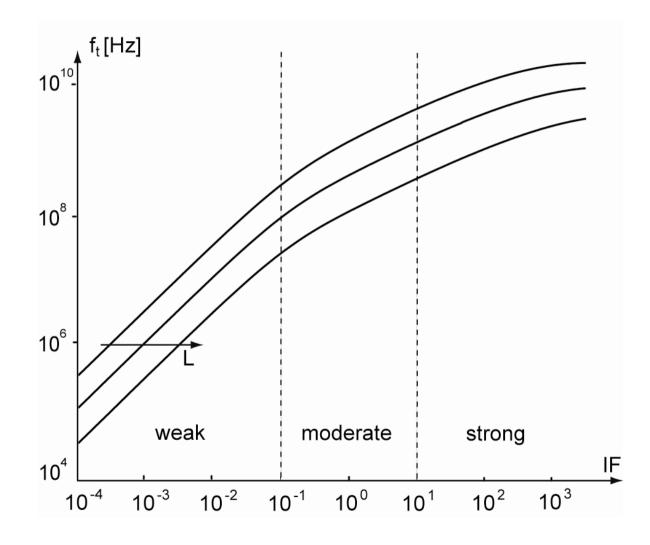

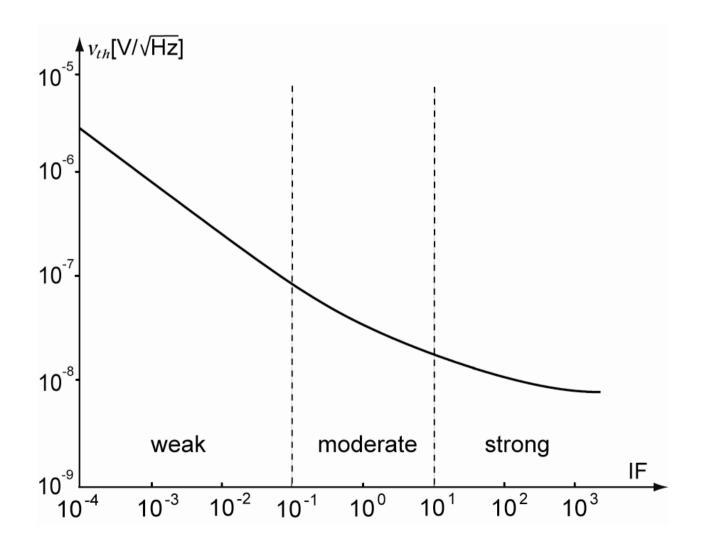

saturation voltage  $V_{DSsat}$ transconductance  $g_m$ output conductance  $g_{DS}$ parasitic capacitances intrinsic gain  $A_i$ transition frequency  $f_t$ equivalent noise saturation current *I*<sub>Dsat</sub> inversion factor *IF* transistor width *W* transistor length *L* ratio *W/L* area *WL*

#### $\rightarrow$ Design variables

$$I_{pol} = I_{Dsat} = 2nKP\left(\frac{W}{L}\right)V_t^2 \cdot IF$$

$$\rightarrow \frac{W}{L} = \frac{I_{Dsat}}{2nKPV_t^2 \cdot IF}$$

$\rightarrow W = \left(\frac{W}{L}\right) \cdot L = \frac{I_{Dsat}}{2nKPV_t^2 \cdot IF} \cdot L$

$$\rightarrow WL = \left(\frac{W}{L}\right) \cdot L^2 = \frac{I_{Dsat}}{2nKPV_t^2 \cdot IF} \cdot L^2$$

inversion factor IF

#### transistor length L

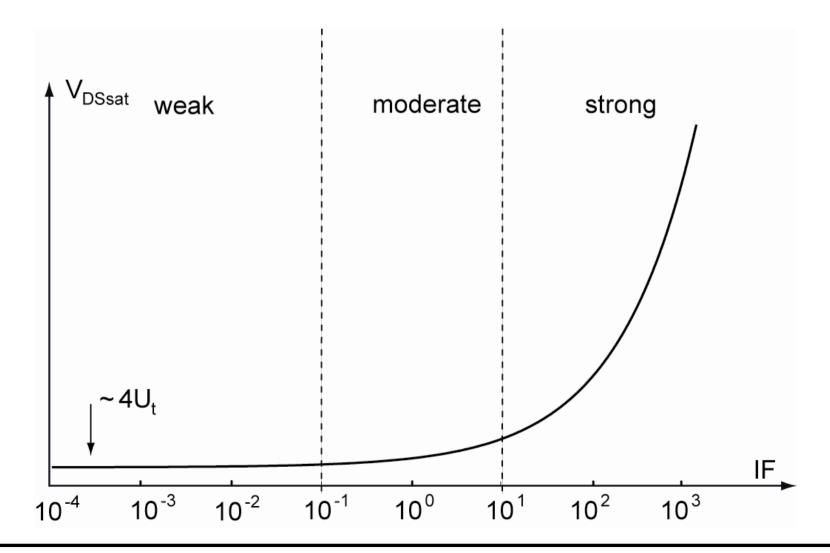

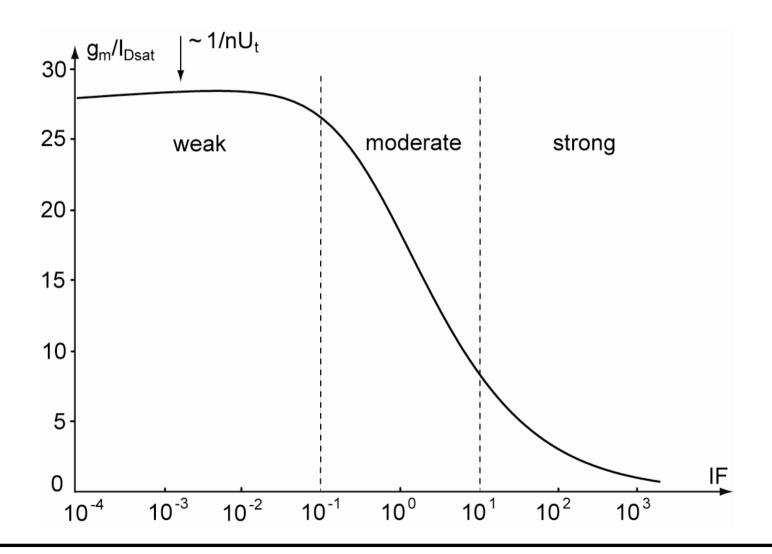

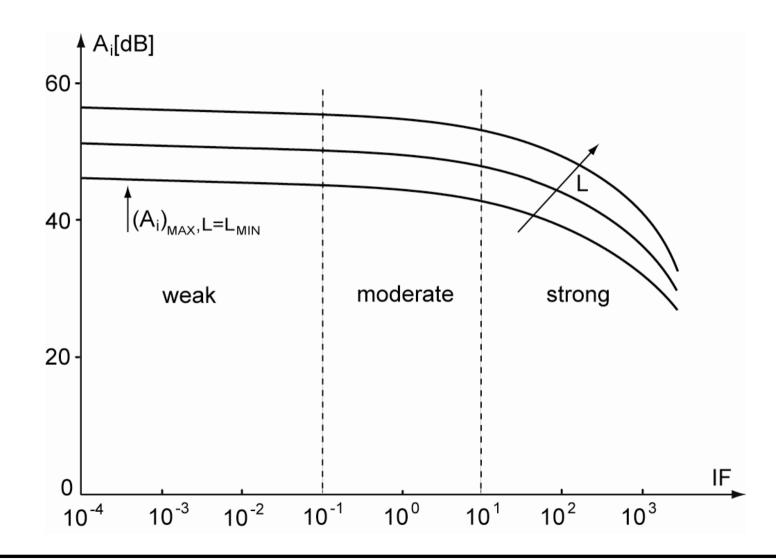

### $\rightarrow$ Design parameters

$$V_{DSsat} = V_t \cdot (2\sqrt{IF} + 4)$$

$$\frac{g_m}{I_{Dsat}} = \frac{1}{nV_t} \cdot \frac{1}{\frac{1}{2} + \sqrt{IF} + \frac{1}{4}}$$

$$g_{DS} = \frac{I_{Dsat}}{L \cdot V_a}$$

$$A_i = \left(\frac{g_m}{I_{Dsat}}\right) \cdot L \cdot V_a$$

$$(\Sigma C_i)_{MAX} = C_{ox} \cdot \frac{I_{Dsat}}{2n(\Sigma C_i)_{MAX}} = \left(\frac{g_m}{I_{Dsat}}\right) \cdot \frac{nKPV_t^2 \cdot IF}{\pi C_{ox} \cdot L^2}$$

$$v_{n,th}^2 = \frac{4KT \cdot n \cdot \frac{1}{1 + IF} \cdot \left(\frac{1}{2} + \frac{2}{3}IF\right)}{\left(\frac{g_m}{I_{Dsat}}\right) \cdot I_{Dsat}}$$

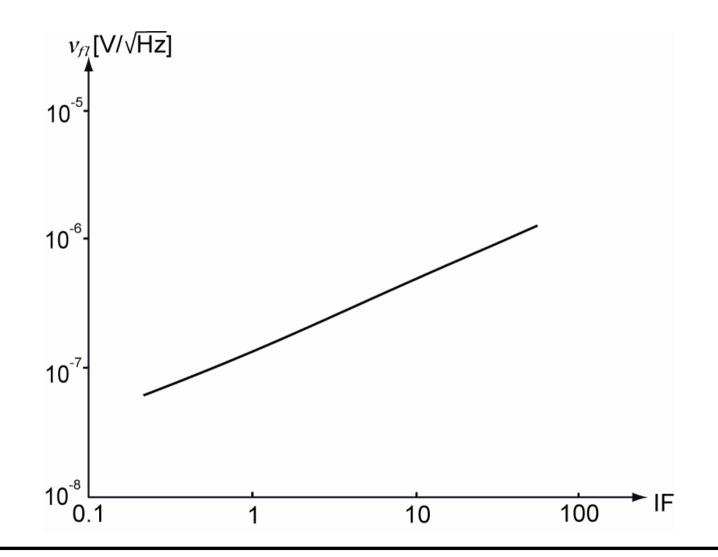

$$v_{n,th}^2 = \frac{2nKPV_t^2 \cdot KF \cdot IF}{L^2 C_{ox}f^{AF} \cdot I_{Dsat}}$$

$\rightarrow$  Design cases :

output conductance + saturation voltage output conductance + transconductance saturation voltage + gain gain + sum of par. caps transconductance + sum of par. caps transconductance + equiv. noise gain + transition frequency transconductance + voltage mismatch saturation voltage + current mismatch

#### $\rightarrow$ Design recipes

## **DESIGN CHARTS**

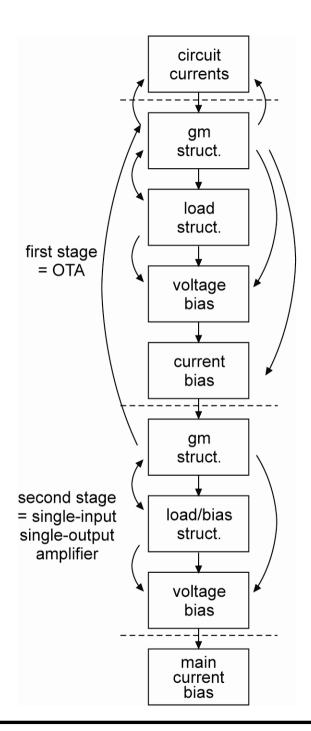

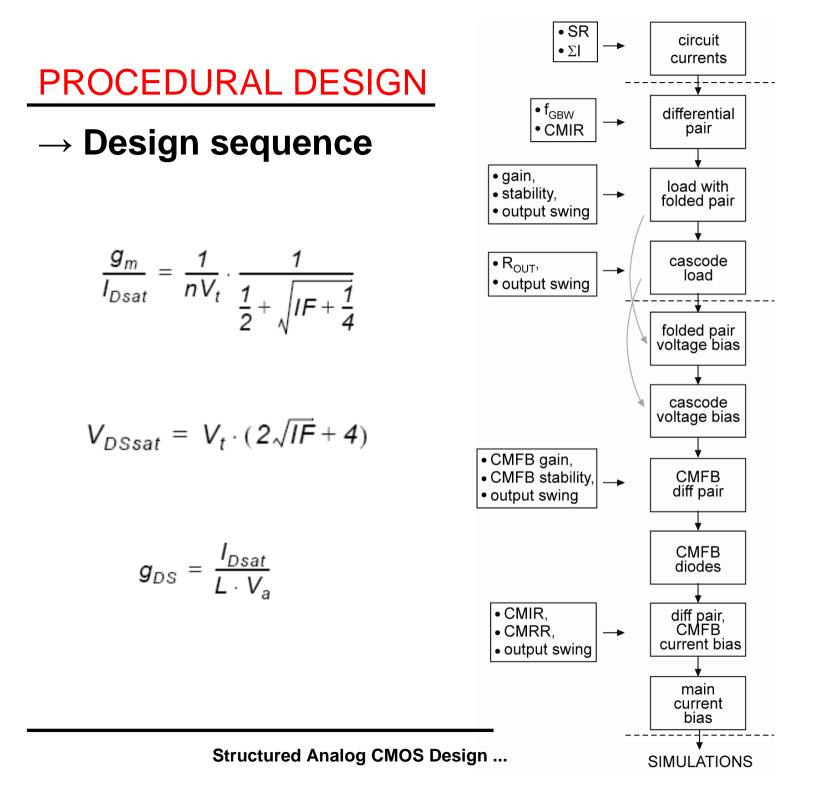

## **PROCEDURAL DESIGN**

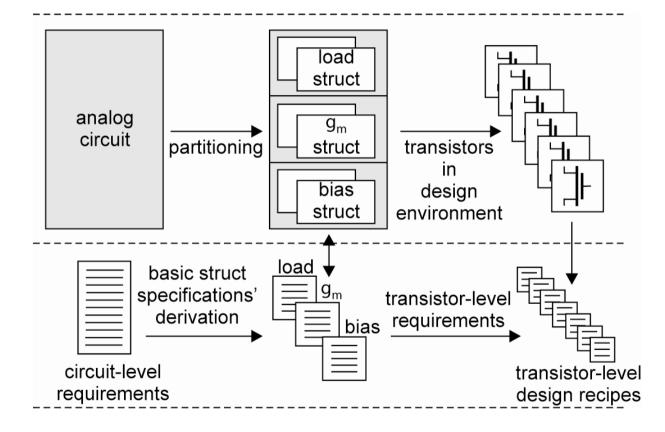

- → Circuit partitioning

- → Basic analog structures specifications derivation

- operational transconductance single-input amplifier single-output amplifier load voltage struct. load/ bias curr bias voltage struct. gm bias struct. gm struct. current bias + / operational amplifier

- → Step-by-step design sequence in transconductance-load-bias structure order

## **PROCEDURAL DESIGN**

- $\rightarrow$  Circuit partitioning

- → Basic analog structures specifications derivation

- → Step-by-step design sequence in transconductance-load-bias structure order

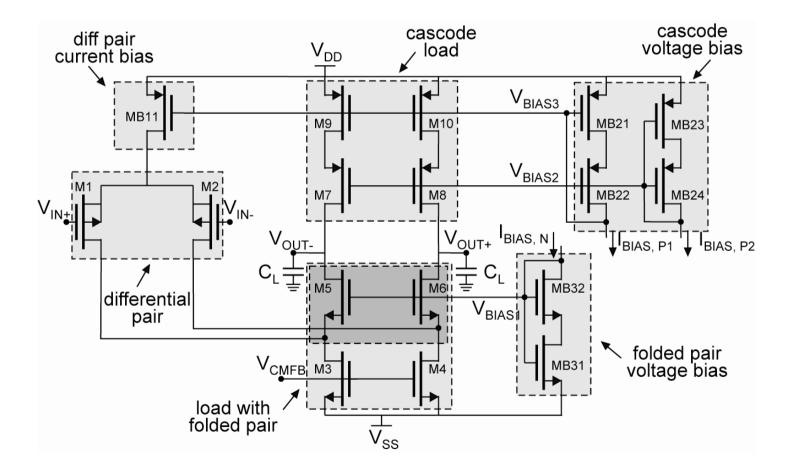

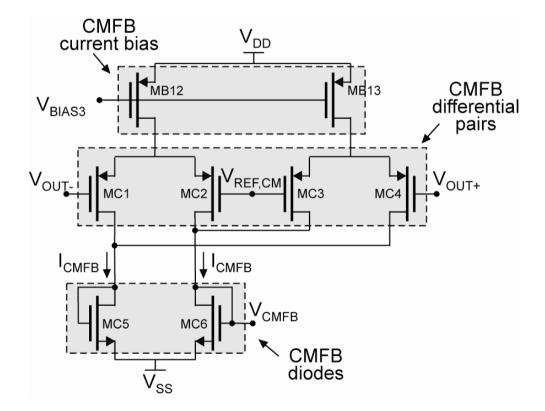

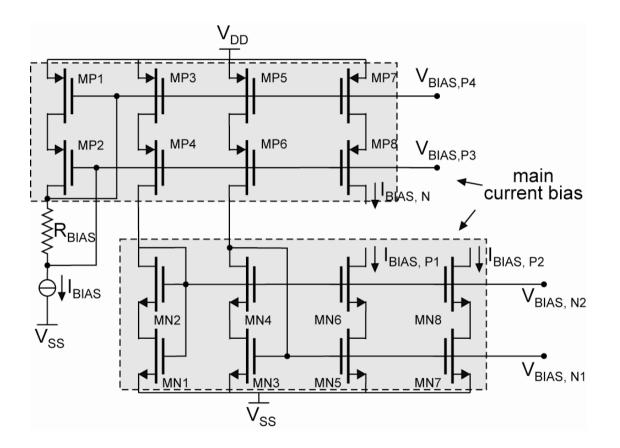

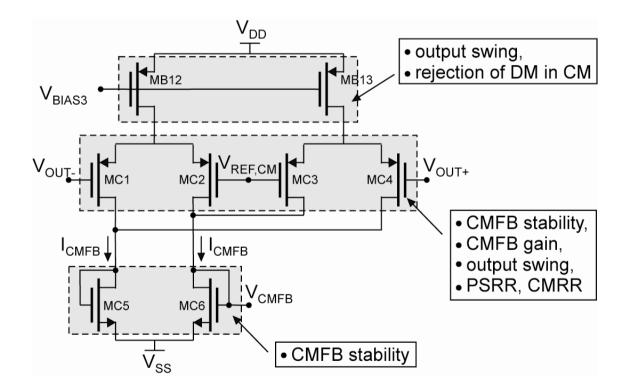

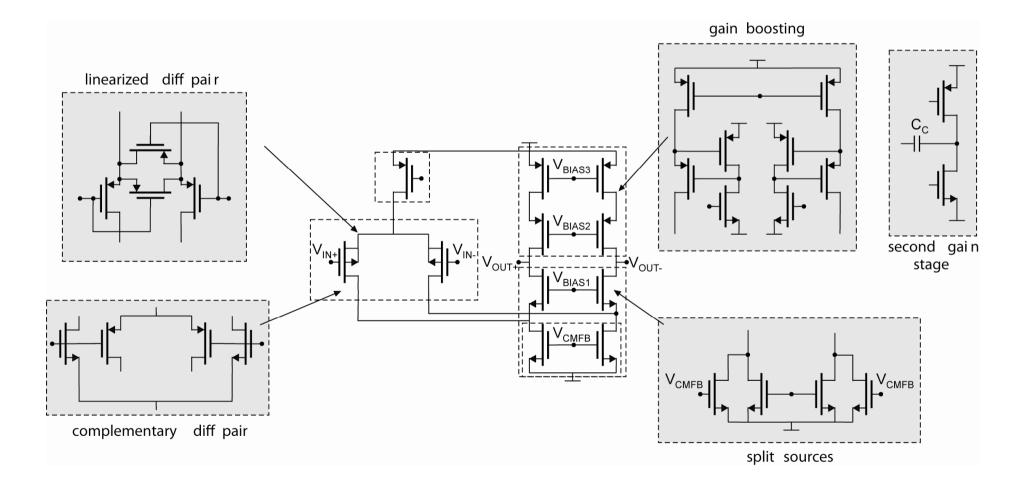

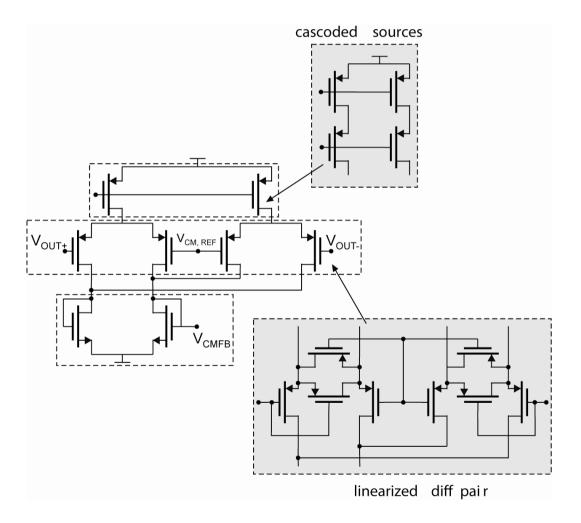

## $\label{eq:circuit} \rightarrow \textit{Circuit partitioning} \rightarrow \textit{example: fully-differential} \\ \textit{folded cascode OTA}$

## $\label{eq:circuit} \rightarrow \textit{Circuit partitioning} \rightarrow \textit{example: fully-differential} \\ \textit{folded cascode OTA}$

## $\rightarrow Circuit \ partitioning \rightarrow example: \ fully-differential folded \ cascode \ OTA$

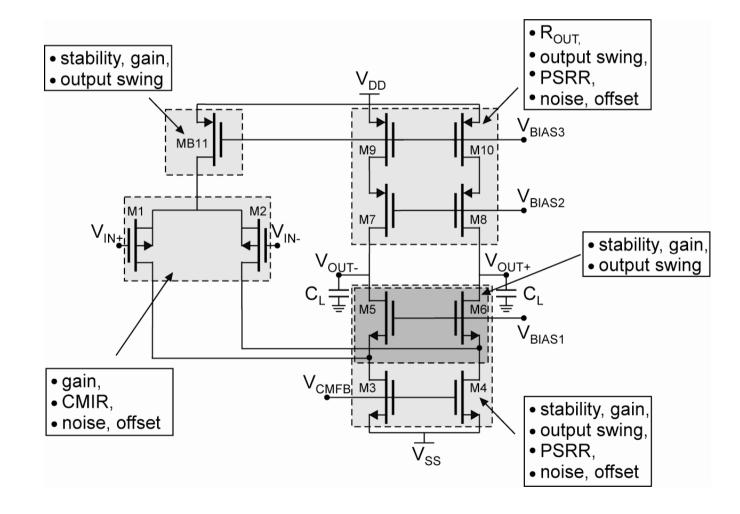

# $\rightarrow \textit{Specifications derivation} \rightarrow \textit{example: fully-differential} \\ \textit{folded cascode OTA}$

# $\rightarrow \textit{Specifications derivation} \rightarrow \textit{example: fully-differential} \\ \textit{folded cascode OTA}$

simulate

and

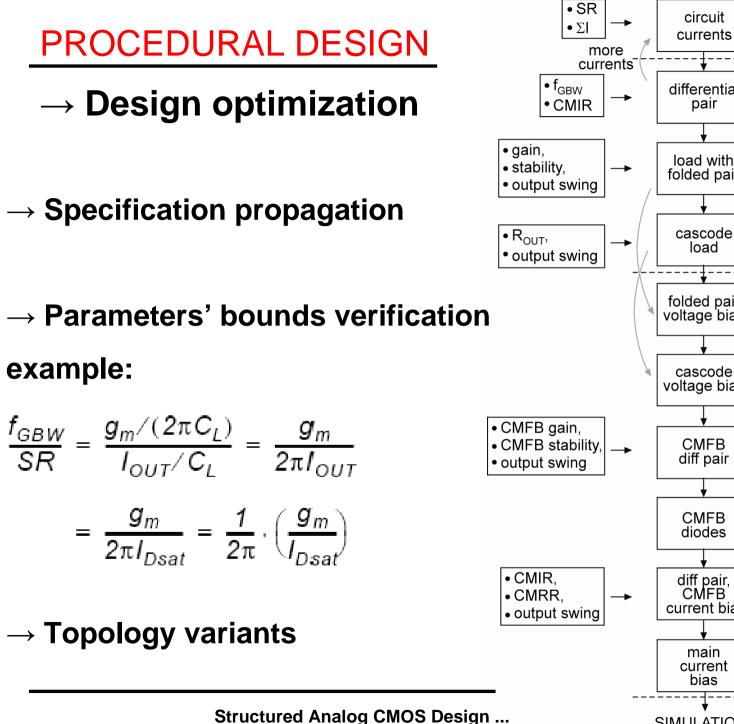

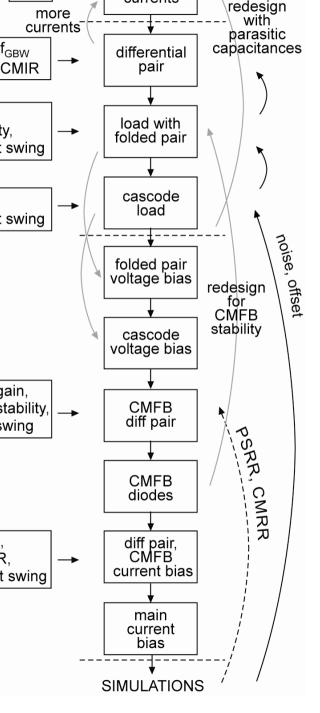

### PROCEDURAL DESIGN

## $\rightarrow$ **Topology variants** $\rightarrow$ example: fully-differential folded cascode OTA

## $\rightarrow$ **Topology variants** $\rightarrow$ example: fully-differential folded cascode OTA

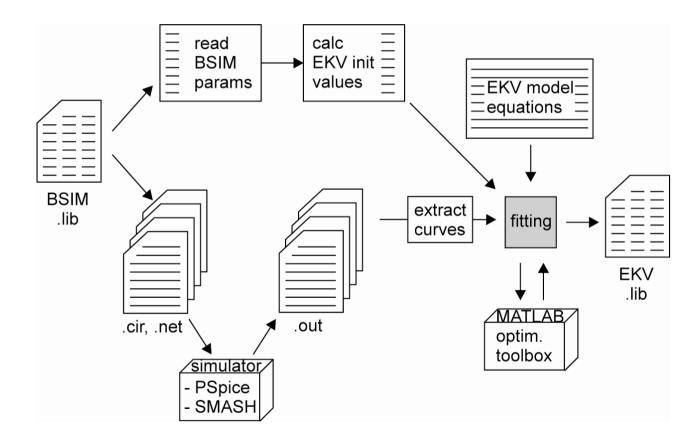

BSIM2EKV tool (http://analog.epfl.ch/)

#### $\rightarrow$ Conversion concept

$\rightarrow$  Simplify complex analog design problems by partitioning of analog cells into basic analog structures

$\rightarrow$  Size each basic analog structure in the environment imposed by the circuit

$\rightarrow$  Look for the design trade-offs on both circuit level and transistor level

$\rightarrow$  Use the inversion level as a key design variable

## STRUCTURED ANALOG CMOS DESIGN Based on the Device Inversion Level

#### **Danica Stefanovic**

danica.stefanovic@gmail.com