Sunday 3/9/14 8:30pm Kiva Ballroom

### PACKAGING AND INTERCONNECT TRENDS: QFN, WLCSP, FINE PITCH AND MODULAR/3D SOLUTIONS

by

Brandon Prior Senior Consultant

**Prismark Partners**

**B** randon Prior, Senior Consultant at Prismark Partners, returns to the BiTS Workshop with an overview of the global packaging market, focusing on emerging and fast growth package solutions. Be prepared for a glimpse of some cool product teardowns he'll use to illustrate his talk.

#### ABSTRACT

**T** his overview of the global packaging market will focus on emerging and fast growth package solutions. In his presentation Mr. Prior will review where package miniaturization and modularization has taken us so far, and where it will lead in the next 5 years. Teardowns of high density boards and packages will be used to illustrate key points.

#### **COPYRIGHT NOTICE**

The paper(s) in this publication comprise the Proceedings of the 2014 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2014 BiTS Workshop. This version of the papers may differ from the version that was distributed in hardcopy & softcopy form at the 2014 BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by BiTS Workshop, LLC or the workshop's sponsors.

There is NO copyright protection claimed on the presentation content by BiTS Workshop, LLC. (Occasionally a Tutorial and/or TechTalk may be copyrighted by the author). However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop, LLC. All rights reserved.

# PACKAGE AND INTERCONNECT TRENDS

### Brandon Prior Prismark Partners LLC

2014 BiTS Workshop March 9 - 12, 2014

2014 BiTS Workshop ~ March 9 - 12, 2014

3

2

2014 BiTS Workshop ~ March 9 - 12, 2014

### POLAR LOOP ACTIVITY WRISTBAND

- Use of conventional single chip packages and rigid flex PCB

- Packages are thin (<0.7mm), but no stacking or PoP

- Low cost is critical in this segment

- Performance and function not comparable to smart phone or tablet

BiTS 2014

PACKAGE AND INTERCONNECT TRENDS - PRISMARK

6

2014 BiTS Workshop ~ March 9 - 12, 2014

| Package Type<br>(Bn Units)                     | 2011  | % of<br>Total | 2013  | 2018  | % of<br>Total | CAAGR<br>2013-2018 |

|------------------------------------------------|-------|---------------|-------|-------|---------------|--------------------|

| Traditional Leadframe<br>(SO, TSOP, QFP)       | 101   | 54%           | 102   | 108   | 40%           | 1.2%               |

| QFN                                            | 21    | 11%           | 27    | 56    | 21%           | 16%                |

| Wire Bond CSP<br>(includes stacked & BOC/DRAM) | 28    | 15%           | 27    | 29    | 11%           | 0.9%               |

| Wire Bond BGA<br>(> 19mm package size)         | 1.1   | 0.6%          | 0.9   | 0.8   | 0.3%          | -2.3%              |

| Wire Bond Bare Die<br>(COB)                    | 11    | 6%            | 12    | 16    | 6%            | 5.3%               |

| Flip Chip CSP<br>(includes DRAM)               | 1.5   | 0.8%          | 4.7   | 14    | 5%            | 25%                |

| Flip Chip BGA/PGA/LGA<br>(19mm Package Size)   | 1.1   | 0.6%          | 1.1   | 1.1   | 0.4%          | 0%                 |

| Wafer CSP                                      | 15    | 8%            | 19    | 35    | 13%           | 13%                |

| COF/COG for Display Drivers                    | 7.9   | 4%            | 8.6   | 11    | 4%            | 4.1%               |

| TOTAL                                          | 186.7 | 100%          | 202.4 | 269.8 | 100%          | 5.9%               |

#### IC PACKAGE LINIT GROWTH

2014

**BiTS 2014**

PACKAGE AND INTERCONNECT TRENDS - PRISMARK

### PACKAGE SIZE REDUCTION AND SYSTEM IN PACKAGE (SiP)

- System Level Size Reduction

- Mobile Consumer Electronics (Notebooks, Media Tablets, Smartphones, etc.) are representing an ever increasing portion of electronics value, and have been driving package roadmaps for the last fifteen years

- Although system size is no longer decreasing dramatically, the area and volume allocated to PCB assembly is getting squeezed out in favor of larger battery, display, and overall thinner systems

- Package Size Reduction

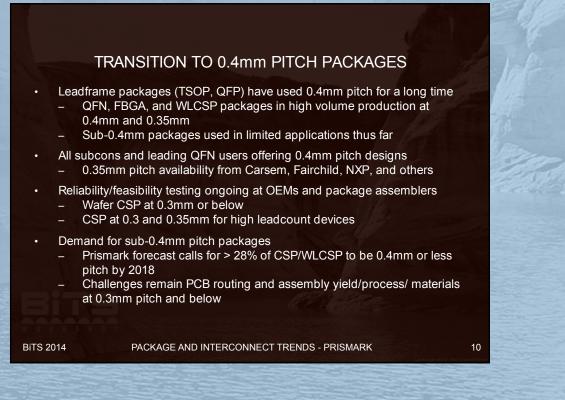

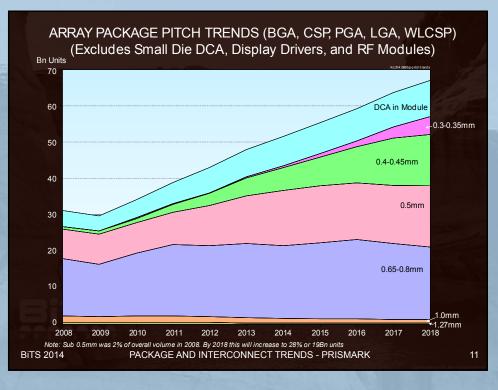

- − Array Packages and Pitch reduction  $(0.5 \rightarrow 0.4 \rightarrow 0.3 \rightarrow 0.25 \text{mm})$

- Wafer Level CSP the "Package-less" Package

- QFN "leadless" packages using low cost leadframe and wirebond technology

- SiP Approaches

- Adoption of stacked die and package stacking was first phase of 3D

- 3D TSV and Silicon Interposers will be the "package" challenge over the coming decade

**BiTS 2014**

PACKAGE AND INTERCONNECT TRENDS - PRISMARK

8

9

### QFN VS. WLCSP

- Both QFN and WLCSP package solutions have taken share from conventional SO packages both offer

- Smaller size

- Lower cost

- Better electrical performance

- · QFN was initially successful across consumer/portable devices

- Today, often displaced by WLCSP, modules, or move to CSP

- QFN ramp now driven across all sectors as inspection/test concerns are

- solved

- Multi-row QFN remains niche, but gaining traction

- WLCSP limitations remain

- Die size and I/O limited

- Fan out may open for more options

- QFN and WLCSP are often preferred packages by device suppliers due to low cost. Decision to use one over another is driven by cost and end-customer preference.

WLCSP is more cost effective for smaller die size and high I/O density. However, may be pitch limited

- QFN looks more like standard package, and therefore has more traction as of 2013.

BiTS 2014

PACKAGE AND INTERCONNECT TRENDS - PRISMARK

2014 BiTS Workshop ~ March 9 - 12, 2014

2014 BiTS Workshop ~ March 9 - 12, 2014

1013.6/193mv

7

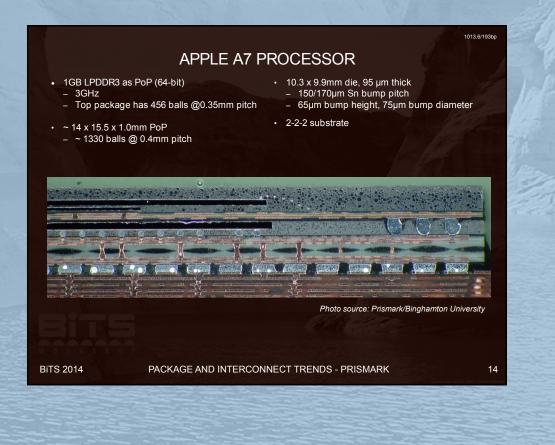

- 15 x 15mm PoP, 1.45mm high

- Bottom Package 1,005 balls, staggered rows, 0.6mm pitch

- Processor flip chip die, 100µm thick, 11 x 11mm About 3,600 bumps, 150µm pitch, 50µm height

- With PCB embedded capacitors

- Top Package 216 balls in two peripheral rows, 0.5mm pitch

- Four memory die, wire bonded, 40µm thick, 9 x ?mm

- Die attach film between die

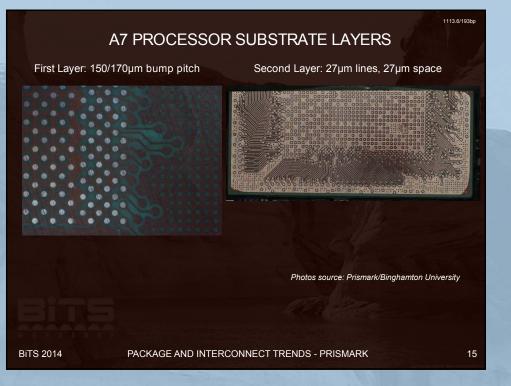

Photos source: Prismark/Binghamton Universit **BiTS 2014** PACKAGE AND INTERCONNECT TRENDS - PRISMARK 13

2014 BiTS Workshop ~ March 9 - 12, 2014

1213.6/193bp

#### PHONE AND TABLET APPLICATION PROCESSOR ROADMAP

|                    | 2014 201       |                              | 2016               | 2016               |  |

|--------------------|----------------|------------------------------|--------------------|--------------------|--|

| Product name       | High End       | Low cost                     | High End           | Low Cost           |  |

| Process node       | 20/22          | 28/32                        | 14/16              | 20/22 (some 14/16) |  |

| Die Size (mm)      | 8-11           | 7-9                          | 8-12 (< 10 target) | 7-10               |  |

| Die thickness (µm) | 75-100         | 100-150                      | 65-80              | 75-200             |  |

| Total Bumps (Est.) | 3500           | 700-1500<br>(some wire bond) | 4000               | 1000-2000          |  |

| Bump Pitch (µm)    | 130-150        | 180                          | 110-130            | 150/180            |  |

| Package Size       | 11-17          | 10-18                        | 12-16              | 12-14              |  |

| Package I/O        | 950-1400       | 700                          | 1100-1500          | 700-900            |  |

| Package Pitch (mm) | 0.4            | 0.5-0.65                     | 0.35               | 0.4-0.65           |  |

| Top PoP I/O        | ~ 300 (456 A7) | 216                          | 300-500            | 250+               |  |

| Top PoP Pitch (mm) | 0.4 / 0.35     | 0.5                          | 0.3/0.35           | 0.4                |  |

BiTS 2014

PACKAGE AND INTERCONNECT TRENDS - PRISMARK

17

ıg

| SIP/MCP FORECAST                                    |      |                  |                                                                              |  |  |  |  |

|-----------------------------------------------------|------|------------------|------------------------------------------------------------------------------|--|--|--|--|

| Product/Package Type<br>Volume (Bn Units)           | 2013 | 2018<br>Forecast | Leading Suppliers/Players                                                    |  |  |  |  |

| Stacked Die In Package and<br>Memory Card           | 8    | 11               | ASE, SPIL, Amkor, STATS ChipPAC, Samsun<br>Micron, SKHynix, Toshiba, SanDisk |  |  |  |  |

| Stacked Package on Package<br>– Bottom Package Only | 0.8  | 1.3              | Amkor, STATS ChipPAC, ASE, SPIL, Samsun<br>Apple, Qualcomm, Sony, Panasonic  |  |  |  |  |

| PA Centric RF Module                                | 4.3  | 6.3              | RFMD, Skyworks, Anadigics, Renesas,<br>TriQuint, Avago                       |  |  |  |  |

| Connectivity Module<br>(Bluetooth/WLAN)             | 0.4  | 0.5              | Murata, Taiyo Yuden, ACSIP, ALPS                                             |  |  |  |  |

| Graphics/CPU or ASIC MCP                            | 0.2  | 0.2              | Intel, IBM, Fujitsu, Xlinx, Altera                                           |  |  |  |  |

| Leadframe Module<br>(Power/Other)                   | 3    | 5                | NXP, STMicro, TI, Freescale, Toshiba,<br>Infineon, Renesas, IR, ON Semi      |  |  |  |  |

| MEMS and Controller                                 | 5    | 8                | ST, Analog, Bosch, Freescale, Knowles,<br>SKHynix, InvenSense Denso          |  |  |  |  |

| TOTAL                                               | 21.7 | 32.3             |                                                                              |  |  |  |  |

BiTS 2014

PACKAGE AND INTERCONNECT TRENDS - PRISMARK

18

2014 BiTS Workshop ~ March 9 - 12, 2014

### CONCLUSIONS

- Package size reduction is ongoing, but pitch limitations draw a logical path towards modular and 3D approaches

- A few clear trends are enabling miniaturization:

- Fine Pitch Array Packages (0.5 → 0.4 → 0.35 → 0.3/0.25mm)

- Stacked Die (Memory) and Package Stacks (Logic/Memory)

- Wafer Level CSP

- Reduced Z- height packages (0.3 to 0.6mm)

- 3D TSV and Silicon Interposer approaches are still in development, with high volumes products expected in next 3-5 years

- Challenges emerge for die level test at pitches <50μm

- Test before die to die or die to wafer assembly often required

BiTS 2014

PACKAGE AND INTERCONNECT TRENDS - PRISMARK