# INDIAN RAILWAYS INSTITUTE OF SIGNAL ENGINEERING & TELECOMMUNICATIONS SECUNDERABAD - 500 017

# **T-13D**

# SYNCHRONOUS DIGITAL HIERARCHY (SDH)

**Issued in October 2008**

# **T-13D**

# SYNCHRONOUS DIGITAL HIERARCHY (SDH)

# **CONTENTS**

| S.No | Chapter                                                   | Page No |

|------|-----------------------------------------------------------|---------|

| 1    | Synchronous Digital Hierarchy (SDH)                       | 1       |

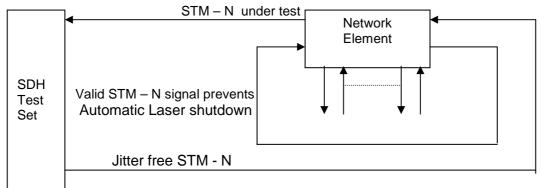

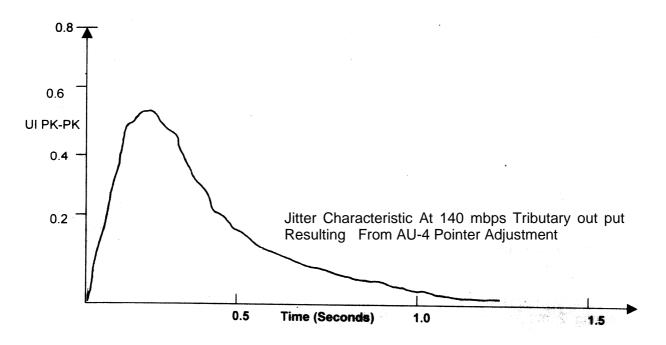

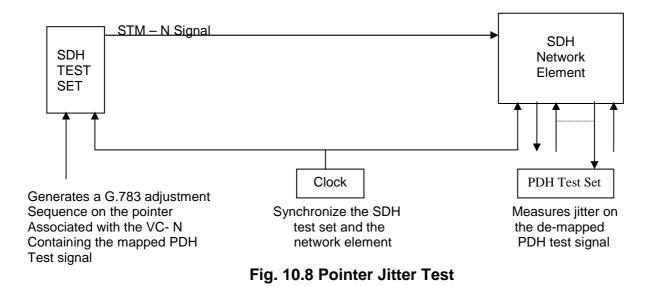

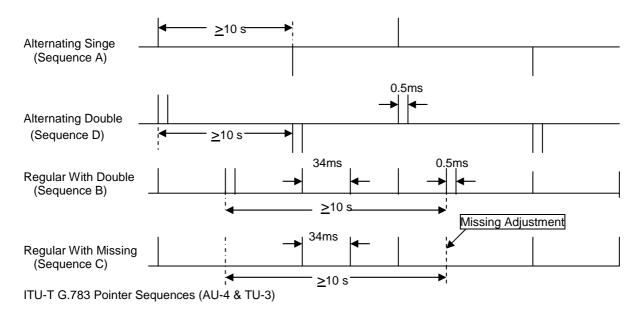

| 2    | SDH Multiplexing Structure                                | 12      |

| 3    | SDH Synchronous Frame Structure                           | 18      |

| 4    | Pointers                                                  | 32      |

| 5    | Network Topologoes                                        | 50      |

| 6    | Availability & Survivability                              | 53      |

| 7    | Network Management                                        | 63      |

| 8    | Synchronization                                           | 68      |

| 9    | ITU (T)'s SDH Recommendations                             | 77      |

| 10   | Jitter and Wander in SDH Systems & Testing of SDH Network | 84      |

Prepared by P.Hari Kumar, APT - 2 Approved by S. K. Biswas, Sr. Professor - Tele **DTP** and Drawings K.Srinivas, JE II(D) September 2003 Date of Issue **Edition No** 01 First re-print October 2008 No. of Pages 102 No.of Sheets 51

# © IRISET

"This is the Intellectual property for exclusive use of Indian Railways. No part of this publication may be stored in a retrieval system, transmitted or reproduced in any way, including but not limited to photo copy, photograph, magnetic, optical or other record without the prior agreement and written permission of IRISET, Secunderabad, India"

http://www.iriset.ac.in

# Chapter 1

# **Synchronous Digital Hierarchy (SDH)**

**Objectives:** By going through this chapter, the trainee must be in a position to understand

- 1. The objectives of SDH.

- 2. The relative advantages of SDH when compared with PDH.

- 3. Other features of SDH hierarchy.

### 1.1 Introduction

Telecommunication is the central nervous system of modern society. No other technology as digital communication has had such a worldwide impact of putting people in touch around the world through voice, video, data etc.

The goal of worldwide telecommunication is free exchange of information throughout the global community. North America, Europe, Japan and India all have different communication standards and hierarchies. Digital networks of these nations cannot be freely connected. The technology of these nations competes with each other and remains incompatible. This not only obstructs telecommunications from one country to the other but also slows down the development.

On a little closer look at the long distance network, it is evident that the present system of independent point to point transmission needs adequate network management capabilities and on line control of network configuration, so that the transport layer is strengthened to match the future requirements of the customers as well as operators. It is particularly true when the multimedia is all set to offer the mega band width services like video on demand. Multimedia service is characterized as integrated computer controlled generation, processing, display, storage, and transmission of text, data, graphics, voice, sound and images including moving picture etc. ATM is all set to offer bandwidth on demand. Obviously the telecom services sector is going to thrive, there by leading to a requirement of a lot more capability on the part of transport to handle variable and much larger bandwidths with better rates and higher availability. The solution, perhaps, lies in the concept of Synchronous Digital Hierarchy (SDH), which can be termed as transport backbone of the broadband era. The Network Node Interface (NNI) operating in Synchronous Digital Hierarchy (SDH) recommended by ITU (T) / CCIR offers a clear solution and sets an international standard for high speed digital transmission.

One of the most important aspects of SDH as a standard for international network is that wide band signals can be transported with in a Plesiochronous (10<sup>-11</sup> frequency offset) environment

without any loss of data, just like in PDH, with benefits of a Synchronous Frame Structure that simplifies drop and insert and cross connect functions. Note that SDH does not deal with the multiplexing of individual 64 kbps signals. SDH only defines mapping for byte structured first level PDH, which does not alter the characteristics of 64 kbps PDH multiplexing method.

## 1.2 Evolution

Current public telecommunication networks are based on the long established ITU (T) Plesiochronous Digital Hierarchy (PDH) of transmission which is not well suited to support the advanced signal processing and control techniques now possible and increasingly demanded by the telecom.

The SDH is designed to overcome the limitations of PDH.

ITU (T) adopted SDH in 1988. The original version was known as SONET — Synchronous Optical Network that was in use in North America 2 or 3 years prior to ITU (T) adopted it and changed the name as SDH.

- 1984: T1X1 American Standardization agency was made responsible for defining interfaces of optical lines for interconnection of high bit rates between operators.

- 1985: Feb 1985, Bellcore introduced SONET (Sync Optical Network) concept of T1X1. It defined a new transmission hierarchy, which permits direct access to the lower level tributaries of a multiplex system. The activities of SONET are divided into 3 parts, Frame format, Optical interface and Measurement.

- 1988: Feb 1988. The ITU (T)'s G.707, G.708, G.709 recommendations for SDH were approved. Bit rate 155.520 mbps was standardized as basic frame of SDH and the structure remained compatible with utilization of the SONET frame at 51.840 mbps in USA

- 1989: The recommendations of ITU (T) working group XVIII were published in Blue Book 1989.

- 1990 : New versions of the recommendations G.707, G.708, G.709 were approved basing on the decisions of European Telecommunication Standards Institute (ETSI) regarding multiplexing structure. Other recommendations concerning multiplexing equipment, optical interfaces, subscriber loop equipment, network management were approved. The recommendations for cross connection equipment, architecture of synchronous network, and performance data of the network were being drawn up.

The maximum band that can be provided by PDH is 565 mbps and the number of speech channels is 7680. It is not in a position to meet any further demand.

The stages of multiplexing and there after demultiplexing required for higher orders are more which contributes for higher costs, more maintenance where as in SDH system the whole job of multiplexing to higher orders is done by a single multiplexer, there by the cost is less, space occupied is less, maintenance is less.

Bit interleaving multiplexing system adopted in PDH, scatters the bits at every stage, making the identification of the location of each bit very difficult and at the same time to bring them back to the original sample shape, as many stages of demultiplexing are to be carried out to return to its primary mux stage,

Over and above to this, addition of justification bits at every mux stage, further complicates the identification of the location of the already scattered bits.

The present challenge is to migrate from PDH to SDH and the cost constraints of the network. The success of SDH in future is possible because of the following reasons.

- Bandwidth of Fibre Optics can be increased and there is no limit for it.

- Microwave system can transmit digital signals with bit rates extending into the gbps range because of new modulation techniques 256 QAM, Stepped Square QAM(SSQAM) and 1024 QAM.

- Using the ever-increasing capabilities of VLSI technique to have more and more functional integration, which is also very cost effective.

- Availability of cheaper memory opens new possibilities.

- Requirement of customer services can be easily met without much additional equipment.

- The mind boggling penetration of software into every walk of life, and increasing stress on distributed processing with the development of object oriented software.

# 1.3 Long Distance Network Requirements

- Greater Bandwidth handling capacity due to emergence of broadband services including multimedia.

- Better Bit Error Rates due to merger of Voice & Data Communication.

- Higher availability due to information transfer having attained a state of criticality.

- Enhanced flexibility to accommodate various types of signals available today.

# 1.4 General Objectives Of SDH

- Creation of a world standard for bit rates above 140 mbps.

- To enable synchronous higher order digital multiplexing.

- Normalization of auxiliary data (overhead).

- More flexibility for networking.

- Direct access to tributaries

- To enable optical mid span meets.

- Transport of both American (T) and European (E) PDH tributaries.

ITU (T) has now standardized SDH recommendations related to Network Node Interface (NNI), network architecture, multiplexing equipment, line equipment etc, thus creating a world wide standard on transmission technology, simultaneous transmission of bit rates of different hierarchy levels and international transfer of information without complicated modification

# 1.5 SDH Advantages

**Worldwide Standard Bit Rates**: An international hierarchy shared worldwide and creation of worldwide standard rates above 140 mbps

**Synchronous Clock**: The SDH system maintains a synchronous clock throughout a defined area. All clocks in the system gets synchronized with a centralized clock known as Primary Rate Clock. For example in India BSNL has the Primary Rate clock in the VSNL headquarters Worli, Mumbai. All the clocks in SDH system of BSNL get synchronized with respect to this clock. This feature gives of the advantage of avoiding the errors in streams due to different clock speeds. The addition of justification bits such as positive justification, negative justification, justification control bits is not needed at each MUX stage for error identification and correction.

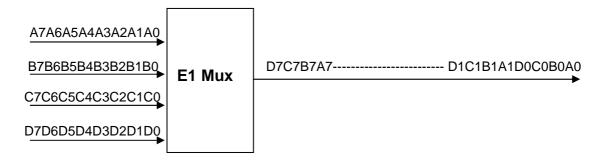

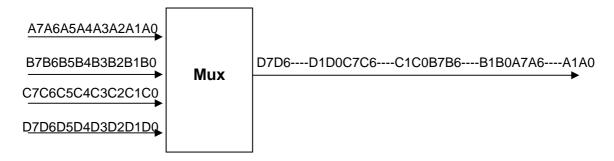

**Byte Interleaving Multiplexing**: In SDH system the multiplexing is done by byte interleaving instead of bit interleaving as followed in PDH systems. This maintains the transparency of each bit stream and any bit stream can be dropped from any stage of SDH. For example a 2 Mbps tributary can be dropped even from STM-64, without any necessity of disturbing the other tributaries.

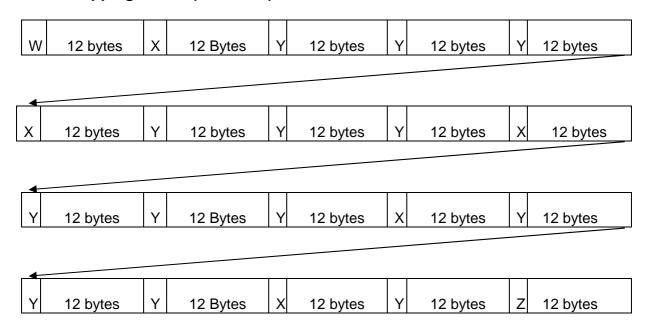

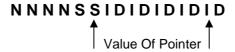

Figure 1.1 Bit Interleaving Multiplexing

Figure 1.2 Byte Interleaving Multiplexing

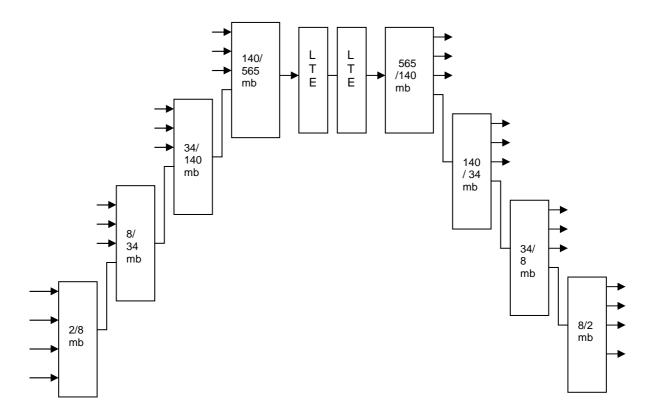

**Direct Access to Lower Speed Tributaries:** In PDH to drop a 2mbps stream from say E5 (565 mbps) 4 stages of demultiplexing is necessary, that is from 565 to 140, 140 to 34, 34 to 8, 8 to 2 mbps. The needed 2mbps is dropped and for carrying out the transmission of remaining tributaries, again multiplexing is to be done from 2 to 8, 8 to 34, 34 to 140, 140 to 565 mbps, where as in SDH any tributary for example an E1 (2 mbps) stream can be dropped from any stage, even from STM 64 without the necessity of demultiplexing or multiplexing at any stage or disturbing the other tributaries.

Figure 1.3 PDH Multiplexing & Demultiplexing Stages

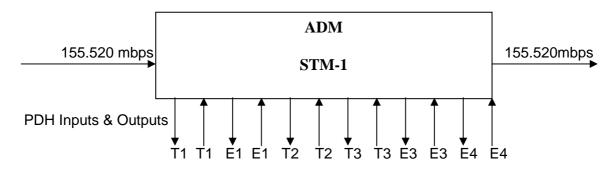

Figure 1.4 SDH Add & Drop Mux

**Drop & Insert Mux:** Individual tributaries of any bandwidth can be dropped or inserted at any multiplexer at any stage, even from STM-64, without any need for demultiplexing.

**World Wide Compatibility:** SDH can transport both E and T hierarchy tributaries without the need of using any additional interfacing equipment. Any tributary of E system or T system can be introduced at any stage of SDH system. The tributaries standardized by ITU (T) for introduction to SDH are E1 (2mbps), E3 (34 mbps), E4 (140 mbps), T1 (1.544 mbps), T2 (6.312 mbps), T3 (45 mbps).

Table 1.1 shows the standard transmission rates in USA, Canada, Europe/India, Japan in a Plesiochronous Digital Hierarchy (PDH).

| Hierarchy       | USA/ Canad       | da   | Japan            |       | Europe/ India    |       |

|-----------------|------------------|------|------------------|-------|------------------|-------|

| level<br>number | Bit Rate in mbps | Chls | Bit Rate in mbps | Chls  | Bit Rate in mpbs | Chls  |

| 1               | 1.544            | 24   | 1.544            | 24    | 2.048            | 30    |

| 2               | 3.152            | 48   | 6.312            | 96    | 8.448            | 120   |

| 3               | 6.312            | 96   | 32.064           | 480   | 34.368           | 480   |

| 4               | 44.736           | 672  | 97.728           | 1440  | 139.264          | 1920  |

| 5               | 91.053           | 1344 | 396.200          | 5760  | 564.992          | 7680  |

| 6               | 274.175          | 4032 | 810.000          | 11520 | 2400.000         | 30720 |

| 7               | 405              | 6048 |                  |       |                  |       |

| 8               | 565              | 8064 |                  |       |                  |       |

Table 1.1 E & T Hierarchies Of PDH

**Standardization:** SDH is a highly standardized system as Open System Interface by ITU (T) such as standardization of optical interface, standardization of frame format, standardization of auxiliary channels and control bits, standardization of multiplexing, standardization with flexible section that be a part of networks LAN, WAN, broad band ISDN, creation of open network structure increasingly required in today's competitive environment where as PDH is standardized upto primary level only other than bit streams. Beyond this the standardization of PDH is as manufacturer system, not an open system. The standardization of equipment interfaces enables the use of multi vendor end equipment.

**Performance Monitoring:** SDH enhances fault detection. Continuous error and quality analysis is integrated into the system by adding some overhead bytes at every stage of SDH system to monitor, identify errors and correct them. Parity checks permit localization of error on every specific section of line and at all levels of hierarchy. This minimizes the failures resulting from impairments. So to say SDH is an almost error free, transport system.

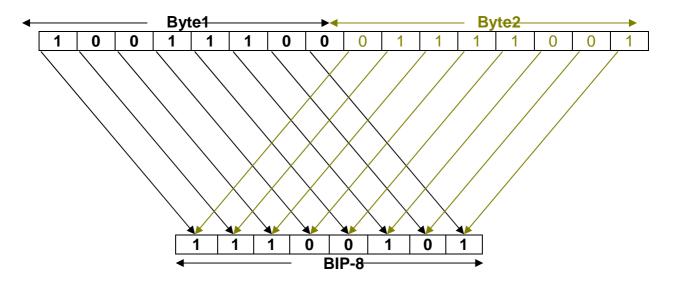

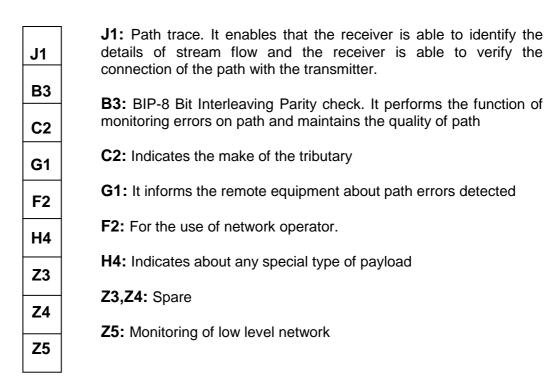

Path Over Head (POH): The POH added at VC level, makes each tributary transparent with respect to its flow and provides the necessary data needed while dropping any tributary. POH contains 9 Bytes. The first Byte is path trace, which contains the origin of path, details of its flow, a low order path access point identifier, which enables the receiving terminal to check its continued connection to the intended transmitter. The second byte is a bit interleaving parity

check over the entire stream frame for subsequent error performance monitoring. The other 7 bytes serve different functions as described latter.

Figure 1.5 Bit Interleaving Parity Check (BIP-8)

**Pointer Technology:** The pointer technology used in SDH to identify the actual starting byte of each tributary, which facilitates easy dropping of channels. When a tributary is multiplexed into a larger tributary, its phase offset in bytes can be identified relative to some reference point in this larger tributary. There is also a mechanism for allowing the value of this pointer to change if there is a loss of synchronization and the smaller capacity tributary is running either slightly slower or slightly faster than the larger tributary. Each of the smaller capacity tributaries have their own pointers, which can change independently. Although the use of these pointers still entails some input buffers, these are very much smaller than would be require if there were no mechanism for changing the phase of a small capacity tributary within a larger one, hence the problem of excessive delays can be contained. In SDH the majority of tributaries both large and small are well synchronized to each other but at the same time, there are a few which are not so well synchronized and every so often the increasing strain of their asynchronism has to be relieved by a byte sized slip relative to the majority of the other tributaries in the network. The pointer value associated with tributary is recalculated whenever a slip occurs.

The pointer mechanism is the heart of the SDH standard. It is this mechanism that enables us to construct networks that are nearly, but not completely synchronous and yet still allows us to easily locate each traffic channel, together with its associated management and control information but without incurring large penalties in transmission delay. SDH networks are not really synchronous at all but are actually very tightly controlled asynchronous networks. The fact that we have quantized the slips due to this asynchronism means that it is possible to locate and route any of the traffic paths within an SDH network. This together with network management software gives the traffic routing flexibility that was very difficult to achieve using

PDH based equipment. In terms of actual network hardware, it opens the way to the production of economically viable drop and insert multiplexers and cross connects.

**Frame Structure:** The structurization of SDH system frames of 125 microseconds transmission as 270 columns and 9 rows gives easy identification of tributary for the purpose of dropping & adding

**Section Over Head (SOH):** Each frame is added with SOH of 9 rows and 9 columns, which contains some Overhead bytes for communication between regenerators, multiplexers, for error correction etc. Sufficient spare locations are kept for future needs and expansion.

**Automatic Protective Systems:** The K1 and K2 bytes in SOH are key bytes for ensuring uninterrupted communication in spite of major breakdowns of equipment, medium, network systems etc. The self-healing, automatic traffic rerouting methods shall ensure no interruption in communication, which gives a higher reliability.

**Optical Fibre As Medium:** Another advantage of SDH lies in it's being struck bolted Optical Fibre as the medium which is inherently being immune to electromagnetic noise and is ideally suited for the much better error performance expected of SDH. Of late, SDH on Microwave is also being talked about and this will give another push to the acceptability of the SDH in variety of terrain.

**Mid Fibre Meet:** Another attraction that SDH carries with it is the mid fibre meet.

**Dynamic Network Capacity Management:** The system can adopt the varying traffic needs. It is possible to dynamically allocate bandwidth on demand to users any where within the network, at a short notice.

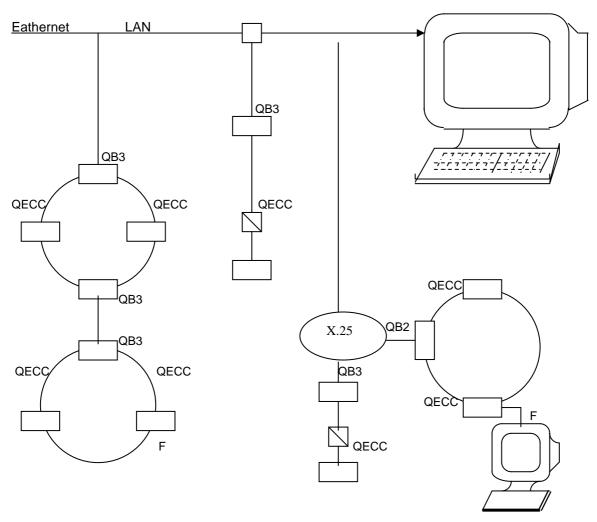

**Network Management System:** The O, A and M of the transmission network is carried out by an automatic and centralized NMS which provides features like easy network management, advanced end to end management to customer connections, flexible access and management of varied fixed bandwidth services to the customer, decreased out lays for personnel and test equipment, rapid computer controlled access to the desired transmission capacity with high transmission quality. NMS is fully software controllable.

The first and foremost advantage lies in the capability of on line network management, traffic management etc. This is possible because SDH provides a significant percentage of bit rates as control bits. With sufficient number of overhead bits, SDH has tremendous power and future scope for network management functions like performance monitoring, configuration

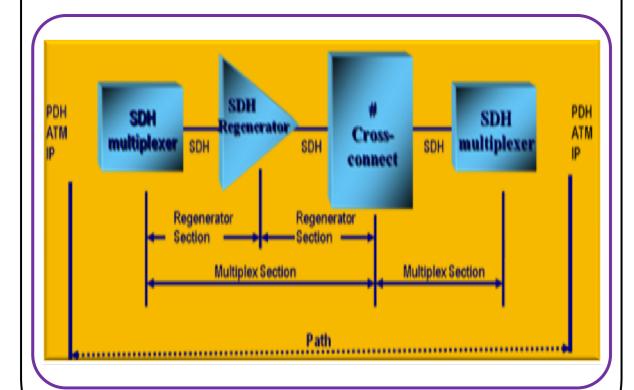

management, resource optimization, network security, remote provisioning & centralized maintenance, which are going to be the pronounced features leading to a significant competitive advantage. The multiplex structure for SDH includes functions that allow continuous performance monitoring and information exchange concerning the network status, should lead to more effective network management in future. Performance monitoring can be done at any of the three levels

- 1. End to end.

- 2. Multiplex section

- 3. Regenerator section.

**Synchronous Multiplexing And Frame Structure:** This gives the advantage of interaction of terminals and multiplexers, development of new generation of multiplexers (ADMs) and Digital Cross Connects (DXCs), MRC flexibility for networking and up gradation, easy growth of higher bit rates and network expansion up to 10Gbps, capability for transporting ATM bit rates and even non standard tributaries, lesser power consumption, reduced quantity of equipment, cost effective and less maintenance, provision of end to end customer services on demand.

**Network Simplification:** The concept of Add-Drop multiplexing in SDH is able to greatly simplify the existing network by replacing the PDH mux mountain which leads to reduction in network elements, resulting drastically reduced fault liability and parallel reduction in operating and maintenance costs. Further more efficient Drop & Insert of the channels offered by SDH network, together with it's powerful network management capabilities will lead to better provisioning of high & variable bandwidth requirements of the broadband services.

**Survivability:** The deployment of optical fibre throughout the network and adoption of the SDH network elements make end-to-end monitoring and maintenance possible. The management capability of the synchronous network will enable the failure of the links or nodes to be identified immediately. Using self-healing ring architectures, the network shall be automatically re configured with traffic instantly re routed until such a time as the faulty section has been repaired. As a result failures do not disrupt services, allowing network operator to commit to extremely high availability of service figures, and guarantee high levels of network performance.

## **Review Questions:**

- 1. What are the objectives of SDH?

- 2. What are the reasons basing on which the success of SDH in future depends?

- 3. What are the disadvantages of PDH system and why it is not suitable in present scenario?

- 4. What are the long distance network requirements?

- 5. What are the advantages of SDH system?

- 6. What is byte interleaving multiplexing and how it is advantageous when compared with bit interleaving multiplexing?

- 7. What do you understand by direct access to lower speed tributaries in SDH and why it is not possible in PDH?

- 8. What is the worldwide compatibility, a feature of SDH, which is not available in PDH?

- 9. What do you understand by pointer and how it is useful in SDH?

- 10. What are the advantages of network management system used in SDH?

\*\*\*\*

# Chapter 2

# **SDH Multiplexing Structure**

Objectives: By going through this chapter, the trainee must be in a position to understand

- 1. The SDH bit rates as per ITU-T's Rec. G.707.

- 2. The meaning of Synchronous Transport Module

- 3. Multiplexing structure of STM N, as per ITU T's Rec. G.709.

- 4. The meaning and functions of different stages of SDH multiplexing structure

- 5. SDH Multiplexing principle

# 2.1 SDH bit rates: As per ITU(T)'s recommendation G.707.

| SI.No. | SDH level | Bit Rate      | No. of Speech Chls |          |

|--------|-----------|---------------|--------------------|----------|

| 1.     | STM 1     | 155.520 mbps  | -                  | 1890     |

| 2.     | STM 4     | 622.080 mbps  | -                  | 7560     |

| 3.     | STM 16    | 2488.320 mbps | 2.5 Gbps           | 30,240   |

| 4.     | STM 64    | 9953.280 mbps | 10.0 Gbps          | 1,20,960 |

**Table 2.1 SDH Bit Rates**

- **2.2 Synchronous Transport Module (STM):** An STM is the information structure. It consists of information payload and overhead bits in block frame structure, which repeats at every 125 microseconds. The information is suitably conditioned for serial transmission on the selected media at a rate, which is synchronized to the network.

- STM followed by an integer, which indicates the level of SDH.

- STM 1 is the first level of SDH bit rates

- Higher SDH bit rates are obtained as integer multiples

- Higher rate levels are denoted by the corresponding multiplication fraction of the first level

STM 1 with 155.520 mbps is the basic rate. STM 4 indicates that it contains 4 STM 1s and each STM 1 is independent in all respects. Similarly STM 16 means 16 Nos of STM 1s and STM 64 is 64 Nos of STM 1s.

STM  $4 = 155.520 \times 4 = 622.080 \text{ mbps}$

It is to be noted that no justification bits are to be added as is done in PDH.

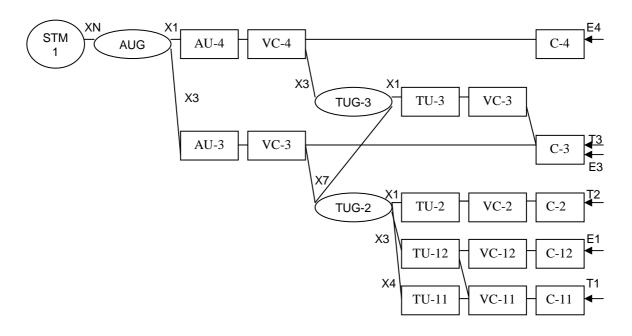

# 2.3 SDH Multiplexing Structure: As per ITU (T)'s recommendation G.709 (Fig 2.1)

The inputs to SDH system are PDH bit streams. ITU (T) has standardized E1, E3, E4 of E hierarchy and T1, T2 and T3 of T hierarchy as inputs into SDH. The block diagram of SDH multiplexing structure shown in figure 2.1, shows the making of STM1 or STM N where N indicates the integer of the SDH level.

**Container(C):** The first entry point of the PDH signal. It is the basic packing unit for tributary channels, is filled with the information from a plesiochronous signal. The process is called as mapping. Justification facilities are provided to adapt plesiochronous tributaries to the synchronous network clock. Each container is suitable for the rate of the signal inputted into it and for the structure of the synchronous frame. Fixed stuffing bits are inserted for synchronous tributaries. Signal is prepared so as to enter into the next stage i.e. virtual container. Containers are Basic Containers and Higher Order Containers. As per recommendation G.709, C-11, C-12,C-2,C-3 & C-4 are the containers for PDH bit rates of 1.544 mbps, 2.048 mbps, 6.312 mbps,34 mbps or 45 mbps and 140 mbps respectively.

Figure 2.1 SDH Multiplexing Structure

# Virtual Container (VC = C + POH):

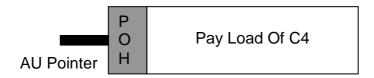

Each container is added with control information known as Path Over Head (POH), which helps the service provider to achieve end-to-end path monitoring. The container and the path overhead are together called as Virtual Container (VC). The POH is 1 column X 9 rows. In Virtual Container the POH fields are organized in a block frame structure either in 125 microseconds or in 500 microseconds. The functions of each byte in POH are shown in figure 2.2

#### **SDH MULTIPLEXING STRUCTURE**

Two types of virtual containers have been identified.

Basic virtual containers: VC11, VC12.

Higher order virtual containers: VC3, VC4.

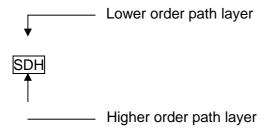

**Tributary unit (TU = VC + Pointer):** This unit is an information structure, which provides adaptation between the lower order path layer and the higher order path layer. It consists of information payload of virtual container and the tributary unit pointer. TU-2 for VC-2, TU-3 for VC-3 etc.

Fig 2.2 Path Over Head

**Tributary unit group (TUG):** One or more tributary units are grouped or multiplexed by byte interleaving to form higher bit stream rate as part of multiplexing structure. TUG-2 is a group of 3 TU-12s or 4 TU11s or 1 TU2. TUG-3 consists of homogenous assembly of TUG-2s or TU-3, either seven TUG-2s or one TU-3.

**Pointer:** It is an indicator whose value defines frame offset of a virtual container with reference to the frame reference of transport entity on which it is supported. It indicates the phase alignment of the virtual containers (VC-n) with respect to the POH of the next higher level VC in which it resides. The tributary Unit Pointer location is fixed with respect to this higher level POH.

**Pointer technology**: The use of pointer to indicate individual multiplex elements is a new feature of SDH. Pointers are not used in asynchronous, especially in PDH. This can take place through indication from the upper level of STM-1 frame to the individual VCs, using the example of a VC-4 as a first step. With in VC-4, four additional pointers are found at fixed locations. The pointers make the beginning of the three VC-3s relative to the VC-4.On one hand it makes possible to insert data signals at any point of time in the form of VCs into the respective higher level frame without a buffer. On the other hand, changes in the phase of the VC with respect to the next higher-level frame can be correlated through a appropriate pointer change. Such changes and phase shifts have caused, such as delay time variations, in the transmission medium or non synchronous branches in the real network

During decomposition of multiplex group, pointer technology makes it possible to directly locate each data channel from every STM-N frame. This considerably simplifies drop and insert mode at network nodes. This is unlike the PDH, where complete demultiplexing is required to be done at each level to access the desired data channel.

**Administrative Unit:** It is the information structure, which provides adaptation between higher order path layer and the multiplex section layer. It consists of information payload and AU pointer, which indicates the offset of the payload frame start relating to the multiplex section frame start. AU location is fixed with respect to STM-frame.

Administrative Group Unit: It consists of a homogenous assembly of AU-3s or AU-4.

**Network Node Interface (NNI):** It is the interface at a network node, which is used to interconnect another network node. The NNI is the most important interface. This interface is defined in ITU (T )'s Rec.G.708 and allows interconnection of network components (e.g., network nodes and multiplex systems) via cable or radio links.

Recommendation G.708 describes the logical characteristics of the interface (i.e., structure and meaning of the bit stream at the NNI). The physical characteristics will be specified in other recommendations. Both electrical and optical interfaces are specified for the STM-1 level (155.52 Mbps). The electrical interface uses CMI coding similar to the 139.264 mbps interface described in ITU (T) Rec. G.703.

For the higher levels of SDH (e.g., 622.080 and 2488.320 mbps) only optical interfaces are specified. The line termination (LT) equipment will be integrated into the multiplexer in the future. Therefore, no standardized electrical interface between the multiplexer and the LT is specified.

#### **SDH MULTIPLEXING STRUCTURE**

Other interfaces important in the test and measurement field are the plesiochronous interfaces found in ITU-T Recommendation G.703. These interfaces will be used as long as the plesiochronous and synchronous systems coexist.

**Multiplexing Principles of SDH:** 1.5 mbps, 2.048 mbps, 6.312 mbps enter their respective containers C-11, C-12 & C-2. These signals are prepared and inserted into their respective VCs and to the tributary unit pointers. TUG-2 can be either four C-11s with TU-11 or three VC-12s with TU-12 or one VC-2 with TU-2. The C-3 container input may be 34 mbps or 44.7 mbps. VC-3 container with AU-3 can directly go to AUG and enter STM frame. Similarly seven TUG-2s can be mapped into one TUG-3, otherwise one VC-3 with one TU-3 can be mapped into one TUG-3. Three TUG-3s can be mapped into VC-4. VC-4 with AU-4 go to AUG and then to STM frame. 3 AU-3s also can go to AUG and then to STM frame.

- Standardization of line optical interface.

- Standardization of frame format.

- Standardization of auxiliary channels and control bits.

- Implementation of system with flexible structure that can become part of new networks (LAN, WAN, B-ISDN).

- A reduced quantity of equipment, cost effective, less maintenance. Reduction of costs allowed by the synchronous frame structure due to following reasons.

- 1. Automatic and centralized management of the transmission network.

- 2. New network topologies.

- 3. Integration of terminals and multiplexers

- 4. New generation of multiplexers, ADMs (Add/Drop Multiplexers).

- 5. Introduction of DXCs (Digital cross Connects).

- 6. Lesser power consumption of the equipment.

- 7. Greater flexibility for transporting non-standard tributaries.

- Continuous error and quality analysis integrated into the system.

- Minimization of failures resulting from impairments.

- Direct access to lower speed tributaries without demultiplexing and multiplexing

- Entire high-speed signal.

- Mid section meets.

#### **SDH MULTIPLEXING STRUCTURE**

- Capable of transporting the existing PDH signals. Compatible with PDH. Various hierarchy levels are interconnected by means of digital multiplexing, employing justification methods.

- Capable of transporting the future broadband ATM bit rates.

- Rapid computer controlled access to the desired transmission capacity with high transmission quality.

- Easy network expansion up to 2.5 gbps.

- Decreased outlays for personnel and test equipment.

- High reliability. Self-healing, automatic traffic rerouting without service interruption.

- Service on demand, fast provision of end-to-end customer services on demand.

- Flexible access, flexible management of varied fixed bandwidth services to the customer premises.

- Creation of open network structures increasingly required in today's competitive environment

- SDH provides advanced end-to-end management to customer connections.

- Easy network management. More flexibility for networking and upgradability.

- Enhanced operation, administration & maintenance (O,A & M) capabilities.

- Easy growth to higher bit rates in steps with the evolution of transmission technology.

# **Review Questions:**

- 1. What are the bit rates used in SDH hierarchy?

- 2. Explain the SDH multiplexing structure with a diagram.

- 3. What are the standardised inputs to STM? In STM N, what does the N indicates?

- 4. Explain what do you understand by Container? What does C11, C12, C2, C3 & C4 indicate?

- 5. Explain about POH and its 9 bytes structure.

- 6. What is the use of pointer?

- 7. Write briefly about NNI.

- 8. Write the multiplexing principles of SDH.

- 9. Show with a block diagram how TUG-3 is made up from C12s.

- 10. Explain briefly about TU, TUG, AU and AUG.

\*\*\*\*

# **Chapter 3**

# **SDH Synchronous Frame Structure**

Objectives: By going through this chapter, the trainee must be in a position to understand

- 1. The Synchronous frame structure

- 2. The functions of Section Over Head

- 3. Make up of C4, C3 and C12

- 4. Generation of VC4 from TUG-3s

- 5. Mapping up of C4 & C3

- 6. Higher order STM N s

## 3.1 Basic Frame:

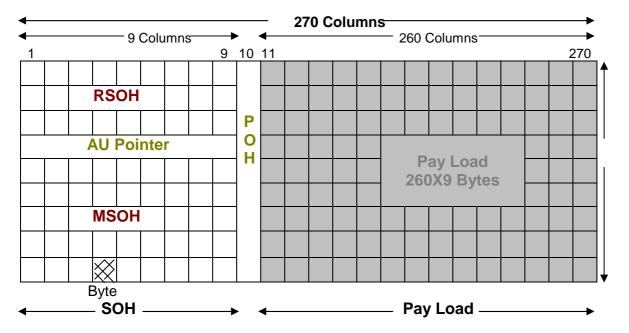

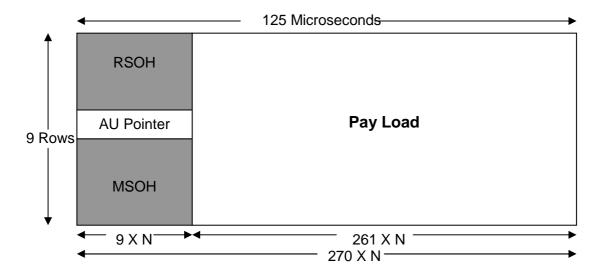

The basic frame of STM 1 is shown in Figure 3.1, contains 270 columns X 9 rows in a duration of 125 micro seconds. It is divided into three main areas.

- 1. **Section Over Head (SOH):** 9 columns X 9 rows, which includes, regenerator section overhead (RSOH) 9 columns X 3 rows, AU Pointer 9 columns X 1 row, and multiplexer section overhead (MSOH) 9 columns X 5 rows.

- 2. Path Over Head (POH): 1 column X 9 rows.

- 3. Pay Load: 260 columns X 9 rows.

Figure 3.1 STM Frame With Over Heads & Pay Load

The details of bytes in frame and bit rates are shown in Para 3.2.

## 3.2 Bytes In Frame & Bit Rates:

| Frame Duration | = 1 | 25 Micro s  | econds    |          |              |

|----------------|-----|-------------|-----------|----------|--------------|

| Frame Length   | = 2 | 70 X 9 = 24 | 430 Bytes | <b></b>  | 155.520 mbps |

| Pay Load       | = 2 | 60 X 9 = 23 | 340 Bytes | <b></b>  | 149.760 mbps |

| POH            | =   | 1 X 9 =     | 9 Bytes   | <b>→</b> | 0.576 mbps   |

| AU Pointer     | =   | 9 X 1 =     | 9 Bytes   | <b></b>  | 0.576 mbps   |

| RSOH           | =   | 9 X 3 =     | 27 Bytes  | <b></b>  | 1.728 mbps   |

| MSOH           | =   | 9 X 5 =     | 45 Bytes  | <b></b>  | 2.880 mbps   |

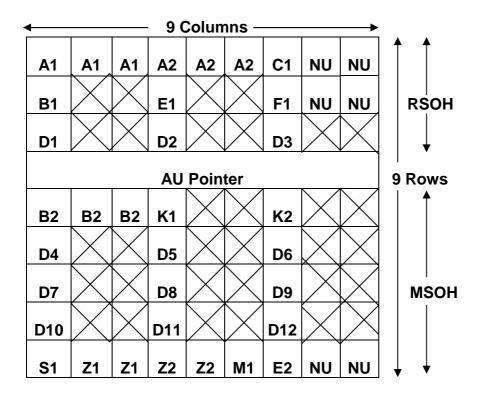

**3.3 Section Over Head (SOH = RSOH + MSOH):** SOH excluding AU pointer, contains O, A&M signals, bytes for the functions of frame alignment, network management, performance monitoring, protection switching, order wire and block framing. STM – N multiplexing uses a simple byte interleaving scheme. The SOHs of individual tributaries are also combined into a byte interleaving block structure.

Figure 3.2 Section Over Head

**3.3.1 Regenerator Section Over Head (RSOH):** Terminated at regenerators as shown in figure 3.3. The RSOH bytes are described as under.

**A1, A2:** Frame Alignment Words A1= 11110110 A2=00101000

6 bytes for each STM – 1. These bytes shall be provided in all STM – 1s.

**J0:** Path trace between regenerators. This byte transmits a Section Access Point Identifier so that a section receiver can verify its continued connection to the intended transmitter.

**B1:** Bip-8. Bit Interleaving Parity (even parity) check, used to monitor the errors between the regenerators. One byte is provided for each STM - 1. This byte performs the bit error monitoring function for elementary regenerator section. BIP - 8 is computed over all the bits of the previous STM - 1 after scrambling and is placed in byte B1. This byte is monitored and recomputed at every regenerator.

**E1:** EOW channel for voice communication. User channel.

**F1:** User channel for special maintenance purposes or for the use of network operators.

**C1:** An unique number assigned to STM -1, prior to it being multiplexed to a higher STM level. On demultiplexing, this byte is used to identify the position of any particular STM -1, within the incoming STM -N signal.

**D1,D2,D3:** Data communication channel for maintenance purpose between regenerators.

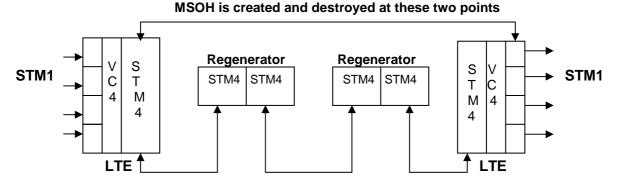

RSOH is created and destroyed at these pairs points

Figure 3.3 Utilization Of MSOH & RSOH

**3.3.2 Multiplexer Section Over Head (MSOH):** Terminated where AUGs are assembled and dissembled. MSOH passes transparent through regenerators. The MSOH bytes are described as under.

**B2:** Bip-24 Bit Interleaving Parity (Even parity) check, used to monitor the errors between multiplexers. Computed over all the bits of the previous STM –1 frame except for the first three rows of SOH (A1 to D3). Provided in all STM – 1s with in a STM – N.

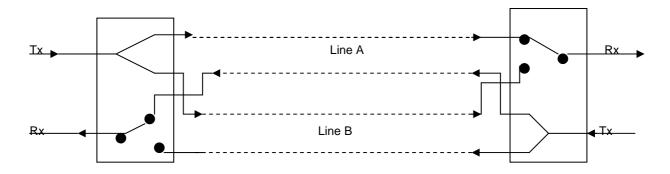

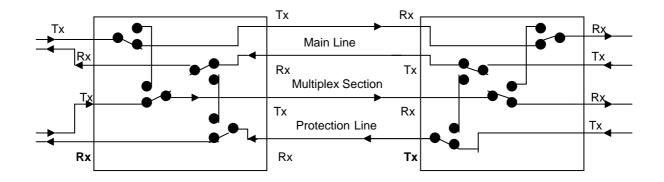

K1, K2: Automatic Protective Switching (APS) command & remote alarm command.

**D4 To D12:** Data communication channel for maintenance purpose between multiplexers.

D1 to D12, the data communication bytes in both RSOH & MSOH are used for network management system (NMS) and are called as Embedded Communication Channel (ECC)

**S1:** Synchronous Status Message. This byte is used to indicate the synchronization reference at each network element.

Z1, Z2: Reserve bytes

**E2:** EOW. Voice channel. User Channel between multiplexers.

M1: Transmits the information of the number of errors detected by B2 to the remote equipment

NU: Bytes reserved for Local or National use

: Bytes Reserved for future use. Presently not used.

**3.3.3 Administrative Unit (AU) Pointer:** Indicates the beginning of VC-4 or 3 VC-3s in relation to STM-1 frame.

AU-4 is VC-4 + Pointer, within STM-1 basic frame. The pointer indicates the beginning of VC-4. In case there is a speed variation between VC-4 and STM-1 due to different working clocks, the pointer is responsible to manage the losses to maintain VC-4 and STM-1 at the same speed. The number of pointer actions is in relation with the difference of bit rate between the VC-4 and STM-1. The pointer adapts Positive / Nil / Negative justification process to manage the loss of synchronization. The justification is accompanied by incrementation or decrementation of pointer bits.

**Positive Justification:** VC-4 is slower than STM-1 payload. The justification bytes are used to carry the information bits of VC-4.

**Justification:** VC-4 is at the same speed of STM-1 payload. The justification bytes are used as just stuffing bits do not carry any intelligence.

**Negative Justification:** VC-4 is faster than STM-1 pay load. The justification bytes are adjusted by using additional bytes to increase the capacity of VC-4.

**3.4 Path Over Head (POH):** VC-4 = C-4 + POH, is located in the 10<sup>th</sup> column of STM-1 frame. It provides the path trace, performance monitoring in addition to other details with regard to the STM-1. The functions of POH are discussed in chapter 1, Para 2.3.

**3.5 Payload:** This is the data area. The bytes containing data from the tributaries are transferred to the pay load area without buffering and are in relation with the STM-N frame.

These tributaries come from all levels of the plesiochronous (free running) hierarchy, E1, T1, T2, T3, E3, and E4. The payload transports the corresponding virtual containers VC12, VC11, VC2, VC3 or VC4.

- **3.5.1 Make Up Of Pay Load:** This is a low level multiplexing of low rate plesiochronous signals, by inserting them into synchronous frame or putting them in contact, which varies as per the flow rates of input signals. To adapt the flow rates of the plesiochronous signals to the required rates of them in VCs, some additional bits are added as pointers as per the process of justification. The entry point of the plesiochronous tributaries is container. In the following paragraphs the insertion of tributaries into containers is described.

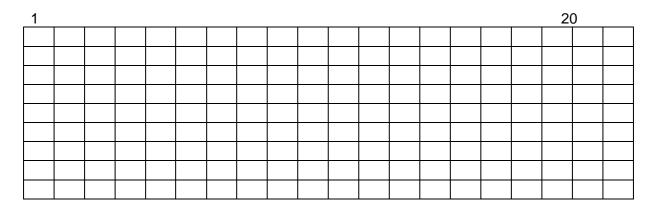

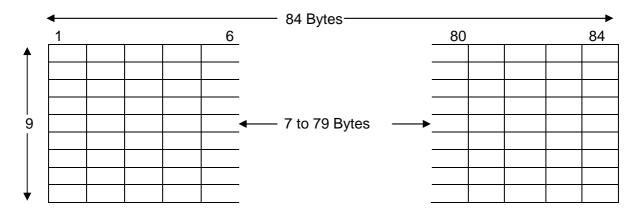

- **3.6 Container C4 (Fig. 3.4):** The input to container C4 is E4 -139.264 mbps. After clock recovery and regeneration of the tributary, the data is placed in container.

Figure 3.4 Container C4

The container is of duration of 125 microseconds and frame structure of 20 blocks X 9 rows

Frame : 20 Blocks (In each row) X 9 Rows = 180 Blocks.

Row: 20 Blocks.

Block : 13 Bytes – Information bytes 12 & Over head bytes 1.

Bytes in Frame:  $13 \times 20 \times 9 = 2340$ .

Frame duration: 125 microseconds

Bit Rate : 2340 X 8 X 8000 = 149.760 mbps.

The bit rate is 149.760 mbps and is higher than input to C4, which is 139.264 mbps. Hence all the bits carried are not information bits. Some additional bits are added for justification and other purposes.

**Justification:** It is an operation, which makes it possible to fit a variable rate signal into a fixed rate frame.

Suppose the normal rate of a tributary = X bits / sec

The variation of rate  $= \pm \Delta$  bits / sec

To transmit the tributary with in S frame, it is necessary to allocate highest possible bit rate.

S =  $X + \Delta$  bits / sec.

E4 =  $139.264 \text{ mbps} \pm 15 \text{ ppm} = 139264 \pm 2.088 \text{ kbps}.$

1 justification bit is added in a row in Z byte.

# 3.6.1 Mapping Of C4: (Each row)

Figure 3.5 Mapping Of Container C4

W = IIIIIIII X = CRRRRROO Y = RRRRRRR Z = IIIIIISR

I = Information bit at 140 mbps

O = Service element bit reserved for future needs

R = Fixed stuffing bit

S = Justification bit (1 per line in Z)

C = 5 Justification indicator bits (by majority detection)

$C = 00000 \longrightarrow S = Information bit$   $C = 11111 \longrightarrow S = stuffing bit$

Total information bits are  $[(12 \times 8 \times 20) + (1 \times 8) + (1 \times 6)] \times 9 \times 8000 = 139.248$  mbps. This bit rate is the rate of C4 bits, which is less than the E4 - 139.264 mbps. To add some more information bits, S bit in Z byte is used as information bit (as justification bit) to the extent necessary, which gives a max. bit rate of 139.320 mbps.

On mapping the container, POH of 9 bytes is added at VC4 & Pointer of 9 bytes is added at AU4 and transmitted to AUG.

Figure 3.6 C4 With POH & Pointer

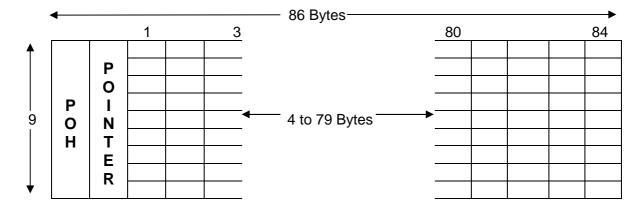

**3.7 Container C3: (Fig 3.6):** The C3 input is 34.368 mbps. C3 consists of 9 rows, 84 bytes in each row and 756 bytes in total.

Figure 3.7 Container C3

C3 is divided as 3 blocks T1, T2, T3, each block containing 84 bytes in a row and three rows. The blocks and  $84 \times 3 = 252$  bytes in each block are as shown in figure 3.7.

The block T1 contains information bytes 178, stuffing bytes 67, C bytes 5, A & B bytes one each, a total of 252 bytes = 252 X 8X 8000 = 16.128 mbps.

Number of information bits in  $T1 = 178 \times 8 + 7$  bits of S = 1431 bits

Number of information bits in  $C3 = 1431 \times 3 = 4293$  bits.

Information bit rate  $= 4293 \times 8000 = 34.344 \text{ mbps}$

Total number of bits in T1 =  $252 \times 8 = 2016 \text{ bits}$

Total number of bits in C3  $= 2016 \times 3 = 6048 \text{ bits}.$

The frame duration of C3 = 125 microseconds.

Bit rate of C3  $= 6048 \times 8000 = 48,384 \text{ mbps}$

The total bit rate of C3 48.384 mbps is higher than the information bit rate of C3 34.344 mbps. Hence all the bits carried are not information bits. Some additional bits are added for justification and other purposes.

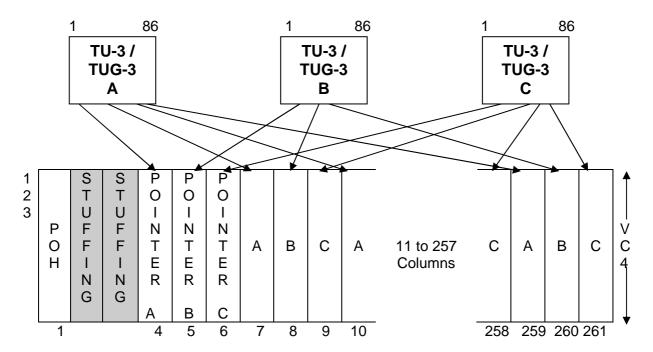

**3.7.1 Generation Of TU3 / TUG3:** TU-3 with 9 X (84 columns pay load + 1 column pointer + 1 column POH = 86 columns) is shown in figure 3.8.

The TU3 is made of the whole of the VC3 + a pointer

The TUG3 defines the locations of the TU3s with in the VC4. The TU3 pointer bytes H1, H2 and H3 are the bytes of lines 1,2 and 3 of columns 4,5 and 6 of VC4. The other 6 bytes of these columns are stuffing bytes.

Figure 3.8 Tributary Unit (TU-3) With POH & Pointer

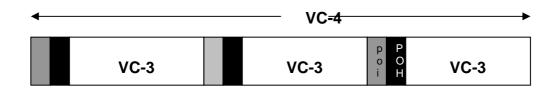

# 3.10 Generation Of VC-4 from 3 TUG-3s: (Figs 3.9 & 10)

3 C-3s make the pay load equivalent to VC-4. Each VC-3 is added with its separate POH for its path trace & performance monitoring etc and added with a separate pointer to adjust its offset in the VC-4.

Figure 3.9 VC4 With 3 Nos. Of C3s With POH & Pointers

Figure 3.10 Generation Of VC-4 From Three TU-3 / TUG-3 Tributaries

The VC-4 is generated by carrying out multiplexing by interlacing the columns of the 3 TUG-3s A, B, and C, after adding the VC-4 POH and two columns with stuffing bytes.

# 3.7.2 Generation OF AUG:

AUG is generated, by adding AU-4 to VC-4. AU-4 is a pointer of STM-1 and AUG is the entity, which contains AU-4 + VC-4 payload. AUG is put into STM-1 along with SOH.

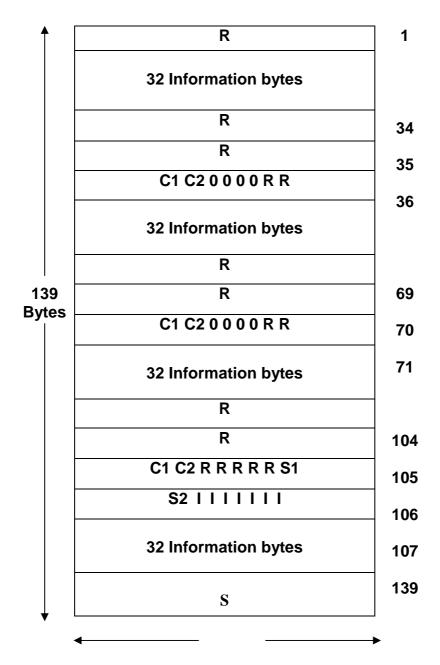

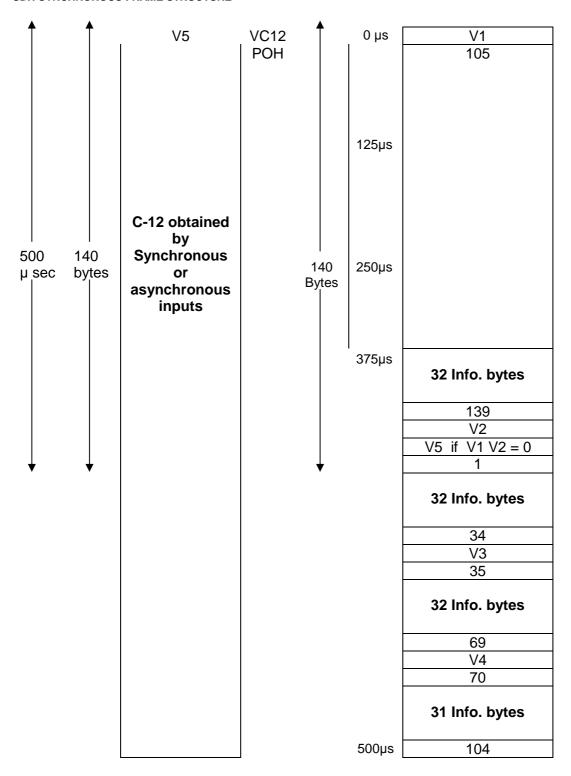

**Container C12 (Fig 3.11):** C-12 input is 2.048 mbps, which can be unstructured – asynchronous (G.703) or structured – synchronous (G.704).

Figure 3.11 Container C12

R = Stuffing bits I = Information bits S1, S2 = Justification Opportunity bits In asynchronous input, the bits are put into C-12 as and when they arrive, the justification takes place at the bit level within C-12.

The duration of combined frame for 4 X E1 tributaries is 500 microseconds.

Figure 3.12 VC-12

Figure 3.13 TU-12

The asynchronous C-12 of duration 500 microseconds is shown in Fig.T.13D.3.11. One C-12 is spread in  $4 \times 125 = 500$  microseconds along with 3 more C-12s, to reduce the overheads.

Information bits :  $(3 \times 32 \times 8) + (1 \times 31 \times 8) = 1023$

Information rate of each C-12 :  $1023 \times 2000 = 2.046 \text{ mbps}$ .

Input to C-12 : 2.048 mbps

The input rate is higher than the container rate hence the justification is negative.

In synchronous input, the bits are structured and organized in bytes and frame.

V1 and V2 constitute the VC-12 pointer.

V3 Negative justification opportunity

V4 presently not used.

Vi & V2: Identification mark of the location of the start of VC-12 i.e. V5

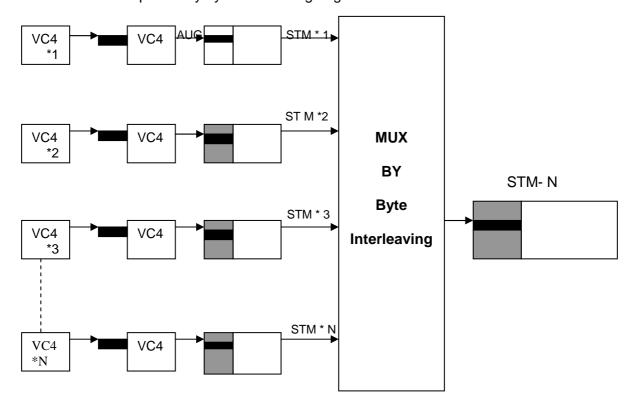

**Higher Order STM-Ns:** Higher order STMs are STM-4, STM-16 & STM-64. High rate multiplexing with STMs as inputs makes them. STM-1 frames of each 155.520 mbps of N numbers are multiplexed by byte interleaving to give STM-N.

Figure 3.14 Formation Of STM-N By High Order Multiplexing

The smallest element in STM-N frame is a byte, represented by a square, which represents a 64 kbps channel that ensures direct access to each individual channel. The transmission of frame is from left to right and top to bottom.

STM-N shall have 270N Columns X 9 Rows. N is the hierarchy level of SDH. N may be equal to 1, 4, 16 or 64, as shown in figure 3.15

Figure 3.15 STM-N Frame

| 12 nos. of A1 |            | 12   | 12 nos. of A2 |    | 4 Nos. of J0 |        | 8 Nos. of X bytes  | 1 |

|---------------|------------|------|---------------|----|--------------|--------|--------------------|---|

|               | bytes      |      | bytes         |    | bytes        |        |                    |   |

| B1            |            | E1   |               |    | F            | •      | 11 Nos. of X bytes |   |

|               | Bytes not  |      | Bytes n       | ot | 1            |        |                    | 9 |

| D1            | used       | D2   | used          |    | D            |        | Bytes not used     |   |

|               |            |      |               |    | 3            |        |                    |   |

|               | l          |      |               | Α  | U P          | ointer |                    | - |

| 12 r          | nos. of B2 | K1   |               |    | K2           |        |                    | 1 |

| byte          | es         |      |               |    |              |        |                    |   |

| D4            |            | D5   | Bytes n       | ot | D6           |        | Bytes not used     | • |

| D7            | Bytes not  | D8   | used          |    | D9           |        |                    |   |

| D1            | used       | D1   |               |    | D1           |        |                    |   |

| 0             |            | 1    |               |    | 2            |        |                    |   |

| S1            | 11 Z1      | 11   | Z2            | М  | E2           |        | 11 Nos. of X bytes |   |

|               | bytes      | byte | es            | 1  |              |        |                    |   |

| •             | 36 Columns |      |               |    |              |        |                    |   |

Figure 3.16 SOH OF STM-4 Frame

The SOH of STM-4 is shown in figure 3.16.

| The A1 Bytes are 3 of STM-1 X4 = 12   | The A2 Bytes are 3 of STM-1 X4 = 12 |

|---------------------------------------|-------------------------------------|

| The B2 Bytes are 3 of STM-1 X4 = 12   | The J0 Bytes are 1 of STM-1 X4 = 4  |

| The Z1 Bytes are 3 of STM-1 X4 -1= 11 | The Z2 Bytes are 3 of STM-1 X4-1=11 |

| AU Pointer 9 of STM-1 X 4 = 36 Bytes  |                                     |

The X bytes are reserved for National use (NU). All other bytes are presently not in use.

# **Review Questions:**

- 1. Explain what do you understand by the basic frame structure of STM-1

- 2. What are the functions performed by RSOH?

- 3. What are the functions performed by MSOH?

- 4. What are the functions of AU pointer and POH added to VC-4 payload?

- 5. Explain the make up of 155.520 mbps from the independent components of STM frame

- 6. What are the functions of BIP-8 and BIP-24 in SOH?

- 7. Explain the functions of Embedded Communication Channel.

- 8. Explain the make up of C4

- 9. Explain the make up of C3

- 10. Explain the mapping of C4

- 11. Explain the generation of VC-4 from C-3s

- 12. Explain the generation of VC-4 from C-12s

\*\*\*\*

# **Chapter 4**

# **Pointers**

**Objectives:** By going through this chapter, the trainee must be in a position to understand

1. The meaning, purpose and functioning of pointer

## 4.1 AU-n Pointer:

The AU-n pointer provides a method of allowing flexible and dynamic alignment of the VC-n within the AU-n frame. Dynamic alignment means that the VC-n is allowed to "float" within the AU-n frame. Thus, the pointer is able to accommodate differences, not only in the phases of the VC-n and the SOH, but also in the frame rates.

## 4.2 AU-n Pointer Location:

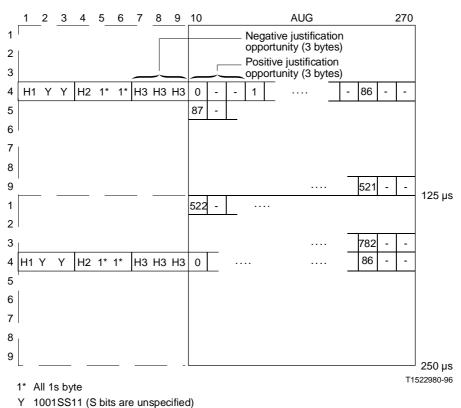

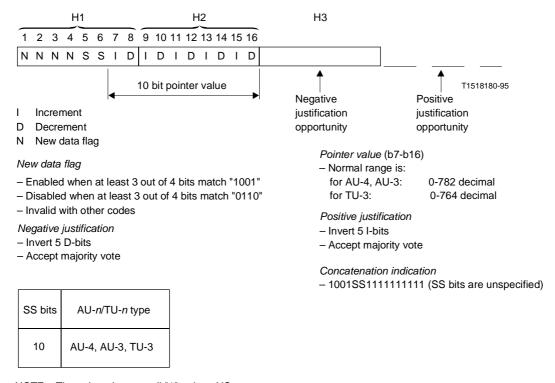

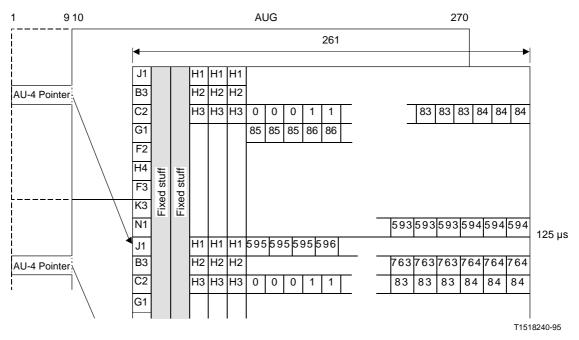

The AU-4 pointer is contained in bytes H1, H2 and H3 as shown in Fig.T.13D.4.1. The three individual AU-3 pointers are contained in three separate H1, H2 and H3 bytes as shown in figure 4.2.

Figure 4.1 AU-4 Pointer Offset Numbering

Figure 4.2 AU-3 Pointer Offset Numbering

$\ensuremath{\mathsf{NOTE}}$  – The pointer is set to all "1"s when AIS occurs.

Figure 4.3 AU-n/TU-3 Pointer (H1, H2, H3) Coding

## 4.3 AU-n Pointer Value:

The pointer contained in H1 and H2 designates the location of the byte where the VC-n begins. The two bytes allocated to the pointer function can be viewed as one word as shown in figure 4.3. The last ten bits (bits 7-16) of the pointer word carry the pointer value. As illustrated in

#### **POINTERS**

figure 4.3, the AU-4 pointer value is a binary number with a range of 0 to 782 which indicates the offset, in three byte increments, between the pointer and the first byte of the VC-4 (figure 4.1). Figure 4.3 also indicates one additional valid pointer, the concatenation Indication. The Concatenation Indication is indicated by "1001" in bits 1-4, bits 5-6 unspecified, and ten "1"s in bits 7-16. The AU-4 pointer is set to Concatenation Indication for AU-4 concatenation (see figure 4.8).

As in Figure 4.3, the AU-3 pointer value is also a binary number with a range of 0 to 782. Since there are three AU-3s in the AUG, each AU-3 has its own associated H1, H2 and H3 bytes. As shown in figure 4.2, the H bytes are shown in sequence. The first H1, H2, H3 set refers to the first AU-3, and the second set to the second AU-3, and so on. For the AU-3s, each pointer operates

independently.

Figure 4.4 AU-4 Pointer Adjustment Operation – Positive Justification

In all cases, the AU-n pointer bytes are not counted in the offset. For example, in an AU-4, the pointer value of 0 indicates that the VC-4 starts in the byte location that immediately follows the last H3 byte, whereas an offset of 87 indicates that the VC-4 starts three bytes after the K2 byte.

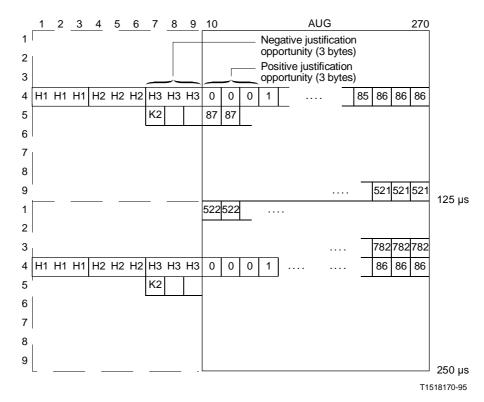

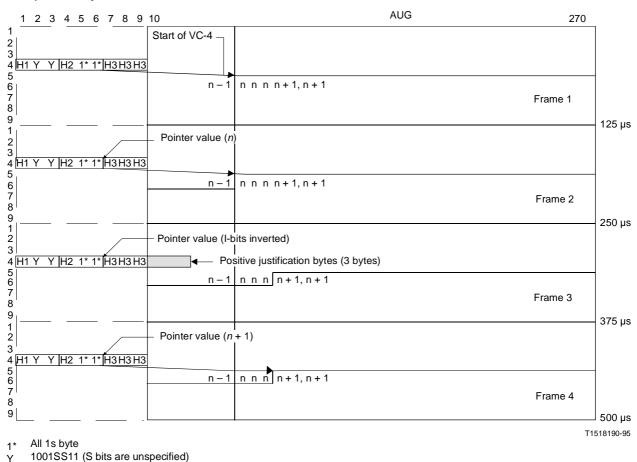

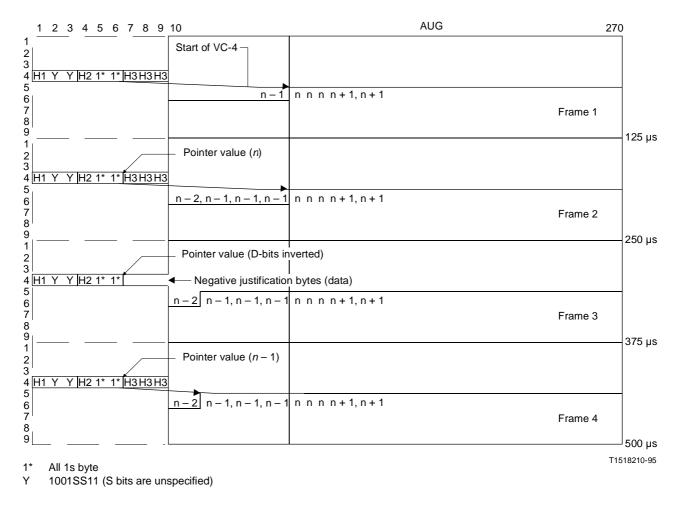

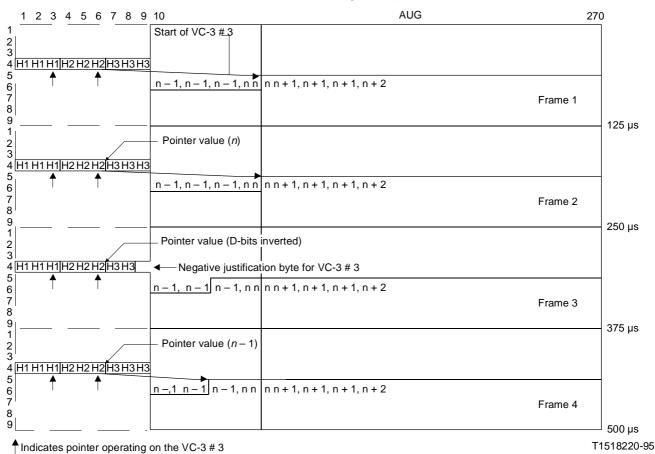

**4.4 Frequency Justification:** If there is a frequency offset between the frame rate of the AUG and that of the VC-n, then the pointer value will be incremented or decremented as needed, accompanied by a corresponding positive or negative justification byte or bytes. Consecutive pointer operations must be separated by at least three frames (i.e. every fourth frame) in which the pointer value remains constant. If the frame rate of the VC-n is too slow with respect to that of the AUG, then the alignment of the VC-n must periodically slip back in time and the pointer value must be incremented by one. This operation is indicated by inverting bits 7, 9, 11, 13 and 15 (I-bits) of the pointer word to allow 5-bit majority voting at the receiver. Three positive justification bytes appear immediately after the last H3 byte in the AU-4 frame containing inverted I-bits. Subsequent pointers will contain the new offset. This is illustrated in figure 4.4.

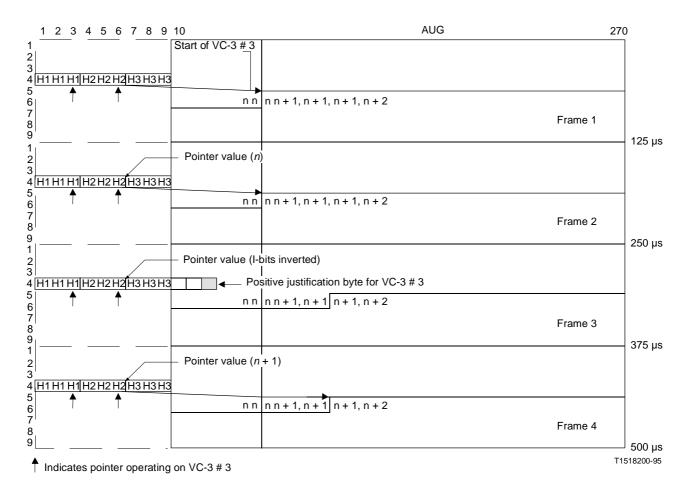

For AU-3 frames, a positive justification byte appears immediately after the individual H3 byte of the AU-3 frame containing inverted I-bits. Subsequent pointers will contain the new offset. This is illustrated in figure 4.5.

Figure 4.5 AU-3 Pointer Adjustment Operation – Positive Justification

If the frame rate of the VC-n is too fast with respect to that of the AUG, then the alignment of the VC-n must periodically be advanced in time and the pointer value must be decremented by one. This operation is indicated by inverting bits 8, 10, 12, 14 and 16 (D-bits) of the pointer word to allow 5-bit majority voting at the receiver. Three negative justification bytes appear in the H3 bytes in the AU-4 frame containing inverted D-bits. Subsequent pointers will contain the new offset. This is illustrated in figure 4.6.

For AU-3 frames, a negative justification byte appears in the individual H3 byte of the AU-3 frame containing inverted D-bits. Subsequent pointers will contain the new offset. This is illustrated in figure 4.7.

Figure 4.6 AU-4 Pointer Adjustment Operation – Negative Justification

# 4.5 New Data Flag (NDF):

Bits 1-4 (N-bits) of the pointer word carry an NDF, which allows an arbitrary change of the pointer value if that change is due to a change in the payload. Four bits are allocated to the flag to allow error correction. Normal operation is indicated by a "0110" code in the N-bits. NDF is indicated by inversion of the N-bits to "1001". An NDF should be interpreted as enabled when three or more of the four bits match the pattern "1001". An NDF should be interpreted as disabled when three or more of the four bits match the pattern "0110". The remaining values

(i.e. "0000", "0011", "0101", "1010", "1100" and "1111") should be interpreted as invalid. The new alignment is indicated by the pointer value accompanying the NDF and takes effect at the offset indicated.

#### 4.6 Pointer Generation:

The following summarizes the rules for generating the AU-n pointers.

During normal operation, the pointer locates the start of the VC-n within the AU-n frame. The NDF is set to "0110".

The pointer value can only be changed by operation 3, 4 or 5.

If a positive justification is required, the current pointer value is sent with the I-bits inverted and the subsequent positive justification opportunity is filled with dummy information. Subsequent pointers contain the previous pointer value incremented by one. If the previous pointer is at its maximum value, the subsequent pointer is set to zero. No subsequent increment or decrement operation is allowed for at least three frames following this operation.

Figure 4.7 AU-3 Pointer adjustment Operation – Negative Justification

If a negative justification is required, the current pointer value is sent with the D-bits inverted and the subsequent negative justification opportunity is overwritten with actual data. Subsequent pointers contain the previous pointer value decremented by one. If the previous pointer value is

zero, the subsequent pointer is set to its maximum value. No subsequent increment or decrement operation is allowed for at least three frames following this operation.

If the alignment of the VC-n changes for any reason other than rules 3 or 4, the new pointer value shall be sent accompanied by NDF set to "1001". The NDF only appears in the first frame that contains the new values. The new location of the VC-n begins at the first occurrence of the offset indicated by the new pointer. No subsequent increment or decrement operation is allowed for at least three frames following this operation.

#### 4.7 Pointer Interpretation:

The following summarizes the rules for interpreting the AU-n pointers.

- During normal operation, the pointer locates the start of the VC-n within the AU-n frame.

- Any variation from the current pointer value is ignored unless a consistent new value is received three times consecutively or it is preceded by one of the rules 3, 4 or 5. Any consistent new value received three times consecutively overrides (i.e. takes priority over) rules 3 or 4.

- If the majority of the I-bits of the pointer word are inverted, a positive justification operation is indicated. Subsequent pointer values shall be incremented by one.

- If the majority of the D-bits of the pointer word are inverted, a negative justification operation is indicated. Subsequent pointer values shall be decremented by one.

- If the NDF is interpreted as enabled, then the coincident pointer value shall replace the current one at the offset indicated by the new pointer value unless the receiver is in a state that corresponds to a loss of pointer.

### 4.8 AU-4 Concatenation:

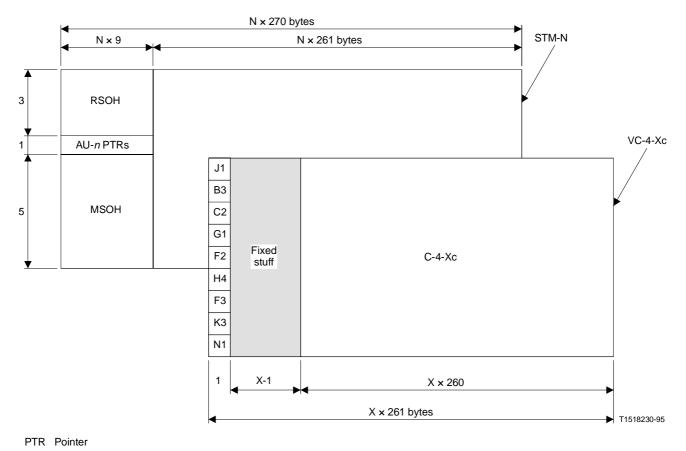

AU-4s can be concatenated together to form an AU-4-Xc (X concatenated AU-4s) which can transport payloads requiring greater capacity than one Container-4 capacity.

# 4.9 Concatenation Of Contiguous AU-4s:

A concatenation indication, used to show that the multi Container-4 payload carried in a single VC-4-Xc should be kept together, is contained in the AU-4 pointer. The capacity available for the mapping, the multi Container-4, is X times the capacity of the Container-4 (e.g. 599 040 Mbit/s for X = 4 and 2 396 160 kbit/s for X = 16). Columns 2 to X of the VC-4-Xc are specified as fixed stuff. The first column of the VC-4-Xc is used for the POH. The POH is assigned to the VC-4-Xc (e.g. the BIP-8 covers 261 X columns of the VC-4-Xc). The VC-4-Xc is shown in figure 4.8.

The first AU-4 of an AU-4-Xc shall have a normal range of pointer values. All subsequent AU-4s within the AU-4-Xc shall have their pointer set to Concatenation Indication "1001" in bits 1-4, bits 5-6 unspecified, and ten "1"s in bits 7-16. The Concatenation Indication indicates that the pointer processors shall perform the same operations as performed on the first AU-4 of the AU-4-Xc.

Figure 4.8 VC-4-XC Structure

#### 4.10 Virtual Concatenation Of AU-4s:

The virtual concatenation method for TU-2s is defined in 4.26. The details and the extensibility of the virtual concatenation method to the AU-4s are under study.

#### 4.11 TU-3 Pointer:

The TU-3 pointer provides a method of allowing flexible and dynamic alignment of VC-3 within the TU-3 frame, independent of the actual content of the VC-3.

## 4.12 TU-3 Pointer Location:

Three individual TU-3 pointers are contained in three separate H1, H2 and H3 bytes as shown in figure 4.9.

#### 4.13 TU-3 Pointer Value:

The TU-3 pointer value contained in H1 and H2 designates the location of the byte where the VC-3 begins. The two bytes allocated to the pointer function can be viewed as one word as shown in figure 4.3. The last ten bits (bits 7-16) of the pointer word carry the pointer value. The TU-3 pointer value is a binary number with a range of 0-764 which indicates the offset between the pointer and the first byte of the VC-3 as shown in figure 4.9.

Figure 4.9 TU-3 Pointer Offset Numbering

# 4.14 Frequency Justification:

If there is a frequency offset between the TU-3 frame rate and that of the VC-3, then the pointer value will be incremented or decremented as needed accompanied by a corresponding positive or negative justification byte. Consecutive pointer operations must be separated by at least three frames in which the pointer value remains constant.

If the frame rate of the VC-3 is too slow with respect to that of the TU-3 frame rate, then the alignment of the VC-3 must periodically slip back in time and the pointer must be incremented by one. This operation is indicated by inverting bits 7, 9, 11, 13 and 15 (I-bits) of the pointer word to allow 5-bit majority voting at the receiver. A positive justification byte appears immediately after the individual H3 byte in the TU-3 frame containing inverted I-bits. Subsequent TU-3 pointers will contain the new offset.

If the frame rate of the VC-3 is too fast with respect to that of the TU-3 frame rate, then the alignment of the VC-3 must be periodically advanced in time and the pointer must be decremented by one. This operation is indicated by inverting bits 8, 10, 12, 14 and 16 (D-bits) of

the pointer word to allow 5-bit majority voting at the receiver. A negative justification byte appears in the individual H3 byte in the TU-3 frame containing inverted D-bits. Subsequent TU-3 pointers will contain the new offset.

#### 4.15 New Data Flag (NDF):

Bits 1-4 (N-bits) of the pointer word carry an NDF, which allows an arbitrary change of the value of the pointer if that change is due to a change in the VC-3. Four bits are allocated to the flag to allow error correction. Normal operation is indicated by a "0110" code in the N-bits. NDF is indicated by inversion of the N-bits to "1001". An NDF should be interpreted as enabled when three or more of the four bits match the pattern "1001". An NDF should be interpreted as disabled when three or more of the four bits match the pattern "0110". The remaining values (i.e. "0000", "0011", "0101", "1010", "1100" and "1111") should be interpreted as invalid. The new alignment is indicated by the pointer value accompanying the NDF and takes effect at the offset indicated.

#### 4.16 Pointer Generation:

The following summarizes the rules for generating the TU-3 pointers:

- During normal operation, the pointer locates the start of the VC-3 within the TU-3 frame. The NDF is set to "0110".

- The pointer value can only be changed by operation 3, 4 or 5.

- If a positive justification is required, the current pointer value is sent with the I-bits inverted and the subsequent positive justification opportunity is filled with dummy information. Subsequent pointers contain the previous pointer value incremented by one. If the previous pointer is at its maximum value, the subsequent pointer is set to zero. No subsequent increment or decrement operation is allowed for at least three frames following this operation.

- If a negative justification is required, the current pointer value is sent with the D-bits inverted and the subsequent negative justification opportunity is overwritten with actual data. Subsequent pointers contain the previous pointer value decremented by one. If the previous pointer value is zero, the subsequent pointer is set to its maximum value. No subsequent increment or decrement operation is allowed for at least three frames following this operation.

- If the alignment of the VC-3 changes for any reason other than rules 3 or 4, the new pointer value shall be sent accompanied by the NDF set to "1001". The NDF only appears in the first frame that contains the new value. The new VC-3 location begins at the first occurrence

of the offset indicated by the new pointer. No subsequent increment or decrement operation is allowed for at least three frames following this operation.

# **4.17 Pointer Interpretation:**

The following summarizes the rules for interpreting the TU-3 pointers:

- During normal operation the pointer locates the start of the VC-3 within the TU-3 frame.

- Any variation from the current pointer value is ignored unless a consistent new value is received three times consecutively or it is preceded by one of rules 3, 4 or 5. Any consistent new value received three times consecutively overrides (i.e. takes priority over) rules 3 or 4.

- If the majority of the I-bits of the pointer word are inverted, a positive justification is indicated. Subsequent pointer values shall be incremented by one.

- If the majority of the D-bits of the pointer word are inverted, a negative justification is indicated. Subsequent pointer values shall be decremented by one.

- If the NDF is interpreted as enabled, then the coincident pointer value shall replace the current one at the offset indicated by the new pointer value unless the receiver is in a state that corresponds to a loss of pointer.

- **4.18 TU-2/TU-1 Pointer:** The TU-1 and TU-2 pointers provide a method of allowing flexible and dynamic alignment of the VC-2/VC-1 within the TU-1 and TU-2 multi-frames independent of the actual contents of the VC-2/VC-1.

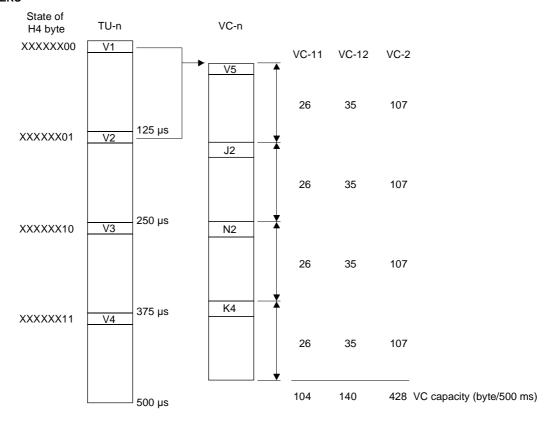

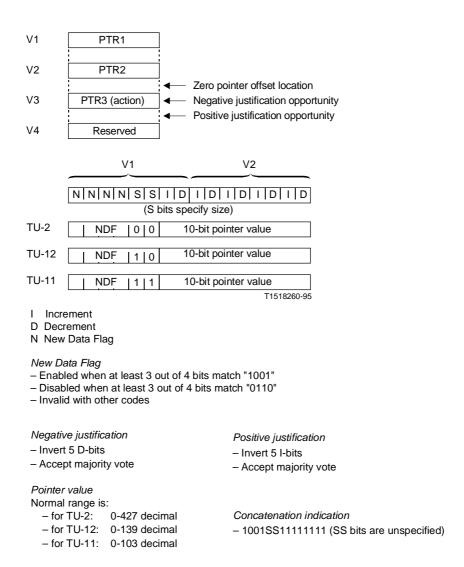

- **4.19 TU-2/TU-1 Pointer Location:** The TU-2/TU-1 pointers are contained in the V1 and V2 bytes as illustrated in figure 4.10.

#### 4.20 TU-2/TU-1 Pointer Value:

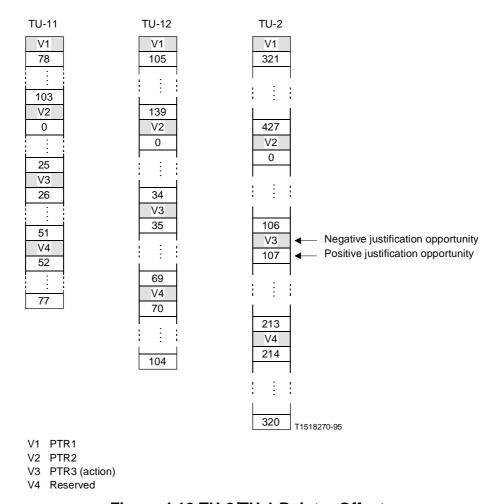

The Tributary Unit pointer word is shown in figure 4.11. The two S bits (bits 5 and 6) indicate the Tributary Unit type. The pointer value (bits 7-16) is a binary number, which indicates the offset from V2 to the first byte of the VC-2/VC-1. The range of the offset is different for each of the Tributary Unit sizes as illustrated in figure 4.12. The pointer bytes are not counted in the offset calculation.

Tributary unit Virtual container VC

V1

VC Pointer 1 VC Pointer 2 VC Pointer 3 (action) V2 V3

Reserved

T1518250-95

NOTE - V1, V2, V3 and V4 bytes are part of the TU-n and are terminated at the pointer processor.

Figure 4.10 Virtual Container Mapping In Multi-framed Tributary Unit

Figure 4.11 TU-2/TU-1 Pointer Coding

#### 4.21 TU-2/TU-1 Frequency Justification:

The TU-2/TU-1 pointer is used to frequency justify the VC-2/VC-1 exactly in the same way that the TU-3 pointer is used to frequency justify the VC-3. A positive justification opportunity immediately follows the V3 byte. Additionally, V3 serves as the negative justification opportunity such that when the opportunity is taken, V3 is overwritten by data. This is also shown in Fig.4.12. The indication of whether or not a justification opportunity has been taken is provided by the I- and D-bits of the pointer in the current Tributary Unit multi-frame. The value contained in V3 when not being used for a negative justification is not defined. The receiver is required to ignore the value contained in V3 whenever it is not used for negative justification.

#### 4.22 New Data Flag (NDF):

Bits 1-4 (N-bits) of the pointer word carry an NDF. It is the mechanism, which allows an arbitrary change of the value of a pointer. As with the TU-3 pointer NDF, the normal value is "0110", and the value "1001" indicates a new alignment for the VC-n, and possibly new size. An NDF should be interpreted as enabled when three or more of the four bits match the pattern "1001". An NDF

should be interpreted as disabled when three or more of the four bits match the pattern "0110". The remaining values (i.e. "0000", "0011", "0101", "1010", "1100" and "1111") should be interpreted as invalid. The new alignment is indicated by the pointer value and size value accompanying the NDF and takes effect at the offset indicated.

# **4.23 TU-2/TU-1 Pointer Generation And Interpretation:**

Figure 4.12 TU-2/TU-1 Pointer Offsets

The rules for generating and interpreting the TU-2/TU-1 pointer for the VC-2/VC-1 are an extension to the rules provided in Fig. 4.16 and Fig. 4.17 for the TU-3 pointer with the following modifications:

The term TU-3 is replaced with TU-2/TU-1 and the term VC-3 is replaced with VC-2/VC-1.

#### 4.24 TU-2 Concatenation:

TU-2s may be concatenated to form a TU-2-mc (m concatenated TU-2s) when a payload requires more than a Container-2. This forms a multi Container-2 payload, which is carried in a single VC-2-mc. The rules by which TU-2s can be concatenated are separated into two categories:

- Concatenation of contiguous TU-2s in the higher order VC-3;

- Virtual concatenation of TU-2s in the higher order VC-4.

## 4.25 Concatenation Of Contiguous TU-2s In The Higher Order VC-3:

TU-2s are contiguous in time in the higher order VC-3. The first TU-2 of an TU-2-mc shall have a normal range of pointer values. All subsequent TU-2s within the TU-2-mc shall have their pointer set to the Concatenation Indication ("1001" in bits 1-4, bits 5-6 unspecified, and all ones in bits 7-16 of the TU-2 pointer). The Concatenation Indication indicates that the TU-2 pointer processor performs all the operations as indicated by the first TU-2 pointer in the TU-2-mc. With this type of concatenation the VC-2-mc contains a single Virtual Container POH which appears in VC-2 #1 of the VC-2-mc.

With virtual concatenation (see 8.3.6.2), the available capacity of the VC-2-mc is lower than that with contiguous concatenation due to the fact that with the virtual concatenation each VC-2 carries its own POH contrary to contiguous concatenation where only the VC-2 # 1 of the VC-2-mc carries its own POH. In order to be able to interconnect VC-2-mcs using different types of concatenation, the mapping of signals in VC-2-mcs should be based on the lower available capacity, namely the capacity of VC-2-mc based on virtual concatenation. Stuffing bytes should be inserted in the VC-2-mc payload based upon contiguous concatenation to accommodate the difference in capacity.

#### 4.26 Virtual Concatenation Of TU-2s In The Higher Order VC-4:

This method of concatenation allows for the transport of a single VC-2-mc in  $m \times TU$ -2 without the use of Concatenation Indication in the pointer bytes. The method only requires the path termination equipment to provide concatenation functionality.

Virtual concatenation requires the concatenated Tributary Unit signals at the origin of the path to be launched with the same pointer value. The so formed Tributary Units at each interface shall be kept in a single higher order VC-4.

When the higher order VC-4 is terminated, the restrictions that apply in passing the concatenated Tributary Units from one interface to another is that all of the concatenated

Tributary Units are connected to a single higher order VC-4 and that the time sequencing of the concatenated Tributary Units is not altered.

Differences in delay of the individual concatenated VC-2 signals may occur due to pointer processing at intermediate equipment. The maximum difference in pointer value within a concatenated group at any interface is for further study. At the path termination the VC-2-mc can be reconstructed by using the pointer values for alignment. Each concatenated VC-2 signal will carry its own POH. At the VC-2-mc path termination, the individual BIP-2s are aggregated to give a single BIP error monitor.

**4.27 TU-2/TU-1 Sizes:** Bits 5 and 6 of TU-2/TU-1 pointer indicate the size of the TU-n. Three sizes are currently provided; they are defined in Table 4.1.

| Size                                                        | Designation | TU-n pointer range (in 500 μs) |  |  |  |

|-------------------------------------------------------------|-------------|--------------------------------|--|--|--|

| 00                                                          | TU-2        | 0-427                          |  |  |  |

| 10                                                          | TU-12       | 0-139                          |  |  |  |

| 11                                                          | TU-11       | 0-103                          |  |  |  |

| NOTE – This technique is only used at the TU-2/TU-1 levels. |             |                                |  |  |  |

Table 4.1 TU-2/TU-1 Sizes

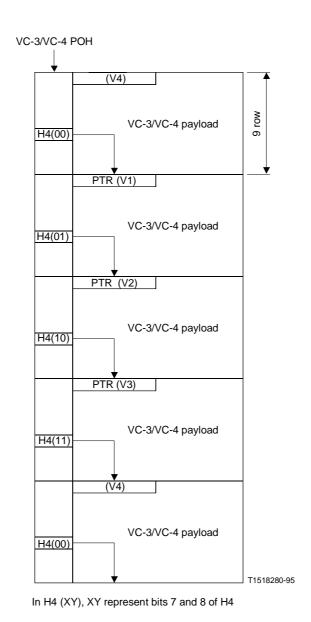

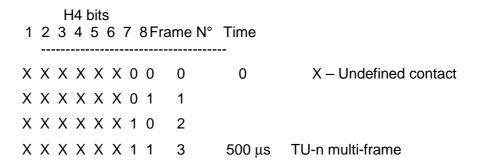

Figure 4.13 TU-1/2 500 µs Multi-frame Indication Using H4 Byte

# 4.28 TU-2/TU-1 Multi-frame Indication Byte:

Figure 4.14 Tributary Unit Multi-frame Indicator Byte (H4) Coding Sequence

The value of the H4 byte, read from the VC-4/VC-3 POH, identifies the frame phase of the next VC-4/VC-3 payload as shown in Fig. 4.13. The coding of the H4 byte is illustrated in Fig. 4.14.

# **Review Questions:**

- 1. Explain the purpose and meaning of pointer.

- 2. What do you understand by positive and negative justification?

- 3. By using H1, H2 and H3 bytes in AU-4 pointer and AU-3 pointer, explain how pointer is useful for offset numbering?

- 4. Pointer is 16 bits with increment and decrement bits. How these bits are used for pointer indication?

- 5. What are the rules for generation and interpretation of TU-3 pointer?

- 6. Explain TU-2,TU12 pointer

\*\*\*\*

# **Chapter 5**

# **Network Topologies**

Objectives: By going through this chapter, the trainee must be in a position to understand

1. Different types of networks used for SDH

Network topologies can be divided into four main types as under,

- String or Bus

- Ring or Loop

- Star

- Mesh

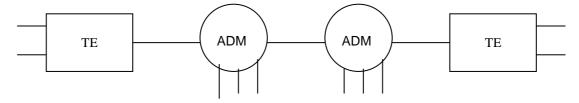

## **5.1 String Network:**

In a String network, the traffic is transported by a succession of interconnection nodes. The services (Voice, Data, Video) can be added or dropped at any node in the chain. The two end nodes are called terminal nodes and can be formed by either terminal multiplexers or line terminals. The intermediate nodes can by either add and drop nodes, containing ADMs (Add/Drop Multiplexers) or regenerating nodes, containing regenerators. String networks are often called linear networks for applications such as railway, highway and pipe line networks.

TE: Terminal Multplexer

ADM: Add & Drop Multiplexer

Figure 5.1 String Network

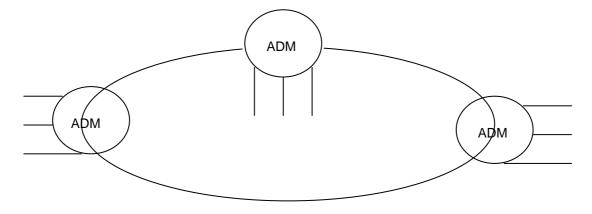

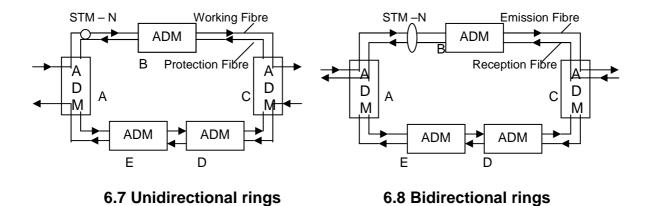

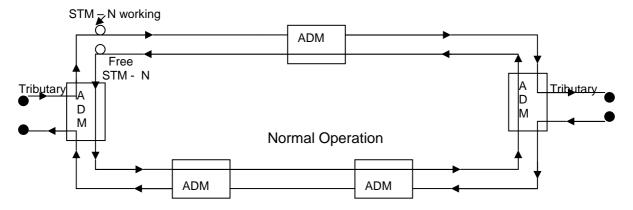

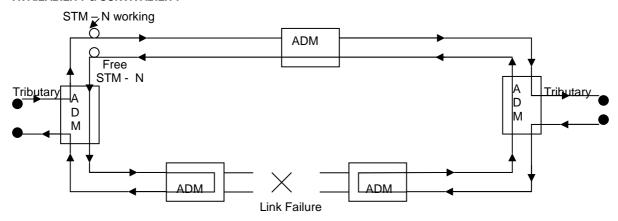

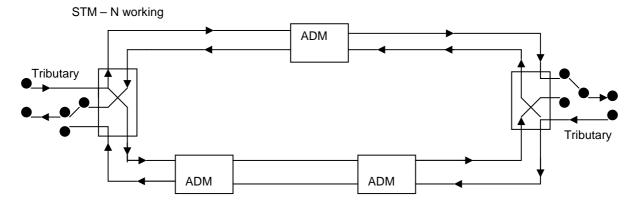

### 5.2 Ring Network:

A Ring network is a string looped back on itself, formed only of ADM nodes, with no terminal nodes. This type network plays an important role because of the network's self healing mechanisms that operate at very high speed (<50 milliseconds), when the network fails due to faults like cable breakage, power failure, fire in a node etc. Ring networks have a wide range of applications from access networks to LAN (Local Area Network), WAN (Wide Area Network) and national networks.

#### 5.3 Star Network:

In a Star network, all the traffic passes through a central node, called the hub, which is generally a cross connect equipment. The main disadvantage of the star topology is the weakness of the network. If the hub fails, no traffic can be transported among the various branches (or links) of the star. This type of topology is commonly used in subscriber access networks.

**Figure 5.2 Ring Network**

Figure 5.3 Star Net Work

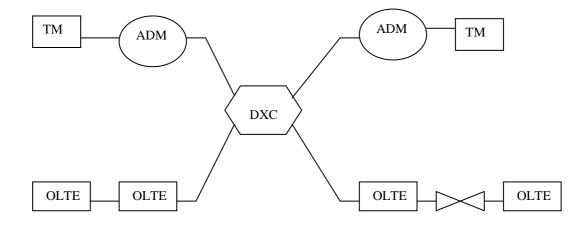

# 5.4 Mesh Network:

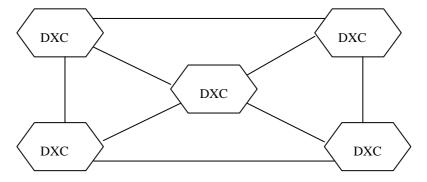

Figure 5.4 Mesh Network

#### **NETWORK TOPOLOGIES**

In a meshed network each node is interconnected to at least two others by one or more links. The nodes of meshed network mainly contain cross-connect equipment. Meshed networks are very useful in SDH, because of their reflex type self heading mechanisms ( <200 milliseconds) with the cross connect equipment or network restoration through re-routing ( assisted by network manager). Meshed networks are mainly used for national networks.

# **Review Questions:**

1. Explain the different types of networks used in SDH.

\*\*\*\*

## Chapter 6

# **Availability and Survivability**

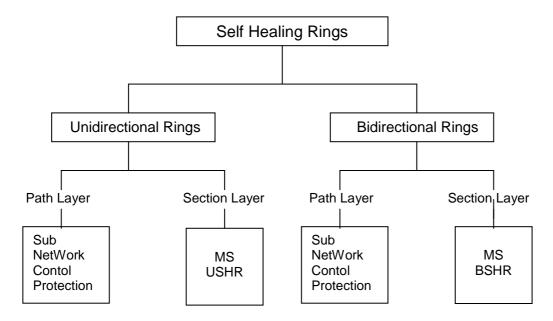

**Objectives:** By going through this chapter, the trainee must be in a position to understand

- 1. 1.Protection categories as defined in ITU-T Rec. G.803.

- 2. 2. Types of protections and applications

- 3. Self healing mechanism

- 4. Ring network protection- self healing ring protection

- 5. Multiple ring networks

# 6.1 Network Availability Enhancement Techniques:

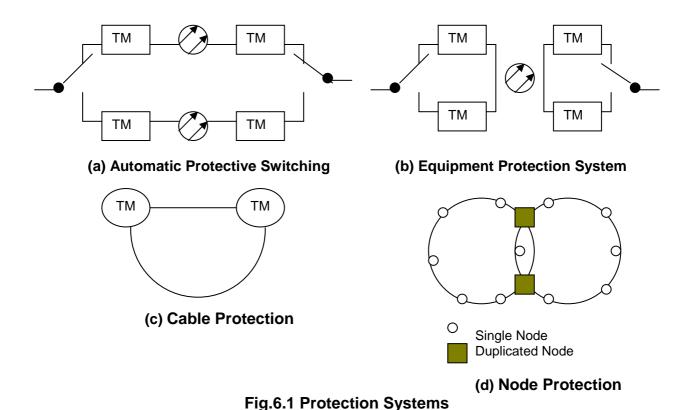

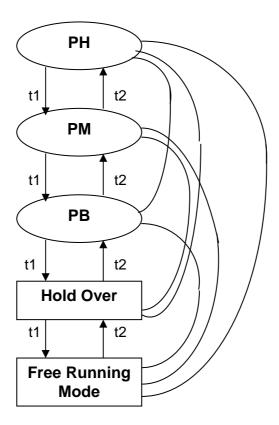

The ITU-T Recommendation G.803 describes the architectural features of the main strategies, which may by used to enhance the availability of a transport network. This availability enhancement can be performed through the following two main mechanisms.