## **TAS2505 Application Reference Guide**

# **Reference Guide**

Literature Number: SLAU472 February 2013

## **TAS2505 Device Overview**

- Chapter 1: Device Overview

- Chapter 2: TAS2505 Application

- Chapter 3: Device Initialization

- Chapter 4: Example Setups

- Chapter 5: Register Map and Descriptions

### Features:

- Digital input mono speaker amp

- Supports 8-kHz to 96-kHz Sample Rates

- Mono Class-D BTL Speaker Driver (2.0 W Into 4  $\Omega$  or 1.7 W Into 8  $\Omega$ )

- Mono Headphone/Lineout Driver

- Two Single-Ended Inputs With Output Mixing and Level Control

- Embedded Power-on-Reset

- Integrated LDO

- Programmable Digital Audio Processing Blocks for Bass Boost, Treble, EQ With up to Six Biquads for Playback

- Integrated PLL Used for Programmable Digital Audio Processing Blocks

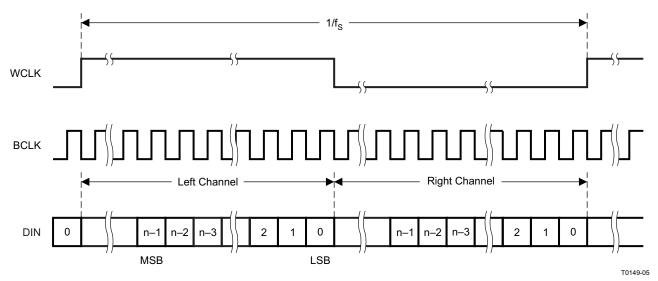

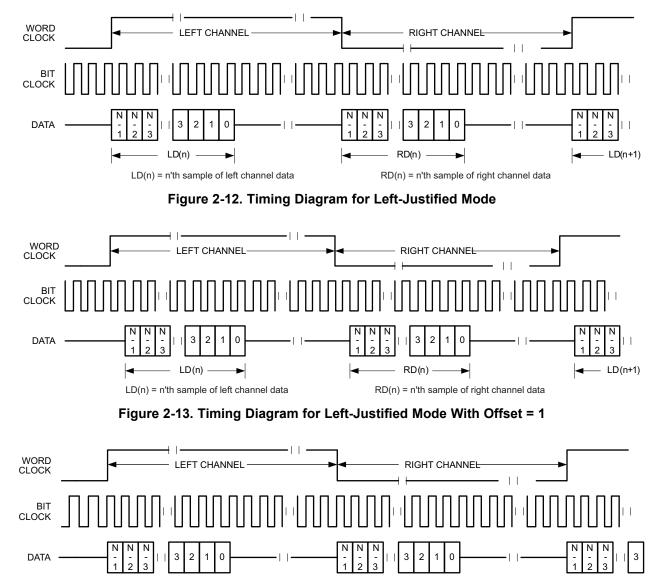

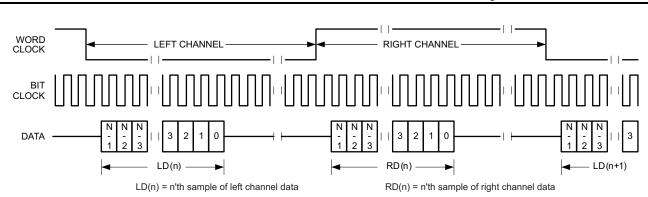

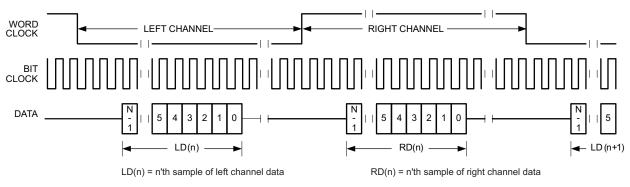

- I<sup>2</sup>S, Left-Justified, Right-Justified, DSP, and TDM Audio Interfaces

- I<sup>2</sup>C and SPI control with auto-increment

- Full Power-Down Control

- Power Supplies:

- Analog: 1.5 V-1.95 V

- Digital Core: 1.65 V–1.95 V

- Digital I/O: 1.1 V–3.6 V

- Class-D: 2.7 V–5.5 V (SPKVDD  $\geq$  AVDD)

- 4mm × 4mm 24-Pin QFN Package

## **Applications:**

- Portable Audio Devices

- · White goods

- Portable Navigation Devices

## 1.1 Description

The TAS2505 is a low power digital input speaker amp with support for 24-bit digital I2S data mono playback.

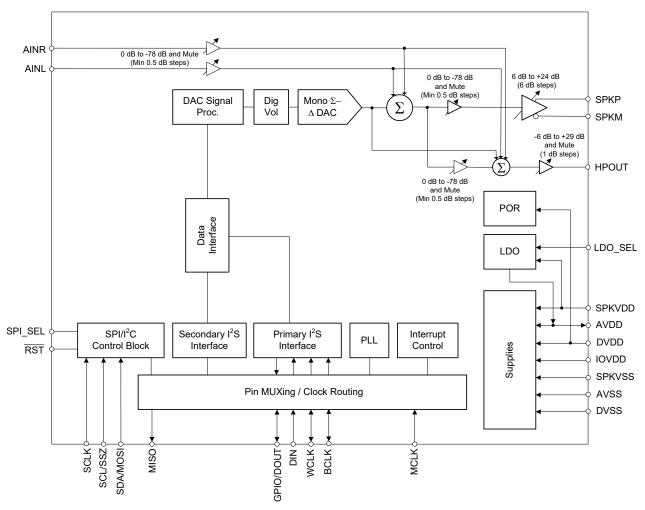

In addition to driving a speaker amp upto 4- $\Omega$ , the device also features a mono headphone driver and a programmable digital-signal processing block. The digital audio data format is programmable to work with popular audio standard protocols (I<sup>2</sup>S, left/right-justified) in master, slave, DSP and TDM modes. The programmable digital-signal processing block can support Bass boost, treble, or EQ functions. An on-chip PLL provides the high-speed clock needed by the digital signal-processing block. The volume level can be controlled by register control. The audio functions are controlled using the I<sup>2</sup>C<sup>TM</sup> serial bus or SPI bus. The device includes an on-board LDO that runs off the speaker power supply to handle all internal device analog and digital power needs. The included POR as power-on-resetcircuit reliably resets the device into its default state so no external reset is required at normal usage; however, the device does have a reset pin for more complex system initialization needs. The device also includes two analog inputs for mixing and MUXing in both speaker and headphone analog paths.

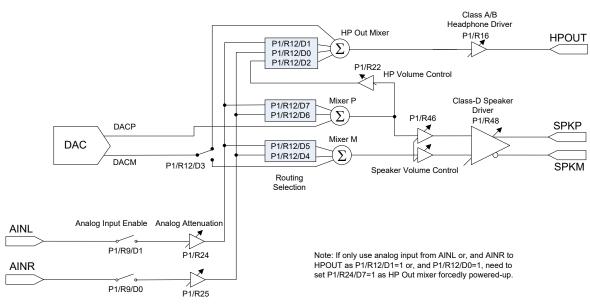

Figure 1-1. Simplified Block Diagram

The device can cover operations from 8kHz mono playback to mono 96kHz DAC playback, making it ideal for portable battery-powered audio and telephony applications. The playback path offers signal processing blocks for filtering and effects, flexible mixing of analog input signals as well as programmable volume controls. The voltage supply range for theTAS2505 for analog is 1.5V–1.95V, and for digital it is 1.65V–1.95V. To ease system-level design, a low-dropout regulator (LDO) is integrated to generate the appropriate analog supply from input voltages ranging from 2.7V to 5.5V. Digital I/O voltages are supported in the range of 1.1V–3.6V. The required internal clock of the TAS2505 can be derived from

#### Typical Circuit Configuration

multiple sources, including the MCLK, BCLK or GPIO/DOUT pins or the output of the internal PLL, where the input to the PLL again can be derived from the MCLK, BCLK or GPIO/DOUT pins. Although using the internal, fractional PLL ensures the availability of a suitable clock signal, it is not recommended for the lowest power settings. The PLL is highly programmable and can accept available input clocks in the range of 512kHz to 50MHz.

The device is available in the 4mm × 4mm, 24-pin QFN package.

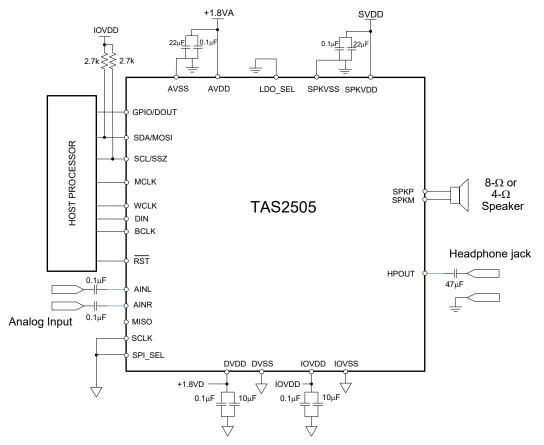

## 1.2 Typical Circuit Configuration

Figure 1-2. Typical Circuit Configuration

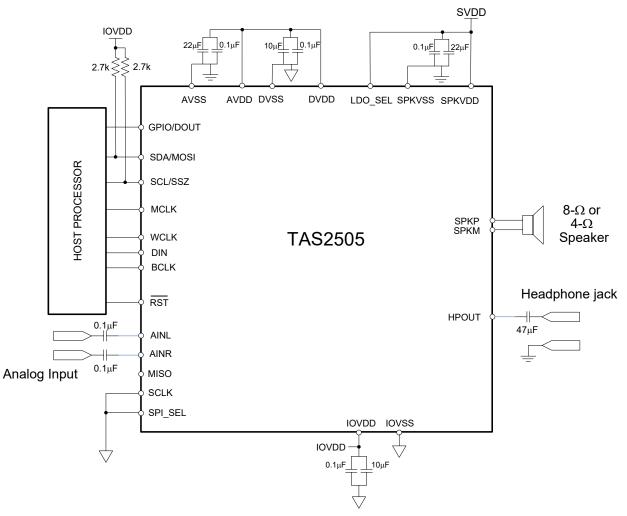

## 1.3 Circuit Configuration with Internal LDO

Figure 1-3. Application Schematics for LDO

5

## **TAS2505** Application

## 2.1 Terminal Descriptions

## 2.1.1 Digital Pins

Only a small number of digital pins are dedicated to a single function; whenever possible, the digital pins have a default function, and also can be reprogrammed to cover alternative functions for various applications.

The fixed-function pins are RST LDO\_SEL and the SPI\_SEL pin, which are HW control pins. Depending on the state of SPI\_SEL, the two control-bus pins SCL/SSZ and SDA/MOSI are configured for either I<sup>2</sup>C or SPI protocol.

Other digital IO pins can be configured for various functions via register control. An overview of available functionality is given in Section 2.1.3.

## 2.1.2 Analog Pins

Analog functions can also be configured to a large degree. For minimum power consumption, analog blocks are powered down by default. The blocks can be powered up with fine granularity according to the application needs.

## 2.1.3 Multifunction Pins

Table 2-1 shows the possible allocation of pins for specific functions. The PLL input, for example, can be programmed to be any of 4 pins (MCLK, BCLK, DIN, GPIO).

|   |                              | 1                                  | 2                   | 3    | 4    | 5             | 6                | 7    |

|---|------------------------------|------------------------------------|---------------------|------|------|---------------|------------------|------|

|   | Pin Function                 | MCLK                               | BCLK                | WCLK | DIN  | GPIO<br>/DOUT | SCLK             | MISO |

| Α | PLL Input                    | S <sup>(1)</sup>                   | S <sup>(2)</sup>    |      | Е    |               | S <sup>(3)</sup> |      |

| В | Codec Clock Input            | S <sup>(1)</sup> ,D <sup>(4)</sup> | S <sup>(2)</sup>    |      |      |               | S <sup>(3)</sup> |      |

| С | I <sup>2</sup> S BCLK input  |                                    | S <sup>(2)</sup> ,D |      |      |               |                  |      |

| D | I <sup>2</sup> S BCLK output |                                    | E <sup>(5)</sup>    |      |      |               |                  |      |

| Е | I <sup>2</sup> S WCLK input  |                                    |                     | E, D |      |               |                  |      |

| F | I <sup>2</sup> S WCLK output |                                    |                     | Е    |      |               |                  |      |

| G | I <sup>2</sup> S DIN         |                                    |                     |      | E, D |               |                  |      |

| I | General Purpose Output I     |                                    |                     |      |      | E             |                  |      |

| I | General Purpose Output II    |                                    |                     |      |      |               |                  | E    |

| J | General Purpose Input I      |                                    |                     |      | Е    |               |                  |      |

| J | General Purpose Input II     |                                    |                     |      |      | E             |                  |      |

| J | General Purpose Input III    |                                    |                     |      |      |               | E                |      |

Table 2-1. Multifunction Pin Assignments

<sup>(1)</sup> S<sup>(1)</sup>: The MCLK pin can drive the PLL and Codec Clock inputs **simultaneously**.

<sup>(2)</sup> S<sup>(2)</sup>: The BCLK pin can drive the PLL and Codec Clock and audio interface bit clock inputs **simultaneously**.

$^{(3)}$  S<sup>(3)</sup>: The GPIO/DOUT pin can drive the PLL and Codec Clock inputs **simultaneously**.

<sup>(4)</sup> D: Default Function

<sup>(5)</sup> E: The pin is **exclusively** used for this function, no other function can be implemented with the same pin. (If GPIO/DOUT has been allocated for General Purpose Output, it cannot be used as the INT1 output at the same time.)

|   |                                       | 1    | 2    | 3    | 4   | 5             | 6    | 7    |

|---|---------------------------------------|------|------|------|-----|---------------|------|------|

|   | Pin Function                          | MCLK | BCLK | WCLK | DIN | GPIO<br>/DOUT | SCLK | MISO |

| κ | INT1 output                           |      |      |      |     | E             |      | E    |

| L | INT2 output                           |      |      |      |     | E             |      | E    |

| М | Secondary I <sup>2</sup> S BCLK input |      |      |      |     | E             | Е    |      |

| Ν | Secondary I <sup>2</sup> S WCLK input |      |      |      |     | E             | Е    |      |

| 0 | Secondary I <sup>2</sup> S DIN        |      |      |      |     | E             | Е    |      |

| Р | Secondary I <sup>2</sup> S BCLK OUT   |      |      |      |     | E             |      | E    |

| Q | Secondary I <sup>2</sup> S WCLK OUT   |      |      |      |     | E             |      | E    |

| R | Secondary I <sup>2</sup> S DOUT       |      |      |      |     |               |      | E    |

| S | Aux Clock Output                      |      |      |      |     | E             |      | E    |

## Table 2-1. Multifunction Pin Assignments (continued)

7

## 2.1.4 Register Settings for Multifunction Pins

To configure the settings seen in Table 2-1, please see the letter-number combination in Table 2-2 for the appropriate registers to modify. In Table 2-2, the letter/number combination represents the row and the column number from Table 2-1 in bold type.

Please be aware that more settings may be necessary to obtain a full interface definition matching the application requirement (see Page 0, Register 25 to 33).

|    | Description                          | Required Register Setting                                                            |    | Description                                           | Required Register<br>Setting                                                         |

|----|--------------------------------------|--------------------------------------------------------------------------------------|----|-------------------------------------------------------|--------------------------------------------------------------------------------------|

| A1 | PLL Input on MCLK                    | Page 0, Register 4, Bits D3-<br>D2 = 00                                              | K7 | INT1 output on MISO                                   | Page 0, Register 55, Bits<br>D4-D1 = 0100                                            |

| A2 | PLL Input on BCLK                    | Page 0, Register 4, Bits D3-<br>D2 = 01                                              | L5 | INT2 output GPIO/DOUT                                 | Page 0, Register 52, Bits<br>D5-D2 = 0110                                            |

| A4 | PLL Input on DIN/MFP1                | Page 0, Register 54, Bits<br>D2-D1 = 01<br>Page 0, Register 4, Bits D3-<br>D2 = 11   | L7 | INT2 output on MISO                                   | Page 0, Register 55, Bits<br>D4-D1 = 0101                                            |

| A5 | PLL Input on GPIO/DOUT               | Page 0, Register 52, Bits<br>D5-D2 = 0001<br>Page 0, Register 4, Bits D3-<br>D2 = 10 | M5 | Secondary I <sup>2</sup> S BCLK input<br>on GPIO/DOUT | Page 0, Register 52, Bits<br>D5-D2 = 0001<br>Page 0, Register 31, Bits<br>D6-D5 = 00 |

| B1 | Codec Clock Input on<br>MCLK         | Page 0, Register 4, Bits D1-<br>D0 = 00                                              | M6 | Secondary I <sup>2</sup> S BCLK input<br>on SCLK      | Page 0, Register 56, Bits<br>D2-D1 = 01<br>Page 0, Register 31, Bits<br>D6-D5 = 01   |

| B2 | Codec Clock Input on<br>BCLK         | Page 0, Register 4, Bits D1-<br>D0 = 01                                              | N5 | Secondary I <sup>2</sup> S WCLK in on GPIO/DOUT       | Page 0, Register 52, Bits<br>D5-D2 = 0001<br>Page 0, Register 31, Bits<br>D4-D3 = 00 |

| B5 | Codec Clock Input on<br>GPIO/DOUT    | Page 0, Register 52, Bits<br>D5-D2 = 0001<br>Page 0, Register 4, Bits D1-<br>D0 = 10 | N6 | Secondary I <sup>2</sup> S WCLK in on SCLK            | Page 0, Register 56, Bits<br>D2-D1 = 01<br>Page 0, Register 31, Bits<br>D4-D3 = 01   |

| C2 | I <sup>2</sup> S BCLK input on BCLK  | Page 0, Register 27, Bit D3<br>= 0                                                   | O5 | Secondary I <sup>2</sup> S DIN on<br>GPIO/DOUT        | Page 0, Register 52, Bits<br>D5-D2 = 0001<br>Page 0, Register 31, Bit D0<br>= 0      |

| D2 | I <sup>2</sup> S BCLK output on BCLK | Page 0, Register 27, Bit D3<br>= 1                                                   | O6 | Secondary I <sup>2</sup> S DIN on<br>SCLK             | Page 0, Register 56, Bits<br>D2-D1 = 01<br>Page 0, Register 31, Bit D0<br>= 1        |

| E3 | I <sup>2</sup> S WCLK input on WCLK  | Page 0, Register 27, Bit D2<br>= 0                                                   | P5 | Secondary I <sup>2</sup> S BCLK OUT<br>on GPIO/DOUT   | Page 0, Register 52, Bits<br>D5-D2 = 1000                                            |

| F3 | I <sup>2</sup> S WCLK output WCLK    | Page 0, Register 27, Bit D2<br>= 1                                                   | P7 | Secondary I <sup>2</sup> S BCLK OUT<br>on MISO        | Page 0, Register 55, Bits<br>D4-D1 = 1001                                            |

| G4 | I <sup>2</sup> S DIN on DIN          | Page 0, Register 54, Bits<br>D2-D1 = 01                                              | Q5 | Secondary I <sup>2</sup> S WCLK OUT<br>on GPIO/DOUT   | Page 0, Register 52, Bits<br>D5-D2 = 1001                                            |

| H5 | N/A                                  |                                                                                      | Q7 | Secondary I <sup>2</sup> S WCLK OUT<br>on MISO        | Page 0, Register 55, Bits<br>D4-D1 = 1010                                            |

| Table 2-2. Multifunction P | in Register Configuration |

|----------------------------|---------------------------|

|----------------------------|---------------------------|

|    | Description                        | Required Register Setting                 |    | Description                             | Required Register<br>Setting              |  |  |

|----|------------------------------------|-------------------------------------------|----|-----------------------------------------|-------------------------------------------|--|--|

| 15 | General Purpose Out I on GPIO/DOUT | Page 0, Register 53, Bits<br>D3-D1 = 010  | R7 | Secondary I <sup>2</sup> S DOUT on MISO | Page 0, Register 55, Bits<br>D4-D1 = 1000 |  |  |

| 17 | General Purpose Out II<br>on MISO  | Page 0, Register 55, Bits<br>D4-D1 = 0010 | S5 | Aux Clock Output on<br>GPIO/DOUT        | Page 0, Register 52, Bits<br>D5-D2 = 0100 |  |  |

| J4 | General Purpose In I on DIN        | Page 0, Register 54, Bits<br>D2-D1 = 10   | S7 | Aux Clock Output on MISO                | Page 0, Register 55, Bits<br>D4-D1 = 0011 |  |  |

| J5 | General Purpose In II on GPIO/DOUT | Page 0, Register 52, Bits<br>D5-D2 = 0010 |    |                                         |                                           |  |  |

| J6 | General Purpose In III on SCLK     | Page 0, Register 56, Bits<br>D2-D1 = 10   |    |                                         |                                           |  |  |

| K5 | INT1 output on<br>GPIO/DOUT        | Page 0, Register 52, Bits<br>D5-D2 = 0101 |    |                                         |                                           |  |  |

Table 2-2. Multifunction Pin Register Configuration (continued)

## 2.2 Audio Analog I/O

The TAS2505 features a mono audio DAC. It supports a wide range of analog interfaces to support different headsets such as  $16-\Omega$  to  $200-\Omega$  impedance and analog line outputs. TheTAS2505 can drive a speaker upto  $4-\Omega$  impedance.

## 2.3 Analog Signals

The TAS2505 analog signals consist of:

- Analog inputs AINR and AINL, which can be used to pass-through or mix analog signals to output stages

- Analog outputs class-D speaker driver and headphone/lineout driver providing output capability for the DAC, AINR, AINL, or a mix of the three

## 2.3.1 Analog Inputs AINL and AINR

AINL (pin 3 or C2) and AINR (pin 4 or B2) are inputs to Mixer P and Mixer M along with the DAC output. Also AINL and AINR can be configured inputs to HP driver. Page1 / register 12 provides control signals for determining the signals routed through Mixer P, Mixer M and HP driver. Input of Mixer P can be attenuated by Page1 / register 24, input of Mixer M can be attenuated by Page1 / register 25 and input of HP driver can be attenuated by Page1 / register 22. Also AINL and AINR can be configured to a monaural differential input with use Mixer P and Mixer M by Page1 / register 12 setting. All the options can be viewed in the functional block diagram, Figure 2-6.

## 2.4 Audio DAC and Audio Analog Outputs

The mono audio DAC consists of a digital audio processing block, a digital interpolation filter, a digital delta-sigma modulator, and an analog reconstruction filter. The high oversampling ratio (normally DOSR is between 32 and 128) exhibits good dynamic range by ensuring that the quantization noise generated within the delta-sigma modulator stays outside of the audio frequency band. Audio analog outputs include mono headphone and lineout and mono class-D speaker outputs. Because the TAS2505 contains a mono DAC, it inputs the mono data from the left channel, the right channel, or a mix of the left and right channels as  $[(L + R) \div 2]$ , selected by page 0, register 63, bits D5–D4. See Figure 1-1 for the signal flow.

## 2.4.1 DAC

The TAS2505 mono audio DAC supports data rates from 8 kHz to 192 kHz. The audio channel of the mono DAC consists of a signal-processing engine with fixed processing blocks, a digital interpolation filter, multibit digital delta-sigma modulator, and an analog reconstruction filter. The DAC is designed to provide enhanced performance at low sampling rates through increased oversampling and image filtering, thereby keeping quantization noise generated within the delta-sigma modulator and observed in the signal images

#### Audio DAC and Audio Analog Outputs

strongly suppressed within the audio band to beyond 20 kHz. To handle multiple input rates and optimize power dissipation and performance, the TAS2505 allows the system designer to program the oversampling rates over a wide range from 1 to 1024 by configuring page 0, register 13 and page 0 / register 14. The system designer can choose higher oversampling ratios for lower input data rates and lower oversampling ratios for higher input data rates.

The TAS2505 DAC channel includes a built-in digital interpolation filter to generate oversampled data for the delta-sigma modulator. The interpolation filter can be chosen from three different types, depending on required frequency response, group delay, and sampling rate.

DAC power up is controlled by writing to page 0, register 63, bit D7 for the mono channel. The monochannel DAC clipping flag is provided as a read-only bit on page 0 / register 39, bit D7.

The DAC path of the TAS2505 features many options for signal conditioning and signal routing:

- Digital volume control with a range of -63.5 to +24dB

- Mute function

In addition to the standard set of DAC features the TAS2505 also offers the following special features:

- Digital auto mute

- Adaptive filter mode

## 2.4.1.1 DAC Processing Blocks

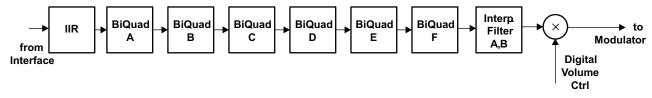

The TAS2505 implements signal-processing capabilities and interpolation filtering via processing blocks. These fixed processing blocks give users the choice of how much and what type of signal processing they may use and which interpolation filter is applied.

The choices among these processing blocks allows the system designer to balance power conservation and signal-processing flexibility. Table 2-3 gives an overview of all available processing blocks of the DAC channel and their properties. The resource-class column gives an approximate indication of power consumption for the digital (DVDD) supply; however, based on the out-of-band noise spectrum, the analog power consumption of the drivers (AVDD) may differ.

The signal-processing blocks available are:

- First-order IIR

- Scalable number of biquad filters

The processing blocks are tuned for common cases and can achieve high image rejection or low group delay in combination with various signal-processing effects such as audio effects and frequency shaping. The available first-order IIR and biquad filters have fully user-programmable coefficients.

|                         |                      | -       |                              |                      |                   |  |

|-------------------------|----------------------|---------|------------------------------|----------------------|-------------------|--|

| Processing<br>Block No. | Interpolation Filter | Channel | First-Order<br>IIR Available | Number of<br>Biquads | Resource<br>Class |  |

| PRB_P1                  | A                    | Mono    | Yes                          | 6                    | 6                 |  |

| PRB_P2                  | A                    | Mono    | No                           | 3                    | 4                 |  |

| PRB_P3                  | В                    | Mono    | Yes                          | 6                    | 4                 |  |

## Table 2-3. Overview – DAC Predefined Processing Blocks

## 2.4.1.2 DAC Processing Blocks – Signal Chain Details

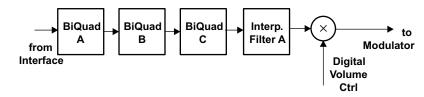

## 2.4.1.2.1 Three Biquads, Filter A

Figure 2-1. Signal Chain for PRB\_P2

## 2.4.1.2.2 Six Biquads, First-Order IIR, Filter A or B

Figure 2-2. Signal Chain for PRB\_P1 and PRB\_P3

## 2.4.1.3 DAC User-Programmable Filters

Depending on the selected processing block, different types and orders of digital filtering are available. Up to six biquad sections are available for specific processing blocks.

The coefficients of the available filters are arranged as sequentially-indexed coefficients in two banks. If adaptive filtering is chosen, the coefficient banks can be switched in real time.

When the DAC is running, the user-programmable filter coefficients are locked and cannot be accessed for either read or write.

However, the TAS2505 offers an adaptive filter mode as well. Setting page 8, register 1, bit D2 = 1 turns on double buffering of the coefficients. In this mode, filter coefficients can be updated through the host and activated without stopping and restarting the DAC. This enables advanced adaptive filtering applications.

In the double-buffering scheme, all coefficients are stored in two buffers (buffers A and B). When the DAC is running and adaptive filtering mode is turned on, setting page 44, register 1, bit D0 = 1 switches the coefficient buffers at the next start of a sampling period. This bit is set back to 0 after the switch occurs. At the same time, page 44, register 1, bit D1 toggles.

The flag in page 44, register 1, bit D1 indicates which of the two buffers is actually in use.

Page 44, register 1, bit D1 = 0: buffer A is in use by the DAC engine; bit D1 = 1: buffer B is in use.

While the device is running, coefficient updates are always made to the buffer not in use by the DAC, regardless of the buffer to which the coefficients have been written.

| DAC Powered<br>Up | Page 44, Reg 1, Bit D1 | Coefficient Buffer in<br>Use | I <sup>2</sup> C Writes to | Will Updates |

|-------------------|------------------------|------------------------------|----------------------------|--------------|

| No                | 0                      | None                         | C1, buffer A               | C1, buffer A |

| No                | 0                      | None                         | C1, buffer B               | C1, buffer B |

| Yes               | 0                      | Buffer A                     | C1, buffer A               | C1, buffer B |

| Yes               | 0                      | Buffer A                     | C1, buffer B               | C1, buffer B |

| Yes               | 1                      | Buffer B                     | C1, buffer A               | C1, buffer A |

| Yes               | 1                      | Buffer B                     | C1, buffer B               | C1, buffer A |

Table 2-4. Adaptive-Mode Filter-Coefficient Buffer Switching

The user-programmable coefficients C1 to C70 for the DAC processing blocks are defined on pages 44 to 46 for buffer A and pages 62 to 64 for buffer B.

The coefficients of these filters are each 24-bit, 2s-complement format, occupying three consecutive 8-bit registers in the register space. Specifically, the filter coefficients are in 1.23 (one dot 23) format with a range from -1.0 (0x800000) to 0.99999988079071044921875 (0x7FFFF).

## 2.4.1.3.1 First-Order IIR Section

The IIR is of first order and its transfer function is given by

$$H(z) = \frac{N_0 + N_1 z^{-1}}{2^{23} - D_1 z^{-1}}$$

(1)

The frequency response for the first-order IIR section with default coefficients is flat.

Table 2-5. DAC IIR Filter Coefficients

| Filter          | Filter Coefficient | DAC Coefficient,<br>Mono Channel   | Default (Reset) Values |

|-----------------|--------------------|------------------------------------|------------------------|

| First-order IIR | N0                 | C65 (Page 46/ registers 28,29,30)  | 0x7FFFFF               |

|                 | N1                 | C66 (Page 46/ registers 32,33,34)  | 0x000000               |

|                 | D1                 | C67 (Page 46 / registers 36,37,38) | 0x000000               |

## 2.4.1.3.2 Biquad Section

The transfer function of each of the biquad filters is given by

$$H(z) = \frac{N_0 + 2 \times N_1 z^{-1} + N_2 z^{-2}}{2^{23} - 2 \times D_1 z^{-1} - D_2 z^{-2}}$$

(2)

## Table 2-6. DAC Biquad Filter Coefficients

| Filter   | Coefficient | Mono DAC Channel                    | Default (Reset) Values |

|----------|-------------|-------------------------------------|------------------------|

| Biquad A | N0          | C1 (Page 44, registers 12, 13, 14)  | 0x7FFFFF               |

|          | N1          | C2 (Page 44, registers 16, 17, 18)  | 0x000000               |

|          | N2          | C3 (Page 44, registers 20, 21, 22)  | 0x000000               |

|          | D1          | C4 (Page 44, registers 24, 25, 26)  | 0x000000               |

|          | D2          | C5 (Page 44, registers 28, 29, 30)  | 0x000000               |

| Biquad B | N0          | C6( Page 44, registers 32, 33, 34)  | 0x7FFFFF               |

|          | N1          | C7 (Page 44, registers 36, 37, 38)  | 0x000000               |

|          | N2          | C8 (Page 44, registers 40, 41, 42)  | 0x000000               |

|          | D1          | C9 (Page 44, registers 44, 45, 46)  | 0x000000               |

|          | D2          | C10 (Page 44, registers 48, 49, 50) | 0x000000               |

| Filter   | Coefficient | Mono DAC Channel                       | Default (Reset) Values |

|----------|-------------|----------------------------------------|------------------------|

| Biquad C | N0          | C11 (Page 44, registers 52, 53, 54)    | 0x7FFFFF               |

|          | N1          | C12 (Page 44, registers 56, 57, 58)    | 0x000000               |

|          | N2          | C13 (Page 44, registers 60, 61, 62)    | 0x000000               |

|          | D1          | C14 (Page 44, registers 64, 65, 66)    | 0x000000               |

|          | D2          | C15 (Page 44, registers 68, 69, 70)    | 0x000000               |

| Biquad D | N0          | C16 (Page 44, registers 72, 73, 74)    | 0x7FFFFF               |

|          | N1          | C17 (Page 44, registers 76, 77, 78)    | 0x000000               |

|          | N2          | C18 (Page 44, registers 80, 81, 82)    | 0x000000               |

|          | D1          | C19 (Page 44, registers 84, 85, 86)    | 0x000000               |

|          | D2          | C20 (Page 44, registers 88, 89, 90)    | 0x000000               |

| Biquad E | N0          | C21 (Page 44, registers 92, 93, 94)    | 0x7FFFFF               |

|          | N1          | C22 (Page 44, registers 96, 97, 98)    | 0x000000               |

|          | N2          | C23 (Page 44, registers 100, 101, 102) | 0x000000               |

|          | D1          | C24 (Page 44, registers 104, 105, 106) | 0x000000               |

|          | D2          | C25 (Page 44, registers 108, 109, 110) | 0x000000               |

| Biquad F | N0          | C26 (Page 44, registers 112, 113, 114) | 0x7FFFFF               |

|          | N1          | C27 (Page 44, registers 116, 117, 118) | 0x000000               |

|          | N2          | C28 (Page 44, registers 120, 121, 122) | 0x000000               |

|          | D1          | C29 (Page 44, registers 124, 125, 126) | 0x000000               |

|          | D2          | C30 (Page 45, registers 8, 9, 10)      | 0x000000               |

## Table 2-6. DAC Biquad Filter Coefficients (continued)

## 2.4.1.4 DAC Interpolation Filter Characteristics

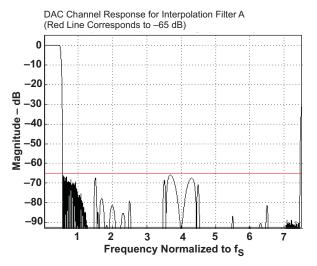

## 2.4.1.4.1 Interpolation Filter A

Filter A is designed for an  $f_s$  up to 48 ksps with a flat pass band of 0 kHz–20 kHz.

|                       | •                                        | •                 |      |

|-----------------------|------------------------------------------|-------------------|------|

| Parameter             | Condition                                | Value (Typical)   | Unit |

| Filter-gain pass band | 0 0.45 f <sub>s</sub>                    | ±0.015            | dB   |

| Filter-gain stop band | 0.55 f <sub>s</sub> 7.455 f <sub>s</sub> | -65               | dB   |

| Filter group delay    |                                          | 21/f <sub>s</sub> | S    |

## Table 2-7. Specification for DAC Interpolation Filter A

Figure 2-3. Frequency Response of DAC Interpolation Filter A

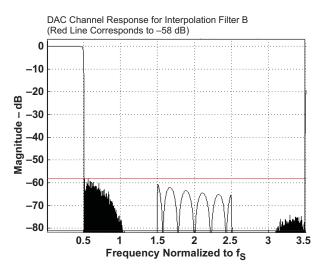

## 2.4.1.4.2 Interpolation Filter B

Filter B is specifically designed for an  $f_s$  up to 96 ksps. Thus, the flat pass-band region easily covers the required audio band of 0 kHz–20 kHz.

| Parameter             | Condition                               | Value (Typical)   | Unit |

|-----------------------|-----------------------------------------|-------------------|------|

| Filter-gain pass band | 0 0.45 f <sub>s</sub>                   | ±0.015            | dB   |

| Filter-gain stop band | 0.55 f <sub>s</sub> 3.45 f <sub>s</sub> | -58               | dB   |

| Filter group delay    |                                         | 18/f <sub>s</sub> | S    |

### Table 2-8. Specification for DAC Interpolation Filter B

Figure 2-4. Frequency Response of Channel Interpolation Filter B

www.ti.com

## 2.4.2 DAC Gain Setting

## 2.4.2.1 PowerTune Modes

As part of the PowerTune strategy, the analog properties of the DAC are adjusted. As a consequence, the full-scale signal swing achieved at the headphone and line outputs must be adjusted. Please see Table 2-9 for the proper gain compensation values across the different combinations.

| DAC PowerTune Mode<br>Control       | PowerTune Mode | Headphone Gain                                                                       |                                                                                     |  |  |

|-------------------------------------|----------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| Page 1,Register 3, Bits (D4-<br>D2) |                | CM = 0.75V, Gain for<br>375mV <sub>RMS</sub> output swing at<br>0dB full scale input | CM = 0.9V, Gain for<br>500mV <sub>RMS</sub> output swing at<br>0dB full scale input |  |  |

| 000                                 | PTM_P3, PTM_P4 | 0                                                                                    | 0                                                                                   |  |  |

| 001                                 | PTM_P2         | 4                                                                                    | 4                                                                                   |  |  |

| 010                                 | PTM_P1         | 14                                                                                   | 14                                                                                  |  |  |

Table 2-9. DAC Gain vs. PowerTune Modes

## 2.4.2.2 DAC Digital-Volume Control

The DAC has a digital volume-control block which implements programmable gain. Each channel has an independent volume control that can be varied from 24 dB to -63.5 dB in 0.5-dB steps. The mono-channel DAC volume can be controlled by writing to page 0, register 65, bits D7–D0. DAC muting and setting up a master gain control to control the mono channel is done by writing to page 0, register 64, bits D3. The gain is implemented with a soft-stepping algorithm, which only changes the actual volume by 0.125 dB per input sample, either up or down, until the desired volume is reached. The rate of soft-stepping can be slowed to one step per two input samples by writing to page 0, register 63, bits D1–D0. Note that the default source for volume-control level settings is controlled by register writes to page 0, register 65.

During soft-stepping, the host does not receive a signal when the DAC has been completely muted. This may be important if the host must mute the DAC before making a significant change, such as changing sample rates. In order to help with this situation, the device provides a flag back to the host via a read-only register, page 0, register 38, bit D4 for the mono channel. This information alerts the host when the part has completed the soft-stepping, and the actual volume has reached the desired volume level. The soft-stepping feature can be disabled by writing to page 0, register 63, bits D1–D0.

If soft-stepping is enabled, the CODEC\_CLKIN signal should be kept active until the DAC power-up flag is cleared. When this flag is cleared, the internal DAC soft-stepping process is complete, and CODEC\_CLKIN can be stopped if desired. (The analog volume control can be ramped down using an internal oscillator.)

## 2.4.3 Interrupts

Some specific events in the TAS2505, which may require host-processor intervention, can be used to trigger interrupts to the host processor. This avoids polling the status-flag registers continuously. The TAS2505 has two defined interrupts, INT1 and INT2, that can be configured by programming page 0, register 48 and page 0, register 49. A user can configure interrupts INT1 and INT2 to be triggered by one or many events, such as:

- Overcurrent condition in headphone drivers/speaker drivers

- Data overflow in the DAC processing blocks and filters

Each of these INT1 and INT2 interrupts can be routed to output pin GPIO. These interrupt signals can either be configured as a single pulse or a series of pulses by programming page 0, register 48, bit D0 and page 0, register 49, bit D0. If the user configures the interrupts as a series of pulses, the events trigger the start of pulses that stop when the flag registers in page 0, register 42 and page 0, register 44 are read by the user to determine the cause of the interrupt.

## 2.4.4 Programming DAC Digital Filter Coefficients

The digital filter coefficients must be programmed through the control interface. All digital filtering for the DAC signal path must be loaded into the RAM before the DAC is powered on. (Note that default ALLPASS filter coefficients for programmable biquads are located in boot ROM. The boot ROM automatically loads the default values into the RAM following a hardware reset (toggling the RST pin) or after a software reset. After resetting the device, loading boot ROM coefficients into the digital filters requires 100 µs of programming time. During this time, reading or writing to page 8 through page 15 for updating DAC filter coefficient values is not permitted. (The DAC should not be powered up until after all of the DAC configurations have been done by the system microprocessor.)

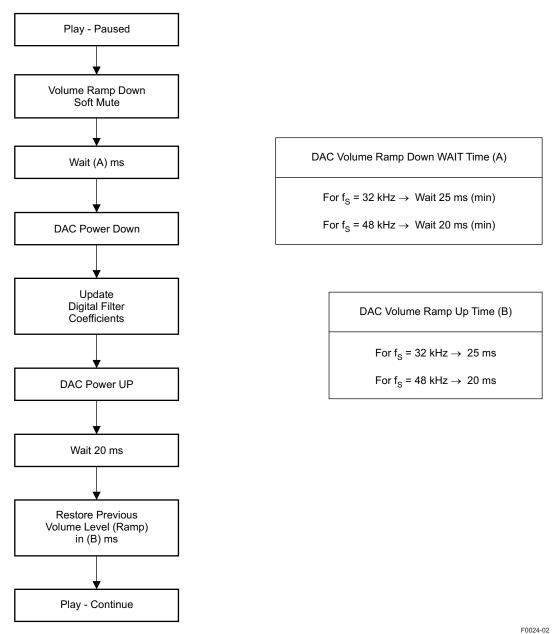

## 2.4.5 Updating DAC Digital Filter Coefficients During PLAY

When it is required to update the DAC digital filter coefficients during play, care must be taken to avoid click and pop noise or even a possible oscillation noise. These artifacts can occur if the DAC coefficients are updated without following the proper update sequence. The correct sequence is shown in Figure 2-5. The values for times listed in Figure 2-5 are conservative and should be used for software purposes.

There is also an adaptive mode, in which DAC coefficients can be updated while the DAC is on. For details, see Section 2.4.1.3.

Figure 2-5. Example Flow For Updating DAC Digital Filter Coefficients During Play

## 2.4.6 Digital Mixing and Routing

The TAS2505 has four digital mixing blocks. Each mixer can provide either mixing or multiplexing of the digital audio data. The first mixer/multiplexer can be used to select input data for the mono DAC from left channel, right channel, or (left channel + right channel) / 2 mixing. This digital routing can be configured by writing to page 0, register 63, bits D5–D4.

## 2.4.7 Analog Audio Routing

The TAS2505 has the capability to route the DAC output to either the headphone or the speaker output. If desirable, both output drivers can be operated at the same time while playing at different volume levels. The TAS2505 provides various digital routing capabilities, allowing digital mixing or even channel swapping in the digital domain. All analog outputs other than the selected ones can be powered down for optimal power consumption.

## 2.4.7.1 Analog Output Volume Control

The output volume control can be used to fine-tune the level of the mixer amplifier signal supplied to the headphone driver or the speaker driver. This architecture supports separate and concurrent volume levels for each of the four output drivers. This volume control can also be used as part of the output pop-noise reduction scheme. This feature is available even if the DAC is powered down.

## 2.4.7.2 Headphone Analog Output Volume Control

For the headphone output, the analog volume control has a range from 0 dB to -78 dB in 0.5-dB steps for most of the useful range plus mute, as shown in Table 2-10. This volume control includes soft-stepping logic.

Changing the analog volume for the headphone is controlled by writing to page 1, register 22, bits D6–D0. Routing the signal from the output of the analog volume control to the input of the headphone power amplifier via Mixer P and Mixer M is done by writing to page 1, register 12, bit D2.

The analog volume-control soft-stepping time is based on the setting in page 0, register 63, bits D1–D0.

Audio DAC and Audio Analog Outputs

| Register<br>Value | Analog<br>Attenuation<br>(dB) | Register<br>Value | Analog<br>Attenuation<br>(dB) | Register<br>Value | Analog<br>Attenuation<br>(dB) | Register<br>Value | Analog<br>Attenuation<br>(dB) |

|-------------------|-------------------------------|-------------------|-------------------------------|-------------------|-------------------------------|-------------------|-------------------------------|

| 0                 | 0.0                           | 30                | -15.0                         | 60                | -30.1                         | 90                | -45.2                         |

| 1                 | -0.5                          | 31                | -15.5                         | 61                | -30.6                         | 91                | -45.8                         |

| 2                 | -1.0                          | 32                | -16.0                         | 62                | -31.1                         | 92                | -46.2                         |

| 3                 | -1.5                          | 33                | -16.5                         | 63                | -31.6                         | 93                | -46.7                         |

| 4                 | -2.0                          | 34                | -17.0                         | 64                | -32.1                         | 94                | -47.4                         |

| 5                 | -2.5                          | 35                | -17.5                         | 65                | -32.6                         | 95                | -47.9                         |

| 6                 | -3.0                          | 36                | -18.1                         | 66                | -33.1                         | 96                | -48.2                         |

| 7                 | -3.5                          | 37                | -18.6                         | 67                | -33.6                         | 97                | -48.7                         |

| 8                 | -4.0                          | 38                | -19.1                         | 68                | -34.1                         | 98                | -49.3                         |

| 9                 | -4.5                          | 39                | -19.6                         | 69                | -34.6                         | 99                | -50.0                         |

| 10                | -5.0                          | 40                | -20.1                         | 70                | -35.2                         | 100               | -50.3                         |

| 11                | -5.5                          | 41                | -20.6                         | 71                | -35.7                         | 101               | -51.0                         |

| 12                | -6.0                          | 42                | -21.1                         | 72                | -36.2                         | 102               | -51.4                         |

| 13                | -6.5                          | 43                | -21.6                         | 73                | -36.7                         | 103               | -51.8                         |

| 14                | -7.0                          | 44                | -22.1                         | 74                | -37.2                         | 104               | -52.2                         |

| 15                | -7.5                          | 45                | -22.6                         | 75                | -37.7                         | 105               | -52.7                         |

| 16                | -8.0                          | 46                | -23.1                         | 76                | -38.2                         | 106               | -53.7                         |

| 17                | -8.5                          | 47                | -23.6                         | 77                | -38.7                         | 107               | -54.2                         |

| 18                | -9.0                          | 48                | -24.1                         | 78                | -39.2                         | 108               | -55.3                         |

| 19                | -9.5                          | 49                | -24.6                         | 79                | -39.7                         | 109               | -56.7                         |

| 20                | -10.0                         | 50                | -25.1                         | 80                | -40.2                         | 110               | -58.3                         |

| 21                | -10.5                         | 51                | -25.6                         | 81                | -40.7                         | 111               | -60.2                         |

| 22                | -11.0                         | 52                | -26.1                         | 82                | -41.2                         | 112               | -62.7                         |

| 23                | -11.5                         | 53                | -26.6                         | 83                | -41.7                         | 113               | -64.3                         |

| 24                | -12.0                         | 54                | -27.1                         | 84                | -42.1                         | 114               | -66.2                         |

| 25                | -12.5                         | 55                | -27.6                         | 85                | -42.7                         | 115               | -68.7                         |

| 26                | -13.0                         | 56                | -28.1                         | 86                | -43.2                         | 116               | -72.2                         |

| 27                | -13.5                         | 57                | -28.6                         | 87                | -43.8                         | 117–127           | -78.3                         |

| 28                | -14.0                         | 58                | -29.1                         | 88                | -44.3                         |                   |                               |

| 29                | -14.5                         | 59                | -29.6                         | 89                | -44.8                         |                   |                               |

## Table 2-10. Analog Volume Control for Headphone and Speaker Outputs

## 2.4.7.3 Class-D Speaker Analog Output Volume Control

For the speaker outputs, the analog volume control has a range from 0 dB to –78 dB in 0.5-dB steps for most of the useful range plus mute, as seen in Table 2-10. The implementation includes soft-stepping logic.

Routing the DAC output signal to the analog volume control via Mixer P and Mixer M is done by writing to page 1, register 12, bits D3. Changing the analog volume for the speaker is controlled by writing to page 1 / register 46, bits D6–D0.

The analog volume-control soft-stepping time is based on the setting in page 0, register 63, bits D1–D0.

## 2.4.8 Analog Outputs

Various analog routings are supported for playback. All the options can be viewed in the functional block diagram, Figure 2-6.

Figure 2-6. Analog Block Diagram

## 2.4.8.1 Headphone Drivers

The TAS2505 features a mono headphone driver (HPOUT) that can deliver up to 28 mW channel, at 1.8-V supply voltage, into a 16- $\Omega$  load. The headphones are used in a single-ended configuration where an accoupling (dc-blocking) capacitor is connected between the device output pins and the headphones. The headphone driver also supports 32- $\Omega$  and 10-k $\Omega$  loads without changing any control register settings.

The headphone driver can be configured to reduce the power consumption in the half drive ability mode by writing 1 to page 1, register 10, bits D2 = 1, also in this mode the headphone driver can support lineout-drive as well.

The common-mode voltage is set to  $\leq$  AVDD/2.

The headphone driver can be powered on by writing to page 1, register 9, bit D5. The HPOUT output driver gain can be controlled by writing to page 1 / register 16 bits D5–D0, and it can be muted by writing to page 1, register 16, bit D6.

The TAS2505 has a short-circuit protection feature for the headphone drivers, which is always enabled to provide protection. The output condition of the headphone driver during short circuit can be programmed by writing to page 1, register 11, bit D1. If D1 = 0 when a short circuit is detected, the device limits the maximum current to the load. If D1 = 1 when a short circuit is detected, the device powers down the output driver. The default condition for headphones is the current-limiting mode. For a short circuit on the channel, the output is disabled and a status flag is provided as read-only bits on page 0 / register 45, bit D5. If shutdown mode is enabled, then as soon as the short circuit is detected, page 0, register 9, bit D5 (for HPOUT) clears automatically. Next, the device requires a reset to re-enable the output stage. Resetting can be done in two ways. First, the device master reset can be used, which requires either toggling the RST pin or using the software reset. If master reset is used, it resets all of the registers. Second, a dedicated headphone power-stage reset can also be used to re-enable the output stage, and that keeps all of the other device settings. The headphone power stage reset is done by setting page 1, register 9, bit D5 for HPOUT. If the fault condition has been removed, then the device returns to normal operation. If the fault is still present, then another shutdown occurs. Repeated resetting (more than three times) is not recommended, as this could lead to overheating.

## Audio DAC and Audio Analog Outputs

### 2.4.8.2 Speaker Driver

The TAS2505 has an integrated class-D mono speaker driver (SPKP/SPKM) capable of driving an 8- $\Omega$  or 4- $\Omega$  differential load. The speaker driver can be powered directly from the battery supply (2.7 V to 5.5 V) on the SPKVDD pins; however, the voltage (including spike voltage) must be limited below the absolute-maximum voltage of 6 V.

The speaker driver is capable of supplying 800 mW per channel with a 3.6-V power supply. Through the use of digital mixing, the device can connect one or both digital audio playback data channels to either speaker driver; this also allows digital channel swapping if needed.

The class-D speaker driver can be powered on by writing to page 1, register 45, bit D1. The class-D output-driver gain can be controlled by writing to page 1, register 48, bits D6–D4, and it can be muted by writing to page 1, register 48, bit D6 - D4 = 000.

The TAS2505 has a short-circuit protection feature for the speaker drivers that is always enabled to provide protection. If the output is shorted, the output stage shuts down on the overcurrent condition. (Current limiting is not an available option for the higher-current speaker driver output stage.) In case of a short circuit, the output is disabled and a status flag is provided as a read-only bit on page 0, register 46, bit D7.

If shutdown occurs due to an overcurrent condition, then the device requires a reset to re-enable the output stage. Resetting can be done in two ways. First, the device master reset can be used, which requires either toggling the RST pin or using the software reset. If master reset is used, it resets all of the registers. Second, a dedicated speaker power-stage reset can be used that keeps all of the other device settings. The speaker power-stage reset is done by setting page 1, register 45, bit D1 for SPKP and SPKM. If the fault condition has been removed, then the device returns to normal operation. If the fault is still present, then another shutdown occurs. Repeated resetting (more than three times) is not recommended, as this could lead to overheating.

## To minimize battery current leakage, the SPKVDD voltage level should not be less than the AVDD voltage level.

The TAS2505 has a thermal protection (OTP) feature for the speaker driver which is always enabled to provide protection. If the device is overheated, then the output stops switching. When the device cools down, the output resumes switching. An overtemperature status flag is provided as a read-only bit on page 0, register 45, bit D7. The OTP feature is for self-protection of the device. If die temperature can be controlled at the system/board level, then overtemperature does not occur.

## 2.4.9 Audio Output-Stage Power Configurations

After the device has been configured (following a RST) and the circuitry has been powered up, the audio output stage can be powered up and powered down by register control.

These functions soft-start automatically. By using these register controls, it is possible to turn all four stages on at the same time without turning two of them off.

See Table 2-11 for register control of audio output stage power configurations.

| Audio Output Pins | Desired Function          | Page 1 / Register, Bit Value     |

|-------------------|---------------------------|----------------------------------|

| HPOUT             | Power-down HPOUT driver   | Page 1 / register 9, bit D5 = 0  |

| HPOUT             | Power-up HPOUT driver     | Page 1 / register 8, bit D5 = 1  |

| SPKP / SPKM       | Power-down class-D driver | Page 1 / register 45, bit D1 = 0 |

| SPKP / SPKM       | Power-up class-D driver   | Page 1 / register 45, bit D1 = 1 |

## Table 2-11. Audio Output Stage Power Configurations

## 2.4.10 5V LDO

The TAS2505 has a built-in LDO which can generate the analog supply (AVDD) also the digital supply (DVDD) from input voltage range of 2.7 V to 5.5 V with high PSRR. If combined power supply current is 50 mA or less, then this LDO can deliver power to both analog and digital power supplies. If the only speaker power supply is present and LDO Select pin is enabled, the LDO can power up without requiring other supplies. This LDO requires a minimum dropout voltage of 300 mV and can support load currents up to 50 mA. For stability reasons the LDO requires a minimum decoupling capacitor of 1  $\mu$ F (±50%) on the analog supply (AVDD) pin and the digital supply (DVDD) pin. If use this LDO output voltage for the digital supply (DVDD) pin, the analog supply (AVDD) pin connected to the digital supply (DVDD) externally is required.

The LDO is by default powered down for low sleep mode currents and can be enabled driving the LDO\_SEL pin to SPKVDD (Speaker power supply). When the LDO is disabled the AVDD pin is tri-stated and the device AVDD needs to be powered using external supply. In that case the DVDD pin is also tri-stated and the device DVDD needs to be powered using external supply. The output voltage of this LDO can be adjusted to a few different values as given in the Table 2-12. A Circuit Configuration with Internal LDO is shown in Section 1.3

| Page-1, Register 2, D(5:4) | LDO Output |

|----------------------------|------------|

| 00                         | 1.8 V      |

| 01                         | 1.6 V      |

| 10                         | 1.7 V      |

| 11                         | 1.5 V      |

## Table 2-12. AVDD LDO Settings

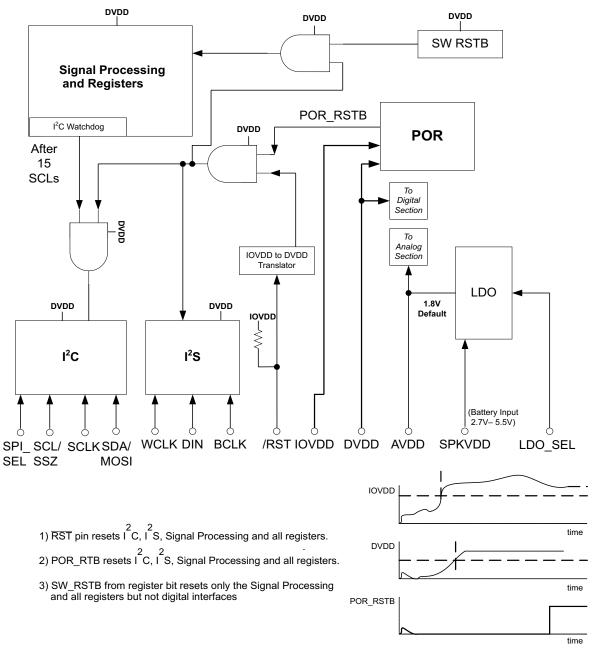

## 2.4.11 POR

TAS2505 has a POR (Power On Reset) function as shown Figure 2-7. This function insures that all registers are automatically set to defaults when a proper power up sequence is executed. The function consume approximately 35uA from the DVDD so if needed this can be disabled by page 1, register 1, bit D3 = 1.

## 2.4.12 DAC Setup

The following paragraphs are intended to guide a user through the steps necessary to configure the TAS2505.

Step 1

The system clock source (master clock) and the targeted DAC sampling frequency must be identified. Depending on the targeted performance, the decimation filter type (A or B) and DOSR value can be determined:

- Filter A should be used for 48-kHz high-performance operation; DOSR must be a multiple of 8.

- Filter B should be used for up to 96-kHz operations; DOSR must be a multiple of 4.

In all cases, DOSR is limited in its range by the following condition:

2.8 MHz < DOSR x DAC\_fS < 6.2 MHz

(3)

(4)

(5)

Based on the identified filter type and the required signal processing capabilities, the appropriate processing block can be determined from the list of available processing blocks (PRB\_P1, PRB\_P2 and PRB\_P3).

Based on the available master clock, the chosen DOSR and the targeted sampling rate, the clock divider values NDAC and MDAC can be determined. If necessary, the internal PLL can add a large degree of flexibility.

In summary, CODEC\_CLKIN (derived directly from the system clock source or from the internal PLL) divided by MDAC, NDAC, and DOSR must be equal to the DAC sampling rate DAC\_fS. The CODEC CLKIN clock signal is shared with the DAC clock generation block.

CODEC\_CLKIN = NDAC × MDAC × DOSR × DAC\_fS

NDAC and MDAC can be chosen independently in the range of 1 to 128. In general, NDAC should be as large as possible as long as the following condition can still be met:

MDAC × DOSR /  $32 \ge RC$

RC is a function of the chosen processing block and is listed in Table 2-3.

The common-mode voltage setting of the device is determined by the available analog power supply. This common-mode (input common-mode) value is common across the ADC, DAC and analog bypass path. The output common-mode setting is determined by the available analog power supplies (AVdd and ) and the desired output-signal swing.

At this point, the following device specific parameters are known:

PRB\_Rx, DOSR, NDAC, MDAC, input and output common-mode values.

If the PLL is used, the PLL parameters P, J, D and R are determined as well.

Step 2

Setting up the device via register programming:

The following list gives a sequence of items that must be executed in the time between powering the device up and reading data from the device:

- 1. Define starting point:

- (a) Power up applicable external power supplies

- (b) Set register page to 0

- (c) Initiate SW reset

- 2. Program Clock Settings

- (a) Program PLL clock dividers P, J, D and R (if PLL is necessary)

- (b) Power up PLL (if PLL is necessary)

- (c) Program and power up NDAC

- (d) Program and power up MDAC

- (e) Program OSR value

- (f) Program I2S word length if required (16, 20, 24, or 32 bits)

- (g) Program the processing block to be used

(h) Miscellaneous page 0 controls

At this point, at the latest, the analog power supply must be applied to the device

- 3. Program Analog Blocks

- (a) Set register page to 1

- (b) Disable coarse AVDD generation

- (c) Enable Master Analog Power Control

- (d) Program common-mode voltage

- (e) Program headphone-specific de-pop settings (if a headphone driver is used)

- (f) Program routing of DAC output to the output amplifier (headphone and lineout or speaker)

- (g) Unmute and set gain of output drivers

- (h) Power up output drivers

- 4. Apply waiting time determined by the de-pop settings and the soft-stepping settings of the driver gain or poll page 1, register 63

- 5. Power up DAC

- (a) Set register page to 0

- (b) Power up DAC channels and set digital gain

- (c) Unmute digital volume control

Detailed examples can be found from Section 4.0.7 to Section 4.0.12.

## 2.5 PowerTune

The TAS2505features PowerTune, a mechanism to balance power-versus-performance tradeoffs at the time of device configuration. The device can be tuned to minimize power dissipation, to maximize performance, or to an operating point between the two extremes to best fit the application.

## 2.5.1 PowerTune Modes

## 2.5.1.1 DAC - Programming PTM\_P1 to PTM\_P4

On the playback side, the performance is determined by a combination of register settings and the audio data word length applied. For the highest performance setting (PTM\_P4), an audio-data word length of 20 bits is required, while for the modes PTM\_P1 to PTM\_P3 a word length of 16 bits is sufficient.

|                                                | PTM_P1          | PTM_P2          | PTM_P3          | PTM_P4                           |

|------------------------------------------------|-----------------|-----------------|-----------------|----------------------------------|

| Pg 1, Reg 3, D(4:2)                            | 0x2             | 0x1             | 0x0             | 0x0                              |

| Audio Data word length<br>Pg 0, Reg 27, D(5:4) | 16 bits<br>0x00 | 16 bits<br>0x00 | 16 bits<br>0x00 | 20 or more bits<br>0x1, 0x2, 0x3 |

## 2.5.1.2 Processing Blocks

The choice of processing blocks, PRB\_P1 to PRB\_P3 for playback, also influences the power consumption. In fact, the numerous processing blocks have been implemented to offer a choice between power-optimization and configurations with more signal-processing resources.

## 2.5.2 DAC Power Consumption

The tables in this section give recommendations for various DAC PowerTune modes. Typical performance and power-consumption numbers for line-out signals are listed.

All measurements were taken with the PLL turned off, no signal is present, and the DAC modulator is fully running. PowerTune modes which are not supported are marked with an 'X'.

## 2.5.2.1 DAC, Mono, 48 kHz, Highest Performance, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V

## DOSR = 128, Processing Block = PRB\_P3 (Interpolation Filter B)

|                |                               | Device Common Mode Setting = 0.75V |        |        |        | Device Common Mode Setting = 0.9V |        |        |        |                              |

|----------------|-------------------------------|------------------------------------|--------|--------|--------|-----------------------------------|--------|--------|--------|------------------------------|

|                |                               | PTM_P1                             | PTM_P2 | PTM_P3 | PTM_P4 | PTM_P1                            | PTM_P2 | PTM_P3 | PTM_P4 | Unit                         |

| 00             | 0dB full scale <sup>(1)</sup> |                                    | 225    | 375    | 375    | 100                               | 300    | 500    | 500    | $\mathrm{mV}_{\mathrm{RMS}}$ |

| HP out         | Idle Channel Noise            | 16.8                               | 16.9   | 17.1   | 17.0   | 19.4                              | 20.0   | 20.1   | 20.0   | uV                           |

| (16-Ω<br>load) | Power consumption             | 7.2                                | 7.4    | 7.7    | 7.7    | 7.3                               | 7.7    | 8.0    | 8.1    | mW                           |

<sup>(1)</sup> Reduced 0dB full-scale swing can be compensated by applying appropriate gain in the output drivers see Section 2.4.2.1.

### Alternative Processing Blocks:

| Processing Block | Filter | Estimated Power Change at PTM_P3 |           |      |  |

|------------------|--------|----------------------------------|-----------|------|--|

|                  |        | HP                               |           |      |  |

|                  |        | CM = 0.75V                       | CM = 0.9V | Unit |  |

| PRB_P1           | А      | +1.34                            | +1.30     | m)0/ |  |

| PRB_P2           | А      | -0.11                            | -0.11     | mW   |  |

## 2.5.2.2 DAC, Mono, Lowest Power Consumption

## DOSR = 64, Processing Block = PRB\_P3 (Interpolation Filter B)

|             |                               | CM = 0.75V<br>AVDD = 1.5V | CM = 0.9V<br>AVDD = 1.8V | Unit              |  |

|-------------|-------------------------------|---------------------------|--------------------------|-------------------|--|

|             |                               | PTM_P1                    | PTM_P1                   |                   |  |

| 0           | 0dB full scale <sup>(1)</sup> |                           | 100                      | mV <sub>RMS</sub> |  |

| HP out      | Idle Channel Noise            | 16.8                      | 19.3                     | uV                |  |

| (16-Ω load) | Power consumption             | 5.8                       | 6.7                      | mW                |  |

<sup>(1)</sup> Reduced 0dB full-scale swing can be compensated by applying appropriate gain in the output drivers see Section 2.4.2.1.

#### Alternative Processing Blocks:

| Processing Block | Filter | Estimated Power Change at PTM_P1<br>HP out |           |      |

|------------------|--------|--------------------------------------------|-----------|------|

|                  |        |                                            |           | Unit |

|                  |        | CM = 0.75V                                 | CM = 0.9V |      |

| PRB_P1           | А      | +1.46                                      | +1.49     | mW   |

| PRB_P2           | А      | 0.00                                       | +0.03     |      |

## 2.5.2.3 DAC, Mono, 8 kHz, Highest Performance, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V DOSR = 768, Processing Block = PRB\_P2 (Interpolation Filter A)

|                       |                               | Device Common Mode Setting =<br>0.75V |        |        | Device Common Mode Setting = 0.9V |        |        |        |        |            |

|-----------------------|-------------------------------|---------------------------------------|--------|--------|-----------------------------------|--------|--------|--------|--------|------------|

|                       |                               | PTM_P1                                | PTM_P2 | PTM_P3 | PTM_P4                            | PTM_P1 | PTM_P2 | PTM_P3 | PTM_P4 | Unit       |

| 0dB 1                 | 0dB full scale <sup>(1)</sup> |                                       | 225    | 375    | 375                               | 100    | 300    | 500    | 500    | $mV_{RMS}$ |

| HP out<br>(16-Ω load) | Idle Channel Noise            | 14.3                                  | 14.3   | 14.5   | 14.4                              | 16.7   | 16.8   | 16.9   | 17.3   | uV         |

|                       | Power consumption             | 5.8                                   | 6.0    | 6.2    | 6.3                               | 5.8    | 6.2    | 6.4    | 6.5    | mW         |

<sup>(1)</sup> Reduced 0dB full-scale swing can be compensated by applying appropriate gain in the output drivers see Section 2.4.2.1.

## Alternative Processing Blocks:

| Processing Block | Filter | Estimated Power Change at PTM_P1<br>HP out |           |      |  |

|------------------|--------|--------------------------------------------|-----------|------|--|

|                  |        |                                            |           | Unit |  |

|                  |        | CM = 0.75V                                 | CM = 0.9V |      |  |

| PRB_P1           | А      | +0.46                                      | +0.53     | m)// |  |

| PRB_P3           | В      | +0.19                                      | +0.26     | mW   |  |

## 2.5.2.4 DAC, Mono, Lowest Power Consumption

## DOSR = 384, Processing Block = PRB\_P2 (Interpolation Filter A)

|             |                               | CM = 0.75V<br>AVDD = 1.5V | CM = 0.9V<br>AVDD = 1.8V | Unit              |  |

|-------------|-------------------------------|---------------------------|--------------------------|-------------------|--|

|             |                               | PTM_P1                    | PTM_P1                   | 1                 |  |

| 00          | 0dB full scale <sup>(1)</sup> |                           | 100                      | mV <sub>RMS</sub> |  |

| HP out      | Idle Channel Noise            | 14.2                      | 16.9                     | uV                |  |

| (16-Ω load) | Power consumption             | 4.2                       | 5.1                      | mW                |  |

<sup>(1)</sup> Reduced 0dB full-scale swing can be compensated by applying appropriate gain in the output drivers see Section 2.4.2.1.

## Alternative Processing Blocks:

| Processing Block | Filter | Estimated Power Change at PTM_P1 |           |       |

|------------------|--------|----------------------------------|-----------|-------|

|                  |        | HP o                             | out       | Unit  |

|                  |        | CM = 0.75V                       | CM = 0.9V |       |

| PRB_P1           | А      | +0.43                            | +0.43     | mW    |

| PRB_P3           | В      | +0.17                            | +0.18     | TIIVV |

## 2.5.3 Speaker output Power Consumption

To consider Speaker output power consumption on the TAS2505, the tables in this section to be may useful to know the power consumption for each power rail. The tables show a representable combination of PRB mode and PTM mode.

All measurements were taken with the PLL turned off, no signal is present, and the DAC modulator is fully running.

## 2.5.3.1 Speaker output, Mono, 48 kHz, Highest Performance, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V

## DOSR = 128, PRB mode = PRB\_P3, PTM mode = PTM\_P3, CM = 0.9V

|                          |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|--------------------------|-------------------|-------|-------|-------|--------|-------|----|

| SPK Driver<br>(4-Ω load) | Power consumption | 28.51 | 3.26  | 3.71  | 0.01   | 35.5  | mW |

## 2.5.3.2 Speaker output, Mono, Lowest Power Consumption

#### DOSR = 64, PRB mode = PRB\_P3, PTM mode = PTM\_P3, CM = 0.9V

|                          |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|--------------------------|-------------------|-------|-------|-------|--------|-------|----|

| SPK Driver<br>(4-Ω load) | Power consumption | 28.50 | 3.26  | 3.01  | 0.01   | 34.8  | mW |

## 2.5.3.3 Speaker output, Mono, 8 kHz, Highest Performance, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V

#### DOSR = 768, PRB mode = PRB\_P2, PTM mode = PTM\_P3, CM = 0.9V

|                            |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|----------------------------|-------------------|-------|-------|-------|--------|-------|----|

| SPK Driver F<br>(4-Ω load) | Power consumption | 28.49 | 3.26  | 2.23  | 0.01   | 34.0  | mW |

## 2.5.3.4 Speaker output, Mono, Lowest Power Consumption

#### DOSR = 384, PRB mode = PRB\_P2, PTM mode = PTM\_P3, CM = 0.9V

|                          |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|--------------------------|-------------------|-------|-------|-------|--------|-------|----|

| SPK Driver<br>(4-Ω load) | Power consumption | 28.49 | 3.26  | 1.53  | 0.01   | 33.3  | mW |

## 2.5.4 Headphone output Power Consumption

To consider Headphone output power consumption on the TAS2505, the tables in this section to be may useful to know the power consumption for each power rail. The tables show a representable combination of PRB mode and PTM mode.

All measurements were taken with the PLL turned off, no signal is present, and the DAC modulator is fully running.

## 2.5.4.1 Headphone output, Mono, 48 kHz, Highest Performance, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V

## DOSR = 128, PRB mode = PRB\_P3, PTM mode = PTM\_P3, CM = 0.9V

|                                 |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|---------------------------------|-------------------|-------|-------|-------|--------|-------|----|

| Headphone Driver<br>(16-Ω load) | Power consumption | 0.11  | 4.50  | 3.42  | 0.01   | 8.0   | mW |

## 2.5.4.2 Headphone output, Mono, Lowest Power Consumption, DVDD = IOVDD = 1.8 V, AVDD = 1.5 V, SPKVDD = 3.6V

## DOSR = 64, PRB mode = PRB\_P3, PTM mode = PTM\_P1, CM = 0.75V

|                                 |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|---------------------------------|-------------------|-------|-------|-------|--------|-------|----|

| Headphone Driver<br>(16-Ω load) | Power consumption | 0.12  | 2.97  | 2.68  | 0.01   | 5.8   | mW |

## 2.5.4.3 Headphone output, Mono, 8 kHz, Highest Performance, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V

## DOSR = 768, PRB mode = PRB\_P2, PTM mode = PTM\_P3, CM = 0.9V

|                                 |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|---------------------------------|-------------------|-------|-------|-------|--------|-------|----|

| Headphone Driver<br>(16-Ω load) | Power consumption | 0.13  | 4.43  | 1.82  | 0.01   | 6.4   | mW |

## 2.5.4.4 Headphone output, Mono, Lowest Power Consumption, DVDD = IOVDD = 1.8 V, AVDD = 1.8 V, SPKVDD = 3.6V

## DOSR = 384, PRB mode = PRB\_P2, PTM mode = PTM\_P1, CM = 0.75V

|                                 |                   | iSVDD | iAVDD | iDVDD | iIOVDD | Total |    |

|---------------------------------|-------------------|-------|-------|-------|--------|-------|----|

| Headphone Driver<br>(16-Ω load) | Power consumption | 0.12  | 2.96  | 1.11  | 0.01   | 4.2   | mW |

PowerTune

## 2.6 CLOCK Generation and PLL

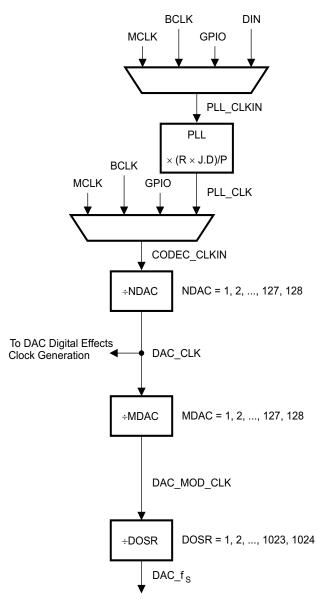

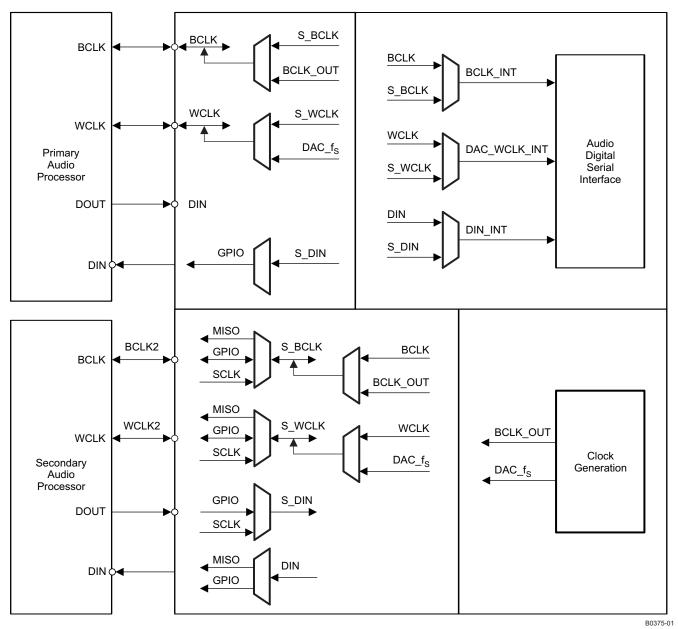

The TAS2505 supports a wide range of options for generating clocks for the DAC sections as well as interface and other control blocks as Fig. 2-8 shows The clocks for the DAC require a source reference clock. This clock can be provided on a variety of device pins, such as the MCLK, BCLK, or GPIO pins. The source reference clock for the codec can be chosen by programming the CODEC\_CLKIN value on page 0, register 4, bits D1–D0. The CODEC\_CLKIN can then be routed through highly-flexible clock dividers shown in to generate the various clocks required for the DAC and the Digital Effects section. In the event that the desired audio clocks cannot be generated from the reference clocks on MCLK, BCLK, or GPIO, the TAS2505 also provides the option of using the on-chip PLL which supports a wide range of fractional multiplication values to generate the required clocks. Starting from CODEC\_CLKIN, the TAS2505 provides several programmable clock dividers to help achieve a variety of sampling rates for the DAC and clocks for the Digital Effects sections.

Figure 2-8. Clock Distribution Tree

# $DAC\_MOD\_CLK = \frac{CODEC\_CLKIN}{NDAC \times MDAC}$

$DAC_{f_{S}} = \frac{CODEC\_CLKIN}{NDAC \times MDAC \times DOSR}$

(6)

## Table 2-13. CODEC CLKIN Clock Dividers

| Divider | Bits                                                                |

|---------|---------------------------------------------------------------------|

| NDAC    | Page 0, register 11, bits D6–D0                                     |

| MDAC    | Page 0, register 12, bits D6–D0                                     |

| DOSR    | Page 0, register 13, bits D1–D0 and page 0, register 14, bits D7–D0 |

The DAC modulator is clocked by DAC\_MOD\_CLK. For proper power-up operation of the DAC channel, these clocks must be enabled by configuring the NDAC and MDAC clock dividers (page 0, register 11, bit D7 = 1 and page 0, register 12, bit D7 = 1). When the DAC channel is powered down, the device internally initiates a power-down sequence for proper shut-down. During this shutdown sequence, the NDAC and MDAC dividers must not be powered down, or else a proper low-power shutdown may not take place. The user can read back the power-status flag at page 0, register 37, bit D7 and page 0, register 37, bit D3. When both the flags indicate power-down, the MDAC divider may be powered down, followed by the NDAC divider.

In general, all the root clock dividers should be powered down only after the child clock dividers have been powered down for proper operation.

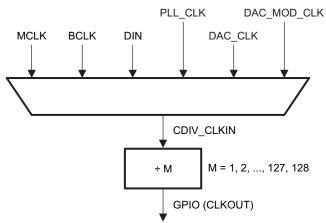

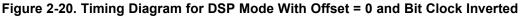

The TAS2505 also has options for routing some of the internal clocks to the GPIO output pin to be used as general-purpose clocks in the system. The feature is shown in Figure 2-10.

Figure 2-9. BCLK Output Options

In the mode when TAS2505 is configured to drive the BCLK pin (page 0, register 27, bit D3 = 1), it can be driven as a divided value of BDIV\_CLKIN. The division value can be programmed in page 0, register 30, bits D6–D0 from 1 to 128 (see Figure 2-9). The BDIV\_CLKIN can itself be configured to be one of DAC\_CLK (DAC DSP clock) or DAC\_MOD\_CLK by configuring the BDIV\_CLKIN multiplexer in page 0, register 29, bits D1-D0. Additionally, a general-purpose clock can be driven out on GPIO.

CLOCK Generation and PLL

www.ti.com

This clock can be a divided-down version of CDIV\_CLKIN. The value of this clock divider can be programmed from 1 to 128 by writing to page 0, register 26, bits D6–D0. The CDIV\_CLKIN can itself be programmed as one of the clocks among the list shown in Figure 2-10. This can be controlled by programming the multiplexer in page 0, register 25, bits D2–D0.

B0363-01

Figure 2-10. General-Purpose Clock Output Options

| Clock              | DVDD ≥ 1.65 V                                   |

|--------------------|-------------------------------------------------|

| CODEC_CLKIN        | ≤ 110 MHz                                       |

| DAC_CLK            | ≤ 49.152 MHz                                    |

| DAC_MOD_CLK        | 6.758 MHz                                       |

| DAC_f <sub>s</sub> | 0.192 MHz                                       |

| BDIV_CLKIN         | 55 MHz                                          |

| CDIV_CLKIN         | 100 MHz when M is odd<br>110 MHz when M is even |

## 2.6.1 PLL