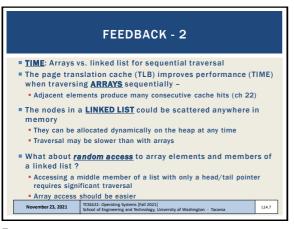

**FEEDBACK** What data structures lend themselves to our goals for address spaces? Goals for OS Memory Virtualization: Transparency Protection (Security/Isolation) Efficiency (Time & Space) ■ Some data structures may be more compact (space) with lower memory virtualization overhead (time) SPACE: consider a statically declared multi-dimensional array vs. a linked list One has a huge up-front cost, while the other grows incrementally November 23, 2021 L14.6

6

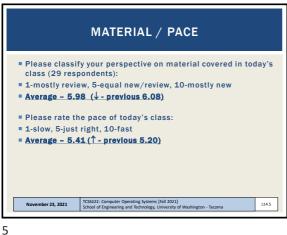

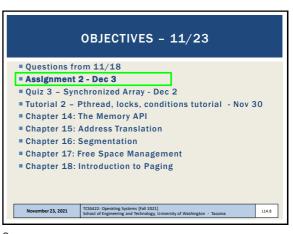

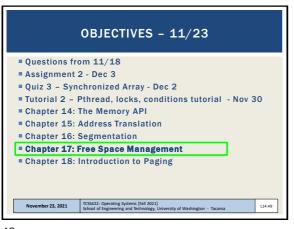

OBJECTIVES - 11/23

Questions from 11/18

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Chapter 14: The Memory API

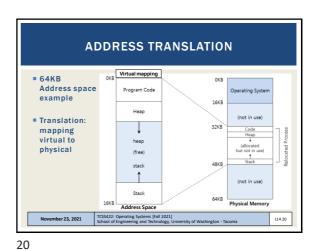

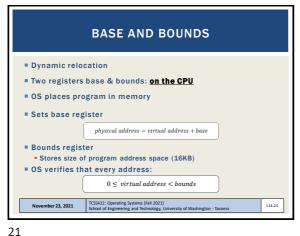

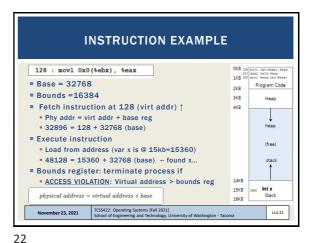

Chapter 15: Address Translation

Chapter 16: Segmentation

Chapter 17: Free Space Management

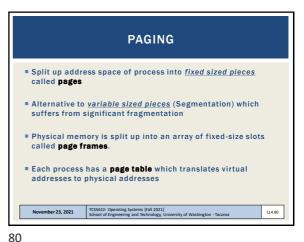

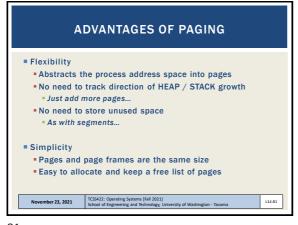

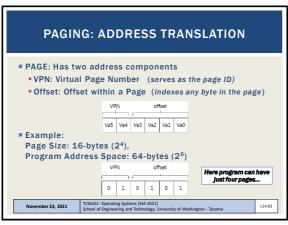

Chapter 18: Introduction to Paging

November 23, 2021

TCSS42: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Taxoma

10

9

CHAPTER 14: THE MEMORY API

TCSS422: Operating Systems [Fal 2021] School of Engineering and Tochnology, University of Washington - 1: orns L14.12

11 12

13

17 18

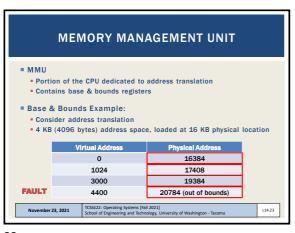

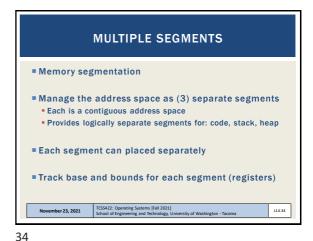

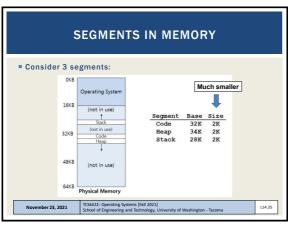

**DYNAMIC RELOCATION OF PROGRAMS** Hardware requirements: Requirements **HW** support Privileged mode CPU modes: kernel, user Registers to support address translation Base / bounds registers Translate virtual addr; check if in Translation circuitry, check limits Privileged instruction(s) to Instructions for modifying base/bound update base / bounds regs Privileged instruction(s) Set code pointers to OS code to handle faults to register exception handlers Ability to raise exceptions For out-of-bounds memory access, or attempts to access privileged instr. TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma November 23, 2021 L14.24

23 24

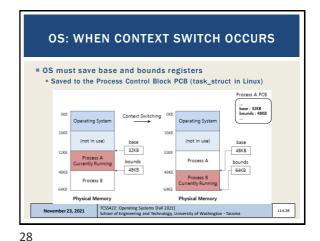

**DYNAMIC RELOCATION** OS can move process data when not running 1. OS un-schedules process from scheduler 2. OS copies address space from current to new location 3. OS updates PCB (base and bounds registers) 4. OS reschedules process When process runs new base register is restored to CPU Process doesn't know it was even moved! TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma November 23, 2021 L14.29

Consider a 64KB computer the loads a program. The BASE register is set to 32768, and the BOUNDS register is set to 4096. What is the physical memory address translation for a virtual address of 6000? 34768 38768 32769 36864 Out of bounds

29 30

00

35 36

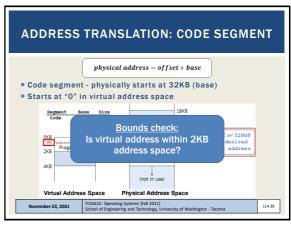

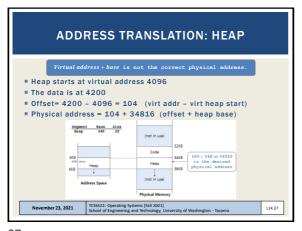

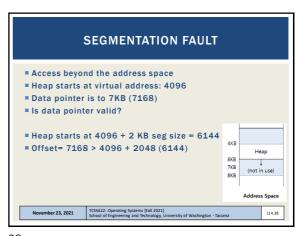

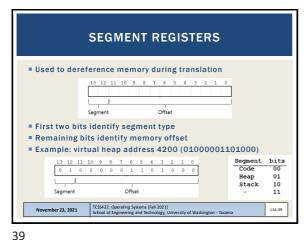

**SEGMENTATION DEREFERENCE** // get top 2 bits of 14-bit VA

Segment = (VirtualAddress & SEG\_MASK) >> SEG\_SHIFT // now get offset

Offset = VirtualAddress & OFFSET\_MASK

if (Offset >= Bounds[Segment])

RaiseException(PROTECTION\_FAULT) PhysAddr = Base[Segment] + Offset Register = AccessMemory(PhysAddr) VIRTUAL ADDRESS = 01000001101000 (on heap) **SEG\_MASK** = 0x3000 (1100000000000) ■ SEG\_SHIFT = 01 → heap (mask gives us segment code) OFFSET\_MASK = 0xFFF (00111111111111) • OFFSET = 000001101000 = 104 (isolates segment offset) ■ OFFSET < BOUNDS: 104 < 2048 November 23, 2021

40

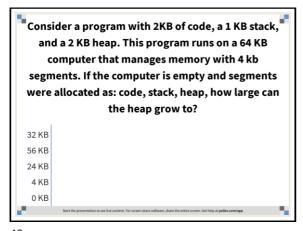

| Stack grows backwards (FILO)  Requires hardware support:  Direction bit: tracks direction segment grows  (not in use)  Segment Register(with Negative-Growth Support)  Segment Base Size Growth Support) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stack   Segment Base Size Grows Positive?                                                                                                                                                                                                                                                                                                                                                                                  |

| Physical Memory                                                                                                                                                                                                                                                                                                                                                                                                            |

**SHARED CODE SEGMENTS** ■ Code sharing: enabled with HW support Supports storing shared libraries in memory only once ■ DLL: dynamic linked library .so (linux): shared object in Linux (under/usr/lib) ■ Many programs can access them ■ Protection bits: track permissions to segment

Base

Size

Grows Positive?

Protection

32K

2K

1

Read-Execute

Read-Write November 23, 2021 L14.42

41 42

47 48

November 23, 2021

OBJECTIVES - 5/18

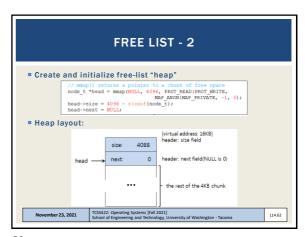

Chapter 17: Free Space Management

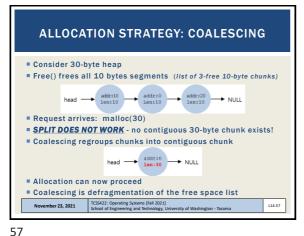

Fragmentation, Splitting, coalescing

The Free List

Memory Allocation Strategies

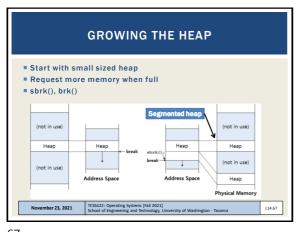

FREE SPACE MANAGEMENT

How should free space be managed, when satisfying variable-sized requests?

What strategies can be used to minimize fragmentation?

What are the time and space overheads of alternate approaches?

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

51

L14.51

52

54

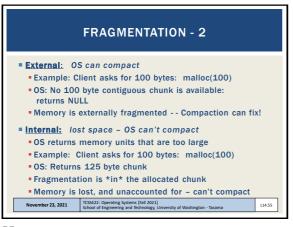

FRAGMENTATION

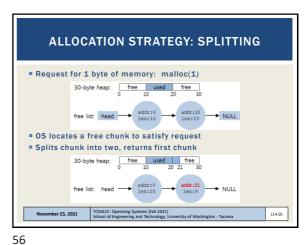

Consider a 30-byte heap

30-byte heap: free used free

0 10 20 30

Request for 15-bytes

free list: head addr:0 addr:20 hen:10 NULL

Free space: 20 bytes

No available contiguous chunk > return NULL

102542: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma L14.54

Slides by Wes J. Lloyd

53

37

```

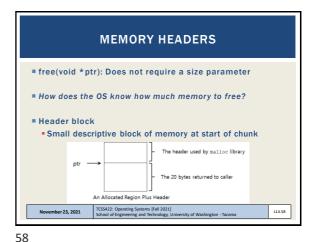

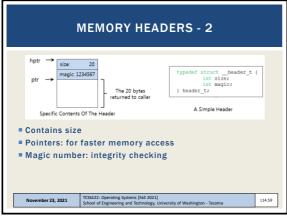

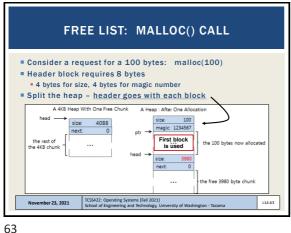

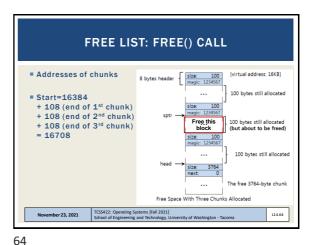

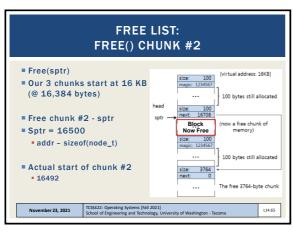

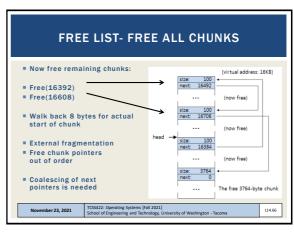

MEMORY HEADERS - 3

Size of memory chunk is:

Header size + user malloc size

N bytes + sizeof(header)

Easy to determine address of header

void free (void *ptr) {

header_t *hptr = (void *)ptr - sizeof(header_t);

}

November 23, 2021

TGSS422-Operating Systems [fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

```

59 60

65 66

70

67

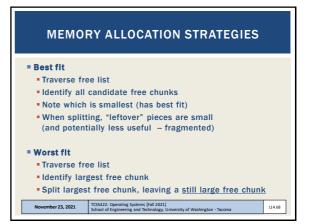

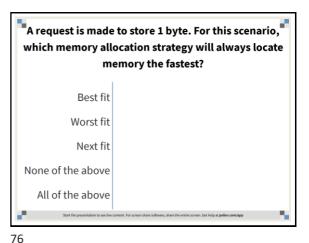

EXAMPLES

■ Allocation request for 15 bytes

head → 10 → 30 → 20 → NULL

■ Result of Best Fit

head → 10 → 30 → 5 → NULL

■ Result of Worst Fit

head → 10 → 15 → 20 → NULL

November 23, 2021 | TCS5422: Operating Systems [Fall 2021] | School of Engineering and Technology, University of Washington - Taxoma | L14.69

69

Which memory allocation strategy is more likely to distribute free chunks closer together which could help when coalescing the free space list?

Best Fit

Worst Fit

First Fit

None of the above

All of the above

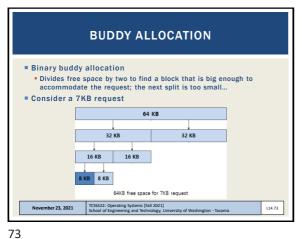

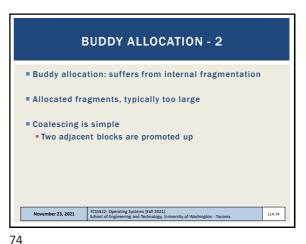

SEGREGATED LISTS

For popular sized requests

e.g. for kernel objects such as locks, inodes, etc.

Manage as segregated free lists

Provide object caches: stores pre-initialized objects

How much memory should be dedicated for specialized requests (object caches)?

If a given cache is low in memory, can request "slabs" of memory from the general allocator for caches.

General allocator will reclaim slabs when not used

| November 23, 2021 | TCSS422- Operating Systems [Sall 2021] | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | School of Engineering and Technology, University of Washington - Tacoma | Lit 172 | Lit 17

71 72

A computer system manages program memory using three separate segments for code, stack, and the heap. The codesize of a program is 1KB but the minimal segment available is 16KB. This is an example of: External fragmentation Binary buddy allocation Internal fragmentation Coalescing **Splitting**

75

77 78

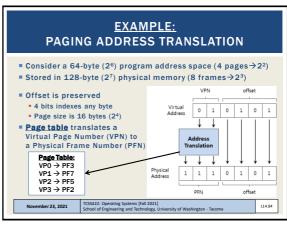

Page Table: **PAGING: EXAMPLE** VP0 → PF3 VP1 → PF7 VP2 → PF5 VP3 → PF2 Consider a 128 byte (27) address space with 16-byte (24) pages page frame 0 of Consider a 64-byte (26) (unused) page frame 1 program address space page 3 of AS page frame 2 page frame 3 (page 1) page 2 of AS page frame 6 (unused) page 1 of AS page frame 7 64-Byte Address Space Placed In Physical Memor ember 23, 2021 L14.82

82

81

83

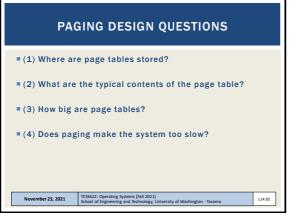

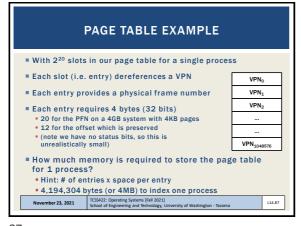

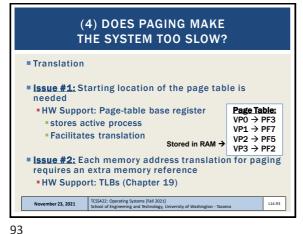

(1) WHERE ARE PAGE TABLES STORED?

Example:

Consider a 32-bit process address space (4GB=2<sup>32</sup> bytes)

With 4 KB pages (4KB=2<sup>12</sup> bytes)

Obits for VPN (2<sup>20</sup> pages)

It bits for the page offset (2<sup>12</sup> unique bytes in a page)

Page tables for each process are stored in RAM

Support potential storage of 2<sup>20</sup> translations

In 1,048,576 pages per process

Each page has a page table entry size of 4 bytes

86

88

85

NOW FOR AN ENTIRE OS

If 4 MB is required to store one process

Consider how much memory is required for an entire OS?

With for example 100 processes...

Page table memory requirement is now 4MB x 100 = 400MB

If computer has 4GB memory (maximum for 32-bits), the page table consumes 10% of memory

400 MB / 4000 GB

Is this efficient?

November 23, 2021

TCSS42: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

87

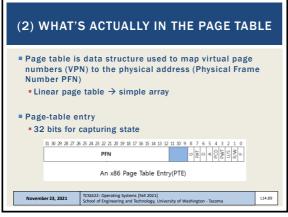

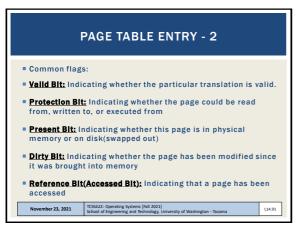

P: present

R/W: read/write bit

U/S: supervisor

A: accessed bit

D: dirty bit

PFN: the page frame number

31 30 29 28 77 26 28 24 22 22 22 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 1 0

PFN

An x86 Page Table Entry(PTE)

November 23, 2021

114.50

L14.50

89 90

(3) HOW BIG ARE PAGE TABLES?

Page tables are too big to store on the CPU

Page tables are stored using physical memory

Paging supports efficiently storing a sparsely populated address space

Reduced memory requirement

Compared to base and bounds, and segments

\*\*TCS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

92

94

91

93

```

COUNTING MEMORY ACCESSES

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1] = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1] = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1) = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1) = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1000);

for (i = 0; i < 1000; i++)

array(1) = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1) = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1) = 0;

Example: Use this Array initialization Code

int array(1000);

for (i = 0; i < 1000; i++)

array(1) = 0;

Example: Use this Array initialization Code

```

**VISUALIZING MEMORY ACCESSES:** FOR THE FIRST 5 LOOP ITERATIONS Locations: Page table 1174 Array - 1124 • Code 1074 0 0000 0000 0000 0000 000 - 1024 50 accesses for 5 loop 7282 iterations 4146 TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, Uni November 23, 2021 L14.96 ersity of Washington - Tacoma

95 96

For the 4GB computer example, how many bits are available for page status bits? 32 - 12 VPN bits = 20 status bits 32 - 24 VPN bits = 8 status bits 32 - 16 VPN bits = 16 status bits 32 - 20 VPN bits = 12 status bits None of the above

For the 4GB computer, how much space does this page table require? (number of page table entries x size of page table entry) 2^20 entries x 4b = 4 MB 2^12 entries x 4b = 16 KB 2^16 entries x 4b = 256 KB 2^24 entries x 4b = 64 MB None of the above

99

For the 4GB computer, how many page tables (for user processes) would fill the entire 4GB of memory? 4 GB / 16 KB = 65,536 4 GB / 64 MB = 256 4GB / 256 KB = 16,384 4GB / 4MB = 1,024 None of the above 101

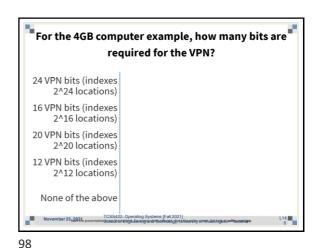

**PAGING SYSTEM EXAMPLE** Consider a 4GB Computer: With a 4096-byte page size (4KB) How many pages would fit in physical memory? Now consider a page table: For the page table entry, how many bits are required for the VPN? If we assume the use of 4-byte (32 bit) page table entries, how many bits are available for status bits? How much space does this page table require? # of page table entries x size of page table entry How many page tables (for user processes) would fill the entire 4GB of memory? November 23, 2021 TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma L14.102

102

100